Professional Documents

Culture Documents

Clase 03 - Interrupciones - Temporizadores

Uploaded by

sergiovelasquezg0 ratings0% found this document useful (0 votes)

50 views91 pagesClase 03 - Interrupciones

Original Title

Clase 03 - Interrupciones_temporizadores

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentClase 03 - Interrupciones

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

50 views91 pagesClase 03 - Interrupciones - Temporizadores

Uploaded by

sergiovelasquezgClase 03 - Interrupciones

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 91

INTERRUPCIONES

Interrupciones de la Familia DSPIC33E/PIC24E

Interrupciones de la Familia DSPIC33E/PIC24E

CARACTERISTICAS

El controlador de interrupcionesde lafamiliadsPIC33E/ PIC24E reduce el numerode

solicitudes de interrupcinde los perifricosaunasimple seal paralos dsPIC33E/ PIC24E.

Este mduloincluyelassiguientescaractersticas:

Ochointerrupcionespor excepciny trampapor software.

Siete niveles de prioridad seleccionable por el usuario.

Tablade vector de interrupcin(IVT) con un total de 254 vectores

Un vector unicoparacadafuentede interrupciny excepcin.

Prioridad fijaen un nivel especificado por el usuario

El dsPIC33E/ PIC24E admite hastacinco fuentes de pin de interrupcin externa(INT0-INT4).

Cadapin de interrupcin externatiene un circuito de deteccin de flanco paradetectar el

evento de interrupcin. El registro INTCON2 tiene cinco bits de control (INT0EP-INT4EP)

que seleccionan lapolaridad de lacircuiterade deteccin de flanco. Cadapin de interrupcin

externapuede ser programadaparainterrumpir laCPU en un flanco ascendente o descendente.

Interrupciones de la Familia DSPIC33E/PIC24E

TABLA DE VECTORES DE INTERRUPCION

LaIVT, como se muestraen ladiapositivasiguiente, reside en lamemoriade programay

empiezaen laubicacin 0x000004. El IVT contiene 254 vectores que consisten en ocho

vectores trampano enmascarables y hasta246 fuentes de interrupcin. En general, cada

fuente de interrupcin tiene su propio vector. Cadavector de interrupcin contiene una

direccin de 24 bits. El valor programado en cadaubicacin de vector de interrupcin es la

direccin de inicio de larutinade servicio de interrupcin asociado (ISR).

Cuando el cdigo se ejecutaen lamemoriaflash auxiliar, un vector de interrupcin especial

nico, ubicado en ladireccin 0x7FFFFA, se utilizaparatodas las fuentes y las trampas de

interrupcin. Unavez vectorizadoaestanicarutina, los bits VECNUM <7:0> en el registro

(INTTREG <7:0>) determinan lafuente de lainterrupcin o trampaparaque puedaser

procesadacorrectamente.

Interrupciones de la Familia DSPIC33E/PIC24E

INTERRUPCIONES DE TRAMPAS (no enmascarables)

Las trampas no son enmascarables, son interrupciones con prioridad fijas. Las trampas

proporcionan un medio paracorregir el funcionamiento errneo durante ladepuracin y el

funcionamiento de laaplicacin. Si el software del usuario no corrige estacondicin anormal,

estos vectores deben ser cargados con ladireccin de unarutinade software parareiniciar el

dispositivo.

Las siguientes fuentes de trampas no enmascarables se implementan en dispositivos

dsPIC33E/ PIC24E:

Trampapor Falladel Oscilador (Oscillator FailureTrap)

Trampapor Error de pila(StackError Trap)

Trampapor Error de Direccin (AddressError Trap)

Trampapor Error Matemtico (MathError Trap)

Trampapor Error DMAC (DMAC Error Trap)

Trampapor Hardware genrico (GenericHardTrap)

Trampapor Software genrico (GenericSoftTrap)

Interrupciones de la Familia DSPIC33E/PIC24E

Interrupciones por trampa de software:

.- STACK ERROR TRAP (SOFT TRAP, LEVEL 12)

.- MATH ERROR TRAP (SOFT TRAP, LEVEL 11)

Desbordamiento del Acumulador A

Desbordamiento del Acumulador B

Desbordamiento catastrfico del acumulador

Divisin por cero

Operacin de desplazamiento del acumulador supera16 bits

.- DMAC ERROR TRAP (SOFT TRAP, LEVEL 10)

.- GENERIC SOFT TRAP (SOFT TRAP, LEVEL 9)

USB Address Error Soft Trap (UAE)

DMA AddressError SoftTrap(DAE)

DO Stack Overflow Soft Trap (DOOVR)

Interrupciones por trampa de Hardware:

.- OSCILLATOR FAILURE TRAP (HARD TRAP, LEVEL 15)

.-ADDRESS ERROR TRAP (HARD TRAP, LEVEL 14)

.- GENERIC HARD TRAP (SOFT TRAP, LEVEL 13)

Interrupciones de la Familia DSPIC33E/PIC24E

Reset GOTOInstruction

Reset GOTOAddress

Oscillator Fail TrapVector

Address Error TrapVector

Generic HardTrapVector

Stack Error TrapVector

MathError TrapVector

DMAC Error TrapVector

Generic Soft TrapVector

Reserved

InterruptVector 0

InterruptVector 1

:

:

:

InterruptVector 52

InterruptVector 53

InterruptVector 54

:

:

:

InterruptVector 116

InterruptVector 117

InterruptVector 118

InterruptVector 119

InterruptVector 120

:

:

:

InterruptVector 244

0x000000

0x000002

0x000004

0x000006

0x000008

0x00000A

0x00000C

0x00000E

0x000010

0x000012

0x000014

0x000016

:

:

:

0x00007C

0x00007E

0x000080

:

:

:

0x0000FC

0x0000FE

0x000100

0x000102

0x000104

:

:

:

0x0001FC

IVT

Mas

prioritario

Menos

prioritario

Interrupciones de la Familia DSPIC33E/PIC24E

Operacin de la Interrupcin

Todas las banderas de eventos de interrupcin se muestrean durante cadaciclo de instruccin.

Unasolicitud de interrupcin pendiente (IRQ) se indicamediante el bit de bandera= 1 en un

registro IFSx. LaIRQ provocaunainterrupcin si el bit correspondiente en el registro de

habilitacin de interrupcin (IECx) estactiva. Durante el resto del ciclo de instruccin en la

que se muestrealaIRQ, se evalan las prioridades de todos las solicitudes pendientes de

interrupcin.

Ningunainstruccin se cancelacuando laCPU responde alaIRQ. Cuando se muestrealaIRQ, la

instruccin en curso se completaantes de que se ejecute larutinade servicio de interrupcin

(ISR).

Si hay un IRQ pendiente en el software del usuario con un nivel de prioridad mayor que el nivel

de prioridad actual de procesador, indicado por los bits IPL <2:0> en el registro de estado (SR

<7:5>), se presentaunainterrupcin al procesador. El procesador continuacin, guardala

siguiente informacin en lapilade software:

Valor de PC Actual

Byte bajo del registro de estado del procesador (SRL)

Bit de estado IPL3 (CORCON <3>)

Formato Activo de lapila(CORCON <2>)

Interrupciones de la Familia DSPIC33E/PIC24E

Estos tres valores permiten retornar ladireccin de retorno del PC, bits de estado del MCU y

el nivel actual de prioridad del procesador que se guardan automticamente.

Despus de que estainformacin se guardaen lapila, laCPU escribe el nivel de prioridad de la

interrupcin aatender en las bits IPL <2:0> . Estaaccin desabilitatodas las interrupciones de

prioridad igual o menor hastaque el ISR se terminacon lainstruccin RETFIE.

Operacin de la pila en un evento de interrupcin

Interrupciones de la Familia DSPIC33E/PIC24E

Fuente de Interrupcin

Vector

# IRQ #

Direccin en el IVT

Localizacin del bit de Interrupcin

Solicitud Habilitacin Prioridad

Ordende Prioridad mas alto

INT0 External Interrupt 0 8 0 0x000014 IFS0<0> IEC0<0> IPC0<2:0>

IC1 Input Capture 1 9 1 0x000016 IFS0<1> IEC0<1> IPC0<6:4>

OC1 Output Compare 1 10 2 0x000018 IFS0<2> IEC0<2> IPC0<10:8>

T1 Timer1 11 3 0x00001A IFS0<3> IEC0<3> IPC0<14:12>

DMA0 DMA Channel 0 12 4 0x00001C IFS0<4> IEC0<4> IPC1<2:0>

IC2 Input Capture 2 13 5 0x00001E IFS0<5> IEC0<5> IPC1<6:4>

OC2 Output Compare 2 14 6 0x000020 IFS0<6> IEC0<6> IPC1<10:8>

T2 Timer2 15 7 0x000022 IFS0<7> IEC0<7> IPC1<14:12>

T3 Timer3 16 8 0x000024 IFS0<8> IEC0<8> IPC2<2:0>

SPI1E SPI1 Error 17 9 0x000026 IFS0<9> IEC0<9> IPC2<6:4>

SPI1 SPI1 Transfer Done 18 10 0x000028 IFS0<10> IEC0<10> IPC2<10:8>

U1RX UART1 Receiver 19 11 0x00002A IFS0<11> IEC0<11> IPC2<14:12>

U1TX UART1 Transmitter 20 12 0x00002C IFS0<12> IEC0<12> IPC3<2:0>

AD1 ADC1 Convert Done 21 13 0x00002E IFS0<13> IEC0<13> IPC3<6:4>

DMA1 DMA Channel 1 22 14 0x000030 IFS0<14> IEC0<14> IPC3<10:8>

NVM NVM Write Complete 23 15 0x000032 IFS0<15> IEC0<15> IPC3<14:12>

SI2C1 I2C1 Slave Event 24 16 0x000034 IFS1<0> IEC1<0> IPC4<2:0>

MI2C1 I2C1 Master Event 25 17 0x000036 IFS1<1> IEC1<1> IPC4<6:4>

CM Comparator Combined Event 26 18 0x000038 IFS1<2> IEC1<2> IPC4<10:8>

CN Input Change Interrupt 27 19 0x00003A IFS1<3> IEC1<3> IPC4<14:12>

INT1 External Interrupt 1 28 20 0x00003C IFS1<4> IEC1<4> IPC5<2:0>

AD2 ADC2 Convert Done 29 21 0x00003E IFS1<5> IEC1<5> IPC5<6:4>

IC7 Input Capture 7 30 22 0x000040 IFS1<6> IEC1<6> IPC5<10:8>

Interrupciones de la Familia DSPIC33E/PIC24E

IC8 Input Capture 8 31 23 0x000042 IFS1<7> IEC1<7> IPC5<14:12>

DMA2 DMA Channel 2 32 24 0x000044 IFS1<8> IEC1<8> IPC6<2:0>

OC3 Output Compare 3 33 25 0x000046 IFS1<9> IEC1<9> IPC6<6:4>

OC4 Output Compare 4 34 26 0x000048 IFS1<10> IEC1<10> IPC6<10:8>

T4 Timer4 35 27 0x00004A IFS1<11> IEC1<11> IPC6<14:12>

T5 Timer5 36 28 0x00004C IFS1<12> IEC1<12> IPC7<2:0>

INT2 External Interrupt 2 37 29 0x00004E IFS1<13> IEC1<13> IPC7<6:4>

U2RX UART2 Receiver 38 30 0x000050 IFS1<14> IEC1<14> IPC7<10:8>

U2TX UART2 Transmitter 39 31 0x000052 IFS1<15> IEC1<15> IPC7<14:12>

SPI2E SPI2 Error 40 32 0x000054 IFS2<0> IEC2<0> IPC8<2:0>

SPI2 SPI2 Transfer Done 41 33 0x000056 IFS2<1> IEC2<1> IPC8<6:4>

C1RX CAN1 RX Data Ready 42 34 0x000058 IFS2<2> IEC2<2> IPC8<10:8>

C1 CAN1 Event 43 35 0x00005A IFS2<3> IEC2<3> IPC8<14:12>

DMA3 DMA Channel 3 44 36 0x00005C IFS2<4> IEC2<4> IPC9<2:0>

IC3 Input Capture 3 45 37 0x00005E IFS2<5> IEC2<5> IPC9<6:4>

IC4 Input Capture 4 46 38 0x000060 IFS2<6> IEC2<6> IPC9<10:8>

IC5 Input Capture 5 47 39 0x000062 IFS2<7> IEC2<7> IPC9<14:12>

IC6 Input Capture 6 48 40 0x000064 IFS2<8> IEC2<8> IPC10<2:0>

OC5 Output Compare 5 49 41 0x000066 IFS2<9> IEC2<9> IPC10<6:4>

OC6 Output Compare 6 50 42 0x000068 IFS2<10> IEC2<10> IPC10<10:8>

OC7 Output Compare 7 51 43 0x00006A IFS2<11> IEC2<11> IPC10<14:12>

OC8 Output Compare 8 52 44 0x00006C IFS2<12> IEC2<12> IPC11<2:0>

PMP Parallel Master Port 53 45 0x00006E IFS2<13> IEC2<13> IPC11<6:4>

DMA4 DMA Channel 4 54 46 0x000070 IFS2<14> IEC2<14> IPC11<10:8>

T6 Timer6 55 47 0x000072 IFS2<15> IEC2<15> IPC11<14:12>

T7 Timer7 56 48 0x000074 IFS3<0> IEC3<0> IPC12<2:0>

Interrupciones de la Familia DSPIC33E/PIC24E

SI2C2 I2C2 Slave Event 57 49 0x000076 IFS3<1> IEC3<1> IPC12<6:4>

MI2C2 I2C2 Master Event 58 50 0x000078 IFS3<2> IEC3<2> IPC12<10:8>

T8 Timer8 59 51 0x00007A IFS3<3> IEC3<3> IPC12<14:12>

T9 Timer9 60 52 0x00007C IFS3<4> IEC3<4> IPC13<2:0>

INT3 External Interrupt 3 61 53 0x00007E IFS3<5> IEC3<5> IPC13<6:4>

INT4 External Interrupt 4 62 54 0x000080 IFS3<6> IEC3<6> IPC13<10:8>

C2RX CAN2 RX Data Ready 63 55 0x000082 IFS3<7> IEC3<7> IPC13<14:12>

C2 CAN2 Event 64 56 0x000084 IFS3<8> IEC3<8> IPC14<2:0>

PSEM PWM Special Event

Match(1)

65 57 0x000086 IFS3<9> IEC3<9> IPC14<6:4>

QEI1 QEI1 Position Counter

Compare(1)

66 58 0x000088 IFS3<10> IEC3<10> IPC14<10:8>

DCIE DCI Fault Interrupt 67 59 0x00008A IFS3<11> IEC3<11> IPC14<14:12>

DCI DCI Transfer Done 68 60 0x00008C IFS3<12> IEC3<12> IPC15<2:0>

DMA5 DMA Channel 5 69 61 0x00008E IFS3<13> IEC3<13> IPC15<6:4>

RTC Real-Time Clock and

Calendar

70 62 0x000090 IFS3<14> IEC3<14> IPC15<10:8>

Reserved 71-72 63-64 0x000092-0x000094

U1E UART1 Error Interrupt 73 65 0x000096 IFS4<1> IEC4<1> IPC16<6:4>

U2E UART2 Error Interrupt 74 66 0x000098 IFS4<2> IEC4<2> IPC16<10:8>

CRC CRC Generator Interrupt 75 67 0x00009A IFS4<3> IEC4<3> IPC16<14:12>

DMA6 DMA Channel 6 76 68 0x00009C IFS4<4> IEC4<4> IPC17<2:0>

DMA7 DMA Channel 7 77 69 0x00009E IFS4<5> IEC4<5> IPC17<6:4>

C1TX CAN1 TX Data Request 78 70 0x0000A0 IFS4<6> IEC4<6> IPC17<10:8>

C2TX CAN2 TX Data Request 79 71 0x0000A2 IFS4<7> IEC4<7> IPC17<14:12>

Reserved 80 72 0x0000A4

Interrupciones de la Familia DSPIC33E/PIC24E

PSESM PWM Secondary Special

Event Match(1)

81 73 0x0000A6 IFS4<9> IEC4<9> IPC18<6:4>

Reserved 82 74 0x0000A8

QEI2 QEI2 Position Counter

Compare(1)

83 75 0x0000AA IFS4<11> IEC4<11> IPC18<14:12>

Reserved 84-88 76-80 0x0000AC-0x0000B4

U3E UART3 Error Interrupt 89 81 0x0000B6 IFS5<1> IEC5<1> IPC20<6:4>

U3RX UART3 Receiver 90 82 0x0000B8 IFS5<2> IEC5<2> IPC20<10:8>

U3TX UART3 Transmitter 91 83 0x0000BA IFS5<3> IEC5<3> IPC20<14:12>

Reserved 92-93 84-85 0x0000BC-0x0000BE

USB1 USB OTG Interrupt(2) 94 86 0x0000C0 IFS5<6> IEC5<6> IPC21<10:8>

U4E UART4 Error Interrupt 95 87 0x0000C2 IFS5<7> IEC5<7> IPC21<14:12>

U4RX UART4 Receiver 96 88 0x0000C4 IFS5<8> IEC5<8> IPC22<2:0>

U4TX UART4 Transmitter 97 89 0x0000C6 IFS5<9> IEC5<9> IPC22<6:4>

SPI3E SPI3 Error 98 90 0x0000C8 IFS5<10> IEC5<10> IPC22<10:8>

SPI3 SPI3 Transfer Done 99 91 0x0000CA IFS5<11> IEC5<11> IPC22<14:12>

OC9 Output Compare 9 100 92 0x0000CC IFS5<12> IEC5<12> IPC23<2:0>

IC9 Input Capture 9 101 93 0x0000CE IFS5<13> IEC5<13> IPC23<6:4>

PWM1 PWM Generator 1(1) 102 94 0x0000D0 IFS5<14> IEC5<14> IPC23<10:8>

PWM2 PWM Generator 2(1) 103 95 0x0000D2 IFS5<15> IEC5<15> IPC23<14:12>

PWM3 PWM Generator 3(1) 104 96 0x0000D4 IFS6<0> IEC6<0> IPC24<2:0>

PWM4 PWM Generator 4(1) 105 97 0x0000D6 IFS6<1> IEC6<1> IPC24<6:4>

PWM5 PWM Generator 5(1) 106 98 0x0000D8 IFS6<2> IEC6<2> IPC24<10:8>

PWM6 PWM Generator 6(1) 107 99 0x0000DA IFS6<3> IEC6<3> IPC24<14:12>

PWM7 PWM Generator 7(1) 108 100 0x0000DC IFS6<4> IEC6<4> IPC25<2:0>

Reserved 109-125 101-117 0x0000DE-0x0000FC

Interrupciones de la Familia DSPIC33E/PIC24E

DMA8 DMA Channel 8 126 118 0x000100 IFS7<6> IEC7<6> IPC29<10:8>

DMA9 DMA Channel 9 127 119 0x000102 IFS7<7> IEC7<7> IPC29<14:12>

DMA10 DMA Channel 10 128 120 0x000104 IFS7<8> IEC7<8> IPC30<2:0>

DMA11 DMA Channel 11 129 121 0x000106 IFS7<9> IEC7<9> IPC30<6:4>

SPI4E SPI4 Error 130 122 0x000108 IFS7<10> IEC7<10> IPC30<10:8>

SPI4 SPI4 Transfer Done 131 123 0x00010A IFS7<11> IEC7<11> IPC30<14:12>

OC10 Output Compare 10 132 124 0x00010C IFS7<12> IEC7<12> IPC31<2:0>

IC10 Input Capture 10 133 125 0x00010E IFS7<13> IEC7<13> IPC31<6:4>

OC11 Output Compare11 134 126 0x000110 IFS7<14> IEC7<14> IPC31<10:8>

IC11 Input Capture 11 135 127 0x000112 IFS7<15> IEC7<15> IPC31<14:12>

OC12 Output Compare 12 136 128 0x000114 IFS8<0> IEC8<0> IPC32<2:0>

IC12 Input Capture 12 137 129 0x000116 IFS8<1> IEC8<1> IPC32<6:4>

DMA12 DMA Channel 12 138 130 0x000118 IFS8<2> IEC8<2> IPC32<10:8>

DMA13 DMA Channel 13 139 131 0x00011A IFS8<3> IEC8<3> IPC32<14:12>

DMA14 DMA Channel 14 140 132 0x00011C IFS8<4> IEC8<4> IPC33<2:0>

Reserved 141 133 0x00011E

OC13 Output Compare 13 142 134 0x000120 IFS8<6> IEC8<6> IPC33<10:8>

IC13 Input Capture 13 143 135 0x000122 IFS8<7> IEC8<7> IPC33<14:12>

OC14 Output Compare14 144 136 0x000124 IFS8<8> IEC8<8> IPC34<2:0>

IC14 Input Capture 14 145 137 0x000126 IFS8<9> IEC8<9> IPC34<6:4>

OC15 Output Compare 15 146 138 0x000128 IFS8<10> IEC8<10> IPC34<10:8>

IC15 Input Capture 15 147 139 0x00012A IFS8<11> IEC8<11> IPC34<14:12>

OC16 Output Compare 16 148 140 0x00012C IFS8<12> IEC8<12> IPC35<2:0>

IC16 Input Capture 16 149 141 0x00012E IFS8<13> IEC8<13> IPC35<6:4>

ICD ICD Application 150 142 0x000130 IFS8<14> IEC8<14> IPC35<10:8>

Reserved 151-245 142-237 0x000130-0x0001FE

Interrupciones de la Familia DSPIC33E/PIC24E

REGISTRO DE ESTADO DEL CPU (SR)

Byte superior

Bit 15 Bit 8

Bits <15:8>: No usado por el modulo de Interrupciones. Ir a la

Seccin 2 CPU.

--- --- --- --- --- --- --- ---

Interrupciones de la Familia DSPIC33E/PIC24E

REGISTRO DE ESTADO DEL CPU (SR)

Byte Inferior

Bit 7 Bit 0

IPL <7:5>: Bits de Estado de Niveles de Prioridad de la Interrupcin por

CPU.

111 =Nivel de prioridad de interrupcin CPU es 7 (15). Interrupciones de

usuario deshabilitada

110 =Nivel de prioridad de interrupcin CPU es 6 (14)

101 =Nivel de prioridad de interrupcin CPU es 5 (13)

100 =Nivel de prioridad de interrupcin CPU es 4 (12)

011 =Nivel de prioridad de interrupcin CPU es 3 (11)

010 =Nivel de prioridad de interrupcin CPU es 2 (10)

001 =Nivel de prioridad de interrupcin CPU es 1 (9)

000 =Nivel de prioridad de interrupcin CPU es 0 (8)

Bits <4:0>: No usado por el modulo de Interrupciones.

IPL <7:5> --- --- --- --- ---

Interrupciones de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE NUCLEO (CORCON)

Byte superior

Bit 15 Bit 8

VAR <15>: Bit de control de procesamiento de Excepcin por

Latencia Variable.

1 =Procesamiento por Excepcin de Latencia Variable

0 =Procesamiento por Excepcin de Latencia Fija

Bits <14:8>: No usado por el modulo de Interrupciones. Ir a la

Seccin 2 CPU.

VAR --- --- --- --- --- --- ---

Interrupciones de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE NUCLEO (CORCON)

Byte Inferior

Bit 7 Bit 0

Bits <7:4>: No usado por el modulo de Interrupciones.

IPL3: Bit de estado de nivel de interrupcin de prioridad del CPU

1 =nivel de prioridad de interrupcin de la CPU es superior a 7

0 =nivel de prioridad de interrupcin de la CPU es 7 o menos

Nota 1: El bit IPL3 se concatena con los bits <IPL 2:0> (SR <7:5>)

para formar el nivel de prioridad de interrupcin de la CPU.

Bits <2:0>: No usado por el modulo de Interrupciones.

--- --- --- --- IPL3 --- --- ---

Interrupciones de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE INTERRUPCION 1 (INTCON1)

Byte superior

Bit 15 Bit 8

NSRDIS<15>: Bit Interrupcin de desactivacin de anidacin.

1 =Anidacin de interrupcin est desactivado.

0 =Anidacin de interrupcin est habilitado.

OVAERR<14>: Bit de estado de trampa de desbordamiento de Acumulador A

1 =Trampa fue causada por el desbordamiento del Acumulador A

0 =Trampa no fue causada por el desbordamiento del Acumulador A.

NSTDIS OVAERR OVBERR COVAERR COVBERR OVATE OVBTE COVTE

Interrupciones de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE INTERRUPCION 1 (INTCON1)

Byte superior

Bit 15 Bit 8

OVBERR<13>: Bit de estado de trampa de desbordamiento de Acumulador B.

1 =Trampa fue causada por el desbordamiento del Acumulador B.

0 =Trampa no fue causada por el desbordamiento del Acumulador B.

COVAERR<12>: Bit de estado de trampa de desbordamiento catastrfico de

Acumulador A.

1 =Trampa fue causada por el desbordamiento catastrfico del Acumulador A.

0 =Trampa no fue causada por el desbordamiento catastrfico del Acumulador

A.

NSTDIS OVAERR OVBERR COVAERR COVBERR OVATE OVBTE COVTE

Interrupciones de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE INTERRUPCION 1 (INTCON1)

Byte superior

Bit 15 Bit 8

COVBERR<11>: Bit de estado de trampa de desbordamiento catastrfico de

Acumulador B.

1 =Trampa fue causada por el desbordamiento catastrfico del Acumulador B.

0 =Trampa no fue causada por el desbordamiento catastrfico del Acumulador

B.

OVATE<10>: Bit de habilitacin de trampa por desbordamiento del Acumulador

A

1 =Habilita Trampa desbordamiento del acumulador A

0 =Desabilita Trampa desbordamiento del acumulador A

NSTDIS OVAERR OVBERR COVAERR COVBERR OVATE OVBTE COVTE

Interrupciones de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE INTERRUPCION 1 (INTCON1)

Byte superior

Bit 15 Bit 8

OVBTE<9>: Bit de habilitacin de trampa por desbordamiento del Acumulador

B

1 =Habilita Trampa desbordamiento del acumulador B

0 =Desabilita Trampa desbordamiento del acumulador B

COVTE<8>: Bit de habilitacin Trampa de desbordamiento catastrfico

1 =Habilita Trampa de desbordamiento catastrfico de acumulador A o B

0 =Desabilita Trampa de desbordamiento catastrfico de acumulador A o B

NSTDIS OVAERR OVBERR COVAERR COVBERR OVATE OVBTE COVTE

Interrupciones de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE INTERRUPCION 1 (INTCON1)

Byte inferior

Bit 7 Bit 0

SFTACERR<7>: Bit de estado del Acumulador de Error de Cambio

1 =Trampa por Error Matemtico se debi a un cambio invalido del Acumulador

0 =Trampa por Error Matemtico no fue causado por un cambio invalido del

Acumulador.

DIV0ERR<6>: Bit de estado por error de Dividir por cero.

1 =Trampa de error causado por divisin por cero

0 =Trampa de error no fue causado por divisin por cero.

SFTACERR DIV0ERR DMACERR MATHERR ADDRERR STKERR OSCFAIL ----

Interrupciones de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE INTERRUPCION 1 (INTCON1)

Byte inferior

Bit 7 Bit 0

DMACERR<5>: Bit de estado de trampa de Error DMAC

1 =Trampa DMAC se ha producido.

0 =Trampa DMAC no se ha producido.

MATHERR<4>: Bit de estado por Error Matemtico.

1 =Trampa de error matemtico se ha producido.

0 =Trampa de error matemtico no se ha producido.

ADDRERR<3>: Bit de estado de trampa por error de direccin.

1 =Trampa de error de direccin se ha producido.

0 =Trampa de error de direccin no se ha producido.

SFTACERR DIV0ERR DMACERR MATHERR ADDRERR STKERR OSCFAIL ----

Interrupciones de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE INTERRUPCION 1 (INTCON1)

Byte inferior

Bit 7 Bit 0

STKERR<2>: Bit de estado de trampa de Error de Pilas.

1 =Trampa por error de pila se ha producido.

0 =Trampa por error de pila no se ha producido.

OSCFAIL<1>: Bit de estado por Falla de Oscilador.

1 =Trampa de falla por oscilador se ha producido.

0 =Trampa de falla por oscilador no se ha producido.

Bit<0>: No implementado. Ledo como 0.

SFTACERR DIV0ERR DMACERR MATHERR ADDRERR STKERR OSCFAIL ----

Interrupciones de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE INTERRUPCION 2 (INTCON2)

Byte superior

Bit 15 Bit 8

GIE<15>: Bit de Habilitacin Global de las Interrupciones.

1 =Interrupciones asociadas a Modulo de Interrupcin son habilitadas.

0 =Interrupciones asociadas a Modulo de Interrupcin estn desabilitadas.

DISI<14>: Bit de estado de la instruccin DISI

1 =instruccin DISI est activo

0 =DISI no est activo

SWTRAP<13>: Bit de estado de Trampa por software.

1 =Trampa por Software esta Habilitada

0 =Trampa por Software esta Deshabilitada

Bits<12:8>: No estn implementados. Ledos como 0.

GIE DISI SWTRAP --- --- --- --- ---

Interrupciones de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE INTERRUPCION 2 (INTCON2)

Byte inferior

Bit 7 Bit 0

Bits<7:5>: No estn implementados. Ledos como 0.

INT4EP<4>: Bit de Seleccin de polaridad de flanco en la Interrupcin

externa 4.

1 =Interrupcin por flanco negativo.

0 =Interrupcin por flanco positivo.

INT3EP<3>: Bit de Seleccin de polaridad de flanco en la Interrupcin

externa 3.

1 =Interrupcin por flanco negativo.

0 =Interrupcin por flanco positivo.

--- --- --- INT4EP INT3EP INT2EP INT1EP INT0EP

Interrupciones de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE INTERRUPCION 2 (INTCON2)

Byte inferior

Bit 7 Bit 0

INT2EP<2>: Bit de Seleccin de polaridad de flanco en la Interrupcin externa 2.

1 =Interrupcin por flanco negativo.

0 =Interrupcin por flanco positivo.

INT1EP<1>: Bit de Seleccin de polaridad de flanco en la Interrupcin externa 1.

1 =Interrupcin por flanco negativo.

0 =Interrupcin por flanco positivo.

INT0EP<0>: Bit de Seleccin de polaridad de flanco en la Interrupcin externa 0.

1 =Interrupcin por flanco negativo.

0 =Interrupcin por flanco positivo.

--- --- --- INT4EP INT3EP INT2EP INT1EP INT0EP

Interrupciones de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE INTERRUPCION 3 (INTCON3)

Byte inferior

Bit 7 Bit 0

Bits<15:8>: No implementados. Ledos como 0.

UAE<6>: Bit de estado de trampa por error de direccin USB.

1 =Trampa por error de direccin USB se ha producido.

0 =Trampa por error de direccin USB no se ha producido.

DAE<5>: Bit de estado de trampa por error de direccin DMA.

1 =Trampa por error de direccin DMA se ha producido.

0 =Trampa por error de direccin DMA no se ha producido.

--- UAE DAE DOOVR --- --- --- ---

Interrupciones de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE INTERRUPCION 3 (INTCON3)

Byte inferior

Bit 7 Bit 0

DOOVR<4>: Bit de estado de trampa por desbordamiento de pila soft .

1 =Trampa por error de desbordamiento de la pila soft se ha producido.

0 =Trampa por error de desbordamiento de la pila soft no se ha producido.

Bits<3:0>: No implementados. Ledos como 0.

--- UAE DAE DOOVR --- --- --- ---

Interrupciones de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE INTERRUPCION 4 (INTCON4)

Byte inferior

Bit 15 Bit 0

Bits<15:1>: No implementados. Ledos como 0.

DOOVR<4>: Bit de estado de trampa Generacin de Software Hard.

1 =Trampa por Generacin de Software Hard se ha producido.

0 =Trampa por Generacin de Software Hard no se ha producido.

BITS <15:1> SGHT

Interrupciones de la Familia DSPIC33E/PIC24E

REGISTRO DE ESTADO DE BANDERAS DE INTERRUPCIONES (IFSx)

Registro 16 Bits

Bit 15 Bit 8

Bit 7 Bit 0

Bits<15:0>: Bits de estado de la Banderas de Interrupcin.

1 =Peticin Interrupcin se ha producido.

0 =Peticin Interrupcin no se ha producido

IFS15 IFS14 IFS13 IFS12 IFS11 IFS10 IFS9 IFS8

IFS15 IFS14 IFS13 IFS12 IFS11 IFS10 IFS9 IFS8

Interrupciones de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE HABILITACION DE INTERRUPCIONES

(IECx)

Registro 16 Bits

Bit 15 Bit 8

Bit 7 Bit 0

Bits<15:0>: Bits de control de habilitacin de Interrupcin.

1 =Peticin Interrupcin habilitado.

0 =Peticin Interrupcin desabilitado.

IEC15 IEC14 IEC13 IEC12 IEC11 IEC10 IEC9 IEC8

IEC7 IEC6 IEC5 IEC4 IEC3 IEC2 IEC1 IEC0

Interrupciones de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE PRIORIDAD DE INTERRUPCIONES (IPCx)

Byte Superior

Bit 15 Bit 8

Bit<15>: No implementados. Ledos como 0.

IP3<2:0>: Bits de Prioridad de Interrupcin.

111 = Interrupcin es de prioridad 7 (Mxima prioridad de interrupcin).

001 =Interrupcin es de prioridad 1

000 =Fuente de Interrupcin desactivada.

Bit<11>: No implementados. Ledos como 0.

IP3<2:0>: Bits de Prioridad de Interrupcin.

Estos Bits tienen la misma definicin que los bits <14:12>.

--- IP3<2:0> --- IP2<2:0>

Interrupciones de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE PRIORIDAD DE INTERRUPCIONES

(IPCx)

Byte inferior

Bit 7 Bit 0

Bit<7>: No implementados. Ledos como 0.

IP1<2:0>: Bits de Prioridad de Interrupcin.

Estos Bits tienen la misma definicin que los bits <14:12>.

Bit<4>: No implementados. Ledos como 0.

IP0<2:0>: Bits de Prioridad de Interrupcin.

Estos Bits tienen la misma definicin que los bits <14:12>.

--- IP1<2:0> --- IP0<2:0>

Interrupciones de la Familia DSPIC33E/PIC24E

REGISTRO DE ESTADO Y CONTROL DE INTERRUPCIONES

(INTTREG)

Byte superior

Bit 15 Bit 8

Bit<15:12>: No implementados. Ledos como 0.

ILR<3:0>: Bits de Nivel de Prioridad de Nueva Interrupcin de CPU.

1111 =Interrupcin de CPU es de prioridad 15.

0001 =Interrupcin de CPU es de prioridad 1.

0000 =Interrupcin de CPU es de prioridad 0.

--- --- --- --- ILR<3:0>

Interrupciones de la Familia DSPIC33E/PIC24E

REGISTRO DE ESTADO Y CONTROL DE INTERRUPCIONES

(INTTREG)

Byte inferior

Bit 7 Bit 0

VECNUM<7:0>: Bits de Vector de numero de Interrupcin pendiente.

11111111 =Numero de Vector de Interrupcin pendiente es 263.

00000001 =Numero de Vector de Interrupcin pendiente es 9.

00000000 =Numero de Vector de Interrupcin pendiente es 8.

VECNUM<7:0>

Interrupciones de la Familia DSPIC33E/PIC24E

Nombr e

Fi l a

Di r ec c i n Bi t 15 Bi t 14 Bi t 13 Bi t 12 Bi t 11 Bi t 10 Bi t 9 Bi t 8 Bi t 7 Bi t 6 Bi t 5 Bi t 4 Bi t 3 Bi t 2 Bi t 1 Bi t 0 Reset

I FS0 800 NVMI F DMA1I F AD1I F U1TXI F U1RXI F SPI 1I F SPI 1EI F T3I F T2I F OC2I F I C2I F DMA0I F T1I F OC1I F I C1I F I NT0I F 0

I FS1 802 U2TXI F U2RXI F I NT2I F T5I F T4I F OC4I F OC3I F DMA2I F I C8I F I C7I F AD2I F I NT1I F CNI F CMI F MI 2C1I F SI 2C1I F 0

I FS2 804 T6I F DMA4I F PMPI F OC8I F OC7I F OC6I F OC5I F I C6I F I C5I F I C4I F I C3I F DMA3I F C1I F C1RXI F SPI 2I F SPI 2EI F 0

I FS3 806 RTCI F DMA5I F DCI I F DCI EI F QEI 1I F PSEMI F C2I F C2RXI F I NT4I F I NT3I F T9I F T8I F MI 2C2I F SI 2C2I F T7I F 0

I FS4 808 QEI 2I F PSESMI F C2TXI F C1TXI F DMA7I F DMA6I F CRCI F U2EI F U1EI F 0

I FS5 80A PWM2I F PWM1I F I C9I F OC9I F SPI 3I F SPI 3EI F U4TXI F U4RXI F U4EI F USB1I F U3TXI F U3RXI F U3EI F 0

I FS6 80C PWM4I F PWM3I F 0

I FS7 80E I C11I F OC11I F I C10I F OC10I F SPI 4I F SPI 4EI F DMA11I F DMA10I F DMA9I F DMA8I F 0

I FS8 810 I CDI F I C16I F OC16I F I C15I F OC15I F I C14I F OC14I F I C13I F OC13I F DMA14I F DMA13I F DMA12I F I C12I F OC12I F 0

I EC0 820 NVMI E DMA1I E AD1I E U1TXI E U1RXI E SPI 1I E SPI 1EI E T3I E T2I E OC2I E I C2I E DMA0I E T1I E OC1I E I C1I E I NT0I E 0

I EC1 822 U2TXI E U2RXI E I NT2I E T5I E T4I E OC4I E OC3I E DMA2I E I C8I E I C7I E AD2I E I NT1I E CNI E CMI E MI 2C1I E SI 2C1I E 0

I EC2 824 T6I E DMA4I E PMPI E OC8I E OC7I E OC6I E OC5I E I C6I E I C5I E I C4I E I C3I E DMA3I E C1I E C1RXI E SPI 2I E SPI 2EI E 0

I EC3 826 RTCI E DMA5I E DCI I E DCI EI E QEI 1I E PSEMI E C2I E C2RXI E I NT4I E I NT3I E T9I E T8I E MI 2C2I E SI 2C2I E T7I E 0

I EC4 828 QEI 2I E PSESMI E C2TXI E C1TXI E DMA7I E DMA6I E CRCI E U2EI E U1EI E 0

I EC5 82A PWM2I E PWM1I E I C9I E OC9I E SPI 3I E SPI 3EI E U4TXI E U4RXI E U4EI E USB1I E U3TXI E U3RXI E U3EI E 0

I EC6 82C PWM4I E PWM3I E 0

I EC7 82E I C11I E OC11I E I C10I E OC10I E SPI 4I E SPI 4EI E DMA11I EDMA10I E DMA9I E DMA8I E 0

I EC8 830 I CDI E I C16I E OC16I E I C15I E OC15I E I C14I E OC14I E I C13I E OC13I E DMA14I EDMA13I EDMA12I E I C12I E OC12I E 0

I PC0 840 T1I P<2:0> OC1I P<2:0> I C1I P<2:0> I NT0I P<2:0> 4444

I PC1 842 T2I P<2:0> OC2I P<2:0> I C2I P<2:0> DMA0I P<2:0> 4444

I PC2 844 U1RXI P<2:0> SPI 1I P<2:0> SPI 1EI P<2:0> T3I P<2:0> 4444

I PC3 846 NVMI P<2:0> DMA1I P<2:0> AD1I P<2:0> U1TXI P<2:0> 4444

I PC4 848 CNI P<2:0> CMI P<2:0> MI 2C1I P<2:0> SI 2C1I P<2:0> 4444

I PC5 84A I C8I P<2:0> I C7I P<2:0> AD2I P<2:0> I NT1I P<2:0> 4444

I PC6 84C T4I P<2:0> OC4I P<2:0> OC3I P<2:0> DMA2I P<2:0> 4444

I PC7 84E U2TXI P<2:0> U2RXI P<2:0> I NT2I P<2:0> T5I P<2:0> 4444

I PC8 850 C1I P<2:0> C1RXI P<2:0> SPI 2I P<2:0> SPI 2EI P<2:0> 4444

I PC9 852 I C5I P<2:0> I C4I P<2:0> I C3I P<2:0> DMA3I P<2:0> 4444

I PC10 854 OC7I P<2:0> OC6I P<2:0> OC5I P<2:0> I C6I P<2:0> 4444

I PC11 856 T6I P<2:0> DMA4I P<2:0> PMPI P<2:0> OC8I P<2:0> 4444

I PC12 858 T8I P<2:0> MI 2C2I P<2:0> SI 2C2I P<2:0> T7I P<2:0> 4444

I PC13 85A C2RXI P<2:0> I NT4I P<2:0> I NT3I P<2:0> T9I P<2:0> 4444

I PC14 85C DCI EI P<2:0> QEI 1I P<2:0> PSEMI P<2:0> C2I P<2:0> 4444

I PC15 85E RTCI P<2:0> DMA5I P<2:0> DCI I P<2:0> 444

I PC16 860 CRCI P<2:0> U2EI P<2:0> U1EI P<2:0> 4440

Mapa de r egi st r os del c ont r ol ador de i nt er r upc i ones sol o par a

l os dsPI C33EPXXXMU806

Interrupciones de la Familia DSPIC33E/PIC24E

I PC17 862 C2TXI P<2:0> C1TXI P<2:0> DMA7I P<2:0> DMA6I P<2:0> 4444

I PC18 864 QEI 2I P<2:0> PSESMI P<2:0> 4040

I PC20 868 U3TXI P<2:0> U3RXI P<2:0> U3EI P<2:0> 4440

I PC21 86A U4EI P<2:0> USB1I P<2:0> 4400

I PC22 86C SPI 3I P<2:0> SPI 3EI P<2:0> U4TXI P<2:0> U4RXI P<2:0> 4444

I PC23 86E PWM2I P<2:0> PWM1I P<2:0> I C9I P<2:0> OC9I P<2:0> 4444

I PC24 870 PWM4I P<2:0> PWM3I P<2:0> 44

I PC29 87A DMA9I P<2:0> DMA8I P<2:0> 4400

I PC30 87C SPI 4I P<2:0> SPI 4EI P<2:0> DMA11I P<2:0> DMA10I P<2:0> 4444

I PC31 87E I C11I P<2:0> OC11I P<2:0> I C10I P<2:0> OC10I P<2:0> 4444

I PC32 880 DMA13I P<2:0> DMA12I P<2:0> I C12I P<2:0> OC12I P<2:0> 4444

I PC33 882 I C13I P<2:0> OC13I P<2:0> DMA14I P 4404

I PC34 884 I C15I P<2:0> OC15I P<2:0> I C14I P<2:0> OC14I P<2:0> 4444

I PC35 886 I CDI P<2:0> I C16I P<2:0> OC16I P<2:0> 444

Nombr e

Fi l a

Di r ec c i

n

Bi t 15 Bi t 14 Bi t 13 Bi t 12 Bi t 11 Bi t 10 Bi t 9 Bi t 8 Bi t 7 Bi t 6 Bi t 5 Bi t 4 Bi t 3 Bi t 2 Bi t 1 Bi t 0 Reset

Interrupciones de la Familia DSPIC33E/PIC24E

Ejemplo de aplicacin para las interrupciones

Se desearealizar unaaplicacin mediante el dsPIC33EP256MU806, que permitaal

usuario visualizar en unainterfaz grficaunaopcin seleccionadautilizando imgenes

o mensajes.

En larealizacin de estaaplicacin se emplearon las interrupciones externas del

dsPIC33EP256MU806, paraeso se habilit lainterrupcin externa0, lacual se

encuentrael pin 0 del puerto D, las siguientes interrupcin en habilitarse fueron las

interrupciones externa1 y lainterrupcin externa2 respectivamente, gracias ala

multiplexacionque posee este dsPIC, dichas interrupciones pueden ser asignadas a

cualquier pin RPI, en nuestro caso configuramos lainterrupcin externa1 en el

RPI75 y lainterrupcin externa2 en el RPI74, Esto se logramediante los registros

RPINR0 y RPINR1.

Tambin se empleo unainterfaz grfica, lacual tuvo como funcin mostrar la

activacin de cualquierade las tres interrupciones, mostrando en lamismauna

imagen animadadependiendo lainterrupcin externaactivada.

Parael correcto manejo de lainterfaz grficase emple las libreras GLCD de

mikroC.

Interrupciones de la Familia DSPIC33E/PIC24E

Interrupciones de la Familia DSPIC33E/PIC24E

Interrupciones de la Familia DSPIC33E/PIC24E

Interrupciones de la Familia DSPIC33E/PIC24E

Interrupciones de la Familia DSPIC33E/PIC24E

Interrupciones de la Familia DSPIC33E/PIC24E

/ / Glcdmodule connections

sbitGLCD_D7 at RE1_bit;

sbitGLCD_D6 at RE0_bit;

sbitGLCD_D5 at RF1_bit;

sbitGLCD_D4 at RF0_bit;

sbitGLCD_D3 at RD7_bit;

sbitGLCD_D2 at RD6_bit;

sbitGLCD_D1 at RD5_bit;

sbitGLCD_D0 at RD4_bit;

sbitGLCD_D7_Direction at TRISE1_bit;

sbitGLCD_D6_Direction at TRISE0_bit;

sbitGLCD_D5_Direction at TRISF1_bit;

sbitGLCD_D4_Direction at TRISF0_bit;

sbitGLCD_D3_Direction at TRISD7_bit;

sbitGLCD_D2_Direction at TRISD6_bit;

sbitGLCD_D1_Direction at TRISD5_bit;

sbitGLCD_D0_Direction at TRISD4_bit;

sbitGLCD_CS1 at LATE3_bit;

sbitGLCD_CS2 at LATE2_bit;

sbit GLCD_RS at LATD1_bit;

sbitGLCD_RW at LATD2_bit;

Interrupciones de la Familia DSPIC33E/PIC24E

sbitGLCD_EN at LATD3_bit;

sbitGLCD_RST at LATE4_bit;

sbitGLCD_CS1_Direction at TRISE3_bit;

sbitGLCD_CS2_Direction at TRISE2_bit;

sbitGLCD_RS_Directionat TRISD1_bit;

sbitGLCD_RW_Directionat TRISD2_bit;

sbitGLCD_EN_Directionat TRISD3_bit;

sbitGLCD_RST_Directionat TRISE4_bit;

/ / EndGlcdmodule connections

unsignedshort posicion=0;

voidINT0() org0x14

{ posicion=1;

IFS0bits.INT0IF=0; }

voidINT1() org0x3C

{ posicion=2;

IFS1bits.INT1IF=0; }

voidINT2() org0x4E

{ posicion=3;

IFS1bits.INT2IF=0; }

Interrupciones de la Familia DSPIC33E/PIC24E

voidmain()

{ ANSELC=0; ANSELD=0; ANSELE=0;

CORCONbits.IPL3=0; / / lainterrupcin de laCPU es de nivel 7 o menor

SRbits.IPL=0; / / interrupcin de laCPU es de nivel 0

INTCON1bits.NSTDIS=0; / / interrupcin anidadas activada

INTCON2bits.GIE=1; / / interrupciones habilitadas

IFS0bits.INT0IF=0;

IFS1bits.INT1IF=0;

IFS1bits.INT2IF=0;

INTCON2bits.INT0EP=0; / / flanco positivo

INTCON2bits.INT1EP=0; / / flanco positivo

INTCON2bits.INT2EP=0; / / flanco positivo

IEC0bits.INT0IE=1;

IEC1bits.INT1IE=1;

IEC1bits.INT2IE=1;

RPINR0Bits.INT1R=75; / / asignaINT1 al puerto rpi75

RPINR1Bits.INT2R=74; / / asignaINT2 al puerto rpi74

Glcd_Init();

Glcd_Set_Font(font5x7 , 5, 7, 32);

Glcd_Fill(0);

Interrupciones de la Familia DSPIC33E/PIC24E

while(1)

{ switch(posicion)

{ case 0:

Glcd_Write_Text("Esperando.......", 5, 3, 1);

delay_ms(500);

break;

case 1:

Glcd_Image(perro); delay_ms(500);

Glcd_Image(perro2); delay_ms(500);

break;

case 2:

Glcd_Image(pez1); delay_ms(250);

Glcd_Image(pez3); delay_ms(250);

Glcd_Image(pez5); delay_ms(250);

Glcd_Image(pez7); delay_ms(250);

break;

case 3:

Glcd_Image(falla); delay_ms(500);

Glcd_Image(falla2);delay_ms(500);

break;

} } }

Interrupciones de la Familia DSPIC33E/PIC24E

constcodechar perro[1024] = {

0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 192, 32, 224, 128, 0,

0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0,

0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0,

0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 128, 192, 96, 32, 48, 8, 14, 9, 8, 11, 12, 9,

14, 8, 16, 16, 32, 32, 64, 64, 192, 192, 96, 24, 228, 2, 254, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0,

0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0,

0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 128, 64, 48, 24, 12, 6, 3, 7, 6, 0, 0, 0, 0, 0, 224, 240, 248,

252, 134, 246, 135, 254, 254, 252, 0, 0, 0, 0, 0, 3, 7, 12, 252, 7, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0,

0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0,

0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 254, 241, 224, 96, 160, 224, 192, 0, 0, 0, 0, 0, 0, 0, 0, 1, 1, 1,

1, 1, 1, 1, 129, 129, 192, 192, 224, 224, 240, 112, 120, 60, 14, 11, 24, 16, 48, 96, 64, 192, 128, 128, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 192, 32, 16, 208,

48, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0,

0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 1, 3, 6, 6, 254, 142, 134, 230, 30, 30, 26, 154, 249, 9, 8, 8, 8,

4, 4, 6, 7, 7, 7, 3, 3, 3, 1, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 1, 1, 3, 2, 4, 12, 24, 16, 48, 16, 140, 67, 48, 12, 3, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0,

0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0,

0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 255, 1, 0, 0, 128, 248, 192, 192,

192, 128, 0, 192, 128, 0, 0, 0, 0, 0, 0, 0, 0, 128, 224, 112, 8, 0, 224, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 255, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0,

0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0,

0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 3, 12, 240, 0, 3, 15, 127, 255,

131, 7, 7, 15, 255, 0, 0, 0, 0, 0, 192, 252, 126, 127, 253, 252, 254, 255, 255, 60, 24, 16, 32, 64, 128, 128, 0, 0, 0, 128, 128, 127, 0, 0, 0, 0, 0, 0, 0,

0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0,

0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 7, 7, 5, 7, 4, 4, 4, 4, 7, 14, 17,

29, 17, 16, 28, 16, 24, 12, 7, 0, 0, 12, 12, 15, 15, 15, 120

7, 0, 0, 0, 0, 0, 56, 39, 56, 32, 32, 63, 32, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0,

0, 0, 0 };

TEMPORIZADORES

Temporizadores de la Familia DSPIC33E/PIC24E

Temporizadores de la Familia DSPIC33E/PIC24E

INTRODUCCIN

El dsPIC33EP256MU806 cuentacon nueve temporizadores/ contadores de 16 bits, de los cuales

algunos poseen lacaractersticade poder combinarse con el objetivo de formar un

temporizador/ contador de 32 bits , todos los temporizadores de 16 bits tienen el mismo circuito

funcional, y se clasifican en tres tipos:

TimerTipo A (Timer 1)

TimerTipo B (Timer 2, Timer 4, Timer 6 y Timer 8)

TimerTipo C (Timer 3, Timer 5, Timer 7 y Timer 9)

Los timersde Tipo B y C se pueden combinar paraformar un temporizador de 32 bits. Cada

mdulo temporizador es un temporizador / contador de 16-bit que poseen los siguiente registros

de lectura/ escritura:

TMRx: Registro contador de 16 bits del temporizador.

PRx: Registro de periodo de 16 bits del temporizador.

TxCON: Registro de control de 16 bits del temporizador.

Cadamdulo de temporizador tambin tiene estos bits asociados paracontrol de interrupcin:

Bit de habilitacin de Interrupcin del temporizador (TxIE)

Bit de solicitud de Interrupcin del temporizador (TxIF)

Bits de control de prioridad de interrupcin del temporizador (TxIP<2:0>)

Temporizadores de la Familia DSPIC33E/PIC24E

MODOS DE FUNCIONAMIENTO

El mdulo temporizador puede funcionar en uno de los siguientes modos:

El modo Temporizador

El modo Disparo acumulado

El modo Contador Sncrono

El modo Contador Asncrono (Solo timer tipo A)

En los modos Temporizador y Disparo Acumulado, el reloj de entradase derivadel reloj interno

(FCY). En los modos Contador Sncrono y Asncrono, el reloj de entradase derivade laentrada

de reloj externaen el pin TxCK.

Los modos de temporizador se determinan por los siguientes bits:

TCS (TxCON<1>): Bit de control de fuente de reloj del temporizador

TSYNC (TxCON<2>): Bit de control de sincronizacin del temporizador (Solo tipo A)

TGATE (TxCON<6>): Bit de control de habilitacin de disparo acumulado

Nota: Bajo ciertas condiciones cualquier timer puede funcionar como entradade interrupcin

externa

Temporizadores de la Familia DSPIC33E/PIC24E

CONFIGURACION DE MODOS DE FUNCIONAMIENTO DEL TEMPORIZADOR

MODO TCS TGATE (2) TSYNC(1)

TEMPORIZADOR 0 0 X

DISPARO ACUMULADO 0 1 X

CONTADOR SINCRONO 1 X 1

CONTADOR ASINCRONO (3) 1 X 0

1.- TSYNC SOLO ESTA DISPONIBLE EN LOS TIMER TIPO A

2.- TGATE NO FUNCIONA EN LOS MODOS CONTADOR

3.- MODO CONTADOR ASINCRONO SOLO FUNCIONA EN TIMER TIPO A

Nota: El temporizador puedeser utilizadopor otrosperifricos, entre ellos:

.- Mdulode Captura.

.- Mdulode Comparacin.

.- Reloj de TiempoReal.

Temporizadores de la Familia DSPIC33E/PIC24E

REGISTROS DE CONTROL DE LOS TEMPORIZADORES

TxCON: Tipo de registro de control del temporizador TIPO A (x = 1)

TxCON: Tipo de registro de control del temporizador TIPO B (x = 2, 4, 6, 8)

TxCON: Tipo de registro de control del temporizador TIPO C (x = 3, 5, 7, 9)

Adems de los registros anteriores, cadatemporizador tiene los siguientes registros de 16 bits

asociado con l.

PRx: Registro de periodo del temporizador (x = 1 a9)

TMRx: Registro de conteo del temporizador (x = 1 a9)

TMRxHLD: Registros de retencin del temporizador (x = 3, 5, 7 y 9)

Este registro se utilizaen el modo de temporizador de 32 bits paralas operaciones de lectura/

escritura.

Temporizadores de la Familia DSPIC33E/PIC24E

Modo Temporizador

En el modo temporizador, el reloj de entradaal temporizador se derivadel reloj interno

(FCY) dividido por un prescaler programable. Cuando el temporizador estactivado, se

incrementaen uno en cadaflanco ascendente del reloj de entraday generaunainterrupcin al

tener el mismo valor del registro de perodo.

Paraconfigurar el modo de temporizador:

1. Borre el bit de control TCS (TxCON<11>) paraseleccionar lafuente de reloj interno.

2. Borre el bit de control TGATE (TxCON<6>) paradesactivar el modo de operacin de

disparo acumulado.

Configurar el bit TSYNC (TxCON<2>) no tiene ningn efecto porque el reloj interno

siempre estasincronizado.

Temporizadores de la Familia DSPIC33E/PIC24E

Modo Contador Sncrono

En el modo de contador sncrono, el reloj de entradaal temporizador se derivade laentrada

de reloj externadividido por un pre-escalador programable. En este modo, laentradade reloj

externo se sincronizacon el reloj interno del dispositivo. Cuando el temporizador est

activado, se incrementaen uno en cadaflanco ascendente del reloj de entrada, y generauna

interrupcin al igualarse con el registro de perodo.

Paraconfigurar el modo de contador sncrono:

Setear el bit de control TSYNC (TxCON<2>) parahabilitar lasincronizacin del reloj

interno con el externo. ( Solo paratimer tipo A)

Paraun timer tipo B o C, laentradade reloj externo siempre estsincronizada.

Setear el bit de control TCS (TxCON<1>) paraseleccionar lafuente de reloj externa.

Un temporizador funcionando en modo contador de reloj externasincronizadano funciona

en el modo de SLEEP, debido aque el circuito de sincronizacin se apagadurante este modo.

Temporizadores de la Familia DSPIC33E/PIC24E

Modo Contador Asncrono (Solo temporizador tipo A)

El temporizador tipo A puede funcionar en modo contador asncrono, el reloj de entradadel

temporizador se derivade laentradade reloj externa(TxCK) dividido por un prescaler

programable. En este modo, laentradade reloj externano estsincronizadacon el reloj del

dispositivo interno. Cuando se activael temporizador el contador se incrementaen uno en cada

cadaflanco ascendente del reloj de entraday generaunainterrupcin al igualarse con el registro de

perodo.

Paraconfigurar el modo de contador asncrono:

1. Borre el bit de control TSYNC (TxCON<2>) paradesactivar lasincronizacin del reloj.

2. Setear el bit de control TCS (TxCON<11>) paraseleccionar lafuente de reloj externa.

En el modo contador asncrono:

El temporizador puede ser configurado paratrabajar en bajo consumo de energacon un cristal

oscilador de 32 kHzexterno en modo oscilador secundario seteandoel bit (LPOSCEN) en el

registro de control de oscilador (OSCCON <1>).

El temporizador se puede operar en el modo de SLEEP si laentradade reloj externao el oscilador

secundario estactivada. Se puede generar unainterrupcin (si estactivado) cuando el registro de

conteo es igual al registro de perodo y podriadespertar el procesador del modo SLEEP.

Temporizadores de la Familia DSPIC33E/PIC24E

Temporizador Tipo A

El Timer1 es un temporizador tipo A. El tipo A tiene las siguientes caractersticas nicas con

respecto aotros tipos de temporizadores:

Funcionamiento como oscilador de bajapotenciacon un cristal de 32 kHzdisponibles en el

dispositivo

Funcionamiento en modo contador asncrono con fuente de reloj externa

Opcionalmente, laentradade reloj externo (TxCK) se puede sincronizar con el reloj

interno del dispositivo y lasincronizacin de reloj se llevaacabo despus de TxCKse divide

por el pre-escalador.

Las caractersticas nicas de un tipo A permiten que seautilizado paraaplicaciones de reloj

de tiempo real (RTCC).

Temporizadores de la Familia DSPIC33E/PIC24E

Diagrama de bloques del temporizador Tipo A

Temporizadores de la Familia DSPIC33E/PIC24E

Temporizador Tipo B

Los Temporizadores 2, 4, 6 y 8 son de tipo B. El temporizador de tipo B tiene la

las siguientes caractersticas especficas:

Puede ser concatenado con un temporizador Tipo C paraformar un

temporizador de 32 bits

Laentradade reloj externo (TxCK) siempre estsincronizado con el reloj

interno del dispositivo y lasincronizacin de reloj se llevaacabo despus que el

TxCKse divide por el pre-escalador.

Temporizadores de la Familia DSPIC33E/PIC24E

Diagrama de bloques del temporizador Tipo B

Temporizadores de la Familia DSPIC33E/PIC24E

Temporizador Tipo C

Los Temporiadores3, 5, 7 y 9, son temporizadores de tipo C. El temporizador Tipo C

tiene lalas siguientes caractersticas especficas:

Se puede concatenar con un temporizador de tipo B paraformar un temporizador

de 32 bits

Al menos un temporizador de Tipo C tiene lacapacidad de iniciar unaconversin

analgica-digital (A / D)

Laentradade reloj externo (TxCK) siempre estsincronizado con el reloj interno

del dispositivo y lasincronizacin de los relojes se realizautilizando TxCK despus de

lo cual este reloj sincronizado es dividido por el pre-escalador

Temporizadores de la Familia DSPIC33E/PIC24E

Diagrama de bloques del temporizador Tipo C

Temporizadores de la Familia DSPIC33E/PIC24E

CONFIGURACIN DEL TEMPORIZADOR DE 32 BITS

Un mdulo de temporizador de 32 bits puede ser formado mediante lacombinacin de

temporizadores de tipo B y tipo C de 16 bits. Parafuncionamiento en modo 32 bits, se debe setear

el bit de control T32 en el Registro de Control Tipo B (TxCON<3>).

El temporizador de Tipo C tiene lapalabrams significativa(MSW) y el temporizador de tipo B

tiene lamenos significativa(LSW) paralaoperacin de 32 bits.

Cuando se configuraparaoperacin de 32 bits, slo los bits del registro de control de los

temporizadores tipo B son necesarios paralaconfiguracin y control. Con laexcepcin del bit

TSIDL, todo los bits del registro de control del temporizador tipo C se ignoran.

Parael control de interrupcin, el temporizador de 32 bits combinado se utilizan los bits de

solicitud, habilitacin y prioridad de control del temporizador tipo C. Los bits de control de

interrupcin del temporizador tipo B se ignoran durante laoperacin del temporizador de 32

bits.

Estafuncin puede trabajar en los modos: Disparo Acumulado, Temporizador y Contador

Sncrono.

Los emparejamientos son: Timer 2 con Timer 3, Timer 4 con Timer 5, Timer 6 con Timer 7 y

Timer 8 con Timer 9

Temporizadores de la Familia DSPIC33E/PIC24E

Parasincronizar lalectura/ escriturade 32-bit entre el LSW ( 16 bits menos significativos) y

MSW ( 16 bits mas significativos) del temporizador de 32 bits, se tiene unalgicade control

adicional y registros de mantenimiento. Cadatemporizador Tipo C tiene un registro llamado

TMRyHLDque se utilizaal leer o escribir el par de registros del temporizador. Los registros

TMRyHLDse utilizan slo cuando sus respectivos temporizadores estn configurados para

operacin de 32 bits.

Suponiendo que TMR3: TMR2 forman un par temporizador de 32 bits, el software debe leer

primero el LSW del valor del temporizador del registro TMR2. Lalecturadel LSW transfiere

automticamente elcontenidode TMR3 en el registro TMR3HLD. El software puede leer el

MSW en el registro TMR3HLD en cualquier momento que se desee.

Paraescribir un valor en el par de registros TMR3: TMR2, laaplicacin de usuario debe

escribir primero el valor MSW al registro TMR3HLD. Cuando el LSW del valor de

temporizacin se escribe en TMR2, el contenido de TMR3HLD se transfiere al registro TMR3.

Temporizadores de la Familia DSPIC33E/PIC24E

Diagrama de bloques del temporizador 32 bits

Temporizadores de la Familia DSPIC33E/PIC24E

Lectura/ Escritura del temporizador 32 bits

/ / Leyendo temporizador de 32 bits

lsw= TMR2; / / Lee LSW del registrode conteodel temporizador tipoB

msw= TMR3HLD; / / Lee MSW del registroholding del temporizador tipoC

/ / Escribiendo temporizador de 32 bits

TMR3HLD = msw; / / EscribeMSW en el registroholding del temporizador tipoC

TMR2 = lsw; / / EscribeLSW en el registrode conteodel temporizador tipoB

Temporizadores de la Familia DSPIC33E/PIC24E

Modo de Disparo Acumulado

Cuando el mdulo de temporizacin funcionacon el reloj interno (TCS = 0), el modo de

disparo acumulado puede ser utilizado paramedir laduracin de unaseal de puertaexterna.

En este modo el temporizador comienzaaincrementarse en uno al haber un flanco de subida

del reloj de entraday continuacontando siempre y cuando laseal de puertaexternaen el pin

TxCKse mantengaen alto. Lainterrupcin del temporizador se generaen el flanco de bajada

del pin TxCKy se detiene el conteo.

Paraconfigurar el modo de disparo acumulado:

1. Setear el bit de control TGATE (TxCON<6>) parapermitir el funcionamiento del disparo

acumulado

2. Borre el bit de control TCS (TxCON<11>) paraseleccionar lafuente de reloj interno.

EL bit TSYNC (TxCON<2>) no tiene ningn efecto porque el reloj interno siempre est

sincronizado.

Temporizadores de la Familia DSPIC33E/PIC24E

Operacin de Modo de Disparo Acumulado

Temporizadores de la Familia DSPIC33E/PIC24E

Disparo de eventos especiales para conversin A/ D

En cadavariante del dispositivo, un temporizador Tipo C puede generar unaseal de disparo

especial de conversin A/ D en un perodo definido, tanto en el modo de 16 bits como en el de

32 bits. El mdulo temporizador proporcionaun inicio de conversin alalgicade muestreo

A/ D.

Si T32 = 0, cuando se produce unacoincidenciaentre el registro de temporizador de 16 bits

(TMRx) y el respectivo perodo de registro de 16-bit (PRx), unaseal de disparo Evento

Especial A/ D se genera

Si T32 = 1, cuando se produce unacoincidenciaentre el temporizador de 32 bits (TMRx:

TMRy) y el respectivo perodo de registro combinado de 32 bits (PRx: PRY), laseal de

disparo Evento Especial A/ D es generada.

Laseal de disparo de eventos especiales siempre se generapor el temporizador. Lafuente de

disparo debe ser seleccionado en el registro de control del convertidor A/ D.

En modo 32 bits solo los pares 2/ 3 y 4/ 5 pueden generar disparo de eventos especiales.

En modo 16 bits solo los timers3 y 5 pueden generar disparo de eventos especiales.

Temporizadores de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE TIMER TIPO A (TxCON) x=1

Byte superior

Bit 15 Bit 8

TON: Bit de encendido del TIMER.

1 =Inicia el temporizador.

0 =Detiene el temporizador.

Bit <14>: No implementado, ledo como 0.

TSIDL: Bit de para de modo IDLE.

1 =Temporizador esta detenido mientras se encuentra en modo IDLE.

0 =Temporizador continua mientras se encuentra en modo IDLE.

TON ---- TSIDL ---- ---- ---- ---- ----

Temporizadores de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE TIMER TIPO A (TxCON) x=1

Byte inferior

Bit 7 Bit 0

Bit <12:7>: No implementado, ledo como 0.

TGATE: Bit de Habilitacin del modo de disparo acumulado.

Mientras TCS =1 :

Este bit ser ignorado.

Mientras TCS =0 :

1 =Modo de disparo acumulado es habilitado.

0 =Modo de disparo acumulado es deshabilitado.

--- TGATE TCKPS<1:0> ---- TSYNC TCS ----

Temporizadores de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE TIMER TIPO A (TxCON) x=1

Byte inferior

Bit 7 Bit 0

TCKPS<1:0>: Bit de seleccin para el Prescalador del TIMER.

11 =1 : 256 Valor de Prescalador.

10 =1 : 64 Valor de Prescalador.

01 =1 : 16 Valor de Prescalador.

00 =1 : 1 Valor de Prescalador.

TSYNC: Bit de Seleccin de sincronizacin de fuente de reloj externo ( Siempre

que TCS=1).

1 =Sincronizar entrada de reloj externo ( Modo contador sncrono).

0 =No sincronizar entrada de reloj externo ( Modo contador asncrono).

--- TGATE TCKPS<1:0> ---- TSYNC TCS ----

Temporizadores de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE TIMER TIPO A (TxCON) x=1

Byte inferior

Bit 7 Bit 0

TCS: Bit de seleccin de fuente de reloj.

1 = Reloj externo en el PIN TxCK en el flanco ascendente o SOSC ( modo

contador)

0 = Reloj interno por FOSC/2 ( modo temporizador)

Bit <0>: No implementado, ledo como 0.

--- TGATE TCKPS<1:0> ---- TSYNC TCS ----

Temporizadores de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE TIMER TIPO B (TxCON) x=2,4,6,8.

Byte superior

Bit 15 Bit 8

TON: Bit de encendido del TIMER.

Cuando T32 =1 (En Modo de Timer de 32 Bit) :

1 =Habilita el TMRy de 32 Bit;

0 =Deshabilita el TMRy de 32 Bit;

Cuando T32 =0 :

1 =Habilita el Timer de 16 Bit.

0 =Deshabilita el Timer de 16 Bit.

Bit <14>: No implementado, ledo como 0.

TON ---- TSIDL ---- ---- ---- ---- ----

Temporizadores de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE TIMER TIPO B (TxCON) x=2,4,6,8.

Byte superior

Bit 15 Bit 8

TSIDL: Bit de para de modo IDLE.

1 =Temporizador esta detenido mientras se encuentra en modo IDLE.

0 =Temporizador continua mientras se encuentra en modo IDLE.

Bit <12:8>: No implementado, ledo como 0.

TON ---- TSIDL ---- ---- ---- ---- ----

Temporizadores de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE TIMER TIPO B (TxCON) x=2,4,6,8.

Byte inferior

Bit 7 Bit 0

Bit <7>: No implementado, ledo como 0.

TGATE: Bit de Habilitacin del modo de disparo acumulado.

Mientras TCS =1 :

Este bit ser ignorado.

Mientras TCS =0 :

1 =Modo de disparo acumulado habilitado.

0 =Modo de disparo acumulado deshabilitado.

--- TGATE TCKPS<1:0> T32 ---- TCS ----

Temporizadores de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE TIMER TIPO B (TxCON) x=2,4,6,8.

Byte inferior

Bit 7 Bit 0

TCKPS<1:0>: Bit de seleccin para el Prescalador del TIMER.

11 =1 : 256 Valor de Prescalador.

10 =1 : 64 Valor de Prescalador.

01 =1 : 16 Valor de Prescalador.

00 =1 : 1 Valor de Prescalador.

T32: Bit de Seleccin del modo de temporizador de 32 Bits.

1 =TMRx y TMRy forman un temporizador de 32 Bits

0 =TMRx y TMRy forman por separado dos temporizadores de 16 Bits

--- TGATE TCKPS<1:0> T32 ---- TCS ----

Temporizadores de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE TIMER TIPO B (TxCON) x=2,4,6,8.

Byte inferior

Bit 7 Bit 0

Bit <2>: No implementado, ledo como 0.

TCS: Bit de seleccin de fuente de reloj.

1 = Reloj externo en el PIN TxCK en el flanco ascendente o SOSC ( modo

contador)

0 = Reloj interno por FOSC/2 ( modo temporizador)

Bit <0>: No implementado, ledo como 0.

NOTA: Los Temporizadores TMRy son los Tipo C (y =3, 5, 7 y 9)

--- TGATE TCKPS<1:0> T32 ---- TCS ----

Temporizadores de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE TIMER TIPO C (TxCON) x=3,5,7,9.

Byte superior

Bit 15 Bit 8

TON: Bit de encendido del TIMER.

1 =Inicia el temporizador de 16 Bits

0 =Detiene el temporizador de 16 Bits.

Bit <14>: No implementado, ledo como 0.

TSIDL: Bit de para de modo IDLE.

1 =Temporizador esta detenido mientras se encuentra en modo IDLE.

0 =Temporizador continua mientras se encuentra en modo IDLE.

TON ---- TSIDL ---- ---- ---- ---- ----

Temporizadores de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE TIMER TIPO C (TxCON) x=3,5,7,9.

Byte inferior

Bit 7 Bit 0

Bit <12:7>: No implementado, ledo como 0.

TGATE: Bit de Habilitacin del modo de disparo acumulado.

Mientras TCS =1 :

Este bit ser ignorado.

Mientras TCS =0 :

1 =Modo de disparo acumulado habilitado.

0 =Modo de disparo acumulado deshabilitado.

--- TGATE TCKPS<1:0> ---- ----- TCS ----

Temporizadores de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE TIMER TIPO C (TxCON) x=3,5,7,9.

Byte inferior

Bit 7 Bit 0

TCKPS<1:0>: Bit de seleccin para el Prescalador del TIMER.

11 =1 : 256 Valor de Prescalador.

10 =1 : 64 Valor de Prescalador.

01 =1 : 16 Valor de Prescalador.

00 =1 : 1 Valor de Prescalador

Bit <3,2>: No implementados, ledo como 0.

--- TGATE TCKPS<1:0> ---- ----- TCS ----

Temporizadores de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE TIMER TIPO C (TxCON) x=3,5,7,9.

Byte inferior

Bit 7 Bit 0

TCS: Bit de seleccin de fuente de reloj.

1 = Reloj externo en el PIN TxCK en el flanco ascendente o SOSC ( modo

contador)

0 = Reloj interno por FOSC/2 ( modo temporizador)

--- TGATE TCKPS<1:0> ---- TSYNC TCS ----

Temporizadores de la Familia DSPIC33E/PIC24E

Aplicacin para temporizadores y contadores

Se desearealizar unaaplicacin mediante el dsPIC33EP256MU806, que permitavisualizar dos

seales cuadradas con distintos periodos alavez de visualizar en unainterfaz graficalaactualizacin

de unahorapreviamente configurada.

Paraestaaplicacin se emplearon el temporizador 1 parallevar el control de lahoramostradaen la

interfaz grafica, asu vez se utilizaron los temporizadores 2 y 3 paragenerar seales adiferentes

frecuencias, cadatemporizador fue utilizado como un timer de 16 bits utilizando como fuente de

reloj el oscilador externo principal (4Mhz).

Parallevar el control de las seales y lavisualizacin de lahorase programaron las interrupciones

correspondientes acadatemporizador, debido que los timer 3 y 2 manejan las seales, en sus

correspondientes interrupciones solo se invirti el valor lgico de lasalidaasignadaacadaseal,

mientras que en lainterrupcin del timer 1 se realizo unaverificacin paralaactualizacin y

posterior visualizacin de lahora.

El control de las interrupciones por el temporizador del dsPIC33EP256MU806 es manejado como

se muestraen ladiapositivasiguiente.

Temporizadores de la Familia DSPIC33E/PIC24E

Temporizadores de la Familia DSPIC33E/PIC24E

sbitGLCD_D7 at RE1_bit;

sbitGLCD_D6 at RE0_bit;

sbit GLCD_D5 at RF1_bit;

sbit GLCD_D4 at RF0_bit;

sbitGLCD_D3 at RD7_bit;

sbitGLCD_D2 at RD6_bit;

sbitGLCD_D1 at RD5_bit;

sbitGLCD_D0 at RD4_bit;

sbitGLCD_D7_Direction at TRISE1_bit;

sbitGLCD_D6_Direction at TRISE0_bit;

sbit GLCD_D5_Direction at TRISF1_bit;

sbit GLCD_D4_Direction at TRISF0_bit;

sbitGLCD_D3_Direction at TRISD7_bit;

sbitGLCD_D2_Direction at TRISD6_bit;

sbitGLCD_D1_Direction at TRISD5_bit;

sbitGLCD_D0_Direction at TRISD4_bit;

sbitGLCD_CS1 at LATE3_bit;

sbitGLCD_CS2 at LATE2_bit;

sbitGLCD_RSat LATD1_bit;

sbitGLCD_RW at LATD2_bit;

sbitGLCD_EN at LATD3_bit;

sbitGLCD_RST at LATE4_bit;

sbit GLCD_CS1_Direction at TRISE3_bit;

sbit GLCD_CS2_Direction at TRISE2_bit;

sbitGLCD_RS_Directionat TRISD1_bit;

sbitGLCD_RW_Directionat TRISD2_bit;

sbitGLCD_EN_Directionat TRISD3_bit;

sbitGLCD_RST_Directionat TRISE4_bit;

Temporizadores de la Familia DSPIC33E/PIC24E

Unsignedshort unidad_segundo=0, decena_segundo=0, unidad_minuto=0,

decena_minuto=0, unidad_hora=0, decena_hora=0;

char hora[8];

voidt1() org0x1A

{ unidad_segundo++;

if(unidad_segundo==10)

{ unidad_segundo=0;

decena_segundo++;

if(decena_segundo==6)

{ decena_segundo=0;

unidad_minuto++;

if(unidad_minuto==10)

{ unidad_minuto=0;

decena_minuto++;

if(decena_minuto==6)

{ decena_minuto=0;

unidad_hora++;

if(unidad_hora==10 && decena_hora==0)

{ unidad_hora=0;

decena_hora++;

}

elseif(unidad_hora==1 && decena_hora==3)

{ unidad_hora=0;

decena_hora=0;

}

}

}

}

}

Temporizadores de la Familia DSPIC33E/PIC24E

hora[0]=decena_hora+'0';

hora[1]=unidad_hora+'0';

hora[2]= ':';

hora[3]=decena_minuto+'0';

hora[4]=unidad_minuto+'0';

hora[5]= ':';

hora[6]=decena_segundo+'0';

hora[7]=unidad_segundo+'0';

hora[8]= '\ 0';

Glcd_Write_Text(hora, 30, 3, 1);

IFS0bits.T1IF=0;

}

voidt2() org0x22

{ PORTBbits.RB15=~PORTBbits.RB15;

IFS0bits.T2IF=0;

}

voidt3() org0x24

{ PORTFbits.RF4=~PORTFbits.RF4;

IFS0bits.T3IF=0;

}

voidmain()

{ ANSELC=0;

ANSELD=0;

ANSELE=0;

ANSELB=0;

Temporizadores de la Familia DSPIC33E/PIC24E

CORCONbits.IPL3=0; / / lainterrupcionde laCPU es de nivel 7 o menor

SRbits.IPL=0; / / interrupcionde laCPU es de nivel 0

INTCON1bits.NSTDIS=0; / / interrupcionanidadas activada

INTCON2bits.GIE=1; / / interrupciones habilitadas

TRISBbits.TRISB15=0;

PORTBbits.RB15=0;

TRISFbits.TRISF4=0;

PORTFbits.RF4=0;

TMR1=0;

T1CON=0X8020; Prescaler 64:1, modo timer

PR1=31250; / / 1000ms

TMR2=0;

T2CON =0X8010; Prescaler 16:1, modo timer

PR2=45000; / / 360ms

TMR3=0;

T3CON=0X8010; Prescaler 16:1 , modo timer

PR3=22500; / / 180ms

IEC0bits.T1IE=1;

IEC0bits.T2IE=1;

IEC0bits.T3IE=1;

IFS0bits.T1IF=0;

IFS0bits.T2IF=0;

IFS0bits.T3IF=0;

IPC0bits.T1IP=3;

IPC1bits.T2IP=4;

IPC2bits.T3IP=5;

Temporizadores de la Familia DSPIC33E/PIC24E

Glcd_Init();

Glcd_Set_Font(Character8x7, 8, 7, 32);

Glcd_Fill(0);

while(1);

}

Fin Clase 3

You might also like

- Intro Ducci On Control OptimoDocument10 pagesIntro Ducci On Control OptimoFernando MendezNo ratings yet

- Sistemas de Gestion - 2015Document56 pagesSistemas de Gestion - 2015sergiovelasquezgNo ratings yet

- Diseño y Evaluación de Separadores Bifásicos y TrifásicoDocument281 pagesDiseño y Evaluación de Separadores Bifásicos y TrifásicoMelissa SanchezNo ratings yet

- 21 Sistemas InformaciOnDocument22 pages21 Sistemas InformaciOnAnonymous OFKjccHONo ratings yet

- Transparencias (Noviembre-2000)Document95 pagesTransparencias (Noviembre-2000)Carlos J Duran ForeNo ratings yet

- TC Corporate TurnaroundDocument25 pagesTC Corporate TurnaroundKary AnLaNo ratings yet

- Diseño de Un Contenedor para PetroleoDocument8 pagesDiseño de Un Contenedor para Petroleoteddyz50No ratings yet

- 21 Sistemas InformaciOnDocument22 pages21 Sistemas InformaciOnAnonymous OFKjccHONo ratings yet

- Prospectiva Estratégica: Caja de Herramientas 2007Document105 pagesProspectiva Estratégica: Caja de Herramientas 2007nelson bary serna marcosNo ratings yet

- Auditorias Calidad 1997Document34 pagesAuditorias Calidad 1997sergiovelasquezgNo ratings yet

- REVISTA Avances Recientes en Laminación de Chapa GruesaDocument7 pagesREVISTA Avances Recientes en Laminación de Chapa GruesasergiovelasquezgNo ratings yet

- Concepto Gestion Medioambiental 01Document20 pagesConcepto Gestion Medioambiental 01sergiovelasquezgNo ratings yet

- Diseño de Un Contenedor para PetroleoDocument8 pagesDiseño de Un Contenedor para Petroleoteddyz50No ratings yet

- Clase 02 - Oscilador - WDT - PuertosDocument117 pagesClase 02 - Oscilador - WDT - PuertossergiovelasquezgNo ratings yet

- Intro Win CCDocument7 pagesIntro Win CCisaacageitosNo ratings yet

- Clase 11 Herramientas para La Planificacin Estratgica I267.ppt (Modo de Compatibilidad)Document17 pagesClase 11 Herramientas para La Planificacin Estratgica I267.ppt (Modo de Compatibilidad)sergiovelasquezgNo ratings yet

- Tes Is Antonio CastilloDocument121 pagesTes Is Antonio CastilloHisauro Lerma MamaniNo ratings yet

- Modelado No Lineal de Actuador HhidraulicoDocument12 pagesModelado No Lineal de Actuador HhidraulicosergiovelasquezgNo ratings yet

- 194 677 1 PBDocument16 pages194 677 1 PBsergiovelasquezgNo ratings yet

- Conocimiento CientificoDocument1 pageConocimiento CientificosergiovelasquezgNo ratings yet

- SID Practica7 WinCC IniciacionDocument65 pagesSID Practica7 WinCC Iniciacionjesus_alex_20No ratings yet

- Mitología Nordica, Breve CompendioDocument18 pagesMitología Nordica, Breve CompendioJuan José Velásquez ArangoNo ratings yet

- Intro Win CCDocument7 pagesIntro Win CCisaacageitosNo ratings yet

- Mitologia Nordica Niedner HeinrichDocument256 pagesMitologia Nordica Niedner Heinrich_fedra_100% (4)

- Gestión Del Conocimiento y Las TicDocument21 pagesGestión Del Conocimiento y Las Ticaipvelasco9920100% (1)

- Sistema de Información Científica: Red de Revistas Científicas de América Latina, El Caribe, España y PortugalDocument20 pagesSistema de Información Científica: Red de Revistas Científicas de América Latina, El Caribe, España y PortugalsergiovelasquezgNo ratings yet

- Gestion Del ConocimientoDocument3 pagesGestion Del ConocimientoJuan C Arce CNo ratings yet

- Gestion Del Conocimiento PDFDocument12 pagesGestion Del Conocimiento PDFfrankirkNo ratings yet

- CMV ApuntesDocument170 pagesCMV ApuntessergiovelasquezgNo ratings yet

- Laboratorio 1 - InformeDocument8 pagesLaboratorio 1 - InformeAnderson QuirozNo ratings yet

- 1 (1) - Como Leer Un Esquematico PDFDocument4 pages1 (1) - Como Leer Un Esquematico PDFLeonias Adrian100% (1)

- Amplificador de Potencia Clase (A, B, AB)Document8 pagesAmplificador de Potencia Clase (A, B, AB)Fabricio Borja Reinoso100% (1)

- Hoja de Chequeo Del ComputadorDocument1 pageHoja de Chequeo Del ComputadorVictor PazNo ratings yet

- Ensamble y Desensable de Los ComputadoresDocument79 pagesEnsamble y Desensable de Los ComputadoresMaria Floresminda Lancheros RiosNo ratings yet

- Laboratorio 2 Electronica IndustrialDocument19 pagesLaboratorio 2 Electronica IndustrialJean Pierre Auqui TovarNo ratings yet

- List A ActualDocument6 pagesList A ActualLuis Fernando Guerra TorricoNo ratings yet

- Trabajo ParalelismoDocument19 pagesTrabajo ParalelismoBelkys GonzalezNo ratings yet

- Caso Tics AccionesDocument5 pagesCaso Tics AccionesChoquehuancaRamosJohanNo ratings yet

- Informe Laboratorio MicroelectronicaDocument10 pagesInforme Laboratorio MicroelectronicaGONZALEZ MOLINA ANGEL ABDIASNo ratings yet

- Lab 01Document14 pagesLab 01Esteban MontesNo ratings yet

- Ensayo Sobre El ColorDocument2 pagesEnsayo Sobre El ColorkatherineNo ratings yet

- Mosfet: Electronic Basics #23: Transistor (MOSFET) As A SwitchDocument7 pagesMosfet: Electronic Basics #23: Transistor (MOSFET) As A SwitchDavid Alejandro Diaz RinconNo ratings yet

- Lista de Precios Mayo 2020 PDFDocument19 pagesLista de Precios Mayo 2020 PDFinghvd2015No ratings yet

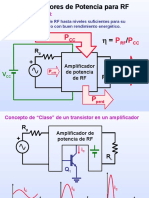

- HOY Amplificadores-Potencia RFDocument62 pagesHOY Amplificadores-Potencia RFJuan Chuna100% (1)

- Ejercicio Resuelto ICTDocument5 pagesEjercicio Resuelto ICTRoberto Pedrón DomingoNo ratings yet

- LAB 3 Tablas de VerdadDocument3 pagesLAB 3 Tablas de VerdadAmerico PattyNo ratings yet

- Levantamiento de Equipos Computacionales Municipalidad de Llanquihue (Autoguardado)Document12 pagesLevantamiento de Equipos Computacionales Municipalidad de Llanquihue (Autoguardado)Francisca Constanza Mansilla GuardaNo ratings yet

- Desbloqueos de Diversos TVDocument8 pagesDesbloqueos de Diversos TVAntonio DalioNo ratings yet

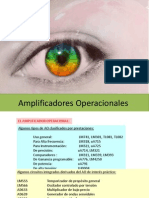

- Amplificador Operaciona1lDocument23 pagesAmplificador Operaciona1lSoledad R.AguilarNo ratings yet

- Proyecto de NavidadDocument12 pagesProyecto de NavidadLuis LirNo ratings yet

- Proyecto II Circuitos Electricos IDocument6 pagesProyecto II Circuitos Electricos IEliud Salazar100% (1)

- Anexo 3.1 Ficha Tecnica Transformador 15-150 Kva Aceite SiemensDocument1 pageAnexo 3.1 Ficha Tecnica Transformador 15-150 Kva Aceite SiemensMiguel AngelNo ratings yet

- Practica 3 - Probador de Continuidad.Document11 pagesPractica 3 - Probador de Continuidad.Angel VazquezNo ratings yet

- ISA - Vigo 2015 Introducción A Los Autómatas Programables 2Document31 pagesISA - Vigo 2015 Introducción A Los Autómatas Programables 2MrulrerNo ratings yet

- Contadores de Rizado PDFDocument8 pagesContadores de Rizado PDFPatoSilvaNo ratings yet

- Datasheet Denwa Advanced Plus CustomDocument4 pagesDatasheet Denwa Advanced Plus CustomLuisa Fernanda Saenz DuarteNo ratings yet

- Ipldk20 PM v36 200606v3Document545 pagesIpldk20 PM v36 200606v3Patricio SánchezNo ratings yet

- PeugeotDocument6 pagesPeugeotErica Amador100% (2)

- FototransistoresDocument13 pagesFototransistoresdbj60885No ratings yet