Professional Documents

Culture Documents

Edn Design Ideas III

Uploaded by

agmnm1962Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Edn Design Ideas III

Uploaded by

agmnm1962Copyright:

Available Formats

Under certain conditions, ESD

events can damage digital circuits

by causing latch-up. For example,

when ESD triggers them, parasitic tran-

sistors normally formed as parts of a

CMOS device can behave as an SCR

(silicon-controlled rectifier). Once

ESD triggers, the SCR presents a low-

resistance path between portions of the

CMOS device and conducts heavily.

Damage to the device can result unless

you immediately remove power from the

circuit. ESD from human interaction

presents a significant problem for

mobile industrial and medical devices.

For adequate ESD protection, most

medical and industrial devices require a

grounded return path for ESD currents.

In the real world, mobile devices may

serve in environments in which properly

grounded power outlets are unavailable.

To protect expensive equipment from

latch-up failures even when no ESD

ground is present, you can add the

power-interruption circuit shown in

Figure 1to prevent damage when ESD-

induced latch-up occurs. Under normal

conditions, current drawn by ESD-sus-

ceptible devices develops a small volt-

age across sense resistor R

6

. A voltage

divider formed by R

4

and R

5

defines a

reset-current threshold for the LED

portion of optoisolator IC

1

, and, under

normal operational current consump-

tion, the LED remains dark.

The output of IC

1

controls the gate

bias applied to MOSFET Q

1

, which is

normally on. When latch-up occurs,

power-supply current drain rapidly

increases by an order of magnitude or

more. The large voltage drop developed

across R

6

forward-biases IC

1

s LED,

which in turn drives IC

1

s phototran-

sistor into conduction and shuts off Q

1

,

interrupting dc power to ESD-suscep-

tible devices for several milliseconds. In

addition, the systems firmware design

must allow for automatic recovery from

a power interruption.

The following describes the rela-

tionship between the reset-current

threshold and the values of R

4

and R

5

:

(R

4

R

5

)/R

4

(I

T

R

6

)/V

LED

, in which

I

T

(V

LED

)/R

6

, and V

CC

V

LED

.

The ESD-induced fault threshold

current, I

T

, is greater than or equal to

the optoisolator LEDs conducting for-

ward-voltage drop divided by the value

of sense resistor R

6

. Also, the raw

power-supply voltage must exceed the

LEDs forward-voltage drop. Resistor R

1

provides a path for IC

1

s base-leakage

current, and resistors R

3

and R

2

deter-

mine Q

1

s gate-shutoff bias.

In Figure 1, the optoisolator presents

an LED forward-voltage drop of 1.2V.

For the component values shown, the

circuit momentarily interrupts V

CC

when ESD-induced power-supply cur-

rent exceeds approximately 300 mA.

Total cost of the six resistors, one MOS-

FET, and one optoisolator is approxi-

mately $1 (production quantities).EDN

READERS SOLVE DESIGN PROBLEMS

DIs Insi de

70 High-impedance FET probe

extends RF-spectrum analyzers

usable range

72 Watchdog circuit protects

against loss of battery chargers

control signals

78 Circuit adds foldback-current

protection

Power-supply interrupter fights

ESD-induced device latch-up

EDITED BY BRAD THOMPSON

AND FRAN GRANVILLE

designideas

Figure 1 Upon sensing an overcurrent spike, this circuit interrupts power and

enables the circuits recovery from ESD-induced latch-up.

Emerson Segura, Lifescale Global Diagnostics Inc, Toronto, ON, Canada

JULY 21, 2005 | EDN 69

V

CC

5V

MICROCONTROLLER/

DSP

EEPROM ETC

4

3

1

NC

AN

NC

IC

1

EMT

BASE

5

6

7

8

R

1

100k

R

2

1k

R

3

15k

R

6

47k

R

4

10k

R

5

1k

NC

6

CAT

MOC211-M

Q

1

BSS-138

I

T

COL

REPRESENTATIVE

LATCH-UP-PRONE

DEVICES

Current models of spectrum ana-

lyzers routinely offer frequency

responses that begin as low as 10 Hz.

When you combine them with 1-Hz or

narrower band FFT software, expand-

ed low-frequency performance makes

the modern spectrum analyzer an in-

valuable tool for designing and debug-

ging high-performance analog circuits.

Unfortunately, a spectrum analyzer

thats primarily for RF typically presents

an input impedance of 50, a heavy

load when you apply it to most high-

impedance analog circuits. You can

improvise a somewhat higher imped-

ance probe by adding a 953 resistor

in series with the 50 input, but this

approach provides only a 1-k input

impedance and reduces the measured

signal by 26 dB.

In addition, most RF-spectrum ana-

lyzers lack ac coupling, and, thus, any

dc-input component directly reaches

either the internal terminating resistor

or the front-end mixer. To maintain a

10-Hz, low-frequency response, you

must connect a coupling capacitor with

a value of at least 2 F in series with

the 953 input probe. Although oscil-

loscopes input circuits can withstand

accidental probe contacts and capaci-

tive-transient overloads, using a low-

impedance, ac-coupled probe with a

spectrum analyzer can lead to destruc-

tion of the analyzers expensive and

possibly hard-to-replace front-end

mixer.

Although high-impedance probes are

commercially available, theyre expen-

sive to purchase and repair. This Design

Idea offers an alternative: an inexpen-

sive and well-protected unity-gain

probe that presents the same input

impedance as a basic bench oscillo-

scope and can drive the spectrum ana-

lyzers 50 input impedance. The

probe has a gain of 00.2 dB at 100

kHz. Input impedance is 1 M, 15 pF,

and maximum input is 0.8V p-p. Load

impedance is 50, and frequency

response is 10 Hz to 200 MHz at 3 dB.

Passband ripple is less than 1 dB p-p.

Input noise at 1 MHz is less than 10

nV/Hz. Distortion for 0.5V p-p input

at 10 MHz is less than 75 dBc for sec-

ond-order distortion and less than 85

dBc for third order. Power requirements

are 5V at 16 mA.

You can assemble the circuit in Fig-

ure 1 in an afternoon from readily

available and inexpensive compo-

nents. The circuits input presents the

same characteristics as a bench oscil-

loscopea 1-M resistance in paral-

lel with 15 pF of capacitance. You can

also use this active probe in place of

standard 1-to-1 or 10-to-1 oscilloscope

probes, thus extending the designs

applicability. The back-to-back silicon

diodes in the D

1

clamp the input signal

to plus or minus one forward-voltage

drop, which limits signal excursions you

apply to the spectrum analyzers front

end, thus protecting the input mixer

from damage due to overloads and

ESD. Because most users employ the

probe and spectrum analyzer to meas-

ure small-amplitude signals and noise,

High-impedance FET probe extends

RF-spectrum analyzers usable range

designideas

Steve Hageman, Windsor, CA

Figure 1 Just a handful of parts can help extend a spectrum analyzers performance. This unity-gain probe emulates a stan-

dard oscilloscope probes 1-M and 15-pF input characteristics and easily drives 50 loads.

70 EDN | JULY 21, 2005

_

+

5V

IN

5V

IN

C

5

2.2 F

C

6

2.2 F

OUTPUT

C

1

0.047 F

C

2

6.8 pF

R

1

1M

R

4

249

R

2

100

R

5

51.1

R

3

249

C

4

0.22 F

C

3

0.22 F

5V

5V

3

6

7

4

2

1

50

INPUT

1M 15 pF

0.8V P-P

MAXIMUM

J

1

J

2

D

1

BAV99L

NOTES:

ENCLOSE IN BRASS TUBE FOR SHIELDING.

ALL RESISTORS ARE 1%.

IC

1

OPA656NB

2

3

5V

+

+

5V

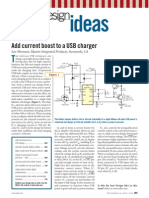

Recharging a mobile phones

internal battery usually occurs

under control of a proprietary charging

algorithm that resides in the baseband

controller. The charger connects to the

internal battery through a P-channel-

MOSFET switch of low on-resistance

(Figure 1). A baseband controller sup-

plies a PWM signal that drives the

switch. To minimize power dissipation

and consequent thermal problems in

the phone, the charging supplyusu-

ally a plug-in transformer assembly

features internal current limiting and

has specifications that correspond to

the batterys chemistry and charge-

recovery requirements.

However, if the baseband processor

stalls for any reason, the nearly direct

charger-to-battery connection could

damage the battery. To circumvent the

problem, another circuit monitors the

chargers PWM input and disables the

series power switch after a predetermined

delay interval (Figure 2). The circuit

operates independently of the baseband

units processor and allows charging to

resume when the PWM signal returns.

In this circuit, microprocessor super-

visor IC

1

, a Maxim MAX6321 that

includes a watchdog circuit that can

monitor software execution, drives IC

2

,

a normally open SPST analog switch.

Components R

4

, D

2

, and C

1

protect IC

1

and IC

2

by limiting V

CC

to a maximum

of 5.1V. Resistor R

4

s value isnt critical

because the protection circuits quies-

cent current is low at approximately 30

A. Select R

4

to provide just enough

currentfor example, 0.5 mAto bias

zener diode D

1

into the knee of its

characteristic V-I curve.

the limited large-signal response does

not affect most applications.

High-performance FET input opera-

tional amplifier IC

1

, a Texas Instru-

ments OPA656, provides a voltage gain

of two. This configuration yields a

bandwidth of approximately 200 MHz

(Figure 2). The OPA656 can drive

50 back-matched loads for a total

load of 100, which results in a 6-dB

gain loss for which IC

1

s gain of two

compensates for a net gain of unity. The

OPA656 also introduces lower noise

and distortion than that of most com-

mercially available, active FET-based

probes.

The probe in Figure 3 fits into a

small section of brass hobby tubing.

The input connector comprises a small

SMA edge-launch connector that you

can easily adapt to other connectors,

including the BNC and its many acces-

sories. The probe requires 5 and 5V

at approximately 18 mA each, which

you can obtain from an instruments

probe-power connector if available

or from a linear supply designed around

an ac wall transformer. For best

results, use 78L05 and 79L05 voltage

regulators to stabilize the supply

voltages.

Standard miniature 50 coaxial

cable connects the probe to the meas-

uring instrument. For the flattest fre-

quency response and uniform gain, ter-

minate the probes output with 50;

the circuit requires no dc-output-block-

ing capacitor.EDN

Watchdog circuit protects against loss

of battery chargers control signals

Andy Fewster, Maxim Integrated Products Inc, Hampshire, UK

designideas

AMPLITUDE

RESPONSE

(dB)

FREQUENCY (MHz)

1

0

1

2

3

CH1

5

6

7

ABS

1

1

STOP 250.000 MHz START 0.300 MHz

dB CH1: MKR1 201.383 MHz

2.99 dB

Figure 2 The probes measured 3-dB frequency response extends from 10 Hz

to 200 MHz with slightly less than 1-dB passband ripple, which compares favor-

ably with the 2-dB response of many commercial active-FET probes.

Figure 3 You can assemble the probe on a piece of breadboard that fits into a

section of brass tubing from model and hobby shops. An SMA input connector

matches a multitude of adapters and probe tips, a few of which are shown.

Use a rubber grommet to close the probes output end.

72 EDN | JULY 21, 2005

(continued on pg 76)

The protection circuit consumes no

power except when the battery under-

goes charging and therefore doesnt bur-

den the battery. Supervisor IC

1

provides

a RESET output that can serve as a

charger-ready interrupt input to the

baseband-controller CPU. The RESET

outputs open-drain structure allows its

connection to other circuits that oper-

ate from different supply voltages. Sup-

plying power to the watchdog and

PWM circuits only during charging also

prevents reverse current from flowing

into the IC

1

s RESET output and dis-

charging the battery via a sneak path.

The timing diagram illustrates the

circuits operation when an active

designideas

Q

1

Q

2

R

1

R

3

D

1

R

2

GROUND

BASEBAND

PWM INPUT

+

MAIN

BATTERY

ONE LI-ION

OR

THREE NIMH

CHARGER

INPUT

SI5853DC

Figure 1 A typical mobile phones battery-charger input circuit comprises a

series switch controlled by a PWM signal.

Figure 2 Adding watchdog protection to the circuit of Figure 1 guards against battery damage when the baseband proces-

sor stalls or ceases software execution.

76 EDN | JULY 21, 2005

Figure 4 When PWM pulses cease, the watchdog circuit

disables the charger after a 1.6-sec interval.

Figure 3 Reset-timing relationships for the circuit of

Figure 2 illustrates its power-on behavior.

GROUND

BASEBAND

PWM INPUT

CHARGER

INPUT

Q

1

BC847

Q

2

R

1

240k

R

4

5.1k

D

2

5.1V

R

3

51k

R

2

56k

C

1

0.1 F

CERAMIC

MAIN

BATTERY

ONE LI-ION

OR

THREE NIMH

CHARGE-

READY SIGNAL

TO BASEBAND

PROCESSOR

D

1

SI5853DC

GND

GND

.

.

.

.

.

.

.

V

CC

V

CC

IC

1

MAX6321-

HPUK30-CY

IC

2

MAX4514CUK

RESET

WDI

RESET

NC

RESET

RESET

t

RP

t

RP

V

RST

V

RST

t

RD

t

RD

NOTES:

t

RP

=RESET-ACTIVE-TIME-OUT PERIOD (200 mSEC).

t

RD

=RESET-DELAY TIME FROM V

CC

(40 SEC).

GND

GND

1V

V

CC

1V

RESET

V

CC

t

RP

t

RST

t

WD

t

RP

WDI

NOTES:

t

WD

=WATCHDOG-TIME-OUT PERIOD (1.6 SEC).

t

RP

=RESET-ACTIVE-TIME-OUT PERIOD (200 mSEC).

For many applications that re-

quire power-supply currents of a

few amperes or less, three-terminal

adjustable-output linear voltage regu-

lators, such as National Semiconduc-

tors LM317, offer ease of use, low cost,

and full on-chip overload protection.

The addition of a few components can

provide a three-terminal regulator

with high-speed short-circuit current

limiting for improved reliability. The

current limiter protects the regulator

from damage by holding the maximum

output current at a constant level, I

MAX

,

that doesnt damage the regulator (Ref-

erence 1). When a fault condition

occurs, the power dissipated in the pass

transistor equals approximately V

IN

I

MAX

. Designing a regulator to survive

an overload requires conservatively

ratedand often over-

designedcomponents

unless you can reduce, or

fold back, the output

current when a fault

occurs (Reference 2).

The circuit in Figure

1 incorporates foldback-

current limiting to pro-

tect the pass transistor

by adding feedback

resistor R

4

. Under nor-

mal conditions, transis-

tor Q

2

doesnt conduct,

and resistors R

1

and R

2

bias MOSFET Q

1

into

conduction. When an

output overload occurs,

Q

2

conducts, reducing

the on-state bias applied

to Q

1

and thus increas-

ing its drain-source

resistance and limiting

the current flowing into

regulator IC

1

, an LM317.

Adding R

4

makes Q

2

s

bias current dependent

on the output voltage,

V

OUT

, which decreases

under overload condi-

tions.

For the circuit in Figure 1, you can

calculate the maximum foldover and

short-circuit currents, I

KNEE

and I

SC

,

respectively, as follows:

In a practical design, you select val-

ues for I

KNEE

and I

SC

and equal values for

R

3A

and R

3B

and then use equations 1

and 2 to calculate resistors R

SC

and R

4

.

For the circuit in Figure 1, the outputs

maximum and short-circuit currents are

fixed at 0.7 and 0.05A, respectively.

With R

3A

and R

3B

set to 100, solving

the equations yields values of 0.73 for

R

SC

and 4.3 k for R

4

.You can demon-

strate the circuits performance by

applying a variable-load resistor thats

adjustable from 0 to 200. As Figure

2 shows, the outputs simulated and

measured voltage-versus-current char-

acteristics, V

OUT

andI

OUT

, respectively,

are in close agreement.EDN

REFERENCES

Hulseman, Herb, MOSFET

enhances voltage regulators overcur-

rent protection, EDN, March 3, 2005,

pg 74.

Galinski, Martin, Circuit folds back

current during fault conditions, EDN,

Nov 28, 2002, pg 102.

charger connects to the phones charg-

er-input socket (Figure 3). In this

example, the MAX6321-HPUK30-CY

that IC

1

uses is factory-trimmed for a 3V

reset threshold, and the -CY suffix indi-

cates complementary reset outputs and

a 1.6-sec delay interval. The reset inter-

val begins when V

CC

reaches 3V45

mV. After 200 msec, RESET goes low,

and RESET goes high.

The RESET output releases the

SPST analog switch, IC

2

, which

enables the PWM input. Meanwhile,

the active WDI (watchdog input)

monitors the PWM input signal. If no

signal transitions occur within 1.6 sec,

the RESET and RESET outputs

become active, disabling the PWM

input and pausing the charger algo-

rithm using a CPU interrupt that the

charger-ready signal conveys (Figure

4). All active and passive components

for the circuit are available in surface-

mount packages. Pass transistor Q

2

, a

Siliconix-Vishay SiS5853, includes an

integrated Schottky diode, D

1

.EDN

designideas

78 EDN | JULY 21, 2005

Figure 1 This circuit adds foldback-overcurrent protection to

a linear regulator.

OUTPUT

VOLTAGE

(V)

OUTPUT CURRENT

(mA)

24

20

16

12

8

4

0

0 100 200 300 400 500 600 700 800

EXPERIMENTAL

SIMULATED

Figure 2 Simulated and measured foldback-current

responses to a load resistance that varies from 200 to

0.01 show close agreement.

Circuit adds foldback-current protection

Rafael Garca-Gil and JM Esp, Electronic Engineering Department, University of Valencia, Spain

1

2

R

1

22k

R

2

22k

C

1

1 F

C

2

1 F

D

1

D

2

R

4

4.3k

Q

1

BC557

Q

2

IRF913

30V

IN

21V

OUT

R

3A

100

R

3B

100

R

6

240

R

5

3.9k

R

SC

0.83

IC

1

LM317

(1)

(2)

You might also like

- Electronic Load and Other Circuit IdeasDocument6 pagesElectronic Load and Other Circuit Ideasanees_172000100% (1)

- LTC4416-1 Flyback Controller BoardDocument1 pageLTC4416-1 Flyback Controller BoardChandrasegar SubramaniNo ratings yet

- Siemens Safety B10 Values - Extract From IC 10-2017Document2 pagesSiemens Safety B10 Values - Extract From IC 10-2017spuntoandreaNo ratings yet

- 16 Design IdeasDocument7 pages16 Design Ideasmailnehru8955100% (2)

- Ee - 105 - ADSP-2100 Family C Programming Examples Guide (En)Document61 pagesEe - 105 - ADSP-2100 Family C Programming Examples Guide (En)tiretrakNo ratings yet

- Led DisplayDocument6 pagesLed DisplayIonut Octavian100% (2)

- Testing The PIC Microcontroller (Pic 16F877A)Document6 pagesTesting The PIC Microcontroller (Pic 16F877A)Matt ImriNo ratings yet

- Boost USB Charging Current with External TransistorDocument8 pagesBoost USB Charging Current with External Transistoragmnm1962100% (2)

- EDN Design Ideas 2008Document124 pagesEDN Design Ideas 2008chag1956100% (2)

- VC SlopeDocument8 pagesVC SlopeEzKeezENo ratings yet

- Stereo Peak Indicator: Small CircuitscollectionDocument1 pageStereo Peak Indicator: Small CircuitscollectionTariq Zuhluf100% (1)

- EDN Design Ideas PDFDocument7 pagesEDN Design Ideas PDFAmine HalimiNo ratings yet

- 12v To 18v ConverterDocument7 pages12v To 18v ConverterLuis Paulo100% (1)

- EDN Design Ideas 2001Document182 pagesEDN Design Ideas 2001chag1956100% (5)

- Class E amplifier achieves 96% efficiency at 3.9 MHzDocument9 pagesClass E amplifier achieves 96% efficiency at 3.9 MHzjrmciNo ratings yet

- 1989 Analog Devices DSP Products DatabookDocument437 pages1989 Analog Devices DSP Products DatabookkgrhoadsNo ratings yet

- 7 Segment N LCDDocument38 pages7 Segment N LCDBaishakhi Bose100% (1)

- 19v From A Car BatteryDocument4 pages19v From A Car Batterysafet100% (1)

- Volume52 Number4Document64 pagesVolume52 Number4torinomg100% (1)

- Best of DesignIdeasDocument48 pagesBest of DesignIdeastinears02100% (1)

- Slua 125Document10 pagesSlua 125Anonymous RloUXGnmSWNo ratings yet

- RS-485 Transceiver Tutorial: 1 IntersilDocument8 pagesRS-485 Transceiver Tutorial: 1 Intersilpiyushpandey100% (3)

- Digital Thermometer Circuit.Document2 pagesDigital Thermometer Circuit.elvergonzalez1100% (1)

- 12 Mosfet BiasingDocument18 pages12 Mosfet BiasingManish KumarNo ratings yet

- EDN Design Ideas 2000Document215 pagesEDN Design Ideas 2000chag1956100% (3)

- Icd 3Document45 pagesIcd 3Sergiu Ene0% (1)

- 200W Leach AmpDocument12 pages200W Leach AmpАлексей Андрияш100% (1)

- 50W Hi-Fi Power Audio Amplifier TDA7294 PDFDocument5 pages50W Hi-Fi Power Audio Amplifier TDA7294 PDFciamponi1959100% (1)

- PT2033Document5 pagesPT2033mite100% (1)

- Adi Mixer Soundcraft - Efx12 - Efx8 - Mixer PDFDocument110 pagesAdi Mixer Soundcraft - Efx12 - Efx8 - Mixer PDFbioteky100% (1)

- Edn Best of Design Ideas 2012Document25 pagesEdn Best of Design Ideas 2012srescia67% (3)

- EDN Design Ideas 1999Document201 pagesEDN Design Ideas 1999chag1956100% (5)

- GLM240128Document35 pagesGLM240128api-3700809No ratings yet

- Audio AmplifiersDocument11 pagesAudio AmplifiersWaqas AbroNo ratings yet

- Ask The Applications Engineer 24-40Document142 pagesAsk The Applications Engineer 24-40Shashikiran HPNo ratings yet

- Protel SchematicDocument1 pageProtel SchematicVictor D'souza50% (2)

- NS-BP112/NS-BP102 CRX-B370/CRX-B370D: MCR-B370/MCR-B270/ MCR-B370D/MCR-B270DDocument65 pagesNS-BP112/NS-BP102 CRX-B370/CRX-B370D: MCR-B370/MCR-B270/ MCR-B370D/MCR-B270DVicente Fernandez100% (1)

- ANCRCT-4 Precision Rectifier CircuitDocument1 pageANCRCT-4 Precision Rectifier Circuitramesh_br85100% (1)

- 1602 Arduino Shield LCD PDFDocument6 pages1602 Arduino Shield LCD PDFpeccerini100% (1)

- Drake PartlistDocument50 pagesDrake PartlistAnonymous hPUlIF6No ratings yet

- PIC18F97J60 Family Data SheetDocument476 pagesPIC18F97J60 Family Data SheetcoccomNo ratings yet

- Halo 180Document2 pagesHalo 180JohnNo ratings yet

- USB to RS232 Converter Using Atmel MicrocontrollersDocument4 pagesUSB to RS232 Converter Using Atmel MicrocontrollersNugraha Indrawan100% (2)

- EDN 0504 SupplementDocument36 pagesEDN 0504 Supplementmcpa-tum100% (2)

- EDN Design Ideas 2005Document134 pagesEDN Design Ideas 2005chag1956100% (2)

- Thyristors and Triacs PDFDocument30 pagesThyristors and Triacs PDFCristianNo ratings yet

- MPC1000 ServManualDocument22 pagesMPC1000 ServManualAdrian DuMayNo ratings yet

- FETs DatabookDocument189 pagesFETs DatabookTito Titon0% (1)

- AVR Hardware Design ConsiderationsDocument14 pagesAVR Hardware Design ConsiderationsAmarnath M Damodaran100% (1)

- Ultrasonic Rangefinder Using 8051Document25 pagesUltrasonic Rangefinder Using 8051Kaos Polos Nakira50% (4)

- Boss DR-880 Service NotesDocument37 pagesBoss DR-880 Service NotesFernando GómezNo ratings yet

- Cascode Amp Design Reduces DistortionDocument4 pagesCascode Amp Design Reduces DistortionRaulh PerezNo ratings yet

- Mini ProjectDocument6 pagesMini ProjectMc EswaranNo ratings yet

- 16.7 All-Pass Filter Design: Figure 16-41. Comparison of Q Between Passive and Active Band-Rejection FiltersDocument8 pages16.7 All-Pass Filter Design: Figure 16-41. Comparison of Q Between Passive and Active Band-Rejection FiltersseleneedithNo ratings yet

- Open Source Frequency Counter DIY Kit 10Hz-250MHzDocument10 pagesOpen Source Frequency Counter DIY Kit 10Hz-250MHzBruno Santos de Miranda100% (1)

- British Special Quality Valves and Electron Tube Devices Data Annual 1964–65From EverandBritish Special Quality Valves and Electron Tube Devices Data Annual 1964–65No ratings yet

- Minor Project FileDocument29 pagesMinor Project FilePoorva ShuklaNo ratings yet

- Power Failure AlarmDocument17 pagesPower Failure AlarmPurva Patil33% (3)

- Electric DriveDocument16 pagesElectric DriveSubhash KumarNo ratings yet

- Broadband Lumped-Element Integrated - Way Power Dividers For Voltage StandardsDocument9 pagesBroadband Lumped-Element Integrated - Way Power Dividers For Voltage Standardsagmnm1962No ratings yet

- A Compact Ultra-Wideband Power Divider With High Isolation 3.1-10.6 GHZDocument2 pagesA Compact Ultra-Wideband Power Divider With High Isolation 3.1-10.6 GHZagmnm1962No ratings yet

- 12 G To 20 G Compact Rectangle Waveguide To Circular Waveguide Mode ConvertorDocument2 pages12 G To 20 G Compact Rectangle Waveguide To Circular Waveguide Mode Convertoragmnm1962No ratings yet

- Mirrored Coupling Structures For Microwave Signal Splitting and Combining PDFDocument6 pagesMirrored Coupling Structures For Microwave Signal Splitting and Combining PDFagmnm1962No ratings yet

- ACS712 Demo Board Guide PDFDocument11 pagesACS712 Demo Board Guide PDFagmnm1962No ratings yet

- Patch Antenna Design MAnualDocument36 pagesPatch Antenna Design MAnualkarthikvel_852246No ratings yet

- A Novel Wideband Bandpass Power Divider With Harmonic Suppressed Ring Resonator 1.41-2.68 GHZDocument4 pagesA Novel Wideband Bandpass Power Divider With Harmonic Suppressed Ring Resonator 1.41-2.68 GHZagmnm1962No ratings yet

- AN5142 Radio Link-Budget Calculations For ISM-RF ProductsDocument11 pagesAN5142 Radio Link-Budget Calculations For ISM-RF Productsagmnm1962No ratings yet

- High Power CombinerDocument5 pagesHigh Power Combineragmnm1962No ratings yet

- C106BOS Datasheetz PDFDocument6 pagesC106BOS Datasheetz PDFAnonymous na7OSZaNo ratings yet

- 51W 10540 1Document16 pages51W 10540 1Mitrofan AnduNo ratings yet

- ADF4355 54-6800 MHZ Microwave Wideband Synthesizer With Integrated VCODocument35 pagesADF4355 54-6800 MHZ Microwave Wideband Synthesizer With Integrated VCOagmnm1962No ratings yet

- Tipl762 - NPN Silicon Power TransistorsDocument7 pagesTipl762 - NPN Silicon Power Transistorsagmnm1962No ratings yet

- Scr's & Triacs Cross ReferenceDocument11 pagesScr's & Triacs Cross Referenceagmnm1962No ratings yet

- SP 500 SpecDocument2 pagesSP 500 Specagmnm1962No ratings yet

- SP431 Adjustable Precision RegulatorsDocument11 pagesSP431 Adjustable Precision Regulatorsagmnm1962No ratings yet

- DB3 DB4 SMDB3 - Diac PDFDocument6 pagesDB3 DB4 SMDB3 - Diac PDFmsicoie1851No ratings yet

- Data Sheet: UHF Push-Pull Power MOS TransistorDocument15 pagesData Sheet: UHF Push-Pull Power MOS Transistoragmnm1962No ratings yet

- MRF 175 GVDocument1 pageMRF 175 GVagmnm1962No ratings yet

- 200watt Active Load UnitDocument14 pages200watt Active Load Unitagmnm1962No ratings yet

- tl783 PDFDocument26 pagestl783 PDFLuiz CaldeiraNo ratings yet

- Variable High Voltage BJT Regulator User ManualDocument7 pagesVariable High Voltage BJT Regulator User Manualagmnm1962No ratings yet

- Basic Calculation of A Boost Converter's Power StageDocument9 pagesBasic Calculation of A Boost Converter's Power Stagexuanvan1303No ratings yet

- Testing A Power Supply For Line and Load TransientsDocument7 pagesTesting A Power Supply For Line and Load Transientsagmnm1962No ratings yet

- Sprabw0b PDFDocument19 pagesSprabw0b PDFAshok KumarNo ratings yet

- Pads WhitepaperDocument23 pagesPads Whitepaperagmnm1962No ratings yet

- LXA-7500 Series X-Band Low Noise AmplifiersDocument4 pagesLXA-7500 Series X-Band Low Noise Amplifiersagmnm1962No ratings yet

- Creating A Fast Load TransientDocument3 pagesCreating A Fast Load Transientagmnm1962No ratings yet

- Design of a 2.5kW isolated DC/DC fullbridge converter for electric vehicle applicationDocument55 pagesDesign of a 2.5kW isolated DC/DC fullbridge converter for electric vehicle applicationmarconi-agNo ratings yet

- A Review of Implantable Antennas For Wireless Biomedical DevicesDocument11 pagesA Review of Implantable Antennas For Wireless Biomedical Devicesagmnm1962No ratings yet

- Champ - 4: ManualDocument12 pagesChamp - 4: Manualcoco dj cocodjNo ratings yet

- Atmel ATmega328 Test Circuit DiagramDocument6 pagesAtmel ATmega328 Test Circuit Diagramcadeyare2No ratings yet

- Ee201 Notes 5Document46 pagesEe201 Notes 5adamwaiz100% (2)

- Press ReleaseDocument3 pagesPress Releaseaycan Digitalsysteme GmbHNo ratings yet

- Vishay SIRA99DP MosfetDocument9 pagesVishay SIRA99DP MosfetJustin FozzardNo ratings yet

- Applications and Characteristics of Differential Relays ANSI 87Document6 pagesApplications and Characteristics of Differential Relays ANSI 87Ricardo A VergaraNo ratings yet

- Semiconductor Memory Types and OrganizationDocument15 pagesSemiconductor Memory Types and OrganizationBereket TarikuNo ratings yet

- Measurement of Microwave Antenna ParametersDocument9 pagesMeasurement of Microwave Antenna ParametersRounit RaiNo ratings yet

- Upgrade Your Fulltone Fulldrive 2 for BassDocument5 pagesUpgrade Your Fulltone Fulldrive 2 for BassPhilipe Vila NovaNo ratings yet

- 555 and 556 Timer CircuitsDocument16 pages555 and 556 Timer Circuitssiddharthmohta100% (2)

- Combina Sanyo Service ManualDocument41 pagesCombina Sanyo Service ManualflorinNo ratings yet

- JVC CA DX t9, DX t7, DX t5Document31 pagesJVC CA DX t9, DX t7, DX t5Roosevelt Vega SanchezNo ratings yet

- JAN-701B, 901B Installation ManualDocument140 pagesJAN-701B, 901B Installation ManualAdi Prasetyo100% (2)

- Dokumen - Tips - Contador 7490 Manual 7490 Manual Circuito 7490 y 7447 Digital Counter AutomaticDocument4 pagesDokumen - Tips - Contador 7490 Manual 7490 Manual Circuito 7490 y 7447 Digital Counter AutomaticRuben AlonsoNo ratings yet

- Internship Presentation Vlsi Soc Design Using Verilog HDL: Name: Suraj Patel Roll No.: 2100910319008Document15 pagesInternship Presentation Vlsi Soc Design Using Verilog HDL: Name: Suraj Patel Roll No.: 2100910319008Suraj PatelNo ratings yet

- Ccs Picc Pic16f87x Tutorial - 1cDocument48 pagesCcs Picc Pic16f87x Tutorial - 1cHuu Hau NguyenNo ratings yet

- Signal and Systems Student Lab Observation Manual For B.E/B.TechDocument100 pagesSignal and Systems Student Lab Observation Manual For B.E/B.TechSrikanth ImmaReddyNo ratings yet

- MEAF - 66372 3 en 0801Document87 pagesMEAF - 66372 3 en 0801Andrew Sison92% (12)

- FlexiPanels User ManualDocument312 pagesFlexiPanels User ManualChris Olson100% (1)

- Pinouts and Communication Protocols for Delta DOP HMI SeriesDocument136 pagesPinouts and Communication Protocols for Delta DOP HMI SeriesramdarkmasterNo ratings yet

- DE10-Lite User Manual PDFDocument74 pagesDE10-Lite User Manual PDFFelix GonzalezNo ratings yet

- Digital Logic Gates ExplainedDocument24 pagesDigital Logic Gates ExplainedEmilia KullutweNo ratings yet

- Ds-7200Huhi-K1 Series Turbo HD DVR: Features and FunctionsDocument3 pagesDs-7200Huhi-K1 Series Turbo HD DVR: Features and FunctionsdamindaNo ratings yet

- Anritsu MP1552B SDH PDH ATM Analyzer Data SheetDocument11 pagesAnritsu MP1552B SDH PDH ATM Analyzer Data Sheetsilvajc30No ratings yet

- AC Circuit Analysis - KVL - KCLDocument24 pagesAC Circuit Analysis - KVL - KCLjenniferNo ratings yet

- 4G MOBILE CommunicationsDocument10 pages4G MOBILE CommunicationsAnkit SrivastavaNo ratings yet

- 5kva Ferrite Core Inverter CircuitDocument30 pages5kva Ferrite Core Inverter CircuitIoannis PerperisNo ratings yet

- BF254 BF255Document3 pagesBF254 BF255rrr2013No ratings yet