Professional Documents

Culture Documents

Von Neumann Havard

Uploaded by

Mohd Zahiruddin ZainonCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Von Neumann Havard

Uploaded by

Mohd Zahiruddin ZainonCopyright:

Available Formats

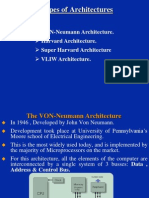

COMPUTER ARCHITECTURE &

ORGANIZATION

CHAPTER 3

Von Neumann and Harvard Architecture

m

o

h

d

.

r

i

z

a

l

@

p

s

m

z

a

.

e

d

u

.

m

y

VON NEUMANN ARCHITECTURE

John Von Neumann's: One shared memory for instructions (program)

and data with one data bus and one address bus between processor

and memory.

Instructions and data have to be fetched in sequential order (known

as the Von Neuman Bottleneck), limiting the operation bandwidth

Its design is simpler than that of the Harvard architecture. It is

mostly used to interface to external memory.[1]

m

o

h

d

.

r

i

z

a

l

@

p

s

m

z

a

.

e

d

u

.

m

y

VON NEUMANN MACHINE OPERATION[2]

The Von Neumann consist of five major

component. Thick arrow represent data paths.

Thin arrow represent control path.

m

o

h

d

.

r

i

z

a

l

@

p

s

m

z

a

.

e

d

u

.

m

y

The input unit provides instructions and data to the

system, which are subsequently stored in the Memory

Unit.

The instruction and data are processed by the

Arithmetic and Logic Unit (ALU) under the direction

of the Control Unit.

The result are sent to the Output Unit.

The ALU and control unit are frequently referred to

collectivity as the Central Processing Unit (CPU).

m

o

h

d

.

r

i

z

a

l

@

p

s

m

z

a

.

e

d

u

.

m

y

The execution of a stored program is the most

important aspect of the Von Neumann model.

A program is stored in the computers memory along

with the data to be processed.

Under von Neumann architecture, the CPU can be

either reading an instruction or reading/writing data

from/to the memory. Both cannot occur at the same

time since the instructions and data use the same bus

system

m

o

h

d

.

r

i

z

a

l

@

p

s

m

z

a

.

e

d

u

.

m

y

HARVARD ARCHITECTURE

The Harvard architecture is a computer

architecture with physically separate storage and

signal pathways for instructions and data.

The term originated from the Harvard Mark I relay-

based computer, which stored instructions on punched

tape (24 bits wide) and data in electro-mechanical

counters

m

o

h

d

.

r

i

z

a

l

@

p

s

m

z

a

.

e

d

u

.

m

y

In a computer using the Harvard architecture, the

CPU can both read an instruction and perform a data

memory access at the same time, even without a

cache. A Harvard architecture computer can thus be

faster for a given circuit complexity because

instruction fetches and data access do not contend for

a single memory pathway.

Also, a Harvard architecture machine has distinct

code and data address spaces: instruction address

zero is not the same as data address zero. Instruction

address zero might identify a twenty-four bit value,

while data address zero might indicate an eight bit

byte that isn't part of that twenty-four bit value.

m

o

h

d

.

r

i

z

a

l

@

p

s

m

z

a

.

e

d

u

.

m

y

DIFFERENTIATION OF VON NEUMANN AND

HARVARD ARCHITECTURE.

Von Neumann Havard

Physical

Share a memory and

bus@pathway for program

and data storage.

Separate memory and bus

@ pathway for program and

data storage.

Usage For normal and low

performance purpose and

application.

For high performance

purpose and application.

m

o

h

d

.

r

i

z

a

l

@

p

s

m

z

a

.

e

d

u

.

m

y

Von Neumann Havard

Reading/

writing

data/

instruction

Under pure von Neumann

architecture the CPU can be

either reading an instruction

or reading/writing data

from/to the memory. Both

cannot occur at the same

time since the instructions

and data use the same bus

system.

CPU can both read an

instruction and perform a data

memory access at the same

time, even without a cache. A

Harvard architecture computer

can thus be faster for a given

circuit complexity because

instruction fetches and data

access do not contend for a

single memory pathway.

Economical Economical,because using a

single memory and bus for

both data and instruction.

Not economical,because using

different memory and bus for

data and instruction.

Speed Low speed performance High speed performance

m

o

h

d

.

r

i

z

a

l

@

p

s

m

z

a

.

e

d

u

.

m

y

STRENGTH AND WEAKNESS OF VON

NEUMANN ARCHITECTURE

Strength Weakness

Economical : Share a memory

and bus for data and

instruction.

Low speed to read/write

data/instruction.

m

o

h

d

.

r

i

z

a

l

@

p

s

m

z

a

.

e

d

u

.

m

y

REFERENCES

[1] search for Von Neumann Architecture

http://www.elec.canterbury.ac.nz/PublicArea/Staf

f/hof/p10-embed/p10-tutorial/p12.html

[2]Computer Architecture And Organization; An

Integrated Approach, Miles Murdocca and

Vincent Heuring, John Wiley & Sons,Inc.

m

o

h

d

.

r

i

z

a

l

@

p

s

m

z

a

.

e

d

u

.

m

y

You might also like

- Computer Architecture AssignDocument9 pagesComputer Architecture AssignZawar HussainNo ratings yet

- The Von NeumannDocument5 pagesThe Von NeumannPluvio PhileNo ratings yet

- Harvard Architecture: Memory DetailsDocument11 pagesHarvard Architecture: Memory DetailsWan ShahmisufiNo ratings yet

- Harvard Architecture PDFDocument3 pagesHarvard Architecture PDFsathkar220% (1)

- 65608543Document4 pages65608543Van SinNo ratings yet

- Harvard Architecture Vs Von Neumann ArchitectureDocument2 pagesHarvard Architecture Vs Von Neumann Architecturena_hariprsadNo ratings yet

- Modified Harvard Architecture - Wikipedia, The Free Encyclopedia PDFDocument4 pagesModified Harvard Architecture - Wikipedia, The Free Encyclopedia PDFbeta2009No ratings yet

- Micro Controller ArchitectureDocument4 pagesMicro Controller ArchitectureMichaelDyksonNo ratings yet

- Activity 2 CPE07Document3 pagesActivity 2 CPE07Ralstine Jane IgneNo ratings yet

- Unit 1Document9 pagesUnit 1Harikrishnan NairNo ratings yet

- Computer ArchitectureDocument2 pagesComputer ArchitectureadonisNo ratings yet

- Harvard ArchitectureDocument3 pagesHarvard Architecturebalu4allNo ratings yet

- Difference Between Harvard and Princeton or Von Neumann ArchitectureDocument3 pagesDifference Between Harvard and Princeton or Von Neumann ArchitectureTarek Bin Zahid67% (3)

- Von Neumann and Harvard ArchitectureDocument13 pagesVon Neumann and Harvard ArchitectureYuvraj KatwalNo ratings yet

- Von Neumann Vs Harvard ArchitectureDocument8 pagesVon Neumann Vs Harvard ArchitectureHarry DabasNo ratings yet

- Von Neuman ArchitectureDocument4 pagesVon Neuman ArchitectureAmeenNo ratings yet

- Asynchronous IIIDocument5 pagesAsynchronous IIIJiever AustriaNo ratings yet

- Processors Used in SOCsDocument25 pagesProcessors Used in SOCsA B ShindeNo ratings yet

- Coa Activity-2Document1 pageCoa Activity-2Althea IgnacioNo ratings yet

- VonneumanDocument8 pagesVonneumanJayson TibayanNo ratings yet

- Harvard ArchiDocument10 pagesHarvard ArchiWin RevansNo ratings yet

- Von Neumann ArchitectureDocument3 pagesVon Neumann Architectureapi-477098244No ratings yet

- Microprocessor and Assembly Language: Lecture-2-Computer ArchitectureDocument21 pagesMicroprocessor and Assembly Language: Lecture-2-Computer ArchitectureIqraNo ratings yet

- Lect 3Document15 pagesLect 3Blaser TacticalNo ratings yet

- Architecture, Is A: First Draft of A Report On The EDVACDocument1 pageArchitecture, Is A: First Draft of A Report On The EDVACrijoiNo ratings yet

- B21ai054 Coa CPDocument2 pagesB21ai054 Coa CPGARNEPALLI RAHULNo ratings yet

- B.ram Lecture 1 2Document11 pagesB.ram Lecture 1 2Yamini GollepallyNo ratings yet

- Harvard ArchitectureDocument4 pagesHarvard ArchitectureminchenggoNo ratings yet

- What Is The Difference Between A Von NeumannDocument2 pagesWhat Is The Difference Between A Von NeumannYogendra UikeyNo ratings yet

- Brief Intro Abt Von-Neumann and Harvard ArchitectureDocument6 pagesBrief Intro Abt Von-Neumann and Harvard ArchitectureAnonymous U8awvgZ3pDNo ratings yet

- Microprocessor NotesDocument44 pagesMicroprocessor NotesMag CreationNo ratings yet

- 3.2.4 Architecture of The DSPDocument4 pages3.2.4 Architecture of The DSPawanitNo ratings yet

- v3 A-Level Presentation - 01 Computer Architecture Auto-Saved Auto-SavedDocument63 pagesv3 A-Level Presentation - 01 Computer Architecture Auto-Saved Auto-SavedYi-Sin Lin - OXF.StudentNo ratings yet

- Computer Organization and ArchitectureDocument12 pagesComputer Organization and ArchitectureNeel RavalNo ratings yet

- Von-Neumann Architecture Vs Harvard Architecture: February 2019Document6 pagesVon-Neumann Architecture Vs Harvard Architecture: February 2019MnshNo ratings yet

- DSP Architecture PDFDocument3 pagesDSP Architecture PDFsumit valsangkarNo ratings yet

- Computer Architecture 2Document6 pagesComputer Architecture 2Clovisprom 2003No ratings yet

- University of South Asia - Computer Architecture Project Proposal The Warp Computer Name: Faseeh Ur Rehman Roll No: B-20010Document5 pagesUniversity of South Asia - Computer Architecture Project Proposal The Warp Computer Name: Faseeh Ur Rehman Roll No: B-20010haiderNo ratings yet

- Computer Architecture 2Document6 pagesComputer Architecture 2Kiapuch Airuch CuophiNo ratings yet

- Von Neumann Vs HarvardDocument3 pagesVon Neumann Vs Harvardom shirdhankarNo ratings yet

- What Is The Difference Between A Von Neumann Architecture and A Harvard Architecture?Document2 pagesWhat Is The Difference Between A Von Neumann Architecture and A Harvard Architecture?Asher N GonzalezNo ratings yet

- What Is The Difference Between A Von Neumann Architecture and A Harvard Architecture? PDFDocument2 pagesWhat Is The Difference Between A Von Neumann Architecture and A Harvard Architecture? PDFAsher N GonzalezNo ratings yet

- Von Neumann ArchitectureDocument30 pagesVon Neumann ArchitectureRochaNavarroNo ratings yet

- Chapter 02Document63 pagesChapter 02Hisham Al-SagerNo ratings yet

- Computer EvolutionDocument27 pagesComputer EvolutionNihash Reddy0% (1)

- Ashish Meena 235CO11Document2 pagesAshish Meena 235CO11officeguy1234No ratings yet

- Von Newman FDDocument4 pagesVon Newman FDapi-3725139100% (2)

- Architecture of DSP ProcessorsDocument13 pagesArchitecture of DSP ProcessorsSugumar Sar DuraiNo ratings yet

- The Anatomy of A ComputerDocument2 pagesThe Anatomy of A ComputerIlieTaranuNo ratings yet

- Architecture: Architecture Is Those Attributes Visible To The Programmer. - Instruction Set, Number of Bits Used For DataDocument3 pagesArchitecture: Architecture Is Those Attributes Visible To The Programmer. - Instruction Set, Number of Bits Used For DataAkash MiaNo ratings yet

- Difference Between Von Neumann and Harvard ArchitectureDocument4 pagesDifference Between Von Neumann and Harvard Architectureramadan hundessaNo ratings yet

- Von Neumann ModelDocument5 pagesVon Neumann ModelTrần Trung HiếuNo ratings yet

- Von Neumann and HarvardDocument11 pagesVon Neumann and HarvardWINORLOSENo ratings yet

- Von-Neumann Vs Harvard Architecture - Differences & UsesDocument14 pagesVon-Neumann Vs Harvard Architecture - Differences & UsesbigumangabaNo ratings yet

- Coa D2.1Document31 pagesCoa D2.1Csk CskNo ratings yet

- Overview of IAS Computer Function - Organization of The Von Neumann Machine and Harvard ArchitectureDocument18 pagesOverview of IAS Computer Function - Organization of The Von Neumann Machine and Harvard Architecturesammy CNo ratings yet

- Types of DSP ArchitecturesDocument45 pagesTypes of DSP ArchitecturesParesh Sawant100% (3)

- CPU ArchitectureDocument14 pagesCPU ArchitectureTrynosNo ratings yet

- Datasheet PDFDocument1 pageDatasheet PDFMohd Zahiruddin ZainonNo ratings yet

- Undergraduate Academic - Guidelines2Document42 pagesUndergraduate Academic - Guidelines2Mohd Zahiruddin ZainonNo ratings yet

- Amplitude ModulationDocument11 pagesAmplitude ModulationMohd Zahiruddin ZainonNo ratings yet

- Shift Register: Flip Flop ApplicationDocument4 pagesShift Register: Flip Flop ApplicationMohd Zahiruddin ZainonNo ratings yet

- RAM WaveformDocument8 pagesRAM WaveformMohd Zahiruddin Zainon0% (1)

- Pipe LiningDocument44 pagesPipe LiningMohd Zahiruddin ZainonNo ratings yet

- Memory ElementDocument7 pagesMemory ElementMohd Zahiruddin ZainonNo ratings yet

- Jawapan FREEDocument1 pageJawapan FREEMohd Zahiruddin ZainonNo ratings yet

- LolDocument4 pagesLolMohd Zahiruddin ZainonNo ratings yet

- 5 3 PDFDocument22 pages5 3 PDFMohd Zahiruddin ZainonNo ratings yet

- Department Session Course Code Topic Assessment: Page 1 of 3Document3 pagesDepartment Session Course Code Topic Assessment: Page 1 of 3Mohd Zahiruddin ZainonNo ratings yet

- PW 5Document8 pagesPW 5Mohd Zahiruddin ZainonNo ratings yet

- 5.5 Connecting Memory Chips To A Computer BusDocument11 pages5.5 Connecting Memory Chips To A Computer BusMohd Zahiruddin ZainonNo ratings yet

- C-Lab - 01 GDocument17 pagesC-Lab - 01 GMohd Zahiruddin ZainonNo ratings yet

- Jawapan FREEDocument1 pageJawapan FREEMohd Zahiruddin ZainonNo ratings yet

- C-Lab 04 HahaDocument12 pagesC-Lab 04 HahaMohd Zahiruddin ZainonNo ratings yet

- C-Lab - 02 LolDocument6 pagesC-Lab - 02 LolMohd Zahiruddin ZainonNo ratings yet

- Sets Catalog BaruDocument16 pagesSets Catalog BaruMohd Zahiruddin ZainonNo ratings yet

- C-Lab 03 LolDocument9 pagesC-Lab 03 LolMohd Zahiruddin ZainonNo ratings yet

- Topic 3Document6 pagesTopic 3Mohd Zahiruddin ZainonNo ratings yet

- Activity 1: Data Transfer Instructions ProceduresDocument7 pagesActivity 1: Data Transfer Instructions ProceduresMohd Zahiruddin ZainonNo ratings yet

- Sets Catalog BaruDocument16 pagesSets Catalog BaruMohd Zahiruddin ZainonNo ratings yet

- Activity 1: Data Transfer Instructions ProceduresDocument7 pagesActivity 1: Data Transfer Instructions ProceduresMohd Zahiruddin ZainonNo ratings yet

- Output Statement - Printf : Input Statements Are Used For AcceptingDocument4 pagesOutput Statement - Printf : Input Statements Are Used For AcceptingMohd Zahiruddin ZainonNo ratings yet

- C Fundamentals: Electrical Engineering DepartmentDocument38 pagesC Fundamentals: Electrical Engineering DepartmentMohd Zahiruddin ZainonNo ratings yet

- Chapter 5Document21 pagesChapter 5Mohd Zahiruddin ZainonNo ratings yet

- Chapter4 Input and OutputDocument15 pagesChapter4 Input and Outputmfh273No ratings yet

- Manual Conditions File and Maybe Jobs Chapter 6selected Implementation Issues809Document4 pagesManual Conditions File and Maybe Jobs Chapter 6selected Implementation Issues809Ayan BanerjeeNo ratings yet

- Windows Win32 API WinmsgDocument1,114 pagesWindows Win32 API WinmsgAbetiou SN - سفيان ابطيوNo ratings yet

- LTE CR-7077 Operation GraphsDocument135 pagesLTE CR-7077 Operation GraphsAdil MuradNo ratings yet

- Development of Car Plate Number Generation System Using Tabu Search AlgorithmDocument3 pagesDevelopment of Car Plate Number Generation System Using Tabu Search Algorithmmafuz biolaNo ratings yet

- 2019-03-21 Edgecase Datafeed Article 89 2019-03-21 Stjohn Piano Creating A Bitcoin Transaction With Two InputsDocument75 pages2019-03-21 Edgecase Datafeed Article 89 2019-03-21 Stjohn Piano Creating A Bitcoin Transaction With Two InputsArdhiNo ratings yet

- Maintenance 63DXB PDFDocument102 pagesMaintenance 63DXB PDFPhilip CairnsNo ratings yet

- Software Update Without Using New FunctionsDocument88 pagesSoftware Update Without Using New FunctionsRamón F. Zapata SánchezNo ratings yet

- Zoomba: A Micro-Language For Jvms .Document163 pagesZoomba: A Micro-Language For Jvms .San DeeptiNo ratings yet

- Prescriptive Analytics: Joseph R. EstillerDocument18 pagesPrescriptive Analytics: Joseph R. EstillerChristian Mark PalayNo ratings yet

- Panel 800 Version 6 Data SheetDocument6 pagesPanel 800 Version 6 Data SheetManuel Penafiel50% (2)

- CodersTrust Responsive Web Design - DecDocument2 pagesCodersTrust Responsive Web Design - DecclementNo ratings yet

- Yemensoft Onyx Pro - User's GuideDocument272 pagesYemensoft Onyx Pro - User's Guideyemensoft88% (8)

- BAdi2 For MM02Document14 pagesBAdi2 For MM02raju221756_843567682100% (1)

- History The Six Invariants of Spiral ModelDocument4 pagesHistory The Six Invariants of Spiral ModelsuhailNo ratings yet

- Wondershare Software Official Website - Multimedia, Utility, MobileDocument2 pagesWondershare Software Official Website - Multimedia, Utility, MobileDaniel VeraNo ratings yet

- Variable Vs Signal in VHDLDocument3 pagesVariable Vs Signal in VHDLOmkar RaneNo ratings yet

- Missing Crypto Timeline Draft 3 - April 2019 - KyleSGibsonDocument25 pagesMissing Crypto Timeline Draft 3 - April 2019 - KyleSGibsonKyle GibsonNo ratings yet

- Oracle® Life Sciences Data Hub: Installation GuideDocument51 pagesOracle® Life Sciences Data Hub: Installation GuideLamasat Specilized Advertising100% (1)

- 3com OfficeConnect NAS Users Manual 2000Document52 pages3com OfficeConnect NAS Users Manual 2000antonius0990No ratings yet

- NSLab 3Document4 pagesNSLab 3Ryan Goh100% (1)

- Lab 3.1 Configuring SDM On A RouterDocument34 pagesLab 3.1 Configuring SDM On A Routergargamel_220No ratings yet

- Ge22 (Edp Syllabus Summer)Document4 pagesGe22 (Edp Syllabus Summer)Daisy Jean Abas CastilloNo ratings yet

- 08 Ancrel TraitsDocument3 pages08 Ancrel TraitsEDUARDO ALCANTARA DUQUE DA SILVANo ratings yet

- DHCP Detailed Operation (En)Document13 pagesDHCP Detailed Operation (En)779482688No ratings yet

- APP GuidelineDocument116 pagesAPP GuidelineVelizar GerginovNo ratings yet

- Excel MacrosDocument2 pagesExcel MacrosSudarshan RaoNo ratings yet

- Data ONTAP 81 Upgrade and RevertDowngrade GuideDocument157 pagesData ONTAP 81 Upgrade and RevertDowngrade GuidePurushothama GnNo ratings yet

- Computer Standards & Interfaces: SciencedirectDocument20 pagesComputer Standards & Interfaces: SciencedirectSalam DamitNo ratings yet

- MSTK 10c - Preparing Quantitative and Qualitative Data For Entry - AnalysisDocument2 pagesMSTK 10c - Preparing Quantitative and Qualitative Data For Entry - AnalysisNaveed UllahNo ratings yet

- Netflix Assignment Week1 Shriansh SrivastavaDocument4 pagesNetflix Assignment Week1 Shriansh SrivastavaAbhishek Rahi100% (1)