Professional Documents

Culture Documents

Basics of CISC and RISC Machines: 171005 Embedded Systems Lecture 3 9/7/2013

Uploaded by

akbar_birbal887Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Basics of CISC and RISC Machines: 171005 Embedded Systems Lecture 3 9/7/2013

Uploaded by

akbar_birbal887Copyright:

Available Formats

9/9/2013

BasicsofCISC

andRISCmachines

171005EmbeddedSystems

Lecture3

9/7/2013

CISCProcessordetails

Beforedecidingwhichprocessor,designershouldthinkwhich

architecturefortheprocessortobeselected?

CISCandRISCarethepopulararchitecturewithmeritsand

demerits.

CISCwereprovidingakindofinstructionsthathelpedincompiler

designeasy!Andthatswhytheinstructionsetwassupportedwith

instructionsforcomplextaskandhencethetaskofcompileris

simplertoconverthighlevellanguageintomachinecodes!

Henceprocessorsweresoldearlierbasedonthecomplexitiesthey

canhandlewithinstructions,addressingmodesanddatatypes.

Butthisrequireshighernumberofgatesonthedietoimplement

complexinstructions.

Eventheexecutiontimeforalltheinstructionsarenotremaining

same!

9/9/2013

ThekindofactivitieshandledbyourCPUare:

InstructionandDatamovementbetweenCPUand

memory.

Executionofinstructions

ALUoperations

DatamovementbetweenCPUandmemoryasapartof

executionoftheinstructions.

DatamovementsbetweenregistersintheCPU

Wemustconsiderthedynamicuseofinstructions

inourprogram.

DynamicInstructionUsage

Around33%instructionsforALUoperationsand67%for

DatamovementandControlflowoperation!

Thistellsthatthemostimportantinstructionstooptimize

arethosewhicharedealingwithdatamovement.

9/9/2013

TypicalSequenceofOperationinCPU

Pipelining

WhatisPipelining?

Pipelininghelpsinfasterexecutionofthe

instructions.

9/9/2013

Read WritePipelineHazard

BranchPipelineHazard

9/9/2013

Problemsinpipeliningduringbranch

instructions.

Pipeliningprovesbetterifexecutiontimeofall

instructionsareuniform.

Itisdifficulttoimplementpipeliningforthe

complexinstructions.

HenceCISCarchitectureisnotinfavorof

achievingfasterexecutiononarchitecture

level.

Tobringuniformityinexecutiontimeforthesupportofpipelining:

Allinstructionweredesignedofbeingfixedlengthinamodified

architecture

Allinstructionsweredesignedsuchthattheyallexecuteinsametime

thatissinglecycleexecutionforpipelinebenefits.Thisleadtoavoiding

Complexinstructionandusingsimpleinstructions(Thatiswhy

ReducedInstructionSet).

Itisnotpossibletoachieveakindofexecutionwherememorydatais

read,processedandagainmodifiedinasinglecycleexecution.

HenceLoad StoreArchitecturewasdesignedwhichsupports

instructionswhichloadsamemorydataintoCPUorstoresCPU

registertomemoryinseparateinstructions.

Largeregisterwindowbankswasrequiredtooperateload store

instructionsefficiently.

Thewholedesignwascarriedoutbasedon32bitarchitecture.

9/9/2013

RISCAdvantages

CISCrequiredhighernumberofgatesondielevelfor

complexinstructionexecution.ButRISCsupports

simplerinstructionset.Henceitdealswithsmalldie

size.

Thishelpsinachievingreducedpowerconsumption.

Shorterdevelopmenttimeforthecpu.

Asimplerprocessorallowshighclockrateonthe

board;whileaCISCkindofmachineisrestrictedfor

theirhigherfrequencyofoperations.

CISCmachinesarehavingmicrocodeROMstodecode

theinstruction;whileRISCprocessorusingHardwired

logicwhichismuchfaster.

DisadvantagesofRISC

PoorcodedensityascomparedtoCISC.So,

highermemoryrequirementswillbetherein

turnhighermemorypowerconsumption.

X86codesarenotportable.

9/9/2013

ARMArchitecture

AcornRISCMachine(ARM)utilizedtheRISCarchitectureforembedded

applicationdevelopment.

FeaturesusedfromRISCarchitecture

ALoadstoreArchitecture

Fixedlength32bitinstructions

3addressinstructionformat(eg.addr0,r1,r2)

FeaturesRejected

RegisterWindows

DelayedBranches

Singlecycleexecutionofallinstruction(Thisisfoundtobepossibleonlyif

dataandinstructionmemoriesareseparate.InitiallyARMwasdesignedwith

VonNeuman Architecturewheredataandinstructionmemoriesare

different)

Featuresadded

ThumbInstructionsettoachievehighercodedensity

You might also like

- A2 Computer Science 9618 Paper 3 NotesDocument57 pagesA2 Computer Science 9618 Paper 3 NotesManav Maistry100% (1)

- RISC Vs CISCDocument13 pagesRISC Vs CISCBehin SamNo ratings yet

- CUDA IntroductionDocument71 pagesCUDA IntroductionSiddu S. KamatarNo ratings yet

- Parallel Processing Chapter - 2: Basics of Architectural DesignDocument29 pagesParallel Processing Chapter - 2: Basics of Architectural DesignGetu GeneneNo ratings yet

- Digital Electronics, Computer Architecture and Microprocessor Design PrinciplesFrom EverandDigital Electronics, Computer Architecture and Microprocessor Design PrinciplesNo ratings yet

- Computer Architecture MCQsDocument33 pagesComputer Architecture MCQsMs.Sangeetha Priya IT DepartNo ratings yet

- Risc and CiscDocument17 pagesRisc and CiscAyazNo ratings yet

- 1.1 Research Background: Project Report On 16-Bit RISC Processor - Sandeepani School of Embedded System DesignDocument14 pages1.1 Research Background: Project Report On 16-Bit RISC Processor - Sandeepani School of Embedded System DesignBoobalan DeiveeganNo ratings yet

- Computer Organzation and Architecture Question BankDocument10 pagesComputer Organzation and Architecture Question Bankmichael100% (2)

- Advanced computer architecture overviewDocument118 pagesAdvanced computer architecture overviewSharathMenonNo ratings yet

- Assembly IntroductionDocument31 pagesAssembly Introductionsohaibislam202No ratings yet

- Chapter 07 RISCDocument62 pagesChapter 07 RISCBinod SAdhikariNo ratings yet

- CSS 548 Joshua LoDocument13 pagesCSS 548 Joshua LoliuylNo ratings yet

- Presidency Univeristy,: School of Engineering Department of Computer Science & EngineeringDocument62 pagesPresidency Univeristy,: School of Engineering Department of Computer Science & EngineeringAneal SinghNo ratings yet

- Cisc & Risc: Mr. Sunanda DasDocument19 pagesCisc & Risc: Mr. Sunanda DasTowsif100% (1)

- Unit-1 (Module-1) : Introduction To MicrocontrollerDocument20 pagesUnit-1 (Module-1) : Introduction To MicrocontrollerRajendra PatelNo ratings yet

- Risc Cisc in Microcontroller and MicroprocessorDocument31 pagesRisc Cisc in Microcontroller and Microprocessormanvir kaurNo ratings yet

- Socunit 1Document65 pagesSocunit 1Sooraj SattirajuNo ratings yet

- Risc and CiscDocument20 pagesRisc and Ciscprathapreddy420No ratings yet

- Risc and Cisc: By: Farheen Masood Sania ShahzadDocument17 pagesRisc and Cisc: By: Farheen Masood Sania ShahzadAlia BashirNo ratings yet

- Core of Emb-SysDocument52 pagesCore of Emb-SysSushrut ZemseNo ratings yet

- TRIPS - An EDGE Instruction Set Architecture: Chirag Shah April 24, 2008Document35 pagesTRIPS - An EDGE Instruction Set Architecture: Chirag Shah April 24, 2008Engr Ayaz KhanNo ratings yet

- Risc and Cisc: Computer ArchitectureDocument17 pagesRisc and Cisc: Computer Architecturedress dressNo ratings yet

- Risc Vs CiscDocument24 pagesRisc Vs CiscRaj KumarNo ratings yet

- General IntroductionDocument29 pagesGeneral IntroductionMisrak kassahunNo ratings yet

- Risc and Cisc: by Eugene ClewlowDocument17 pagesRisc and Cisc: by Eugene ClewlowSampathhhhh Sai TadepalliNo ratings yet

- RISC and CISC - Eugene ClewlowDocument17 pagesRISC and CISC - Eugene Clewlowilg1No ratings yet

- Risc and Cisc: by Eugene ClewlowDocument17 pagesRisc and Cisc: by Eugene ClewlowRamnath PraveenNo ratings yet

- PPT4 - Module 1Document15 pagesPPT4 - Module 1sammy CNo ratings yet

- CISC Is An Acronym For Complex Instruction Set ComputerDocument44 pagesCISC Is An Acronym For Complex Instruction Set ComputerVantharAlaNo ratings yet

- Microprocess OR & Computer Architecture: 14CS253 / UE14CS253Document12 pagesMicroprocess OR & Computer Architecture: 14CS253 / UE14CS253Prathik GSNo ratings yet

- Computer Organization: Basic Structure of ComputerDocument59 pagesComputer Organization: Basic Structure of ComputersaiNo ratings yet

- Risc Vs Cisc 2 1424454141105114Document12 pagesRisc Vs Cisc 2 1424454141105114Sam RockvilleNo ratings yet

- AD Up Dig Design Be ADocument130 pagesAD Up Dig Design Be ATutul BanerjeeNo ratings yet

- L1 IntroductionDocument26 pagesL1 IntroductionMuhammad sohaibNo ratings yet

- Chapter 2 - Lecture 6 Risc vs. CiscDocument7 pagesChapter 2 - Lecture 6 Risc vs. CiscAlazar DInberuNo ratings yet

- Unit 1: Introduction To Embedded SystemDocument48 pagesUnit 1: Introduction To Embedded SystemDenise NelsonNo ratings yet

- Understanding Processors in 40 CharactersDocument8 pagesUnderstanding Processors in 40 CharactersSNo ratings yet

- Risc A Cisc PDocument10 pagesRisc A Cisc PAlexander KirosNo ratings yet

- Introduction MicroControllerDocument12 pagesIntroduction MicroControllerAbhijeet ShekharNo ratings yet

- Unit 5 (Coa) NotesDocument35 pagesUnit 5 (Coa) NotesmudiyalaruchithaNo ratings yet

- CISC Processors: (Complex Instruction Set Computing)Document3 pagesCISC Processors: (Complex Instruction Set Computing)Hari Krishna DNo ratings yet

- Stud CSA Processors Mod2 Part1Document64 pagesStud CSA Processors Mod2 Part1SHEENA YNo ratings yet

- Risc vs Cisc: Key DifferencesDocument8 pagesRisc vs Cisc: Key Differencesjjba93No ratings yet

- Coa 9Document4 pagesCoa 9adadaNo ratings yet

- Superscalar Architectures: COMP375 Computer Architecture and OrganizationDocument35 pagesSuperscalar Architectures: COMP375 Computer Architecture and OrganizationIndumathi ElayarajaNo ratings yet

- Module1 3-Ias Risc CiscDocument19 pagesModule1 3-Ias Risc CiscCharan ChowdaryNo ratings yet

- EC8791 Embedded and Real Time SystemsDocument78 pagesEC8791 Embedded and Real Time SystemsSivagami ManiNo ratings yet

- Lecture 18 - RICS and CISC PropertiesDocument8 pagesLecture 18 - RICS and CISC PropertiesPragya SinghNo ratings yet

- MOD1MCESDocument4 pagesMOD1MCESanandita chalamalasettiNo ratings yet

- UNIT 5 RISC ArchitectureDocument16 pagesUNIT 5 RISC ArchitectureKESSAVAN.M ECE20No ratings yet

- W5 - L3 - Inst Set Archi-RISC CISCDocument34 pagesW5 - L3 - Inst Set Archi-RISC CISCNeel RavalNo ratings yet

- Embedded Systems:: Hacking of Electronic EquipmentsDocument76 pagesEmbedded Systems:: Hacking of Electronic EquipmentsKailashi Chandra SekharNo ratings yet

- COA - Unit 1 An IntroductionDocument26 pagesCOA - Unit 1 An IntroductionDevika csbsNo ratings yet

- CSE 675.02: Introduction To Computer Architecture: Instructor: Roger CrawfisDocument37 pagesCSE 675.02: Introduction To Computer Architecture: Instructor: Roger CrawfisJamsher BhanbhroNo ratings yet

- CISC Vs RISCDocument20 pagesCISC Vs RISCShopon PalNo ratings yet

- 1-Introduction 1.0 Motivation: Which Is Like A"blueprint" For Building The Machine)Document63 pages1-Introduction 1.0 Motivation: Which Is Like A"blueprint" For Building The Machine)Manikanta Raja MedapatiNo ratings yet

- CISC vs RISC: Understanding Complex and Reduced Instruction Set ComputersDocument18 pagesCISC vs RISC: Understanding Complex and Reduced Instruction Set Computerswelcome to my worldNo ratings yet

- CS-424/580A Microcontrollers & RoboticsDocument21 pagesCS-424/580A Microcontrollers & Roboticsprabhuswamiji6160No ratings yet

- Embedded Systems Lecture on Design Challenges and Processor TechnologiesDocument54 pagesEmbedded Systems Lecture on Design Challenges and Processor TechnologiesHafizNo ratings yet

- What Is RISC and CISC Architecture - EdgefxkitsDocument11 pagesWhat Is RISC and CISC Architecture - EdgefxkitsjeyasuthanjNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- DCN FileDocument12 pagesDCN Fileakbar_birbal887No ratings yet

- DWDM CienaDocument23 pagesDWDM CienaRicardo Torres TorricoNo ratings yet

- Project IDocument2 pagesProject Isuneerav17No ratings yet

- Evaluation Scheme of (Industry Defined Project / User Defined Projects) For University Project Exam For 8th Semester in B.EDocument2 pagesEvaluation Scheme of (Industry Defined Project / User Defined Projects) For University Project Exam For 8th Semester in B.EEr Pradip PatelNo ratings yet

- j24 Bolo-07 Infphy 2012Document6 pagesj24 Bolo-07 Infphy 2012akbar_birbal887No ratings yet

- Annex UredDocument1 pageAnnex UredRajesh UpadhyayNo ratings yet

- Gsm-Physical and Logical ChannelsDocument5 pagesGsm-Physical and Logical ChannelsOmair MirNo ratings yet

- MSOR 161601 Assignment-1Document3 pagesMSOR 161601 Assignment-1akbar_birbal887No ratings yet

- Computer Oriented Statistical MethodsDocument3 pagesComputer Oriented Statistical Methodschetanking4033% (3)

- (85958437) Ffo - NewDocument81 pages(85958437) Ffo - Newakbar_birbal887No ratings yet

- DWDM 2Document16 pagesDWDM 2akbar_birbal887No ratings yet

- Reality TechDocument68 pagesReality Techakbar_birbal887No ratings yet

- Long 5 AAAI12WS OpenGovernmentDataforTacklingCorruptionJuly2012Document13 pagesLong 5 AAAI12WS OpenGovernmentDataforTacklingCorruptionJuly2012akbar_birbal887No ratings yet

- List of ExperimentDocument2 pagesList of Experimentakbar_birbal887No ratings yet

- SeminarDocument3 pagesSeminarakbar_birbal887No ratings yet

- HAPTIC TECHNOLOGY (WWW - Projectsforyou.co - CC)Document14 pagesHAPTIC TECHNOLOGY (WWW - Projectsforyou.co - CC)akbar_birbal887No ratings yet

- FlardrumsDocument1 pageFlardrumsParan JainNo ratings yet

- SeminarDocument3 pagesSeminarakbar_birbal887No ratings yet

- FlarDocument1 pageFlarakbar_birbal887No ratings yet

- SeminarDocument3 pagesSeminarakbar_birbal887No ratings yet

- Unit-5 (Coa) NotesDocument33 pagesUnit-5 (Coa) NotesyashNo ratings yet

- MCES-21CS43 Module-1 NotesDocument14 pagesMCES-21CS43 Module-1 NotesEdu techNo ratings yet

- COA511S Supplementary TEST MemoDocument6 pagesCOA511S Supplementary TEST MemoLavinia DongwiNo ratings yet

- Impetus Gurukul Revision Class-1-Number System and Computer Organization-1Document6 pagesImpetus Gurukul Revision Class-1-Number System and Computer Organization-1sarol90668No ratings yet

- Microprocessor and Programming 4TH SEM CM-IfDocument174 pagesMicroprocessor and Programming 4TH SEM CM-IfAbha SinghNo ratings yet

- COA Mod 3Document25 pagesCOA Mod 3Rosh Roy GeorgeNo ratings yet

- Computer Organization - Functional Units of A ComputerDocument31 pagesComputer Organization - Functional Units of A ComputerKiruthiga PrabakaranNo ratings yet

- Chapter 4 (Processors and Memory Hierarchy)Document17 pagesChapter 4 (Processors and Memory Hierarchy)Kushal ShNo ratings yet

- A 30-b Integrated Logarithmic Number System Processor - 91Document8 pagesA 30-b Integrated Logarithmic Number System Processor - 91Phuc HoangNo ratings yet

- B - Tech - (CSE) 2nd Year Final SyllabusDocument37 pagesB - Tech - (CSE) 2nd Year Final Syllabussarang jamwalNo ratings yet

- Design of 32-Bit Risc Processor and Efficient VerificationDocument6 pagesDesign of 32-Bit Risc Processor and Efficient VerificationPallavi DikshitNo ratings yet

- Pipeline and Memory ConceptsDocument22 pagesPipeline and Memory Conceptsanilnaik287No ratings yet

- Reserved: Basic Structure of Computers and Instruction SetDocument20 pagesReserved: Basic Structure of Computers and Instruction SetJuanNo ratings yet

- ACA Assignment: Name: Anjali Singh Roll No.: 10001012017 Semester: 7th Class: CSE-2Document4 pagesACA Assignment: Name: Anjali Singh Roll No.: 10001012017 Semester: 7th Class: CSE-2Disha goyalNo ratings yet

- ARM Organization and Implementation: Aleksandar MilenkovicDocument37 pagesARM Organization and Implementation: Aleksandar Milenkovicarthicse100% (1)

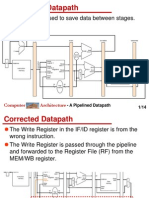

- A Pipelined Datapath: Resisters Are Used To Save Data Between StagesDocument14 pagesA Pipelined Datapath: Resisters Are Used To Save Data Between StagesJohnDaGRTNo ratings yet

- Project Review On Design & Implementation of Low Power 32-Bit Risc ProcessorDocument3 pagesProject Review On Design & Implementation of Low Power 32-Bit Risc ProcessorKedhar MallaNo ratings yet

- Lecture 1 - Introduction To ARMDocument30 pagesLecture 1 - Introduction To ARMAnonymous JZSeM82IbVNo ratings yet

- 2.1: Advanced Processor Technology: Qn:Explain Design Space of Processor?Document29 pages2.1: Advanced Processor Technology: Qn:Explain Design Space of Processor?ripcord jakeNo ratings yet

- CSO Lecture Notes Unit - 5Document11 pagesCSO Lecture Notes Unit - 5Naman PatidarNo ratings yet

- Lecture 13: Trace Scheduling, Conditional Execution, Speculation, Limits of ILPDocument21 pagesLecture 13: Trace Scheduling, Conditional Execution, Speculation, Limits of ILPBalasubramanian JayaramanNo ratings yet

- Manual PipeliningDocument12 pagesManual Pipeliningrktiwary256034No ratings yet

- CSC 200 INTRODUCTIONDocument18 pagesCSC 200 INTRODUCTIONbenjamin onumNo ratings yet

- HPC Question Bank Modules 1-5Document3 pagesHPC Question Bank Modules 1-5Celex VargheseNo ratings yet

- Assignment 2 SolutionDocument4 pagesAssignment 2 SolutionAaliya Ali Abdul0% (1)

- CPU Id and TshootingDocument60 pagesCPU Id and TshootingDrift GeeNo ratings yet

- Influence of Branch Mispredictions On Sorting AlgorithmsDocument88 pagesInfluence of Branch Mispredictions On Sorting AlgorithmsAnonymous DC0H8ymVNo ratings yet