Professional Documents

Culture Documents

FPGA

Uploaded by

u110010Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

FPGA

Uploaded by

u110010Copyright:

Available Formats

1.1.

Modulo adder:

In this subsection modular adders have been described. The

modulo adder is one of the basic important arithmetic units in

RNS operation [16].

The basic idea of modulo addition of any two numbers X and

Y with respect to modulus m is

|

|

(11)

= X+Y-m

: X+Y m

Where 0 X, Y< m.

The basic implementation of equation (11) is shown in fig: 3.

After first addition the output S is directly connected to the

first input of the MUX and again the output S is also

connected to the input of the 2nd conventional adder whose

another input is complement of m ( ). The output of the 2nd

adder S-m is connected to the next input of the previous

MUX and carry out of the 2nd adder is directly connected to

the select line of this MUX. The whole idea is that if

is 0

means X+Y< m and if

is 1 means X+Y m.

X

Y

S

M

U

X

Adder

Adder

S-m

r1

y1

y

r

r2

Merge

Split

ROM

y2

(n n)

r3

y3

Fig: 4 RNS divider circuit

2.

PROPOSED ARCHITECTURE

2.1. ROM based RNS 1D IWT using lifting scheme:

In this section, we will first propose a novel ROM based

RNS architecture for 1D 5/3 IWT using lifting scheme. In this

architecture, three basic building blocks which will repeat for

each and every level of decomposition [16]. In these three

blocks, the split block is very simple and easy to implement.

The job of this block is to separate the input samples into two

parts: one is even and another is odd. The diagram of the split

block is shown in fig 5. But implement the other two blocks

(predict and update) are more critical than first one. A new

implemented architecture is designed by pipeline technique.

Fig: 3 basic modulo adder circuit

1.2. Modulo divider:

Derive and implementation of RNS division is really difficult

and this is also the drawback of RNS. If the number divides

with a fixed integer number and the result is also an integer

number then it is little bit easier to implement by using ROM.

ROM based approach we can only use when any kind of

architecture is difficult to implement by using conventional

method and FPGA is a best platform where ROM is very easy

to use.

The main logic behind this architecture is that we consider a

number r (in RNS domain it is r1, r2 and r3) which divides by

an integer number n and its result is also an integer number

y. Again output y splits into y1, y2, y3 in RNS domain. The

input address of the ROM is the number r which is divided

by n and the output of each corresponding address is the

result of RNS division. The figure-4 shown the modulo

divider circuit.

Fig 5: implemented split block

2.2. Implemented architecture of RNS based predict block

for 1-level 1-D 5/3 lifting DWT:

The implemented RNS based predict block for 1-level 1-D

5/3 lifting DWT is designed to receive four even input

samples and generate four outputs which is the wavelet

coefficient as the error in predicting the odd samples from

even samples based on given four formulas:

)

D1=D1 - [ (

].. .(10)

D2=D2 - [ (

]... (11)

D3=D3 - [ (

]... (12)

D4=D4 - [ (

]... (13)

Where D1, D2, D3, D4 are odd samples and S1, S2, S3, S4 are

even samples which is generate after passing the split block.

To implement these basic formulas, we have used 6shift

registers to store the even and odd samples for 3 different

modules (m1, m2, m3). Each shift register has two outputs

which are connected with modulo adder and the outputs of 4

bits three modulo adders are merged to generate a 12 bits

unique number. To avoid the critical RNS division, we use a

)

1212 bits ROM which is solved the equation [ (

] and round off and give an integer number. Then the output

of ROM is connected with splitter whose job is to split the 12

bits into three 4 bits. These 4 bits numbers are again connected

to the modulo subtractor (mainly use modulo 2s complement

adder) whose another input is attached with another shift

register and store the data in same location. The diagram of

the proposed RNS based predicts block of lifting scheme is

shown in fig 9.

2.3. Implemented RNS based update block for 1-level 1-D

5/3 lifting DWT:

The design of the implemented RNS based update block

for 1-level 1-D 5/3 lifting DWT is exactly same as Predict

block, but this block accepts odd samples and using update

operator it generates scaling coefficient to the original signal.

The predict block is implemented by using basic four

equations to solve 5/3 lifting DWT [5].

S1= S1 + [ (

].... (14)

S2 = S2 + [ (

]..... (15)

S3 = S3 + [ (

].. (16)

S4 = S4 +[ (

]. (17)

Where D0=0, D1, D2, D3, D4 are odd samples and S1, S2, S3,

S4 are even samples which is generate after passing the split

block [16].

The operation of this block is exactly same as predict block

but the 1212 bits ROM evaluate the value of

)

equation (

and round off the value to make an

integer number. The diagram of the proposed architecture is

shown in fig 10.

After 1-level decomposition, the output of the update block

has again connected to the split block. The rest of blocks are

used in same fashion of the first level. We will get the final

output after 3-level decomposition.

Finally, the output of the both filter bank and lifting

architecture is again converted by signed RNS to binary

decoder circuit using CRT technique.

Fig: 9 implemented RNS based predict block for LS

Fig: 10 implemented RNS based update block for LS

3.

EXPERIMENTAL RESULT

In this section, the result reported for the performance

comparison of the one level decomposing RNS based 5/3

DWT using lifting scheme and filter bank architectures

include evaluation in term of the number of ROM multipliers,

the number of adders, shift registers, computational time and

the consume power during performance. Firstly, we will

analysis the performance of the proposed architecture. The

computational time of both circuits has been observed at the

same internal clock rate and can easily understand that the

lifting scheme is more efficient for high speed applications. If

we discuss about the hardware utilization, the RNS based

lifting structure is reduced the ROM multipliers, mod adders

and shift registers significantly. But the other hand the same

lifting scheme is not a power efficient circuit when it again

compare with filter bank scheme .Every module in our

proposed architecture has 100% hardware utilization. The

detail comparison of results are list in table 2 from which it is

clear that our proposed RNS based lifting structure is more

efficient to other in term of hardware utilization and time

delay.

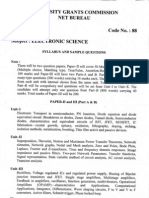

TABLE 2

Comparison of resource utilization summary:

Proposed

architecture

Mod

adders

Shift

registers

ROM

multiplier

Delay

(ns)

Power

(w)

RNS based

FB Scheme

18

24

6.332

0.586

RNS based

Lifting

Scheme

4.180

1.332

Hardware Utilization of 1-level

decomposition(FB & LS)

30

25

20

15

10

5

0

Adder

ROM

multiplier

Filter Bank

Shift Register

Lifting Scheme

Fig 11 hardware utilization of 1-level decomposition of filter

bank and lifting scheme

Timing & Power Analysis

7

6

5

4

3

2

1

0

Power(W)

Delay(nS)

Filter bank

Lifting Scheme

Fig 12 comparison of timing delay and power of FB and LS

4.

CONCLUSION

In this paper, new RNS based architectures of lifting

scheme and filter bank for DWT have been implemented. The

main contribution of the implemented architectures is divided

into three parts. First of all, we have implemented an efficient

reconfigurable RNS based filter bank for 5/3 DWT which

takes less time and power as compared to binary filter bank.

Secondly we represent a novel architecture of RNS based

lifting scheme for 1-D 5/3 DWT. This lifting structure has

been designed to modify the existing binary lifting structure in

terms of complexity and delay and also solve the problem of

implementing the critical RNS divider circuit. Finally, we

have compared the two different efficient structures and

analyzed their performances.

The experimental results demonstrate that the proposed

RNS based lifting structure is better than the RNS based filter

bank in term of speed, power and complexity. These proposed

architectures could be very efficient alternatives for high

speed and low power DSP; communication based applications

and is also suitable for VLSI implementation.

5.

REFFERENCES

[1] G. Quellec, M. Lamard, G. Cazuguel, B.Cochener, and C. Roux,

"Adaptive Non separable Wavelet Transform via Lifting and its

Application to Content-Based Image Retrieval," Image Processing,

IEEE Transactions on, vol.19, no.1, pp.25-35, Jan. 2010.

[2] S.L. Linfoot, Wavelet families for orthogonal wavelet division

multiplex, Electronics Letters,28th August 2008, Vol.44.No.18.

[3] C. V. Bouwel, Wavelet Packet Based Multicarrier Modulation

IEEE Communications and Vehicular Technology, SCVT 200, pp.

131-138, 2000.

[4] W. Sweldens,The Lifting Scheme: A custom-design

construction of biorthogonal wavelet, J. Appl. Comp. Harm. Anal.,

Vol.3, no.2, pp. 186-200, 1996.

[5] I. Daubechies and W. Sweldens, Factoring wavelet transforms

into Lifting steps, tech. rep., Bell Laboratories, 1996.

[6] W. Ding, F. Wu, S. Li, Lifting-based wavelet transform with

directionally spatial prediction, Picture Coding Symposium 2004,

USA, Dec. 2004.

[7] O.N. Gerek, A.E. Cetin, A 2D orientation-adaptive prediction

filter in lifting structures for image coding, IEEE Trans. Image

Process., vol.15, no. 1, Jan 2006 .

[8] T. Wedi, Adaptive interpolation filters and high-resolution

displacements for video coding, IEEE Trans. Circuits Syst. Video

Technol., Vol.16, No.4, pp.484-491, April 2006.

[9 R. Xiong, F. Wu, J.Xu, S. Li and Y.-Q. Zhang, Barbell lifting

wavelet transform for highly scalable video coding, Picture Coding

Symposium 2004, USA, Dec 2004.

[10] P. Kogge and H. Stone. A parallel algorithm for the efficient

solution of a general class of recurrence equations. IEEE

Transactions on Computers, 22(8):786-793, 1973.

[11] A. S. Lewis and G. Knowles, Image compression using the 2D wavelet transfor111, IEEE Trans. Image Processing, I, p.

244(1992).

[12] P. Mohan. Residue Number Systems: Algorithms and

Architectures. Kluwer Academic Publishers, Norwell, MA, 2002.

[13] Sayed Ahmad Salehi and Rasoul Amirfattahi, VLSI

Architectures of Lifting-Based Discrete Wavelet Transform, Discrete

Wavelet Transforms - Algorithmsand Applications, Prof. Hannu

Olkkonen (Ed.), ISBN: 978-953-307-482-5 (2011),

[14] I Daubechies and W. Sweldens, Factoring Wavelet Transforms

into Lifting Steps, Program for Applied and Computational

Mathematics, Princeton University, November 1997.

[15] I Daubechies and W. Sweldens, Factoring Wavelet Transforms

into Lifting Steps, J. Fourier Anal. Appl.4, 247-269 (1998).

{16} U.N.Thakur, S.Saha, A.Mukherjee, A Proposed

Architecture for Residue Number System Based 1D 5/3

Discrete Wavelet Transform using Filter Bank and Lifting

Scheme, International Journal of Computer Applications

(0975 8887), Vol. 90. No.14, pp. 43-48, March in 2014.

You might also like

- CSE Digital SyllabusDocument2 pagesCSE Digital Syllabusu110010No ratings yet

- Microprocessor Architecture: Introduction To Microprocessors Chapter 2 1Document47 pagesMicroprocessor Architecture: Introduction To Microprocessors Chapter 2 1harilakNo ratings yet

- ECE Final Upto 4th Year SyllabusDocument42 pagesECE Final Upto 4th Year Syllabusu110010No ratings yet

- Memory OrganizationDocument21 pagesMemory Organizationu110010No ratings yet

- Ugc Net SyllabusDocument4 pagesUgc Net Syllabus123bala123No ratings yet

- University of Engineering Management: CE 301 CE 302 CE 303 CH 301Document6 pagesUniversity of Engineering Management: CE 301 CE 302 CE 303 CH 301u110010No ratings yet

- IIT/SRIC/R/MUE/2014/225, DATED 25th August, 2014Document1 pageIIT/SRIC/R/MUE/2014/225, DATED 25th August, 2014u110010No ratings yet

- Digital ElectronicsDocument51 pagesDigital Electronicsu110010No ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Strenght of Mat DR AhmedDocument184 pagesStrenght of Mat DR AhmedAlaomda Albasrawy100% (1)

- Pemerintah Kabupaten Pamekasan Cabang Dinas Pendidikan Dan Kebudayaan Kecamatan GalisDocument2 pagesPemerintah Kabupaten Pamekasan Cabang Dinas Pendidikan Dan Kebudayaan Kecamatan GalisMuhamad AminNo ratings yet

- Geotechnical Engineering C2Document8 pagesGeotechnical Engineering C2Tyn MaturanNo ratings yet

- Dbms McqsDocument5 pagesDbms McqsShweta Sharma100% (2)

- Twist RateDocument3 pagesTwist RateFernando ParabellumNo ratings yet

- Fuzzy Set TheoryDocument36 pagesFuzzy Set TheoryJyotirmayee PandaNo ratings yet

- Chapter 3Document23 pagesChapter 3marwanNo ratings yet

- Major Scale - WikipediaDocument5 pagesMajor Scale - WikipediaDiana GhiusNo ratings yet

- Anmol Publications - PB Catalog (14-05-2014)Document70 pagesAnmol Publications - PB Catalog (14-05-2014)Beenu BhallaNo ratings yet

- Regime-Switching Models: Department of Economics and Nuffield College, University of OxfordDocument50 pagesRegime-Switching Models: Department of Economics and Nuffield College, University of OxfordeconométricaNo ratings yet

- BSC 1 Sem Mathematics Differential and Integral Calculus Part 1 Winter 2018Document4 pagesBSC 1 Sem Mathematics Differential and Integral Calculus Part 1 Winter 2018Viraj PatilNo ratings yet

- Graph Sheet V.2Document13 pagesGraph Sheet V.2youssef amrNo ratings yet

- Properties of Uniform Circular MotionDocument16 pagesProperties of Uniform Circular MotionAndresEstebanSilvaSanchezNo ratings yet

- A Detailed Lesson Plan in Mathematics (Joven)Document12 pagesA Detailed Lesson Plan in Mathematics (Joven)dapitomaryjoy100% (1)

- HWK Yr7 Unit 1.5 & 1.6Document3 pagesHWK Yr7 Unit 1.5 & 1.6King FonsekaNo ratings yet

- ROC Z TransformDocument15 pagesROC Z TransformMohammad Gulam Ahamad0% (1)

- Stress: Normal Stress Shearing Stress Bearing StressDocument79 pagesStress: Normal Stress Shearing Stress Bearing StressMelanie Samsona100% (1)

- 1st Quarter Exam 2022Document4 pages1st Quarter Exam 2022Angela RuleteNo ratings yet

- 6 CoordDocument58 pages6 Coordrosenthal elvis chimpay ariasNo ratings yet

- Chapter 3: Continuous Random Variables: Nguyễn Thị Thu ThủyDocument69 pagesChapter 3: Continuous Random Variables: Nguyễn Thị Thu ThủyThanh NgânNo ratings yet

- Homework 8Document2 pagesHomework 8RazaMobizoNo ratings yet

- Quantitative AssignmentDocument6 pagesQuantitative AssignmentAlemu Muleta KebedeNo ratings yet

- MTH 210A Assignment 6Document2 pagesMTH 210A Assignment 6Rohit SharmaNo ratings yet

- hw11 DallasonnekommtDocument2 pageshw11 DallasonnekommtDan Yapp0% (1)

- Standard Functions in PI 7.0 - Process Integration - Community WikiDocument34 pagesStandard Functions in PI 7.0 - Process Integration - Community Wikifziwen100% (1)

- Worksheet 4 Memorandum Exponents Grrade 10 MathematicsDocument4 pagesWorksheet 4 Memorandum Exponents Grrade 10 MathematicsAat JuhatiNo ratings yet

- Designing Aplanatic Thick Lenses: SPIE NewsroomDocument2 pagesDesigning Aplanatic Thick Lenses: SPIE NewsroomHitesh KashyapNo ratings yet

- Air Passenger Demand Forecasting For Planned Airports, Case Study Zafer and OR-GI Airports in Turkey (Planlanan Havalimanlarının Yolcu Talep Miktarlarının Tahmin Edilmesi Zafer Ve OR-Gİ Hava L PDFDocument149 pagesAir Passenger Demand Forecasting For Planned Airports, Case Study Zafer and OR-GI Airports in Turkey (Planlanan Havalimanlarının Yolcu Talep Miktarlarının Tahmin Edilmesi Zafer Ve OR-Gİ Hava L PDFÇağrı KARABİLLİOĞLUNo ratings yet

- Unit 10 Plane Trusses: StructureDocument33 pagesUnit 10 Plane Trusses: StructureVic LindoNo ratings yet

- CS 1996Document19 pagesCS 1996amrendra7No ratings yet