Professional Documents

Culture Documents

Chapter - 5 - Two Stage Cmos Op-Amp

Uploaded by

nilesh0001Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Chapter - 5 - Two Stage Cmos Op-Amp

Uploaded by

nilesh0001Copyright:

Available Formats

Chapter 5

Two-Stage CMOS Operational Amplifier

5.1 Introduction

In single stage Op-Amp, small signal current produced by the input pair to flow directly

through the output impedance. The gain of these topologies is limited by the product of

the input pair transconductance and the output impedance. In cascode circuit, its provide

high gain while limiting the output swing. In some application, op-amp requires high gain

and large output swing with operate 0.5V power supply. In such a case, we require extra

stage so called two-stage. In multistage amplifier, first stage is require to provide a high

resistance source. In differential amplifier, input stage must provide large CMRR. The

function of the middle stage of an amplifier cascade is to provide the bulk of the voltage

gain, also provide other function like conversion of the signal from differential mode to

single-ended mode and shifting of the dc level of the signal in order to allow the output

signal to swing both positive and negative. The main function of the last stage of an

amplifier is to provide a low output resistance in order to avoid loss of gain when a lowvalued load resistance is connected to the amplifier, also output stage should be able to

supply the current required by the load that is without dissipating large amount of power

in the output transistors.

Compensation

circuit

Vin+

Vin

Input Differential

Amplifier stage

Second Voltage gain

stage

Bias circuit

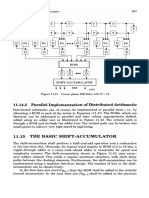

Figure 5.1: Block diagram of Two Stage CMOS Op-Amp [1]

Page 30

Vo

Two-Stage CMOS Operational Amplifier

CC

Vin+

Vin

1st stage

2nd stage

Output Buffer

Vo

Figure 5.2: Simplified block diagram of Two-Stage Op-amp [1]

Basically operational amplifier has three stages, but ignoring output buffer stage so called

two-stage op-amp. Two-stage refers as number of gain stages in the op-amp.

Operational Amplifiers are the backbone for many analog circuit designs. The speed and

accuracy of these circuits depends on the bandwidth and DC gain of the Op-amp. Larger

will be the bandwidth and gain, higher will the speed and accuracy of the amplifier. The

general block diagram of an op-amp is shown above in Figure 5.1. The simplified Block

Diagram is shown in figure 5.2.

The first block is a differential amplifier. It has two inputs that are the inverting and noninverting voltage. It gives a differential voltage at the output or a differential current

which depends only on differential input voltage. The second block is a differential ended

to single-ended converter. It is used to transform the differential signal generated by the

first block into a single ended output signal. Some architecture doesnt require the

differential to single ended function; therefore this block can be eliminated in that. In

single stage amplifier, the gain provided by the input stages is not sufficient, so there is

an additional amplification is required which is provided by the second stage, i.e. the

common source amplifier, driven by the first stage output. As this stage uses differential

input unbalanced output differential amplifier, so it provides the required extra gain. The

biasing circuit is here to provide the proper operating point to each transistor in its

saturation region. Third stage, the output buffer stage provides the low impedance at

output and larger output current needed to drive the load of op-amp or improves the slew

rate. Even the output stage can be dropped since many applications do not need low

output impedance. If the op-amp is intended to drive a small purely capacitive load, then

output buffer is not required. Compensation capacitor is included to ensure stability when

31

Two-Stage CMOS Operational Amplifier

op-amp is used with feedback. Because CC is place between input and output of the

second common source stage, so it is called Miller capacitance.

5.2 Two-Stage CMOS Op-Amp

VDD

M4

M3

M6

Iref

Vo

CC

Vin+

M1

M2

VinCL

M7

M5

M8

Figure 5.3: Two-Stage Op-Amp using miller compensation

The topology of this circuit is that of a standard two-stage CMOS op-amp. it has three

subparts, namely input differential amplifier stage, second gain stage and biasing circuit.

5.3 Circuit Description

Two-stage op-amp is containing three subsections:

First Stage: Figure 5.3 contains two part of two-stage op-amp. Transistor M1, M2, M3,

and M4 constitute the first stage of differential amplifier. M1 and M2 transistors are

nMOS. M3 and M4 transistors are pMOS transistor. Input voltage V in+ and Vin- are given

to gate terminal of transistor M1 and M2. Gate of M1 is noninverting input and gate of

M2 is inverting input. M3 and M4 constitute current mirror. A differential input signal is

32

Two-Stage CMOS Operational Amplifier

applied across the two input terminals will be amplified according to the gain of the

differential stage. So that gain of this stage is the transconductance of M1 times to the

total output resistance seen at the drain of M4. The main resistances that constitute to the

output resistance are that of the input transistors and output resistance of the load

transistors M3 and M4. Transconductance and output resistance of the first stage is given

by Gm1 and Rout1

Gm1 = g m1

(5.3.1)

R out 1 = ro4 ro2

(5.3.2)

In this circuit, current mirror active load used has three main advantages. First, active

load devices crate large output resistance that provides small amount of chip area. Second

current mirror topology provides the differential to single ended conversion of input

signal. The voltage gain of the differential amplifier is given by AV1

AV1 = g m1 (ro4 ro2 )

(5.3.3)

The differential to single ended conversion is achieved by using current mirror M3 and

M4. The current from M1 is mirror by M3 and M4 and subtracted from the current from

M2. Finally the differential current from M1 and M2 multiplied by the output resistance

of the input stage that gives the single ended output voltage. This is the part of the second

stage.

Second Stage: Second stage is a common source stage. The aim of this second stage is to

provide the additional gain consisting of transistors M6 and M8. Input of the second stage

is the output of the differential amplifier stage. This stage receives the output from the

drain of M4 and amplifies it through M6 by the common source configuration. Similar to

differential amplifier, this stage employs an active device, M8 to work as the load

resistance for M6. The gain of this stage is the transconductance of M6 times the

effective load resistance comprised of the output resistance of M6 and M8.

Transconductance and output resistance of the second stage is given by G m2 and Rout

Gm2 = g m6

(5.3.4)

33

Two-Stage CMOS Operational Amplifier

R out = (ro6 ro8 )

(5.3.5)

M6 is driver and M8 is acts as the load. The voltage gain of the second stage is given by

AV2

AV2 = g m6 (ro5 ro8 )

(5.3.6)

So that total gain of the two stage CMOS operational amplifier is given by

AV = AV1 AV2

(5.3.7)

AV = Gm1 R out 1 Gm2 R out

(5.3.8)

AV = g m1 ro4 ro2 g m6 (ro6 ro8 )

(5.3.9)

Biasing Circuit: The purpose of the biasing circuit is to provide the gate to source

voltage of the entire transistor. The biasing of the operational amplifier is achieved with

only three transistors. Transistor M5 supplies a voltage between gate and source of M7

and M8. Transistors M7 and M8 sink a certain amount of current based on their gate to

source voltage which is controlled by the bias string. M5 is diode connected to ensure

they operate in the saturation region. Proper biasing of the other transistor in the circuit

(M1-M4, M6) is controlled by the node voltages present in the circuit itself. M6 is biased

by the gate to source voltage set up by the VGS of the current mirror load as are the M3

and M4 transistors.

Third stage: In fig 5.2, third stage is output buffer stage which is simply common drain

stage. This stage is often called a source follower, because the source voltage follows the

gate voltage, except for a level shift. When possible, it is desirable to tie the substrate of

the source-follower device to its source in order to eliminate gain degradations due to the

body effect. This connection also results in a smaller dc voltage drop from the gate to the

source of the source-follower device, which is a major limitation on the maximum

positive output voltage. So that in fig 5.3, we dont show output buffer stage due above

drawback.

34

Two-Stage CMOS Operational Amplifier

5.4 Small single analysis

CC

Vo 2

V1 1

Vo

Vin

CC

gm1V1

CL

ro1

roL

gm2V1

-

Figure 5.4: Small signal analysis of two-stage CMOS op-amp without miller

compensation

V

General transfer function of fig. 5.4 is given by T.F = V o

in

Vo

As per small signal diagram,

V in

= V 1 Vo

in

(5.4.1)

Apply KCL to node 1 above circuit,

v1

v1

v1 vo

+

+

g

v

+

=0

m1

in

1

1

R1

SC 1

SC L

v1 sc1 +

v1

+ g m1 vin + scc (v1 vo ) = 0

R1

v1 (sc1 +

v1 =

1

+ sc1 ) + g m1 vin vo scc = 0

R1

v o sc 1 R 1 g m 1 v in R 1

(5.4.2)

1+sR 1 (c c +c 1 )

Apply KCL to node 2 in above circuit,

vo

1

sc 2

sc2 vo +

sc c

vo

+ g m2 v1 + scc (vo v1 ) = 0

R2

vo sc2 +

vo

vo 1 + sR 2 cc + c2

vo

vo v1

+ g m2 v1 +

=0

1

R2

1

+ scc v1 scc + g m2 v1 = 0

R2

1

+ (sc2 + scc ) = v1 scc g m2

R2

1 + sR1 cc + c1

= vo scc R1 g m1 R1 vin scc g m2

35

Two-Stage CMOS Operational Amplifier

sc

g m1 g m2 R1 R 2 1 g c

vo

m2

= 2

vin s R1 R 2 c1 c2 + c1 cc + c2 cc + s R 2 cc + c2 + R1 cc + c1 + cc g m2 R1 R 2 + 1

(5.4.3)

Equation 5.4.3 is standard transfer function of fig. 5.3.

Two pole transfer function:

vo

v in

vo

v in

A DC 1Z

=

=

s

1+P

(5.4.4)

1+P

s

Z

1

1

1

+ +s 2 (P P )

P1 P 2

1 3

A DC (1 )

1+s

1

P1

1

P2

=s

P2

(5.4.5)

(5.4.6)

P1

=Co-efficient of s

If pole P1 and P2 is shown in graph. In this graphs pole P2 is far away from the pole P1 at

high frequency so that pole P1 is located at low frequency so that pole P2 is ignored in

equation (5.4.6).

Compare equation (5.4.3) and (5.4.5), poles P1, P2 , zeros Z and DC gain ADC is given by

Pole P1,

P1 = R

1

2

P1 g

Pole P2,

1

1

1 R 2 c 1 c 2 +c 1 c c +c 2 c c

P2 = P

1

1 R 1 R 2 c 1 c 2 +c 1 c c +c 2 c c

P2 = R

Zeros Z,

(5.4.7)

m 2R1R2cc

P1 P2 = R

P2 =

c c +c 2 +R 1 c c +c 1 +g m 2 R 1 R 2

gm 2R1R2cc

1R2

c 1 c 2 +c 1 c c +c 2 c c

(P1 from equation 5.4.7)

gm 2cc

c 1 c 2 +c 1 c c +c 2 c c

P2

g m 2c c

P2

gm 2

cc c2

(5.4.8)

c2

(5.4.9)

36

Two-Stage CMOS Operational Amplifier

ADC = g m1 g m2 R1 R 2

DC voltage gain,

(5.4.10)

5.5 Derivation of two-stage Op-Amp parameter

We will derive the performance parameter of two-stage CMOS operational amplifier

which is given below.

Gain

Slew-rate, SR

Gain-bandwidth product, GBW

Phase margin, PM

Output voltage swing

Load capacitance, CL

Power dissipation, Pdiss

Gain-bandwidth Product, GBW:

GBW = DC gain P1

From the equation (5.4.10) and (5.4.7), put the value of DC gain and pole P 1

GBW = g m1 R1 g m2 R 2

GBW =

1

g m2 R1 R 2 CC

gm 1

(5.5.1)

CC

Zeros is far away from the 10 times located after unity gain. So therefore, we are express

zeros in bode plot diagram,

Z 10GBW

Slew-rate, SR: It is defined by the maximum rate of change of output voltage per unit

time, generally express in V/s

SR =

dv

dt

Maximum

Relation between voltage and capacitor in term of capacitor

1

V=C

I dt

VC =

I dt

Replacing capacitor C by cc and current I by Io,

37

Io = cc

dv

Io

dt

cc

dv

dt

Two-Stage CMOS Operational Amplifier

SR =

Final equation of the slew rate is given by

I0

(5.5.2)

cc

Phase margin, PM:

From the equation (5.4.4), phase angle of the pole and zero of the overall transfer

function is given by

Angle

V0

V in

= tan1

W

Z

tan1 P tan1 P

(5.5.3)

V0

GBW

GBW

GBW

= tan1

tan1

tan1

Vin

Z

P1

P2

Putting the value of the GBW, Z, P1 and P2 from the equation (5.5.1) (5.4.7), (5.4.8) and

(5.4.9)

V0

GBW

g m1 g m2 R1 R 2 CC

GBW

= tan1

tan1

tan1

Vin

10 GBW

CC

P2

V0

1

GBW

= tan1

tan1 g m1 g m2 R1 R 2 tan1

Vin

10

P2

From the equation (5.4.10), g m1 g m2 R1 R 2 is voltage gain ADC

V0

1

GBW

= tan1

tan1 ADC tan1

Vin

10

P2

1

Putting tan1 10 = 5.71 and voltage gain is always 90 phase angle in bode plot

180 + PM = 5.71 90 tan1

PM = 180 5.71 90 tan1

PM = 84.29 tan1

GBW

GBW

P2

GBW

P2

(5.5.4)

P2

Op-amp has better phase margin and improve stability at 60 phase angle. So that we will

take phase margin is 60 as according to find relation between GBW and second pole P2

in bode plot.

60 = 84.29 tan1

tan1

GBW

P2

GBW

= 24.29

P2

38

Two-Stage CMOS Operational Amplifier

GBW

= tan 24.29

P2

GBW

= 0.4513

P2

P2 = 2.2 GBW

For PM = 60, relation between P2 and GBW is given by

P2 2.2 GBW

(5.5.5)

From the equation (5.5.4)

PM = 84.29 tan1

GBW

P2

Now second case, take the phase margin PM = 45

45 = 84.29 tan1

tan1

GBW

P2

GBW

= 39.29

P2

GBW

= 0.8181

P2

P2 =

GBW

0.8181

For, PM = 45, relation between P2 and GBW is given by

P2 1.22 GBW

(5.5.6)

From the equation (5.4.8) and (5.5.1), put the value of P 2 and GBW in equation (5.5.5)

g m2

g m1

2.2

C2

CC

C2 is output capacitance; we replace C2 by load capacitance

gm 2

CL

2.2

gm 1

CC

In transfer function, zeros is given by

Z = 10GBW

39

(5.5.7)

Two-Stage CMOS Operational Amplifier

Form the equation (5.4.9) and (5.5.1)

g m2

g m1

= 10

CC

CC

g m2 = 10g m1

(5.5.8)

Put the value of 2 in equation (5.5.7)

10 g m1

g m1

2.2

CL

CC

10

2.2

CL

CC

CC

2.2

10

CL

CC 0.22 CL

(5.5.9)

So that relation between compensation capacitor and load capacitor is given by in

equation (5.5.9). if load capacitor is given, we will easily finds out the value of

compensation capacitor

40

You might also like

- Research Paper On Two Stage Single Ended CMOS AmplifierDocument4 pagesResearch Paper On Two Stage Single Ended CMOS AmplifierDilip MathuriaNo ratings yet

- Cmos Two Stage OpamppublishedDocument5 pagesCmos Two Stage Opamppublisheddeepak pandeyNo ratings yet

- Ee 215 ADocument8 pagesEe 215 AArjun Singhal100% (1)

- Two Stage Opamp BerkeleyDocument25 pagesTwo Stage Opamp BerkeleyCircuit CruzNo ratings yet

- Design High Speed, Low Noise, Low Power Two Stage CMOSDocument5 pagesDesign High Speed, Low Noise, Low Power Two Stage CMOSsanjeevsoni64No ratings yet

- EMT Assignment 5Document15 pagesEMT Assignment 5Kelvin KohNo ratings yet

- Cpe08 Midterm Exam Part 1and 2Document4 pagesCpe08 Midterm Exam Part 1and 2Elle ElleNo ratings yet

- Principles of The LVDTDocument3 pagesPrinciples of The LVDTWalid FattahNo ratings yet

- Experiment No. 1: Aim: Study of Tanner Tools THEORY: Tanner ToolsDocument24 pagesExperiment No. 1: Aim: Study of Tanner Tools THEORY: Tanner ToolsVarun GargNo ratings yet

- SMD Question BankDocument2 pagesSMD Question BankBharatNo ratings yet

- Presentation: Thin Film TransistorDocument9 pagesPresentation: Thin Film TransistorMayankSharma100% (1)

- Detecting and Correcting Errors in CodesDocument4 pagesDetecting and Correcting Errors in CodesStephenPengNo ratings yet

- CMOS Design RulesDocument21 pagesCMOS Design Rulesrakheep123No ratings yet

- CMFB DesignDocument4 pagesCMFB Designaminkhan83No ratings yet

- II BTECH - I SEM - ECE - EDC - THEORY & QUIZ QUESTIONS - MID 2 - Students PDFDocument19 pagesII BTECH - I SEM - ECE - EDC - THEORY & QUIZ QUESTIONS - MID 2 - Students PDFK SrinuNo ratings yet

- Optical Fiber Transmission Link ElementsDocument15 pagesOptical Fiber Transmission Link ElementsAchu0% (1)

- Mini Project Report-2Document26 pagesMini Project Report-2Remya Ramakrishnan0% (2)

- Micro MCQ Unit 4,5Document20 pagesMicro MCQ Unit 4,5Abhijit KumarNo ratings yet

- High-Speed Cmos Op-Amp Design TechniqueDocument4 pagesHigh-Speed Cmos Op-Amp Design Techniquemax511894902No ratings yet

- MIM Cap ModelDocument4 pagesMIM Cap ModelDuc DucNo ratings yet

- Interview Questions ElectricalDocument3 pagesInterview Questions ElectricalsivabalakrishnanNo ratings yet

- Basic Shift AccumulatorDocument4 pagesBasic Shift AccumulatorThahsin ThahirNo ratings yet

- Design, Fabrication and Testing of Analog IC AmplifiersDocument17 pagesDesign, Fabrication and Testing of Analog IC AmplifiersNurul Hanim HashimNo ratings yet

- Optimal Design of A Reversible Full AdderDocument17 pagesOptimal Design of A Reversible Full AdderMohamedNo ratings yet

- Amplifier Project GradDocument5 pagesAmplifier Project Gradمحمد قاسم نفل سميرNo ratings yet

- Dspa 17ec751 M5Document34 pagesDspa 17ec751 M5digital loveNo ratings yet

- Low Power Circuit Design Techniques for Adders and MultipliersDocument27 pagesLow Power Circuit Design Techniques for Adders and Multipliersharikirthika100% (1)

- Chapter02 - Logic Design With MOSFETsDocument51 pagesChapter02 - Logic Design With MOSFETsbal3xNo ratings yet

- Design of Two-Stage Operational Amplifier: Shahin Shah (12116053), Abhinav Singhal (12116001)Document2 pagesDesign of Two-Stage Operational Amplifier: Shahin Shah (12116053), Abhinav Singhal (12116001)Shahin ShahNo ratings yet

- Ece VI Digital Communication 10ec61 NotesDocument252 pagesEce VI Digital Communication 10ec61 NotesNiharika Korukonda100% (1)

- Two-Stage Operational Amplifier Design Using Gm/Id MethodDocument7 pagesTwo-Stage Operational Amplifier Design Using Gm/Id Methodabhinav kumarNo ratings yet

- IES Bangalore Analog Electronics Old GATE ECE QuestionsDocument74 pagesIES Bangalore Analog Electronics Old GATE ECE QuestionsPrateek Khare100% (2)

- Mechatronics ExamDocument5 pagesMechatronics Exammoro1992No ratings yet

- TRANSMISSION LINES - CHARACTERISTICS, EQUATIONS AND IMPEDANCE MATCHINGDocument5 pagesTRANSMISSION LINES - CHARACTERISTICS, EQUATIONS AND IMPEDANCE MATCHINGMunni 1123No ratings yet

- Ecad Lab ManualDocument55 pagesEcad Lab Manualjeravi84100% (3)

- Amplitude Modulation and Sideband Modulation ConceptsDocument5 pagesAmplitude Modulation and Sideband Modulation Conceptssameer nayakNo ratings yet

- Power Electronics Important QuestionsDocument4 pagesPower Electronics Important QuestionsShuvamSarkar0% (1)

- Double Stub MatchingDocument10 pagesDouble Stub Matchingjubair0% (1)

- Design of A Fully Differential High-Speed High-Precision AmplifierDocument10 pagesDesign of A Fully Differential High-Speed High-Precision Amplifierkirkland1337No ratings yet

- Design and Implementation of High Gain, High Bandwidth CMOS Folded Cascode Operational Transconductance AmplifierDocument5 pagesDesign and Implementation of High Gain, High Bandwidth CMOS Folded Cascode Operational Transconductance AmplifierChristian Montano GalvezNo ratings yet

- CMOS Translinear CellsDocument4 pagesCMOS Translinear CellsSumitChoudharyNo ratings yet

- Folded Cascode ChopperDocument4 pagesFolded Cascode ChoppergirishknathNo ratings yet

- Question Bank Fundamentals of CMOS VLSI-10EC56 15-16Document10 pagesQuestion Bank Fundamentals of CMOS VLSI-10EC56 15-16Pranav KpNo ratings yet

- To Make A DC Switching Circuit Using SCR'sDocument2 pagesTo Make A DC Switching Circuit Using SCR'sH Aries OñaNo ratings yet

- Basic PLC Scada MCQDocument2 pagesBasic PLC Scada MCQjoshikaustubhp070No ratings yet

- BLDC DriveDocument37 pagesBLDC DriveLasya Ganapathi100% (1)

- Interfacing Programs For 8085Document37 pagesInterfacing Programs For 8085archankumarturagaNo ratings yet

- Pipelining and Parallel ProcessingDocument16 pagesPipelining and Parallel ProcessingBilgaNo ratings yet

- Preventing Latch Up - NationalDocument2 pagesPreventing Latch Up - Nationalkvpk_vlsiNo ratings yet

- Fpga ManualDocument7 pagesFpga ManualRahul SharmaNo ratings yet

- AM Electronics (March 2020) : C) An SR Flip-Flop and A T Flip-FlopDocument22 pagesAM Electronics (March 2020) : C) An SR Flip-Flop and A T Flip-FlopFatima HasnainNo ratings yet

- FPSC TestDocument6 pagesFPSC TestTouqeer MetloNo ratings yet

- EDC Question BankDocument13 pagesEDC Question BankvenzkrishNo ratings yet

- LOW POWER VLSI DESIGN TECHNIQUES AND ANALYSISDocument10 pagesLOW POWER VLSI DESIGN TECHNIQUES AND ANALYSISluckymanjuNo ratings yet

- EC 1401 - VLSI Design QuestionsDocument18 pagesEC 1401 - VLSI Design QuestionsChaitanya PrabhuNo ratings yet

- Electrical Overstress (EOS): Devices, Circuits and SystemsFrom EverandElectrical Overstress (EOS): Devices, Circuits and SystemsNo ratings yet

- Active Disturbance Rejection Control for Nonlinear Systems: An IntroductionFrom EverandActive Disturbance Rejection Control for Nonlinear Systems: An IntroductionNo ratings yet

- 1.0 S15 3-Wire Control App NoteDocument2 pages1.0 S15 3-Wire Control App Notenilesh0001No ratings yet

- SETDocument14 pagesSETnilesh0001No ratings yet

- Design of Two Stage CMOS Operational Amplifier and Analyze The Effect of Scaling Using CMOS Deep Submicron TechnologyDocument12 pagesDesign of Two Stage CMOS Operational Amplifier and Analyze The Effect of Scaling Using CMOS Deep Submicron Technologynilesh0001No ratings yet

- Perspe1110.0.ctive D T O T W Wsp4finDocument1 pagePerspe1110.0.ctive D T O T W Wsp4finnilesh0001No ratings yet

- MY RESUMEsdfsdffdsfsdDocument2 pagesMY RESUMEsdfsdffdsfsdnilesh0001No ratings yet

- Experiment: 1: Introduction To HDL Simulation and Synthesis ToolsDocument6 pagesExperiment: 1: Introduction To HDL Simulation and Synthesis Toolsnilesh0001No ratings yet

- Hspice Lab ManualDocument47 pagesHspice Lab Manualnilesh0001No ratings yet

- 2dpipe Ge31111313131omDocument13 pages2dpipe Ge31111313131omnilesh0001No ratings yet

- Experiment - 03: 1. FPGA-A Board and Its Power SupplyDocument6 pagesExperiment - 03: 1. FPGA-A Board and Its Power Supplynilesh0001No ratings yet

- Experiment 1fdfsdfDocument14 pagesExperiment 1fdfsdfnilesh0001No ratings yet

- 2dpipe Ge31111313131omDocument13 pages2dpipe Ge31111313131omnilesh0001No ratings yet

- MY RESUMEsdfsdffdsfsdDocument2 pagesMY RESUMEsdfsdffdsfsdnilesh0001No ratings yet

- MuxDocument1 pageMuxnilesh0001No ratings yet

- Sp3 Im Board UfsdcfDocument3 pagesSp3 Im Board Ufsdcfnilesh0001No ratings yet

- LCD Test: He LCD Displays "BIT"pattern When RESET Is PressedDocument1 pageLCD Test: He LCD Displays "BIT"pattern When RESET Is Pressednilesh0001No ratings yet

- EGCP 1010 Digital Logic Design (DLD) Laboratory #7: ObjectiveDocument9 pagesEGCP 1010 Digital Logic Design (DLD) Laboratory #7: Objectivenilesh0001No ratings yet

- LCD Test: He LCD Displays "BIT"pattern When RESET Is PressedDocument1 pageLCD Test: He LCD Displays "BIT"pattern When RESET Is Pressednilesh0001No ratings yet

- Sp3 Im Board UfsdcfDocument3 pagesSp3 Im Board Ufsdcfnilesh0001No ratings yet

- Nijitronics: Supplier of Electronic, Civil, Mechanical and Electrical Instruments CorrespondenceDocument1 pageNijitronics: Supplier of Electronic, Civil, Mechanical and Electrical Instruments Correspondencenilesh0001No ratings yet

- Experiment - 01: To Study The Characteristics of Operational AmplifierDocument3 pagesExperiment - 01: To Study The Characteristics of Operational Amplifiernilesh0001No ratings yet

- Test Bench For JK FlipDocument2 pagesTest Bench For JK Flipmnpaliwal020100% (2)

- MicrowaveDocument1 pageMicrowavenilesh0001No ratings yet

- 01 TutorialDocument6 pages01 TutorialalijanavarNo ratings yet

- Fixed 1,8 Prodelin Antenna Product InfoDocument2 pagesFixed 1,8 Prodelin Antenna Product Infoanon_578762250No ratings yet

- 2022 Annual Report-E PDFDocument325 pages2022 Annual Report-E PDFF550VNo ratings yet

- Semiconductor Diodes ExplainedDocument127 pagesSemiconductor Diodes ExplainedKimberly BañesNo ratings yet

- X-Ray Beam Collimator ManualDocument32 pagesX-Ray Beam Collimator ManualRogerio CastroNo ratings yet

- Chapter 7 - Lecture 8Document37 pagesChapter 7 - Lecture 8Trường An TháiNo ratings yet

- Ssc-Je-Electronic-Devices Electrical EngineeringDocument13 pagesSsc-Je-Electronic-Devices Electrical EngineeringPeerzada WahidNo ratings yet

- Compact NS - 630A - 34022 PDFDocument2 pagesCompact NS - 630A - 34022 PDFTrai Nhà NôngNo ratings yet

- Jntuh Previous Year PaperDocument2 pagesJntuh Previous Year Paper20BA693 KmitNo ratings yet

- Blink An LED With Arduino in TinkercadDocument15 pagesBlink An LED With Arduino in TinkercadVirendra GourNo ratings yet

- Chapter One: 1.1 Background of The StudyDocument45 pagesChapter One: 1.1 Background of The StudysamNo ratings yet

- Medusa 4 TS 09 033Document2 pagesMedusa 4 TS 09 033doantran2508No ratings yet

- 32TMSS02R2Document62 pages32TMSS02R2Amjith MeerasNo ratings yet

- Datasheet - Turck Module IM1-22EX-T - ENDocument4 pagesDatasheet - Turck Module IM1-22EX-T - ENscm balikpapanNo ratings yet

- 7SA6 Catalog SIP E7Document42 pages7SA6 Catalog SIP E7Robert MihayoNo ratings yet

- Debug 1214Document19 pagesDebug 1214Ivan StevkovskiNo ratings yet

- Single Family DwellingDocument27 pagesSingle Family Dwellingjayson platinoNo ratings yet

- WatchIN Brochure en-LRDocument2 pagesWatchIN Brochure en-LRJohnatan FlorezNo ratings yet

- SF DumpDocument13 pagesSF DumpMJ Aranda beniNo ratings yet

- Buscar Energy Harvesting PDFDocument527 pagesBuscar Energy Harvesting PDFJONATHAN VALENCIA BOLANOSNo ratings yet

- HP ProCurve Switch 2810-24G (J9021A)Document1 pageHP ProCurve Switch 2810-24G (J9021A)peterNo ratings yet

- Method of ComputationDocument10 pagesMethod of ComputationPatricia Ann PedrazaNo ratings yet

- Tanggal No Jurnal Keterangan Debit Kredit Saldo Note I Saldo Awal Per 31 Desember 2020Document35 pagesTanggal No Jurnal Keterangan Debit Kredit Saldo Note I Saldo Awal Per 31 Desember 2020RUSMAWAN SHNo ratings yet

- Efficient Wiring and Logic Control: Designed For Easy IntegrationDocument2 pagesEfficient Wiring and Logic Control: Designed For Easy IntegrationAna RuganiNo ratings yet

- Solar Pumping System GuideDocument2 pagesSolar Pumping System GuideKaffel AhmedNo ratings yet

- Control Remoto OrtsDocument37 pagesControl Remoto OrtsRick CianuroNo ratings yet

- Biddle 550503 Specifications F9026 PDFDocument4 pagesBiddle 550503 Specifications F9026 PDFRamon Orlando Sanchez AltamirandaNo ratings yet

- TRANSMITTER To The Antenna Connector of Your TransceiverDocument2 pagesTRANSMITTER To The Antenna Connector of Your TransceiverMarcos VidelaNo ratings yet

- Yamaha YSTSW 320 Owners ManualDocument19 pagesYamaha YSTSW 320 Owners ManualMarius SanduNo ratings yet

- IGCSE - Physics - Lesson Plan 6 - ElectricityDocument3 pagesIGCSE - Physics - Lesson Plan 6 - ElectricityHoracio FerrándizNo ratings yet

- Radar II ManualDocument261 pagesRadar II ManualPREVISTONo ratings yet