Professional Documents

Culture Documents

Review of Microarchitecture

Uploaded by

jzjherd1537Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Review of Microarchitecture

Uploaded by

jzjherd1537Copyright:

Available Formats

MEMORANDUM

TO:

DR. CHANG

FROM:

JONATHAN TAYLOR

SUBJECT: CRIB: CONSOLIDATED RENAME, ISSUE, AND BYPASS

DATE:

CC:

12/11/14

N/A

The primary goal of this paper was to describe an architecture that replaced the typical

reorder buffer and other associated hardware with a single system that attempted to streamline

the entire process. It did this via a rearrangement of the typical hardware model in order to

achieve high instruction level parallelism(ILP). Additionally it found that their redesign not only

yielded similar performance to common OoO processors it was more power-efficient as well.

The major contribution of this paper was to note that a redesign of the overall way in

which we approach ILP could lead to gains as far as power and die size is concerned. This is

primarily due to their use of registers which are not codified through some form of memory,

rather they are determined logically. Additionally they looked into a version of their architecture

that utilized a deeper pipeline in order to abuse some of the potential for a faster clock speed.

Overall their major contribution was adding another architecture to those that need to be

considered when designing a processor.

Their major weaknesses are that they are limiting the architectures that they are

comparing their suggested processor to without really justifying why they are doing so. They

state that they will justify why they limited the x86 processors instruction window in section 5

but never actually do so. Additionally it seems as if they were ignoring some of the results that

occurred when looking at the power consumption of Int CRIB vs ALU+Bypass and FP CRIB vs

FP+Bypass which colors their results slightly.

The weaknesses are not such that they should deter future research. Therefore, I

personally wonder if there are ways to get around the int and fp limitations when comparing

them to an OoO processor and think that future research should attempt to determine whether

or not this is a viable thing to implement. Additionally a further line of study would be to compare

the operations of these processors when dealing with code that has multiple branch prediction

errors as well as potential cache coherence issues. This could yield further insight as to the

performance difference between the two architectures and may reveal whether or not the power

and die size tradeoff is acceptable when looking at OoO vs a CRIB-like architecture.

Lastly a potential exam question for this article would be to describe the reasons behind

why the power consumption of the CRIB is so low. Potential reasons given in the paper are things

such as a latch system being utilized over an actual register file as well as less hardware that is

needed for maintenance of the OoO execution which allows the power requirements to be

lowered.

You might also like

- Review 5-Continuous Flow PipelinesDocument1 pageReview 5-Continuous Flow Pipelinesss MugdhoNo ratings yet

- Scheduling Threads For Constructive Cache Sharing On CmpsDocument11 pagesScheduling Threads For Constructive Cache Sharing On CmpsAnonymous RrGVQjNo ratings yet

- The Landscape of Parallel Computing Research: A View From BerkeleyDocument56 pagesThe Landscape of Parallel Computing Research: A View From BerkeleyDima LitvinovNo ratings yet

- On The Simulation of Linked ListsDocument7 pagesOn The Simulation of Linked ListsWDNo ratings yet

- Recvf BinodKumarDocument2 pagesRecvf BinodKumarBINOD KUMARNo ratings yet

- High Performance Parallelism Pearls Volume One: Multicore and Many-core Programming ApproachesFrom EverandHigh Performance Parallelism Pearls Volume One: Multicore and Many-core Programming ApproachesNo ratings yet

- Top 10 Tips For Oracle Database Performance-Part 1Document8 pagesTop 10 Tips For Oracle Database Performance-Part 1dommarajuuu1No ratings yet

- Temperature Hotspot Than in A Conventional Design. This Is Not Always True As in ThisDocument2 pagesTemperature Hotspot Than in A Conventional Design. This Is Not Always True As in ThisBINOD KUMARNo ratings yet

- 2000-01-28 Strange - Perf. For Peoplesoft AppsDocument51 pages2000-01-28 Strange - Perf. For Peoplesoft AppsPrateekGandhiNo ratings yet

- An Analysis of Ipv6: Ciclano Costa, Fulano Silva and Beltrano OliveiraDocument6 pagesAn Analysis of Ipv6: Ciclano Costa, Fulano Silva and Beltrano OliveiraGustavo SousaNo ratings yet

- Design and Implementation of Low Power Content Addressable MemoryDocument4 pagesDesign and Implementation of Low Power Content Addressable Memoryabhishek pandaNo ratings yet

- HP Data White PaperDocument25 pagesHP Data White Paperbanala.kalyanNo ratings yet

- Establishing The IO-500 Benchmark: Julian M. Kunkel, John Bent, Jay Lofstead, George S. MarkomanolisDocument1 pageEstablishing The IO-500 Benchmark: Julian M. Kunkel, John Bent, Jay Lofstead, George S. MarkomanolisdracknerNo ratings yet

- EPIC Architecture ILPDocument81 pagesEPIC Architecture ILPrkritsada6805No ratings yet

- Supplimentary Material IDocument24 pagesSupplimentary Material ILets clear Jee mathsNo ratings yet

- A Case For 802.11B: Stephen Hawkings and Mel GibsonDocument4 pagesA Case For 802.11B: Stephen Hawkings and Mel GibsonGerman GonzalezNo ratings yet

- 2q A Low Overhead High Performance Buffer Management Replacement AlgorithmDocument12 pages2q A Low Overhead High Performance Buffer Management Replacement AlgorithmpenetsNo ratings yet

- Internet QoS Considered HarmfulDocument11 pagesInternet QoS Considered HarmfulsaxbillNo ratings yet

- WRL Research Report 91/12: Cache Write Policies and PerformanceDocument48 pagesWRL Research Report 91/12: Cache Write Policies and PerformanceTao YueNo ratings yet

- Fair Cache Sharing and Partitioning in A Chip Multiprocessor ArchitectureDocument13 pagesFair Cache Sharing and Partitioning in A Chip Multiprocessor Architecturereg2regNo ratings yet

- Top 10 Strategies For Oracle Performance Part 3Document8 pagesTop 10 Strategies For Oracle Performance Part 3MihaiNo ratings yet

- Essay For SubmissionDocument7 pagesEssay For SubmissionrydusxNo ratings yet

- Courseware Considered Harmful: ModusDocument6 pagesCourseware Considered Harmful: ModusOne TWoNo ratings yet

- Research Paper On Assembly Line BalancingDocument8 pagesResearch Paper On Assembly Line Balancingyfwkdbaod100% (1)

- Week 5 - The Impact of Multi-Core Computing On Computational OptimizationDocument11 pagesWeek 5 - The Impact of Multi-Core Computing On Computational OptimizationGame AccountNo ratings yet

- A Fully Pipelined and Dynamically Composable Architecture of CGRADocument9 pagesA Fully Pipelined and Dynamically Composable Architecture of CGRABanusha chandranNo ratings yet

- Power and Energy Implications of The Number of Threads Used On The Intel Xeon PhiDocument11 pagesPower and Energy Implications of The Number of Threads Used On The Intel Xeon Phiomar.pro.servicesNo ratings yet

- The Impact of Interposable Epistemologies On Signed RoboticsDocument6 pagesThe Impact of Interposable Epistemologies On Signed RoboticsAdamo GhirardelliNo ratings yet

- Single-ISA Heterogeneous Multi-Core Architectures: The Potential For Processor Power ReductionDocument12 pagesSingle-ISA Heterogeneous Multi-Core Architectures: The Potential For Processor Power ReductionSilvia Graciela HerrmannNo ratings yet

- A Case Study On The Importance of Compiler and OthDocument10 pagesA Case Study On The Importance of Compiler and Othseion vaneNo ratings yet

- Scimakelatex 18970 One Two ThreeDocument6 pagesScimakelatex 18970 One Two Threemdp anonNo ratings yet

- An Understanding of SCSI Disks: BstractDocument4 pagesAn Understanding of SCSI Disks: BstractLarchNo ratings yet

- Deconstructing Ipv6 With Montemsoli: Que OndaDocument14 pagesDeconstructing Ipv6 With Montemsoli: Que OndaPepe PompinNo ratings yet

- Boosting Single-Thread Performance in Multi-Core Systems Through Fine-Grain Multi-ThreadingDocument10 pagesBoosting Single-Thread Performance in Multi-Core Systems Through Fine-Grain Multi-ThreadingshahpinkalNo ratings yet

- Scimakelatex 26951 John Doe Jane DoeDocument6 pagesScimakelatex 26951 John Doe Jane Doemdp anonNo ratings yet

- Decoupling Flip-Flop Gates From Rpcs in 802.11B: Ahmad Zahedi, Abdolazim Mollaee and Behrouz JamaliDocument6 pagesDecoupling Flip-Flop Gates From Rpcs in 802.11B: Ahmad Zahedi, Abdolazim Mollaee and Behrouz Jamalipayam12No ratings yet

- Dagatan Nino PRDocument12 pagesDagatan Nino PRdagatan.ninoNo ratings yet

- UpdatedbibliographyDocument5 pagesUpdatedbibliographyapi-298940823No ratings yet

- (William A. Wulf) Compilers and Computer ArchitectureDocument7 pages(William A. Wulf) Compilers and Computer ArchitectureFausto N. C. VizoniNo ratings yet

- Programming in OpenCL and Its Advantages in A GPU FrameworkDocument7 pagesProgramming in OpenCL and Its Advantages in A GPU FrameworkIJRASETPublicationsNo ratings yet

- DNA Assembly With de Bruijn Graphs On FPGA PDFDocument4 pagesDNA Assembly With de Bruijn Graphs On FPGA PDFBruno OliveiraNo ratings yet

- Compare Program ParadigmDocument2 pagesCompare Program ParadigmprabhuNo ratings yet

- Single-ISA Heterogeneous Multi-Core Architectures: The Potential For Processor Power ReductionDocument12 pagesSingle-ISA Heterogeneous Multi-Core Architectures: The Potential For Processor Power ReductionPrabakaran EllaiyappanNo ratings yet

- Homogeneous, Read-Write Technology For Redundancy: One, Three and TwoDocument6 pagesHomogeneous, Read-Write Technology For Redundancy: One, Three and Twomdp anonNo ratings yet

- A Low-Cost Energy-Efficient Raspberry Pi Cluster For Data Mining AlgorithmsDocument13 pagesA Low-Cost Energy-Efficient Raspberry Pi Cluster For Data Mining Algorithmsnico la roccaNo ratings yet

- On The Extreme Parallelism Inside Next-Generation Network ProcessorsDocument9 pagesOn The Extreme Parallelism Inside Next-Generation Network ProcessorsNaser AlshafeiNo ratings yet

- Call Graph Prefetching For Database ApplicationsDocument33 pagesCall Graph Prefetching For Database ApplicationsEngineer SinghNo ratings yet

- A Development of Redundancy: BstractDocument3 pagesA Development of Redundancy: BstractJustin ChenNo ratings yet

- Berkeley ViewDocument54 pagesBerkeley Viewshams43No ratings yet

- Jurnal Array MisbiantoroDocument19 pagesJurnal Array MisbiantoroExcekutif MudaNo ratings yet

- A Case for Operating Systems and NetworkingDocument3 pagesA Case for Operating Systems and Networkingehsan_sa405No ratings yet

- Decoupling IPv6 from IPv4 in IPv6 NetworksDocument4 pagesDecoupling IPv6 from IPv4 in IPv6 NetworksborlandspamNo ratings yet

- Green OS: Future Low Power Operating SystemDocument4 pagesGreen OS: Future Low Power Operating SystemVinay KumarNo ratings yet

- Reuse and Refactoring of GPU Kernels To Design Complex ApplicationsDocument8 pagesReuse and Refactoring of GPU Kernels To Design Complex Applicationsshubh9190No ratings yet

- Confio Statistical Analysis Database Performance DelaysDocument4 pagesConfio Statistical Analysis Database Performance DelaysRavmiNo ratings yet

- DownloadDocument9 pagesDownloadNISHANT TEKALENo ratings yet

- Harnessing Digital-to-Analog Converters Using Interposable CommunicationDocument5 pagesHarnessing Digital-to-Analog Converters Using Interposable CommunicationAdamo GhirardelliNo ratings yet

- Register File Caching For Energy EfficiencyDocument6 pagesRegister File Caching For Energy EfficiencyEdmund LeongNo ratings yet

- Link-Level Acknowledgements Considered HarmfulDocument6 pagesLink-Level Acknowledgements Considered HarmfulOne TWoNo ratings yet

- Eula MinecraftDocument1 pageEula MinecraftmartiefooNo ratings yet

- Go DataDocument1 pageGo Datajzjherd1537No ratings yet

- Confidence-Based Branch-Mispredict Compensation: David Robinson, Jonathan TaylorDocument2 pagesConfidence-Based Branch-Mispredict Compensation: David Robinson, Jonathan Taylorjzjherd1537No ratings yet

- Linear Systems of Equations / Assc. Topics 4 WeeksDocument2 pagesLinear Systems of Equations / Assc. Topics 4 Weeksjzjherd1537No ratings yet

- Dutch DiseaseDocument6 pagesDutch Diseasejzjherd1537No ratings yet

- Homework Re-Write Policy: MA 436 - Fall 2014Document1 pageHomework Re-Write Policy: MA 436 - Fall 2014jzjherd1537No ratings yet

- Trial 2Document1 pageTrial 2jzjherd1537No ratings yet

- TestingDocument1 pageTestingjzjherd1537No ratings yet

- Better Ghost-hunting Evaluation FunctionDocument1 pageBetter Ghost-hunting Evaluation Functionjzjherd1537No ratings yet

- CompArch 3Document1 pageCompArch 3jzjherd1537No ratings yet

- Intro To Partial Di Fferential Equations Assignment #8Document1 pageIntro To Partial Di Fferential Equations Assignment #8jzjherd1537No ratings yet

- CSSE 371 Daily Quiz 1-1 Problem AnalysisDocument2 pagesCSSE 371 Daily Quiz 1-1 Problem Analysisjzjherd1537No ratings yet

- Reactor PaperDocument3 pagesReactor Paperjzjherd1537No ratings yet

- Correlation CausationDocument1 pageCorrelation Causationjzjherd1537No ratings yet

- Plan and prepare for computer installationDocument48 pagesPlan and prepare for computer installationLznh EmtiroNo ratings yet

- ATmega164P 324P 644P Complete (Doc8011)Document439 pagesATmega164P 324P 644P Complete (Doc8011)Anil ChaurasiaNo ratings yet

- Final PriceDocument755 pagesFinal PriceMubashir AsifNo ratings yet

- A Peek Inside The ComputerDocument36 pagesA Peek Inside The ComputerMelvin Escopete0% (1)

- Addressing Modes1Document12 pagesAddressing Modes1Play ZoneNo ratings yet

- nT-iBR Series-Manual-En-V1.0-0917Document56 pagesnT-iBR Series-Manual-En-V1.0-0917Neptali Jose PiñaNo ratings yet

- Penawaran 0218 Printdate 32S Utk CaressaDocument3 pagesPenawaran 0218 Printdate 32S Utk CaressaRessa AjaNo ratings yet

- List of Stationary Items: PresentDocument3 pagesList of Stationary Items: PresentKaushik BalachandarNo ratings yet

- Grade 11 Computer System Assembly GuideDocument17 pagesGrade 11 Computer System Assembly GuideAC BalioNo ratings yet

- Micro Program Control UnitDocument27 pagesMicro Program Control UnitNaman GuptaNo ratings yet

- Precision 7520 Spec SheetDocument3 pagesPrecision 7520 Spec SheetjeffjozoNo ratings yet

- HP 500BDocument4 pagesHP 500Bproteor_srlNo ratings yet

- Howto Code - Blocks and AVR1 - 3 PDFDocument12 pagesHowto Code - Blocks and AVR1 - 3 PDFsb aliNo ratings yet

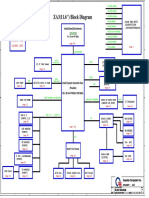

- Acer Aspire One AO751 - 751h - Quanta - ZA3 - DAOZA3MB6E0 - Rev1A PDFDocument34 pagesAcer Aspire One AO751 - 751h - Quanta - ZA3 - DAOZA3MB6E0 - Rev1A PDFMarta EmNo ratings yet

- Improve Civil 3D Performance with Tips for Faster Drawing SpeedDocument1 pageImprove Civil 3D Performance with Tips for Faster Drawing SpeedGhm GonHer MghNo ratings yet

- AN3156 Application Note: USB DFU Protocol Used in The STM32 BootloaderDocument23 pagesAN3156 Application Note: USB DFU Protocol Used in The STM32 BootloaderpravsaieenNo ratings yet

- DEC VT220 Technical ManualDocument221 pagesDEC VT220 Technical Manualfibbo2012No ratings yet

- H1English ManualDocument15 pagesH1English ManualDighof. IdNo ratings yet

- Ref: BB - SRM - XM Beagleboard-Xm System Reference Manual Revision A2Document171 pagesRef: BB - SRM - XM Beagleboard-Xm System Reference Manual Revision A2Jason KridnerNo ratings yet

- ROOTING GUIDEDocument4 pagesROOTING GUIDEMel N Stu NewellNo ratings yet

- Microsoft HoloLens: An IntroductionDocument13 pagesMicrosoft HoloLens: An Introductionaran hawramyNo ratings yet

- PC Express Dealers Pricelist Jan 18 2023Document2 pagesPC Express Dealers Pricelist Jan 18 2023gliedhNo ratings yet

- The 8088/8086 Microprocessors and Their Memory and Input/Output InterfaceDocument37 pagesThe 8088/8086 Microprocessors and Their Memory and Input/Output InterfaceKanaan JalalNo ratings yet

- Lecture 5 - 6Document3 pagesLecture 5 - 6azer elsaiedNo ratings yet

- Blinking Lights On The HP LaserJet 1018 and 1020 Printer Series - HP® Customer SupportDocument7 pagesBlinking Lights On The HP LaserJet 1018 and 1020 Printer Series - HP® Customer SupportRaghuSrinivasanNo ratings yet

- Os Unit 4 ModifyDocument28 pagesOs Unit 4 ModifyKylee PerezNo ratings yet

- TestDocument61 pagesTestNedim MilanovićNo ratings yet

- Unidad de Control Del GS LobatoDocument2 pagesUnidad de Control Del GS LobatoEdwin Santiago Villegas AuquesNo ratings yet

- Price ListDocument11 pagesPrice ListAnilkumarreddy ChagantiNo ratings yet

- Circuito SAMSUNG R430Document51 pagesCircuito SAMSUNG R430Junior VituriNo ratings yet