Professional Documents

Culture Documents

VLSI Lab Maual

Uploaded by

Muhammad Kamran AkramCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

VLSI Lab Maual

Uploaded by

Muhammad Kamran AkramCopyright:

Available Formats

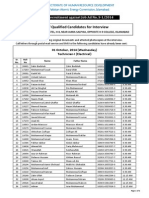

The University of Faisalabad

VLSI Systems Design

LAB MANUAL

VLSI SYSTEMS

EE-414

Prepared By:

Engr. Tafseer Ahmed (Lab Engineer)

Approved By:

Engr. Faraz Khan (Lecturer)

SCHOOL OF ELECTRICAL ENGINEERING

VLSI Systems Design

The University of Faisalabad

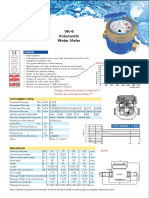

SOFTWARE REQUIREMENTS

S.No.

Software Title

DSCH

Microwind

Description

The

DSCH

program

is

logic

editor

and

Simulator.DSCH is used to validate the architecture of logic

circuit before the microelectronics design is started.DSCH

provides a user-friendly environment for hierarchical logic

design, and fast simulation with delay analysis, which

allows the design and validation of complex logic

structure. DSCH also features the symbols, models and

assembly support for 8051 and 80f64. DSCH also includes

an interface to SPICE.

The Microwind program allows the student to design and

simulate an integrated circuit at physical description level.

The package contains a library of common logic and analog

ICs to view and simulate. Microwind includes all the

commands for a mask editor as well as original tools never

gathered before in a single module (2D and 3D process

view Verilog Compiler, tutorial on MOS devices). You gain

access to circuit simulation by pressing one single key. The

electric extraction of your circuit is automatically

performed and the analog simulator produces voltage and

current curves immediately.

Xilinx ISE (Integrated Software Environment) is a

software tool produced by Xilinx for synthesis and

analysis of HDL designs, enabling the developer to

Xilinx with FPGA synthesize ("compile") their designs, perform timing

analysis, examine RTL diagrams, simulate a design's

reaction to different stimuli, and configure the target device

with the programmer.

The University of Faisalabad

VLSI Systems Design

CONTENTS

Lab No. Lab Title

Page

Lab # 1

Introduction to DSCH and CMOS 0.25 micron Technology

Inverter Implementation

05

Lab # 2

Introduction to Microwind and CMOS 0.25 micron Technology

Inverter Layout Implementation in Microwind

09

Lab # 3

Layout of Basic Gates using CMOS 0.25micron Technology in

Microwind.

17

Lab # 4

Layout of XOR and XNOR Gates using Static Complementary

CMOS Logic and Pass Transistor Logic

22

Lab # 5

Layout of Multiplexer using Transmission Gates in Microwind

25

Lab # 6

Design and implementation of Complex Gates using Static Ratio

(Generic & Pseudo-NMOS) Logic in Microwind

27

Lab # 7

Design and implementation of Layout of Complex Gates using

Static DCVSL and Pass Transistor LogicinMicrowind

29

Lab # 8

Design and implementation of Complex Gates using Dynamic

Domino Logic & np-CMOS Logic Layout in Microwind

35

Lab # 9

Study of transistor sizing and implementation of Layout of Half

Adder inMicrowind

37

Lab # 10

Design and implementation of Layout of Full Adder using CMOS

0.25 micron Technology in Microwind

42

Lab # 11

To Perform the Basic Digital Logic Gate (AND Gate, OR Gate,

NOT Gate, NAND Gate, NOR Gate) Operation using VHDL

Language with the help of CPLD Development Platform.

46

Lab # 12

To Design a Multiplexer (4-to-1 and 8-to-1) in Verilog HDL

Language using CPLD Development Platform

54

VLSI Systems Design

The University of Faisalabad

Lab # 13

To Design a Full Adder and Half Adder in VHDL Language

using FPGA Circuit board.

58

Lab # 14

To Design a BCD to Seven Segment Decoder using VHDL

Language on CPLD Development Platform and Output showed

on Seven Segment Display.

63

Lab # 15

To Design an Octal to Binary number system and output of the

number system to be displayed on Seven Segment Display and

LEDs.

67

The University of Faisalabad

VLSI Systems Design

Lab 01

Lab Title: Introduction to DSCH and CMOS 0.25 micron Technology Inverter

Implementation

Lab Objective: In this lab students will be introduced to a Layout based EDAtool

DSCH and the introduction will be accompanied with an implementation of simple

Gate at Gate level and at CMOS switch level.. The tool used in this lab is DSCH

(Digital Schematics).

The goals for this Lab are:

Familiarity and Hands on Example using the tool.

Schematic Design in using the tool.

Schematic Design Verification.

Simulation of the design

Tool used: DSCH

Lab Description:

Theory:

Ideal switches can be used to construct logic gates. NMOS behaves like assert high

switch and strong pass logic 0. On the other hand PMOS behaves like assert low switch

and strong pass logic 1.

To design CMOS structure, there are two networks i.e. Pull up & Pull down networks.

The output of CMOS is in between these networks. Pull down network is constructed

from NMOS transistors while for Pull up networks, PMOS elements are used. Battery is

connected to pull up network as they strongly pass logic 1 while Pull down network is

grounded.

Now how to design these? First see the expression and design the Pull down network

according to it via NMOS entities. The Pull up is formed just opposite to that of Pull

down network i.e. if two NMOS were parallel to each other, then they must be in series in

the Pull up network. And we see that for every input there are two transistors. This rule of

designing is just meant for those expressions containing whole complement on them. If

there is no whole complement, then try to make it consider via DLD rules & laws.

DSCH Utilities:

User-friendly environment for rapid design of logic circuits.

Handles both conventional pattern-based logic simulation and intuitive on-screen

mouse driven simulation.

Supports hierarchical logic design.

Built-in extractor which generates a SPICE net list from the schematic diagram

(Compatible with PSPICE and WinSpice).

Current and power consumption analysis.

Generates a VERILOG description of the schematic for layout editor.

Immediate access to symbol properties (Delay, fan-out).

Sub-micron, deep-submicron, nanoscale technology support.

5

VLSI Systems Design

The University of Faisalabad

Supported by huge symbol library.

INSTRUCTIONS:

1) Open the DSCH by double clicking it located in the installed directory of Dsch2

The following screen will open:

2) Select the foundry using the command File > Select Foundry

3) Select 0.25-micron process by selecting cmos025.tec file. Click Open tab to

continue.

VLSI Systems Design

The University of Faisalabad

4) Save the design as Lab01 using the command File > Save as.

5) Now we will make the above schematics manually. Click on the pMOS and

nMOS symbol button in the Symbol Library and drag it the schematic design

areas as indicated in the figure.

6) You can view the Timing diagram by clicking on Timing Diagram command

button on the icon bar.

VLSI Systems Design

The University of Faisalabad

7) Save the design.

8) Explore the Schema to new symbol, Make Verilog File, Generate Spice netlist in

the File menu, delays of each symbol and the Advanced Tab in the symbol library

Lab Report :

Give a short description of the contents of the lab

Include block diagram/diagrams of your design in the lab report

Describe your design approach and explain the working of each the schematic

Include the results in your report

The University of Faisalabad

VLSI Systems Design

Lab 02

Lab Title: Introduction to Microwind and CMOS 0.25 micron Technology

Inverter Layout Implementation in Microwind

Lab Objective: In this lab students will be introduced to a Layout based EDAtool

Microwind and the introduction will be accompanied with analysis of MOS

transistors. The tool used in this lab is Microwind.

The tasks given in the lab include,

1)

2)

3)

4)

Familiarity and Hands on Example using the tool.

Layout Design using the tool.

Study of MOSFET Characteristics.

Analog Simulation of MOSFETs.

Tool used: DSCH,Microwind

Lab Description:

MOSFET:

The Metal Oxide Semiconductor Field Effect Transistor is very important part of Digital

Integrated Circuits. It is mostly used as switch in digital design. MOSFET is a four

terminal device. The voltage applied to the gate terminal determine the current flow

between drain and source terminals. The body/substrate of the transistor is the fourth

terminal. Mostly the fourth terminal (body/substrate) of the device is connected to dc

supply that is identical for all devices of the same type (GND fro nMOS and Vdd for

pMOS). Usually this terminal is not shown on the schematics.

nMOS:

The nMOS transistor consists of n+ drain and source diffusion regions, which are

embedded in a p-type substrate. The electrons in the channel beneath the gate between

source and drain terminal are responsible for the current flow.

pMOS:

The pMOS transistor consists of p+ drain and source diffusion regions, which are

embedded in an n-type substrate. The holes in the channel beneath the gate between

source and drain terminal are responsible for the current flow.

CMOS:

The CMOS (Complementary MOS) consist of both p-type and n-type MOS. The

advantage of CMOS is its low power design due its Static behavior.

Design/ Diagram/Circuit:

VLSI Systems Design

The University of Faisalabad

Lab Instructions

a) Open the Microwind2 by double clicking it located in the installed directory of

microwind2-7

The following screen will be appeared

b) Select the foundry using the command File > Select Foundry

c) Select 0.25-micron process by selecting cmos025.tec file. Click Open tab to

continue.

10

VLSI Systems Design

The University of Faisalabad

d) Save the design as Lab02 using the command File > Save as.

e) Create an nMOS by using the nMOS generator button in the Palette

You can set the width and length of MOS by typing in the fields Width MOS

andLength MOS either in micron or in lambda units as indicated in the above

figure.Click on Generate Device Tab to generate the device.

11

VLSI Systems Design

The University of Faisalabad

f) Apply the voltages and output node using the symbol buttons Vdd, Gnd, Add aPulse,

and Visible node in the Palette menu, as indicated in the following figure.You can use

the Stretch/Move command button for these actions.

g) Click on the Run Tab on the Tool bar menu to start the simulation or using the

command Simulate > Run Simulation.

h) Now apply the Vdd to the n+ diffusion or drain terminal instead of Vss, run the

simulation again.

12

The University of Faisalabad

VLSI Systems Design

Analyze the simulation waveform, use different values of voltages for Vdd by double

clicking on it and set the voltage level. Now we will make the above schematics.

CMOS Inverter

CMOS Inverter/NOT gate is considered to be the heart of VLSI circuits, based on the

understanding of NOT gate we can extend it easily to NAND and NOR gates which are

the basic building blocks of more complex circuits e.g. multipliers and microprocessors.

As per discussion and design on white board in the Lab, a NOT gate can be implemented

using two FETs i.e. a pFET and an nFET both connected in series, in which Vdd is

supplied to pFET and nFET is grounded, input x is applied to the gate terminals of both

and the output is obtained at node y.

Design/ Diagram/Circuit

As covered in the lectures we know that the mobility of the holes is less than that of

electrons, and in CMOS inverter pFET is responsible for the conduction of current

leading a logic 1 at the output, while nFET is responsible for the conduction of current

leading a logic 0 at the output. This means that the gate delay form low to high will be

greater than the gate delay for low to high voltage.

Lab Instructions

Automated Layout from the Schematic Design

1. Open DSCH and select the foundry cmos025.

2. Save the design as Save as as Lab02. Save the design frequently during lab

session.

3. Draw the circuit diagram of inverter.

4. Check for floating point if any.

5. Simulate the Design

6. Make a Verilog file of the design.

7. Open Microwind and select the foundry cmos025.

13

VLSI Systems Design

The University of Faisalabad

8. Compile the Verilog file of inverter Lab02.txt for Compile > Compile Verilog File

command

9. Save the design.

10. Simulate the design using the Run command

11. Analyze configuration delay, gate delay, current, power, and midpoint voltage.

12. Repeat the design for different value of transistor size and supply voltage

andcarefully observe the changes in configuration delay, gate delay, current, power, and

midpoint voltage.

Manual Layout of Inverter

1. Open Microwind and select the foundry cmos025.

2. Save the design as Save as as Lab02, and save the design frequently during the

Lab session.

3. Draw the layout of nMOS using MOS Generator

4. Draw the layout of pMOS using MOS Generator by setting the appropriate width of

pMOS.

5. Connect the two transistors using Metal 1 as per design.

6. Draw the rails of VDD and ground rails above and below.

7. Connect the nWell to VDD

8. Check the design using DRC for any design rule violation and correct the design in

case of error, again run the DRC and check for errors. Or run the DRC after each change

in the layout.

9. Check for Electrical connections to be valid.

10. Add inputs and outputs to the design; also add virtual capacitance at the output in

your design.

11. Simulate the Design. Observe the values of configuration delay, gate delay, power,

current, VTC, and area.

12. Repeat the design using for different values of transistors dimensions, supply

voltages. And observe the changes in configuration delay, gate delay, power, current,

VTC, and area carefully. Make a conclusion of your observations.

14

VLSI Systems Design

The University of Faisalabad

15

VLSI Systems Design

The University of Faisalabad

Lab Report

Give a short description of the contents of the lab

Include block diagram/diagrams of your design in the lab report

Describe your layout design approach parameters and explain the effects of each the

parameter

Include layout of your design also add your name on the design for evaluation purpose.

Include the results in timing waveform format in your report

16

The University of Faisalabad

VLSI Systems Design

Lab 03

Lab Title:Layout of Basic Gates using CMOS 0.25micron Technology in Microwind.

Lab Objective:In this lab students will design and implement the layouts of different

CMOS gates, which includes NAND, AND NOR, OR and a Complex Gate. The tool

used in this lab is Microwind.

The tasks given in the lab include,

1) Design of CMOS NAND, AND, NOR, OR Gates and a Complex Gate.

2) Layout Design using the tool.

3) Gate delay, area, power and current analysis and the effects of transistor sizing on

these parameters.

Tool used: Microwind

Lab Description:

a) NAND Gate:

As per discussion and design on white board in the Lab, a NAND gate can be

implemented using four FETS i.e. two pFETs and two nFETs as the inputs of the gate is

two. pFETs are connected in parallel while nFETs are connected in series, Vdd is

supplied to the parallel combination of pFETs while the series combination of nFETs is

grounded. Inputs a & b are applied to the gate terminals of all FETs, and the output f is

obtained from the common junction of these series and parallel combinations as

illustrated in NAND circuit under the heading of Design Diagram/Circuit.

b) NOR Gate:

As per discussion and design on white board in the Lab, a NOR gate can be implemented

using four FETS i.e. two pFETs and two nFETs as the inputs of the gate is two. pFETs

are connected in series while nFETs are connected in parallel, Vdd is supplied to the

series combination of pFETs while the parallel combination of nFETs is grounded. Inputs

a & b are applied to the gate terminals of all FETs, and the output f is obtained from the

common junction of these parallel and series combinations as illustrated in NOR circuit

under the heading of Design Diagram/Circuit.

c) Complex Gate

The expression for the complex gate is given as under

As per discussion and design on white board in the Lab, this complex gate can

be

implemented

as

under.

17

VLSI Systems Design

The University of Faisalabad

For pFETs Array

Group1: Three pFETs with inputs c, d and d at its gate terminals are connected in

parallel.

Group2: Two pFETs with inputs a and d are in parallel and is connected in series

with Group1

For nFETs Array

Group1: Three nFETs with inputs c, d and d at its gate terminals are connected in

series.

Group2: Two nFETs with inputs a and d are in series and is connected in parallel

with Group1

Design/ Diagram/Circuit

(a)

Symbol, Truth Table and CMOS circuit of NAND Gate

(b)

Symbol, Truth Table and CMOS circuit of NOR Gate

18

VLSI Systems Design

The University of Faisalabad

Design Layout:

NOR Gate:

Simulation Diagram:

19

VLSI Systems Design

The University of Faisalabad

NAND Gate:

Simulation Diagram:

20

VLSI Systems Design

The University of Faisalabad

Lab Report:

21

The University of Faisalabad

VLSI Systems Design

Lab 04

Lab Title: Layout of XOR and XNOR Gates using Static Complementary CMOS

Logic and Pass Transistor Logic

Lab Objective: In this lab students will design and implement the layouts of XORand

XNOR GateS. The tool used in this lab is Microwind.

.

The tasks given in the lab include,

1) Design of XOR and XNOR Gates.

2) Layout Design using the tool.

3) Gate delay, area, power and current analysis and the effects of transistor sizing

on these parameters

Tool used: DSCH, Microwind

Lab Description:

Schematic of XOR Gate

22

VLSI Systems Design

The University of Faisalabad

23

VLSI Systems Design

The University of Faisalabad

24

The University of Faisalabad

VLSI Systems Design

Lab 05

Lab Title: Layout of Multiplexer using Transmission Gates in Microwind

Lab Objective: In this lab students will design and implement the layout of Multiplexer

using transmission Gates. The tool used in this lab is Microwind.

The tasks given in lab include:

1) Design of 8 input 3 select line Multiplexer.

2) Layout Design using the tool.

3) Gate delay, area, power and current analysis and the effects of

transistor sizing on these parameters.

Lab Description:

Multiplexer:

Generally speaking, a multiplexer is used to transmit a large amount of information

through a smaller number of connections. A digital multiplexor is a circuit that selects

binary information from one of many input logic signals and directs it to a single input

line. A behavioral description of the multiplexor is the case statement:

The usual symbol for the multiplexor is given in figure 6-67. It consists of the two

multiplexed inputs in0 and in1 on the left side, the command sel at the bottom of the

symbol, and the output f on the right.

25

VLSI Systems Design

The University of Faisalabad

Design of the Multiplexer:

26

The University of Faisalabad

VLSI Systems Design

Lab 06

Lab Title: Design and implementation of Complex Gates using Static Ratioed (Generic

& Pseudo-NMOS) Logic in Microwind

Lab Objective: In this lab students will design and implement the basic and complex

gates by use of the Ratioed Logic. The Generic Ratioed Logic will be implemented only

in DSCH and Pseudo-NMOS Ratioed Logic will be implemeted in Both DSCH &

Microwind.

The tasks given in lab include:

1) Design of basic & complex gates using Ratioed Logic.

2) Layout Design using the tool.

3) Gate delay, area, power and current analysis and the effects of

transistor sizing on these parameters.

Tools Used:DSCH, Microwind

Lab Description:

Ratioed Logic:

Ratioed logic is an attempt to reduce the number of transistors required to implement a

given logic function, at the cost of reduced robustness and extra power dissipation. The

purpose of the PUN in complementary CMOS is to provide a conditional path between

VDD and the output when the PDN is turned off. In ratioed logic, the entire PUN is

replaced with a single unconditional load device that pulls up the output for a high output.

Instead of a combination of active pull-down and pull-up networks, such a gate consists

of an NMOS pull-down network that realizes the logic function, and a simple load

device. Figure shows an example of ratioed logic, which uses a grounded PMOS load and

is referred to as a pseudo-NMOS gate.

The clear advantage of pseudo-NMOS is the reduced number of transistors (N+1 versus

2N for complementary CMOS). The nominal high output voltage (VOH) for this gate is

VDD since the pull-down devices are turned off when the output is pulled high

27

The University of Faisalabad

VLSI Systems Design

(assuming that VOL is below VTn). On the other hand, the nominal low output voltage is

not 0 V since there is a fight between the devices in the PDN and the grounded PMOS

load device. This results in reduced noise margins and more importantly static power

dissipation. The sizing of the load device relative to the pull-down devices can be used to

trade-off parameters such a noise margin, propagation delay and power dissipation. Since

the voltage swing on the output and the overall functionality of the gate depends upon the

ratio between the NMOS and PMOS sizes, the circuit is called ratioed. This is in contrast

to the ratioless logic styles, such as complementary CMOS, where the low and high

levelsdo not depend upon transistor sizes.

Design of NOR Gate:

Layout Using Pseudo NMOS Logic

28

The University of Faisalabad

VLSI Systems Design

Lab 07

Lab Title: Design and implementation of Layoutof Complex Gates using Static DCVSL

and Pass Transistor LogicinMicrowind

Lab Objective: In this lab students will design and implement the basic and complex

gates by use of the Differential Cascade Voltage swing logic and Pass Transistor Logic.

The tasks given in lab include:

1) Design of basic & complex gates using DCVSL & CPL.

1) Layout Design using the tool.

2) Gate delay, area, power and current analysis and the effects of

transistor sizing on these parameters.

Tools Used:DSCH, Microwind

Lab Description:

Differential Cascade Voltage Swing Logic:

It is possible to create a ratioed logic style that completely eliminates static currents

andprovides rail-to-rail swing. Such a gate combines two concepts: differential logic

and positive feedback. A differential gate requires that each input is provided in

complementaryformat, and produces complementary outputs in turn. The feedback

mechanism ensuresthat the load device is turned off when not needed. An example

of such a logic family is Differential Cascade Voltage Switch Logic (or DCVSL).

The pull-down networks PDN1 and PDN2

use NMOS devices and are

mutuallyexclusive (this is, when PDN1 conducts, PDN2 is off, and when PDN1 is

off, PDN2 conducts), such that the required logic function and its inverse are

simultaneously implemented. Assume now that, for a given set of inputs, PDN1

conducts while PDN2 does not and that Out and Outare initially high and low,

respectively. Turning on PDN1, causesOut to be pulled down, although there is still

a fight between M1 and PDN1. Out is in ahigh impedance state, as M2 and PDN2

are both turned off.

The resulting circuit exhibits a rail-to-rail swing, and the static power dissipation

29

VLSI Systems Design

The University of Faisalabad

iseliminated: in steady state, none of the stacked pull-down networks and load

devices are simultaneously conducting. However, the circuit is still ratioed since the

sizing of thePMOS devices relative to the pull-down devices is critical to

functionality, not just performance. In addition to the problem of increase

complexity in design, this circuit style still has a power-dissipation problem that is

due to cross-over currents. During the transition, there is a period of time when

PMOS and PDN are turned on simultaneously, producing a short circuit path.

Pass Transistor Logic:

A popular and widely-used alternative to complementary CMOS is pass-transistor

logic, which attempts to reduce the number of transistors required to implement

logic by allowing the primary inputs to drive gate terminals as well as source/drain

terminals. This is in contrast to logic families that we have studied so far, which

only allow primary inputs to drive the gate terminals of MOSFETS.

Figure shows an implementation of the AND function constructed that way, using

only NMOS transistors. In this gate, if the B input is high, the top transistor is turned

on and copies the input A to the output F.When B is low, the bottom pass transistor

is turned on and passes a 0. The switch driven by B seems to be redundant at first

glance. Its presence is essential to ensure that the gate is static, this is that a lowimpedance path exists to the supply rails under all circumstances, or, in this

particular case, when B is low.

Differential Pass Transistor Logic:

For high performance design, a differential pass-transistor logic family, called CPL

or DPL, is commonly used. The basic idea (similar to DCVSL) is to accept true and

complementary inputs and produce true and complementary outputs. A CPL gate

(AND/NAND) is shown in Figure.

30

VLSI Systems Design

The University of Faisalabad

In summary, CPL is a conceptually simple and modular logic style. Its applicability

depends strongly upon the logic function to be implemented. The availability of a

simplex OR as well of the ease of implementing some specific gate structures makes

it attractive for structures such as adders and multipliers. Some extremely fast and

efficient implement \tations have been reported in that application domain. When

considering CPL,the designer should not ignore the implicit routing overhead of the

complementary signals.

Design of AND/NAND Gate Using DCVSL:

Schematic:

Layout:

31

VLSI Systems Design

The University of Faisalabad

Timing Diagram:

Design of XOR/XNOR Gate Using CPL:

Schematic:

32

VLSI Systems Design

The University of Faisalabad

Layout:

Timing Diagram:

33

VLSI Systems Design

The University of Faisalabad

34

The University of Faisalabad

VLSI Systems Design

Lab 08

Lab Title: Design and implementation of Complex Gates using Dynamic Domino Logic

& np-CMOS Logic Layout in Microwind

Lab Objective: In this lab students will design and implement the basic and complex

gates by use of the Domino logic and np-CMOS Logic.

The tasks given in lab include:

2) Design of basic & complex gates using Dynamic Logic.

3) Layout Design using the tool.

4) Gate delay, area, power and current analysis and the effects of

transistor sizing on these parameters.

Tools Used:DSCH, Microwind

Lab Description:

Domino Logic:

A Domino logic module consists of an n-type dynamic logic block followed by a

static inverter (Figure 6.65). During precharge, the output of the n-type dynamic

gate is charged up to VDD, and the output of the inverter is set to 0. During

evaluation, the dynamic gate conditionally discharges, and the output of the

inverter makes a conditional transition from 0 to 1. If one assumes that all the inputs

of a Domino gate are outputs of other Domino gates

3, then it is ensured that all inputs are set to 0 at the end of the precharge phase, and

that the only transitions during evaluation are 0 to 1 transitions. The formulated rule

is hence beyed. The introduction of the static inverter has the additional advantage

that the fan-out of the ate is driven by a static inverter with a low-impedance output,

which increases noise immunity. The buffer furthermore reduces the capacitance of

the dynamic output node by separating internal and load capacitances.

Consider now the operation of a chain of Domino gates. During precharge, all inputs

are set to 0. During evaluation, the output of the first Domino block either stays at 0

or makes a 0 to 1 transition, affecting the second gate. This effect might ripple

through the whole chain, one after the other, similar to a line of falling dominoes hence the name.

35

VLSI Systems Design

The University of Faisalabad

n-p CMOS Logic:

The Domino logic presented in the previous section has the disadvantage that each

dynamic gate requires an extra static inverter in the critical path to make the circuit

functional. np-CMOS, provides an alternate approach to cascading dynamic logic by

using two flavors (n-tree and p-tree) of dynamic logic. In a p-tree logic gate, PMOS

devices are used to build a pull-up logic network, including a PMOS evaluation

transistor. The NMOS predischarge transistor drives the output low during

precharge. The output conditionally makes a 0 to 1 transition during evaluation

depending on its inputs.

np-CMOS logic exploits the duality between n-tree and p-tree logic gates to

eliminate the cascading problem. If the n-tree gates are controlled by CLK, and ptree gates are controlled using CLK, n-tree gates can directly drive p-tree gates, and

vice-versa. Similar to Domino, n-tree outputs must go through an inverter when

connecting to another n-tree gate. During the precharge phase (CLK = 0), the output

of the n-tree gate, Out1, is charged to VDD, while the output of the p-tree gate,

Out2, is pre-discharged to 0V. Since the n-tree gate connects PMOS pull-up devices,

the PUN of the p-tree is turned off at that time. During evaluation, the output of the

n-tree gate can only make a 1 to 0 transition, conditionally turning on some

transistors in the p-tree. This ensures that no accidental discharge of Out2can occur.

Similarly, n-tree blocks can follow p-tree gates without any problems, as the inputs

to the n-gate are precharged to 0. A disadvantage of the np-CMOS logic style is that

the p-tree blocks are slower than the n-tree modules, due to the lower current drive

of thePMOS transistors in the logic network. Equalizing the propagation delays

requires extra area.

36

The University of Faisalabad

VLSI Systems Design

Lab 09

Lab Title: Study of transistor sizing and implementation of Layout of Half Adder

inMicrowind

Lab Objective: In this lab students will learn the effects of changes in width of PMOS &

NMOS and also implement the half adder by use of the suitable CMOS logic.

The tasks given in lab include:

1) Effect of transistor sizing (inverter).

2) Designing Schematic of the Half Adder

3) Layout Design using the tool.

4) Gate delay, area, power and current analysis and the effects of

transistor sizing on these parameters.

Tools Used:DSCH, Microwind

Lab Description:

Transistor Sizing:

A symmetrical inverter is an inverter in which PMOS andNMOS are sized such that

the rise and fall delays are identical. The load capacitance of theinverter can be

divided into an intrinsic and an extrinsic component, or CL = Cint + Cext.Cint

represents the self-loading or intrinsic output capacitance of the inverter, and is

associated with the diffusion capacitances of the NMOS and PMOS transistors as

well as thegate-drain overlap (Miller) capacitances. Cext is the extrinsic load

capacitance, attributableto fanout and wiring capacitance.

Half Adder:

The half adder adds two single binary digits A and B. It has two outputs, sum (S)

and carry (C). The carry signal represents an overflow into the next digit of a multidigit addition. The value of the sum is 2C + S. The simplest half-adder design,

incorporates an XOR gate for S and an AND gate for C. With the addition of an OR

gate to combine their carry outputs, two half adders can be combined to make a full

adder.

The half-adder adds two input bits and generates a carry and sum, which are the two

outputs of half-adder.The input variables of a half adder are called the augend and

addend bits.The output variables are the sum and carry. Its truth table is given by:

37

VLSI Systems Design

The University of Faisalabad

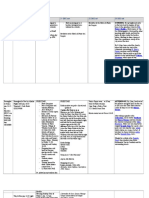

COMPARISON OF CMOS PROPERTIES AT DIFFERENT SIZES

TIMING DIAGRAM

38

The University of Faisalabad

VLSI Systems Design

CHARACTERISTIC CURVES FOR DIFFERENT PMOS WIDTHS

TABLE

wp

0.5 m

1.00 m

1.5 m

2.00 m

2.5 m

3.00 m

vm

1.05 v

1.437 v

1.78 v

1.9 v

2.01 v

2.1 v

voL

0.31 v

0.37 v

0.4 v

0.42 v

0.45 v

0.50 v

Half Adder:

Design Schematic:

39

VLSI Systems Design

The University of Faisalabad

Layout:

Timing Diagram:

40

VLSI Systems Design

The University of Faisalabad

41

The University of Faisalabad

VLSI Systems Design

Lab 10

Lab Title: Design and implementation of Layout of Full Adder usingCMOS 0.25 micron

Technology in Microwind.

Lab Objective:In this lab students will design and implement the layouts of

FullAdder.Delay, area, power and currents of full adder will be observed. This lab

assumed that students are familiar with Microwind and Lambda Based design rules. The

tool used in this lab is Microwind.

The tasks given in lab include:

1. Design of CMOS Full Adder layout.

2. Layout Design using the tool.

3. Gate delay, area, power and current analysis and the effects of transistor sizingon

these parameters.

Tools used: Microwind

Lab Description:

42

VLSI Systems Design

The University of Faisalabad

43

VLSI Systems Design

The University of Faisalabad

44

VLSI Systems Design

The University of Faisalabad

45

The University of Faisalabad

VLSI Systems Design

Lab 11

Objective:

To Perform the Basic Digital Logic Gate (AND Gate, OR Gate, NOT Gate, NAND Gate,

NOR Gate) Operation using VHDL Language with the help of CPLD Development

Platform or FPGA Circuit Board.

-----------------------------------------------------------------------------------------------------------AND Gate:

A Logic Circuit whose output is Logic 1 if and only if all of inputs are Logic 1.

Logic Diagram:

Truth Table:

Inputs

A

0

0

1

1

B

0

1

0

1

Output

Y

0

0

0

1

VHDL Code for AND Gate:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity andgate is

Port( A

:

in std_logic;

B

:

in std_logic;

Y

:

out std_logic

);

end andgate;

architecture Behavioral of andgate is

begin

Y <= A and B;

end Behavioral;

User Constraints File (UCF) of AND Gate for CPLD XC95108PC84:

NET

LOC=P1;

#DIP1

46

The University of Faisalabad

VLSI Systems Design

NET

NET

B

Y

LOC=P2;

LOC=P14;

#DIP2

#LED1

User Constraints File (UCF) of AND Gate for SPARTAN 2 XC2S200PQ208:

NET

NET

NET

A

B

Y

LOC=P195;

LOC=P199;

LOC=P111;

#DIP1

#DIP2

#LED1

User Constraints File (UCF) of AND Gate for SPARTAN 2 XC2S30PQ208 to J5

Connector:

NET

NET

NET

A

B

Y

LOC=P3;

LOC=P49;

LOC=P5;

#DIP1

#DIP2

#LED1

User Constraints File (UCF) of AND Gate for SPARTAN 2 XC2S30PQ208 to J6

Connector:

NET

NET

NET

A

B

Y

LOC=P57;

LOC=P110;

LOC=P59;

#DIP1

#DIP2

#LED1

User Constraints File (UCF) of AND Gate for SPARTAN 2 XC2S30PQ208 to J7

Connector:

NET

NET

NET

A

B

Y

LOC=P111;

LOC=163;

LOC=P114;

#DIP1

#DIP2

#LED1

OR Gate:

A Logic Circuit whose output is Logic 0 if and only if all of its inputs are Logic 0.

Logic Diagram

Truth Table:

Inputs

A

0

B

0

Output

Y

0

47

The University of Faisalabad

VLSI Systems Design

0

1

1

1

0

1

1

1

1

VHDL Code for OR Gate:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity orgate is

Port( A

:

in std_logic;

B

:

in std_logic;

Y

:

out std_logic

);

end orgate;

architecture Behavioral of orgate is

begin

Y <= A or B;

end Behavioral;

User Constraints File (UCF) of OR Gate for CPLD XC95108PC84:

NET

NET

NET

A

B

Y

LOC=P1;

LOC=P2;

LOC=P14;

#DIP1

#DIP2

#LED1

User Constraints File (UCF) of OR Gate for SPARTAN 2 XC2S200PQ208:

NET

NET

NET

A

B

Y

LOC=P195;

LOC=P199;

LOC=P111;

#DIP1

#DIP2

#LED1

User Constraints File (UCF) of OR Gate for SPARTAN 2 XC2S30PQ208 to J5 Connector:

NET

NET

NET

A

B

Y

LOC=P3;

LOC=P49;

LOC=P5;

#DIP1

#DIP2

#LED1

User Constraints File (UCF) of OR Gate for SPARTAN 2 XC2S30PQ208 to J6 Connector:

48

The University of Faisalabad

VLSI Systems Design

NET

NET

NET

A

B

Y

LOC=P57;

LOC=P110;

LOC=P59;

#DIP1

#DIP2

#LED1

User Constraints File (UCF) of OR Gate for SPARTAN 2 XC2S30PQ208 to J7 Connector:

NET

NET

NET

A

B

Y

LOC=P111;

LOC=163;

LOC=P114;

#DIP1

#DIP2

#LED1

NOT Gate:

A Logic Circuit whose output is complement of its input.

Logic Diagram

Truth Table:

Input

A

0

1

Output

Y

1

0

VHDL Code for NOT Gate:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity notgate is

Port( A

:

in std_logic;

Y

:

out std_logic

);

end notgate;

architecture Behavioral of notgate is

begin

Y <= not A;

end Behavioral;

49

The University of Faisalabad

VLSI Systems Design

User Constraints File (UCF) of NOT Gate for CPLD XC95108PC84:

NET

NET

A

Y

LOC=P1;

LOC=P14;

#DIP1

#LED1

User Constraints File (UCF) of NOT Gate for SPARTAN 2 XC2S200PQ208:

NET

NET

A

Y

LOC=P195;

LOC=P111;

#DIP1

#LED1

User Constraints File (UCF) of NOT Gate for SPARTAN 2 XC2S30PQ208 to J5

Connector:

NET

NET

A

Y

LOC=P3;

LOC=P5;

#DIP1

#LED1

User Constraints File (UCF) of NOT Gate for SPARTAN 2 XC2S30PQ208 to J6

Connector:

NET

NET

A

Y

LOC=P57;

LOC=P59;

#DIP1

#LED1

User Constraints File (UCF) of NOT Gate for SPARTAN 2 XC2S30PQ208 to J7

Connector:

NET

NET

A

Y

LOC=P111;

LOC=P114;

#DIP1

#LED1

NAND Gate:

A Logic gate which gives logic 0 output if and only if all of its inputs are logic 1.

Logic Diagram

Truth Table:

Inputs

A

Output

Y

50

The University of Faisalabad

VLSI Systems Design

0

0

1

1

0

1

0

1

1

1

1

0

VHDL Code for NAND Gate:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity nandgate is

Port( A

:

in std_logic;

B

:

in std_logic;

Y

:

out std_logic

);

end nandgate;

architecture Behavioral of nandgate is

begin

Y <= A nand B;

end Behavioral;

User Constraints File (UCF) of NAND Gate for CPLD XC95108PC84:

NET

NET

NET

A

B

Y

LOC=P1;

LOC=P2;

LOC=P14;

#DIP1

#DIP2

#LED1

User Constraints File (UCF) of NAND Gate for SPARTAN 2 XC2S200PQ208:

NET

NET

NET

A

B

Y

LOC=P195;

LOC=P199;

LOC=P111;

#DIP1

#DIP2

#LED1

User Constraints File (UCF) of NAND Gate for SPARTAN 2 XC2S30PQ208 to J5

Connector:

NET

NET

NET

A

B

Y

LOC=P3;

LOC=P49;

LOC=P5;

#DIP1

#DIP2

#LED1

51

The University of Faisalabad

VLSI Systems Design

User Constraints File (UCF) of NAND Gate for SPARTAN 2 XC2S30PQ208 to J6

Connector:

NET

NET

NET

A

B

Y

LOC=P57;

LOC=P110;

LOC=P59;

#DIP1

#DIP2

#LED1

User Constraints File (UCF) of NAND Gate for SPARTAN 2 XC2S30PQ208 to J7

Connector:

NET

NET

NET

A

B

Y

LOC=P111;

LOC=163;

LOC=P114;

#DIP1

#DIP2

#LED1

NOR Gate:

A Logic gate whose output is logic 1 if and only if all of its inputs are logic 0.

Logic Diagram

Truth Table:

Inputs

A

0

0

1

1

B

0

1

0

1

Output

Y

1

0

0

0

VHDL Code for NOR Gate:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity norgate is

Port( A

:

in std_logic;

52

The University of Faisalabad

VLSI Systems Design

B

Y

:

:

in std_logic;

out std_logic

);

end norgate;

architecture Behavioral of norgate is

begin

Y <= A nor B;

end Behavioral;

User Constraints File (UCF) of NOR Gate for CPLD XC95108PC84:

NET

NET

NET

A

B

Y

LOC=P1;

LOC=P2;

LOC=P14;

#DIP1

#DIP2

#LED1

User Constraints File (UCF) of NOR Gate for SPARTAN 2 XC2S200PQ208:

NET

NET

NET

A

B

Y

LOC=P195;

LOC=P199;

LOC=P111;

#DIP1

#DIP2

#LED1

User Constraints File (UCF) of NOR Gate for SPARTAN 2 XC2S30PQ208 to J5

Connector:

NET

NET

NET

A

B

Y

LOC=P3;

LOC=P49;

LOC=P5;

#DIP1

#DIP2

#LED1

User Constraints File (UCF) of NOR Gate for SPARTAN 2 XC2S30PQ208 to J6

Connector:

NET

NET

NET

A

B

Y

LOC=P57;

LOC=P110;

LOC=P59;

#DIP1

#DIP2

#LED1

User Constraints File (UCF) of NOR Gate for SPARTAN 2 XC2S30PQ208 to J7

Connector:

NET

NET

NET

A

B

Y

LOC=P111;

LOC=163;

LOC=P114;

#DIP1

#DIP2

#LED1

53

The University of Faisalabad

VLSI Systems Design

Lab 12

Objective:

To Design a Multiplexer (4-to-1 and 8-to-1) in Verilog HDL Language using

CPLD

Development Platform or FPGA Circuit Board.

-----------------------------------------------------------------------------------------------------------Multiplexer:

The Multiplexer is a combinational circuit which accepts several data inputs and allows only one

of them at a Time to get through to the output.

4:1 Multiplexer:

Truth Table:

Selected Inputs

Sel<0> Sel<1>

0

0

0

1

1

0

1

1

I0

1

0

0

0

Mux Inputs

I1

I2

0

0

1

0

0

1

0

0

I3

0

0

0

1

Output

Mux out

I0

I1

I2

I3

Verilog HDL Code for 4:1 Multiplexer:

module Mux_4_1(sel,mux_in,mux_out);

input [1:0] sel;

input [3:0] mux_in;

output mux_out;

reg mux_out;

always@(sel or mux_in)

begin

case (sel)

2'b00 : mux_out <= mux_in[0];

2'b01 : mux_out <= mux_in[1];

2'b10 : mux_out <= mux_in[2];

2'b11 : mux_out <= mux_in[3];

endcase

end

54

The University of Faisalabad

VLSI Systems Design

endmodule

User Constraints File (UCF) of 4:1 Multiplexer for CPLD XC95108PC84:

NET

NET

NET

NET

NET

NET

NET

sel<1>

sel<0>

mux_in<0>

mux_in<1>

mux_in<2>

mux_in<3>

mux_out

LOC=P11;

LOC=P7;

LOC=P1;

LOC=P2;

LOC=P3;

LOC=P4;

LOC=P14;

#DIP5

#DIP6

#DIP1

#DIP2

#DIP3

#DIP4

#LED1

User Constraints File (UCF) of 4:1 Multiplexer for SPARTAN 2 XC2S200PQ208:

NET

NET

NET

NET

NET

NET

NET

sel<1>

sel<0>

mux_in<0>

mux_in<1>

mux_in<2>

mux_in<3>

mux_out

LOC=P98;

LOC=P100;

LOC=P195;

LOC=P199;

LOC=P201;

LOC=P202;

LOC=P111;

#DIP5

#DIP6

#DIP1

#DIP2

#DIP3

#DIP4

#LED1

User Constraints File (UCF) of 4:1 Multiplexer for SPARTAN 2 XC2S30PQ208 to J5

Connector:

NET

NET

NET

NET

NET

NET

NET

sel<1>

sel<0>

mux_in<0>

mux_in<1>

mux_in<2>

mux_in<3>

mux_out

LOC=P17;

LOC=P35;

LOC=P3;

LOC=P49;

LOC=P4;

LOC=P48;

LOC=P5;

#DIP5

#DIP6

#DIP1

#DIP2

#DIP3

#DIP4

#LED1

User Constraints File (UCF) of 4:1 Multiplexer for SPARTAN 2 XC2S30PQ208 to J6

Connector:

NET

NET

NET

sel<1>

sel<0>

mux_in<0>

LOC=P71;

LOC=P94;

LOC=P57;

#DIP5

#DIP6

#DIP1

55

The University of Faisalabad

VLSI Systems Design

NET

NET

NET

NET

mux_in<1>

mux_in<2>

mux_in<3>

mux_out

LOC=P110;

LOC=P58;

LOC=P109;

LOC=P59;

#DIP2

#DIP3

#DIP4

#LED1

User Constraints File (UCF) of 4:1 Multiplexer for SPARTAN 2 XC2S30PQ208 to J7

Connector:

NET

NET

NET

NET

NET

NET

NET

sel<1>

sel<0>

mux_in<0>

mux_in<1>

mux_in<2>

mux_in<3>

mux_out

LOC=P126;

LOC=P146;

LOC=P111;

LOC=P163;

LOC=P113;

LOC=P162;

LOC=P114;

#DIP5

#DIP6

#DIP1

#DIP2

#DIP3

#DIP4

#LED1

8:1 Multiplexer:

This Experiment only performs CPLD Development Platform (ST105) circuit board.

Truth Table:

Selected Inputs

Mux Inputs

Bin<4> Bin<2> Bin<1> DIP1 DIP2 DIP3 DIP4 DIP5 DIP6 DIP7 DIP8

Sel<2> Sel<1> Sel<0>

I0

I1

I2

I3

I4

I5

I6

I7

0

0

0

1

0

0

0

0

0

0

0

0

0

1

0

1

0

0

0

0

0

0

0

1

0

0

0

1

0

0

0

0

0

0

1

1

0

0

0

1

0

0

0

0

1

0

0

0

0

0

0

1

0

0

0

1

0

1

0

0

0

0

0

1

0

0

1

1

0

0

0

0

0

0

0

1

0

1

1

1

0

0

0

0

0

0

0

1

Output

LED 1

Mux_out

DIP1

DIP2

DIP3

DIP4

DIP5

DIP6

DIP7

DIP8

Verilog HDL Code for 4:1 Multiplexer:

module Mux_8_1(sel,mux_in,mux_out);

input [2:0] sel;

input [7:0] mux_in;

output mux_out;

56

The University of Faisalabad

VLSI Systems Design

reg mux_out;

always@(sel or mux_in)

begin

case (sel)

2'b000 : mux_out <= mux_in[0];

2'b001 : mux_out <= mux_in[1];

2'b010 : mux_out <= mux_in[2];

2'b011 : mux_out <= mux_in[3];

2'b100 : mux_out <= mux_in[4];

2'b101 : mux_out <= mux_in[5];

2'b110 : mux_out <= mux_in[6];

2'b111 : mux_out <= mux_in[7];

endcase

end

endmodule

User Constraints File (UCF) of 8:1 Multiplexer for CPLD XC95108PC84:

NET

NET

NET

NET

NET

NET

NET

NET

NET

NET

NET

NET

sel<2>

sel<1>

sel<0>

mux_in<0>

mux_in<1>

mux_in<2>

mux_in<3>

mux_in<4>

mux_in<5>

mux_in<6>

mux_in<7>

mux_out

LOC=P13;

LOC=P71;

LOC=P72;

LOC=P1;

LOC=P2;

LOC=P3;

LOC=P4;

LOC=P11;

LOC=P7;

LOC=P6;

LOC=P5;

LOC=P14;

#DIP9

#DIP10

#DIP11

#DIP1

#DIP2

#DIP3

#DIP4

#DIP5

#DIP6

#DIP7

#DIP8

#LED1

57

The University of Faisalabad

VLSI Systems Design

Lab 13

Objective:

To Design a Half Adder and Full Adder in VHDL Language using CPLD Development

Platform or FPGA Circuit Board.

-----------------------------------------------------------------------------------------------------------Half Adder:

A Logic circuit for the addition of two one bit numbers is called Half Adder. It has two

inputs (A and B) and two outputs (SUM and CARRY).

Logic Diagram:

Truth Table:

Inputs

A

0

0

1

1

B

0

1

0

1

Outputs

SUM CARRY

0

0

1

0

1

0

0

1

VHDL Code for Half Adder:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity hadd1 is

Port (

a

:

b

:

s

:

in std_logic;

in std_logic;

out std_logic;

58

The University of Faisalabad

VLSI Systems Design

c

:

out std_logic

);

end hadd1;

architecture Behavioral of hadd1 is

begin

process(a,b)

begin

if(a='0') then

s <= b;

c <= '0';

else

s <= not b;

c <= b;

end if;

end process;

end Behavioral;

User Constraints File (UCF) of Half Adder for CPLD XC95108PC84:

NET

NET

NET

NET

a

b

s

c

LOC=P1;

LOC=P2;

LOC=P14;

LOC=P15;

#DIP 1

#DIP 2

#LED 1

#LED 2

User Constraints File (UCF) of Half Adder for SPARTAN 2 XC2S200PQ208:

NET

NET

NET

NET

a

b

s

c

LOC=P195;

LOC=P199;

LOC=P111;

LOC=P114;

#DIP 1

#DIP 2

#LED 1

#LED 2

User Constraints File (UCF) of Half Adder for SPARTAN 2 XC2S30PQ208 to J5

Connector:

NET

NET

NET

NET

a

b

s

c

LOC=P3;

LOC=P49;

LOC=P5;

LOC=P47;

#DIP 1

#DIP 2

#LED 1

#LED 2

59

The University of Faisalabad

VLSI Systems Design

User Constraints File (UCF) of Half Adder for SPARTAN 2 XC2S30PQ208 to J6

Connector:

NET

NET

NET

NET

a

b

s

c

LOC=P57;

LOC=P110;

LOC=P59;

LOC=P108;

#DIP 1

#DIP 2

#LED 1

#LED 2

User Constraints File (UCF) of Half Adder for SPARTAN 2 XC2S30PQ208 to J7

Connector:

NET

NET

NET

NET

a

b

s

c

LOC=P111;

LOC=P163;

LOC=P114;

LOC=P161;

#DIP 1

#DIP 2

#LED 1

#LED 2

Full Adder:

A Logic circuit that accepts two one bit signal and carry_in as inputs and produces their

SUM and CARRY as output is called Full Adder. It has three inputs (A, B and Cin) and

two outputs (SUM and CARRY).

Logic Diagram:

Truth Table:

A

0

0

0

0

Inputs

B

0

0

1

1

Cin

0

1

0

1

Outputs

SUM CARRY

0

0

1

0

1

0

0

1

60

The University of Faisalabad

VLSI Systems Design

1

1

1

1

0

0

1

1

0

1

0

1

1

0

0

1

0

1

1

1

VHDL Code for Full Adder:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity full_adder is

Port (

a

b

c

s

cout

:

:

:

:

:

in std_logic;

in std_logic;

in std_logic;

out std_logic;

out std_logic);

end full_adder;

architecture Behavioral of full_adder is

begin

process(a,b,c)

begin

if((a='0' and b='0') or (a='1' and b='1')) then

s <= c;

cout <= b;

end if;

if ((a='0' and b='1') or (a='1' and b='0')) then

s <= not c;

cout <= c;

end if;

end process;

end Behavioral;

61

The University of Faisalabad

VLSI Systems Design

User Constraints File (UCF) of Full Adder for CPLD XC95108PC84:

NET

NET

NET

NET

NET

a

b

c

s

cout

LOC=P1;

LOC=P2;

LOC=P3;

LOC=P14;

LOC=P15;

#DIP 1

#DIP 2

#DIP 3

#LED 1

#LED 2

User Constraints File (UCF) of Full Adder for SPARTAN 2 XC2S200PQ208:

NET

NET

NET

NET

NET

a

b

c

s

cout

LOC=P195;

LOC=P199;

LOC=P201;

LOC=P111;

LOC=P114;

#DIP 1

#DIP 2

#DIP 3

#LED 1

#LED 2

User Constraints File (UCF) of Full Adder for SPARTAN 2 XC2S30PQ208 to J5

Connector:

NET

NET

NET

NET

NET

a

b

c

s

cout

LOC=P3;

LOC=P49;

LOC=P4;

LOC=P5;

LOC=P47;

#DIP 1

#DIP 2

#DIP 3

#LED 1

#LED 2

User Constraints File (UCF) of Full Adder for SPARTAN 2 XC2S30PQ208 to J6

Connector:

NET

NET

NET

NET

NET

a

b

c

s

cout

LOC=P57;

LOC=P110;

LOC=P58;

LOC=P59;

LOC=P108;

#DIP 1

#DIP 2

#DIP 3

#LED 1

#LED 2

User Constraints File (UCF) of Full Adder for SPARTAN 2 XC2S30PQ208 to J7

Connector:

NET

NET

NET

NET

NET

a

b

c

s

cout

LOC=P111;

LOC=P163;

LOC=P113;

LOC=P114;

LOC=P161;

#DIP 1

#DIP 2

#DIP 3

#LED 1

#LED 2

62

The University of Faisalabad

VLSI Systems Design

Lab 14

Objective:

To design a 4Bit BCD to Seven Segment Decoder using VHDL Language on FPGA

circuit board or CPLD development platform and Output showed on Seven Segment

Display.

-----------------------------------------------------------------------------------------------------------BCD to Seven Segment Decoder:

Decoder is a device which converts one digital format into another and the most

commonly used device for doing this is the Binary Coded Decimal (BCD) to 7-Segment Display

Decoder. 7-segment LED (Light Emitting Diode) or LCD (Liquid Crystal) displays, provide a

very convenient way of displaying information or digital data in the form of numbers, letters or

even alpha-numerical characters and they consist of 7 individual LED's (the segments), within

one single display package.

There are two important types of 7-segment LED digital display.

The Common Cathode Display (CCD) - In the common cathode display, all the cathode

connections of the LED's are joined together to logic "0" and the individual segments are

illuminated by application of a "HIGH", logic "1" signal to the individual Anode

terminals.

The Common Anode Display (CAD) - In the common anode display, all the anode

connections of the LED's are joined together to logic "1" and the individual segments are

illuminated by connecting the individual Cathode terminals to a "LOW", logic "0" signal.

7-Segment Display Format:

Logic Diagram:

63

The University of Faisalabad

VLSI Systems Design

Truth Table:

BCD Inputs

Q<3> Q<2> Q<1> Q<0>

0

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

0

1

0

0

0

1

0

1

0

1

1

0

0

1

1

1

1

0

0

0

1

0

0

1

1

0

1

0

1

0

1

1

1

1

0

0

1

1

0

1

1

1

1

0

1

1

1

1

a

1

0

1

1

0

1

0

1

1

1

1

0

1

0

1

1

B

1

1

1

1

1

0

0

1

1

1

1

0

0

1

0

0

Segments Outputs

c

d

e

1

1

1

1

0

0

0

1

1

1

1

0

1

0

0

1

1

0

1

1

1

1

0

0

1

1

1

1

0

0

1

0

1

1

1

1

0

1

1

1

1

1

0

1

1

0

0

1

f

1

0

0

0

1

1

1

0

1

1

1

1

1

0

1

1

g

0

0

1

1

1

1

1

0

1

1

1

1

0

1

1

1

Display

0

1

2

3

4

5

6

7

8

9

A

b

C

d

E

F

VHDL Code for BCD to Seven Segment Display:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity bcd is

Port (

q

a

);

end bcd;

:

:

in std_logic_vector(3 downto 0);

out std_logic_vector(7 downto 0)

architecture Behavioral of bcd is

begin

process (q)

begin

case q is

when "0000" =>

a

<=

"10111111";

64

The University of Faisalabad

VLSI Systems Design

when "0001" =>

when "0010" =>

when "0011" =>

when "0100" =>

when "0101" =>

when "0110" =>

when "0111" =>

when "1000" =>

when "1001" =>

when "1010" =>

when "1011" =>

when "1100" =>

when "1101" =>

when "1110" =>

when "1111" =>

when others =>

end case;

end process;

end Behavioral;

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

<=

<=

<=

<=

<=

<=

<=

<=

<=

<=

<=

<=

<=

<=

<=

<=

"10000110";

"11011011";

"11001111";

"11100110";

"11101101";

"11111101";

"10000111";

"11111111";

"11101111";

"11110111";

"11111100";

"10111001";

"11011110";

"11111001";

"11110001";

"ZZZZZZZZ";

User Constraints File (UCF) of BCD to Seven Segment Display Decoder for CPLD

XC95108PC84:

NET

q<3>

LOC=P1;

#DIP 1

NET

q<2>

LOC=P2;

#DIP 2

NET

q<1>

LOC=P3;

#DIP 3

NET

q<0>

LOC=P4;

#DIP 4

NET

a<0>

LOC=P70;

#Displaying A

NET

a<1>

LOC=P32;

#Displaying B

NET

a<2>

LOC=P33;

#Displaying C

NET

a<3>

LOC=P34;

#Displaying D

NET

a<4>

LOC=P35;

#Displaying E

NET

a<5>

LOC=P36;

#Displaying F

NET

a<6>

LOC=P37;

#Displaying G

NET

a<7>

LOC=P63;

#Cathode for seven segment

display

65

The University of Faisalabad

VLSI Systems Design

User Constraints File (UCF) of BCD to Seven Segment Display Decoder for SPARTAN 2

XC2S200PQ208:

NET

q<3>

LOC=P195;

#DIP 1

NET

q<2>

LOC=P199;

#DIP 2

NET

q<1>

LOC=P201;

#DIP 3

NET

q<0>

LOC=P202;

#DIP 4

NET

a<0>

LOC=P45;

#Displaying A

NET

a<1>

LOC=P47;

#Displaying B

NET

a<2>

LOC=P49;

#Displaying C

NET

a<3>

LOC=P57;

#Displaying D

NET

a<4>

LOC=P59;

#Displaying E

NET

a<5>

LOC=P62;

#Displaying F

NET

a<6>

LOC=P73;

#Displaying G

NET

a<7>

LOC=P4;

#Cathode for seven segment

display

User Constraints File (UCF) of BCD to Seven Segment Display Decoder for SPARTAN 2

XC2S30PQ208 to J5 Connector:

NET

q<3>

LOC=P3;

#DIP 1

NET

q<2>

LOC=P49;

#DIP 2

NET

q<1>

LOC=P4;

#DIP 3

NET

q<0>

LOC=P48;

#DIP 4

NET

a<0>

LOC=P42;

#Displaying A

NET

a<1>

LOC=P36;

#Displaying B

NET

a<2>

LOC=P37;

#Displaying C

NET

a<3>

LOC=P15;

#Displaying D

NET

a<4>

LOC=P16;

#Displaying E

NET

a<5>

LOC=P14;

#Displaying F

NET

a<6>

LOC=P41;

#Displaying G

NET

a<7>

LOC=P8;

#Cathode for seven segment

display

66

The University of Faisalabad

VLSI Systems Design

User Constraints File (UCF) of BCD to Seven Segment Display Decoder for SPARTAN 2

XC2S30PQ208 to J6 Connector:

NET

q<3>

LOC=P57;

#DIP 1

NET

q<2>

LOC=P110;

#DIP 2

NET

q<1>

LOC=P58;

#DIP 3

NET

q<0>

LOC=P109;

#DIP 4

NET

a<0>

LOC=P99;

#Displaying A

NET

a<1>

LOC=P95;

#Displaying B

NET

a<2>

LOC=P96;

#Displaying C

NET

a<3>

LOC=P69;

#Displaying D

NET

a<4>

LOC=P70;

#Displaying E

NET

a<5>

LOC=P68;

#Displaying F

NET

a<6>

LOC=P98;

#Displaying G

NET

a<7>

LOC=P62;

#Cathode for seven segment

display

User Constraints File (UCF) of BCD to Seven Segment Display Decoder for SPARTAN 2

XC2S30PQ208 to J7 Connector:

NET

q<3>

LOC=P111;

#DIP 1

NET

q<2>

LOC=P163;

#DIP 2

NET

q<1>

LOC=P113;

#DIP 3

NET

q<0>

LOC=P162;

#DIP 4

NET

a<0>

LOC=P151;

#Displaying A

NET

a<1>

LOC=P147;

#Displaying B

NET

a<2>

LOC=P148;

#Displaying C

NET

a<3>

LOC=P123;

#Displaying D

NET

a<4>

LOC=P125;

#Displaying E

NET

a<5>

LOC=P122;

#Displaying F

NET

a<6>

LOC=P150;

#Displaying G

NET

a<7>

LOC=P119;

#Cathode for seven segment

display

67

The University of Faisalabad

VLSI Systems Design

Lab 15

Objective:

To design an Octal to Binary number system using VHDL Language on FPGA circuit

board or CPLD development platform and Output of the number system to be displayed

on Seven Segment Display and LEDs.

-----------------------------------------------------------------------------------------------------------Octal to Binary Encoder:

The Octal to Binary Encoder consists of Eight Inputs. One for each of the eight digits, and

three outputs that generates the corresponding binary numbers. It is constructed with OR gates

whose inputs can be determined from the truth table.

Logic Diagram:

68

The University of Faisalabad

VLSI Systems Design

Truth Table:

DIP 8

0

0

0

0

0

0

0

1

DIP 7

0

0

0

0

0

0

1

0

DIP 6

0

0

0

0

0

1

0

0

Octal Inputs

DIP 5 DIP 4

0

0

0

0

0

0

0

1

1

0

0

0

0

0

0

0

DIP 3

0

0

1

0

0

0

0

0

DIP 2

0

1

0

0

0

0

0

0

DIP 1

1

0

0

0

0

0

0

0

Binary Outputs

LED 3 LED 2 LED 1

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

Display

0

1

2

3

4

5

6

7

VHDL Code for Octal to Binary Number System:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity octal_to_binary is

Port (

q

:

in std_logic_vector(7 downto 0);

a

:

out std_logic_vector(7 downto 0);

b

:

out std_logic_vector(2 downto 0)

);

end octal_to_binary;

architecture Behavioral of octal_to_binary is

begin

process(q)

begin

case q is

when "00000001" => a <="10111111";

when "00000010" => a <="10000110";

when "00000100" => a <="11011011";

when "00001000" => a <="11001111";

when "00010000" => a <="11100110";

when "00100000" => a <="11101101";

when "01000000" => a <="11111101";

when "10000000" => a <="10000111";

when others

=> a <="11000000";

end case;

69

The University of Faisalabad

VLSI Systems Design

case q is

when "00000001" => b <="000";

when "00000010" => b <="001";

when "00000100" => b <="010";

when "00001000" => b <="011";

when "00010000" => b <="100";

when "00100000" => b <="101";

when "01000000" => b <="110";

when "10000000" => b <="111";

when others

=> b <="000";

end case;

end process;

end Behavioral;

User Constraints File (UCF) of Octal to Binary Number System for CPLD XC95108PC84:

NET

q<7>

LOC=P1;

#DIP 1

NET

q<6>

LOC=P2;

#DIP 2

NET

q<5>

LOC=P3;

#DIP 3

NET

q<4>

LOC=P4;

#DIP 4

NET

q<3>

LOC=P11;

#DIP 5

NET

q<2>

LOC=P7;

#DIP 6

NET

q<1>

LOC=P6;

#DIP 7

NET

q<0>

LOC=P5;

#DIP 8

NET

a<7>

LOC=P63;

#Cathode for 7 Segment A

NET

a<6>

LOC=P37;

#Displaying G

NET

a<5>

LOC=P36;

#Displaying F

NET

a<4>

LOC=P35;

#Displaying E

NET

a<3>

LOC=P34;

#Displaying D

NET

a<2>

LOC=P33;

#Displaying C

NET

a<1>

LOC=P32;

#Displaying B

NET

a<0>

LOC=P70;

#Displaying A

NET

b<0>

LOC=P14;

#LED 1

NET

b<1>

LOC=P15;

#LED 2

NET

b<2>

LOC=P17;

#LED 3

70

The University of Faisalabad

VLSI Systems Design

User Constraints File (UCF) of Octal to Binary Number System for SPARTAN 2

XC2S200PQ208:

NET

q<7>

LOC=P195;

#DIP 1

NET

q<6>

LOC=P199;

#DIP 2

NET

q<5>

LOC=P201;

#DIP 3

NET

q<4>

LOC=P202;

#DIP 4

NET

q<3>

LOC=P98;

#DIP 5

NET

q<2>

LOC=P100;

#DIP 6

NET

q<1>

LOC=P108;

#DIP 7

NET

q<0>

LOC=P109;

#DIP 8

NET

a<7>

LOC=P4;

#Cathode for 7 Segment A

NET

a<6>

LOC=P73;

#Displaying G

NET

a<5>

LOC=P62;

#Displaying F

NET

a<4>

LOC=P59;

#Displaying E

NET

a<3>

LOC=P57;

#Displaying D

NET

a<2>

LOC=P49;

#Displaying C

NET

a<1>

LOC=P47;

#Displaying B

NET

a<0>

LOC=P45;

#Displaying A

NET

b<0>

LOC=P111;

#LED 1

NET

b<1>

LOC=P114;

#LED 2

NET

b<2>

LOC=P115;

#LED 3

User Constraints File (UCF) of BCD Octal to Binary Number System for SPARTAN 2

XC2S30PQ208 to J5 Connector:

NET

q<7>

LOC=P3;

#DIP 1

NET

q<6>

LOC=P49;

#DIP 2

NET

q<5>

LOC=P4;

#DIP 3

NET

q<4>

LOC=P48;

#DIP 4

NET

q<3>

LOC=P17;

#DIP 5

NET

q<2>

LOC=P35;

#DIP 6

71

The University of Faisalabad

VLSI Systems Design

NET

q<1>

LOC=P18;

#DIP 7

NET

q<0>

LOC=P34;

#DIP 8

NET

a<7>

LOC=P8;

#Cathode for 7 Segment A

NET

a<6>

LOC=P41;

#Displaying G

NET

a<5>

LOC=P14;

#Displaying F

NET

a<4>

LOC=P16;

#Displaying E

NET

a<3>

LOC=P15;

#Displaying D

NET

a<2>

LOC=P37;

#Displaying C

NET

a<1>

LOC=P36;

#Displaying B

NET

a<0>

LOC=P42;

#Displaying A

NET

b<0>

LOC=P5;

#LED 1

NET

b<1>

LOC=P47;

#LED 2

NET

b<2>

LOC=P6;

#LED 3

User Constraints File (UCF) of Octal to Binary Number System for SPARTAN 2

XC2S30PQ208 to J6 Connector:

NET

q<7>

LOC=P57;

#DIP 1

NET

q<6>

LOC=P110;

#DIP 2

NET

q<5>

LOC=P58;

#DIP 3

NET

q<4>

LOC=P109;

#DIP 4

NET

q<3>

LOC=P71;

#DIP 5

NET

q<2>

LOC=P94;

#DIP 6

NET

q<1>

LOC=P73;

#DIP 7

NET

q<0>

LOC=P90;

#DIP 8

NET

a<7>

LOC=P62;

#Cathode for 7 Segment A

NET

a<6>

LOC=P98;

#Displaying G

NET

a<5>

LOC=P68;

#Displaying F

NET

a<4>

LOC=P70;

#Displaying E

NET

a<3>

LOC=P69;

#Displaying D

NET

a<2>

LOC=P96;

#Displaying C

72

The University of Faisalabad

VLSI Systems Design

NET

a<1>

LOC=P95;

#Displaying B

NET

a<0>

LOC=P99;

#Displaying A

NET

b<0>

LOC=P59;

#LED 1

NET

b<1>

LOC=P108;

#LED 2

NET

b<2>

LOC=P61;

#LED 3

User Constraints File (UCF) of Octal to Binary Number System for SPARTAN 2

XC2S30PQ208 to J7 Connector:

NET

q<7>

LOC=P111;

#DIP 1

NET

q<6>

LOC=P163;

#DIP 2

NET

q<5>

LOC=P113;

#DIP 3

NET

q<4>

LOC=P162;

#DIP 4

NET

q<3>

LOC=P126;

#DIP 5

NET

q<2>

LOC=P146;

#DIP 6

NET

q<1>

LOC=P127;

#DIP 7

NET

q<0>

LOC=P142;

#DIP 8

NET

a<7>

LOC=P119;

#Cathode for 7 Segment A

NET

a<6>

LOC=P150;

#Displaying G

NET

a<5>

LOC=P122;

#Displaying F

NET

a<4>

LOC=P125;

#Displaying E

NET

a<3>

LOC=P123;

#Displaying D

NET

a<2>

LOC=P148;

#Displaying C

NET

a<1>

LOC=P147;

#Displaying B

NET

a<0>

LOC=P151;

#Displaying A

NET

b<0>

LOC=P114;

#LED 1

NET

b<1>

LOC=P161;

#LED 2

NET

b<2>

LOC=P115;

#LED 3

73

VLSI Systems Design

The University of Faisalabad

74

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)