Professional Documents

Culture Documents

74LVC1G386: 1. General Description

Uploaded by

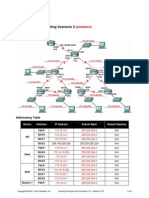

Êder ContrerasOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

74LVC1G386: 1. General Description

Uploaded by

Êder ContrerasCopyright:

Available Formats

74LVC1G386

3-input EXCLUSIVE-OR gate

Rev. 02 3 September 2007

Product data sheet

1. General description

The 74LVC1G386 provides a 3-input EXCLUSIVE-OR function.

The input can be driven from either 3.3 or 5 V devices. This feature allows the use of

these devices in a mixed 3.3 and 5 V environment.

Schmitt-trigger action at all inputs makes the circuit tolerant of slower input rise and fall

time.

This device is fully specified for partial power-down applications using IOFF. The IOFF

circuitry disables the output, preventing the damaging backflow current through the device

when it is powered down.

2. Features

Wide supply voltage range from 1.65 to 5.5 V

High noise immunity

Complies with JEDEC standard:

JESD8-7 (1.65 V to 1.95 V)

JESD8-5 (2.3 V to 2.7 V)

JESD8B/JESD36 (2.7 V to 3.6 V)

24 mA output drive (VCC = 3.0 V)

Latch-up performance exceeds 250 mA

CMOS low power consumption

Direct interface with TTL levels

Inputs accept voltages up to 5 V

ESD protection:

HBM EIA/JESD22-A114E exceeds 2000 V

MM EIA/JESD22-A115-A exceeds 200 V.

SOT363 and SOT457 package

Specified from 40 to +85 C and 40 to +125 C.

3. Ordering information

Table 1.

Ordering information

Type number

Package

Temperature range Name

Description

Version

74LVC1G386GW

40 C to +125 C

SC-88

plastic surface-mounted package; 6 leads

SOT363

74LVC1G386GV

40 C to +125 C

SC-74A

plastic surface-mounted package (TSOP6); 6 leads

SOT457

74LVC1G386

NXP Semiconductors

3-input EXCLUSIVE-OR gate

4. Marking

Table 2.

Marking

Type number

Marking code

74LVC1G386GW

YH

74LVC1G386GV

YH

5. Functional diagram

1

3

6

A

Y

1

3

6

=1

mnb143

mnb145

Fig 1. Logic symbol

Fig 2. IEC logic symbol

B

Y

mnb144

Fig 3. Logic diagram

6. Pinning information

6.1 Pinning

74LVC1G386

A

GND

VCC

001aag920

Fig 4. Pin configuration

74LVC1G386_2

Product data sheet

NXP B.V. 2007. All rights reserved.

Rev. 02 3 September 2007

2 of 12

74LVC1G386

NXP Semiconductors

3-input EXCLUSIVE-OR gate

6.2 Pin description

Table 3.

Pin description

Symbol

Pin

Description

data input

GND

ground (0 V)

data input

data output

VCC

supply voltage

data input

7. Functional description

Table 4.

Function table[1]

Input

Output

[1]

H = HIGH voltage level; L = LOW voltage level

8. Limiting values

Table 5.

Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).

Symbol

Parameter

VCC

supply voltage

IIK

input clamping current

VI

input voltage

IOK

output clamping current

output voltage

VO

IO

output current

ICC

supply current

IGND

ground current

Ptot

total power dissipation

Tstg

storage temperature

[1]

Conditions

Min

Max

Unit

0.5

+6.5

50

mA

0.5

+6.5

50

mA

Active mode

[1][2]

0.5

VCC + 0.5

Power-down mode

[1][2]

0.5

+6.5

50

mA

100

mA

100

mA

250

mW

65

+150

VI < 0 V

[1]

VO > VCC or VO < 0 V

VO = 0 V to VCC

Tamb = 40 C to +125 C

[3]

The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

74LVC1G386_2

Product data sheet

NXP B.V. 2007. All rights reserved.

Rev. 02 3 September 2007

3 of 12

74LVC1G386

NXP Semiconductors

3-input EXCLUSIVE-OR gate

[2]

When VCC = 0 V (Power-down mode), the output voltage can be 5.5 V in normal operation.

[3]

For SC-74 and SC-88 packages: above 87.5 C the value of Ptot derates linearly with 4.0 mW/K.

9. Recommended operating conditions

Table 6.

Recommended operating conditions

Symbol

Parameter

VCC

supply voltage

VI

input voltage

VO

output voltage

Conditions

Tamb

ambient temperature

t/V

input transition rise and fall rate

Min

Typ

Max

Unit

1.65

5.5

5.5

Active mode

VCC

VO

VCC = 0 V; Power-down mode

5.5

VO

40

+125

VCC = 1.65 V to 2.7 V

20

ns/V

VCC = 2.7 V to 5.5 V

10

ns/V

10. Static characteristics

Table 7.

Static characteristics

At recommended operating conditions. Voltages are referenced to GND (ground = 0 V).

Symbol Parameter

Conditions

Min

Typ[1] Max

Unit

Tamb = 40 C to +85 C

VIH

VIL

VOH

VOL

II

HIGH-level input voltage

LOW-level input voltage

HIGH-level output voltage

LOW-level output voltage

input leakage current

VCC = 1.65 V to 1.95 V

0.65 VCC

VCC = 2.3 V to 2.7 V

1.7

VCC = 2.7 V to 3.6 V

2.0

VCC = 4.5 V to 5.5 V

0.7 VCC

VCC = 1.65 V to 1.95 V

0.35 VCC

VCC = 2.3 V to 2.7 V

0.7

VCC = 2.7 V to 3.6 V

0.8

VCC = 4.5 V to 5.5 V

0.3 VCC

IO = 100 A; VCC = 1.65 V to 5.5 V

VCC 0.1

IO = 4 mA; VCC = 1.65 V

1.2

IO = 8 mA; VCC = 2.3 V

1.9

VI = VIH or VIL

IO = 12 mA; VCC = 2.7 V

2.2

IO = 24 mA; VCC = 3.0 V

2.3

IO = 32 mA; VCC = 4.5 V

3.8

VI = VIH or VIL

IO = 100 A; VCC = 1.65 V to 5.5 V

0.1

IO = 4 mA; VCC = 1.65 V

0.45

IO = 8 mA; VCC = 2.3 V

0.3

IO = 12 mA; VCC = 2.7 V

0.4

IO = 24 mA; VCC = 3.0 V

0.55

IO = 32 mA; VCC = 4.5 V

0.55

0.1

VCC = 0 V to 5.5 V; VI = 5.5 V or GND

74LVC1G386_2

Product data sheet

NXP B.V. 2007. All rights reserved.

Rev. 02 3 September 2007

4 of 12

74LVC1G386

NXP Semiconductors

3-input EXCLUSIVE-OR gate

Table 7.

Static characteristics continued

At recommended operating conditions. Voltages are referenced to GND (ground = 0 V).

Symbol Parameter

Conditions

Min

Typ[1] Max

Unit

IOFF

power-off leakage current

VCC = 0 V; VI or VO = 5.5 V

0.1

10

ICC

supply current

VI = 5.5 V or GND;

VCC = 1.65 V to 5.5 V; IO = 0 A

0.1

10

ICC

additional supply current

per pin; VCC = 2.3 V to 5.5 V;

VI = VCC 0.6 V; IO = 0 A

500

CI

input capacitance

VCC = 3.3 V; VI = GND to VCC

pF

VCC = 1.65 V to 1.95 V

0.65 VCC

VCC = 2.3 V to 2.7 V

1.7

VCC = 2.7 V to 3.6 V

2.0

VCC = 4.5 V to 5.5 V

0.7 VCC

VCC = 1.65 V to 1.95 V

0.35 VCC

VCC = 2.3 V to 2.7 V

0.7

VCC = 2.7 V to 3.6 V

0.8

VCC = 4.5 V to 5.5 V

0.3 VCC

IO = 100 A; VCC = 1.65 V to 5.5 V

VCC 0.1

IO = 4 mA; VCC = 1.65 V

0.95

IO = 8 mA; VCC = 2.3 V

1.7

IO = 12 mA; VCC = 2.7 V

1.9

IO = 24 mA; VCC = 3.0 V

2.0

IO = 32 mA; VCC = 4.5 V

3.4

IO = 100 A; VCC = 1.65 V to 5.5 V

0.1

IO = 4 mA; VCC = 1.65 V

0.70

IO = 8 mA; VCC = 2.3 V

0.45

Tamb = 40 C to +125 C

HIGH-level input voltage

VIH

LOW-level input voltage

VIL

VOH

HIGH-level output voltage

LOW-level output voltage

VOL

VI = VIH or VIL

VI = VIH or VIL

IO = 12 mA; VCC = 2.7 V

0.60

IO = 24 mA; VCC = 3.0 V

0.80

IO = 32 mA; VCC = 4.5 V

0.80

100

II

input leakage current

VCC = 0 V to 5.5 V; VI = 5.5 V or GND

IOFF

power-off leakage current

VCC = 0 V; VI or VO = 5.5 V

200

ICC

supply current

VI = 5.5 V or GND;

VCC = 1.65 V to 5.5 V; IO = 0 A

200

ICC

additional supply current

per pin; VCC = 2.3 V to 5.5 V;

VI = VCC 0.6 V; IO = 0 A

5000

[1]

All typical values are measured at VCC = 3.3 V and Tamb = 25 C.

74LVC1G386_2

Product data sheet

NXP B.V. 2007. All rights reserved.

Rev. 02 3 September 2007

5 of 12

74LVC1G386

NXP Semiconductors

3-input EXCLUSIVE-OR gate

11. Dynamic characteristics

Table 8.

Dynamic characteristics

Voltages are referenced to GND (ground = 0 V). For test circuit see Figure 6.

Symbol Parameter

40 C to +85 C

Conditions

power dissipation

capacitance

CPD

Unit

Min

Max

Min

Max

VCC = 1.65 V to 1.95 V

2.0

8.0

17.0

2.0

22.0

ns

VCC = 2.3 V to 2.7 V

1.5

5.0

9.0

1.5

11.5

ns

VCC = 2.7 V

1.5

5.0

8.5

1.5

11.0

ns

VCC = 3.0 V to 3.6 V

1.0

4.5

7.5

1.0

9.5

ns

VCC = 4.5 V to 5.5 V

1.0

3.5

5.5

1.0

7.0

ns

13

pF

[2]

propagation delay A, B, C to Y; see Figure 5

tpd

40 C to +125 C

Typ[1]

VI = GND to VCC; VCC = 3.3 V

[3]

[1]

Typical values are measured at Tamb = 25 C and VCC = 1.8 V, 2.5 V, 2.7 V, 3.3 V and 5.0 V respectively.

[2]

tpd is the same as tPLH and tPHL.

[3]

CPD is used to determine the dynamic power dissipation (PD in W).

PD = CPD VCC2 fi N + (CL VCC2 fo) where:

fi = input frequency in MHz;

fo = output frequency in MHz;

CL = output load capacitance in pF;

VCC = supply voltage in V;

N = number of inputs switching;

(CL VCC2 fo) = sum of outputs.

12. AC waveforms

VI

A, B, C

input

VM

GND

t PHL

t PLH

VOH

Y output

in phase

VM

VOL

t PLH

tPHL

VOH

Y output

out of phase

VM

VOL

mnb147

Measurement points are given in Table 9.

VOL and VOH are typical output voltage levels that occur with the output load.

Fig 5. Input A, B, C to output Y propagation delays

74LVC1G386_2

Product data sheet

NXP B.V. 2007. All rights reserved.

Rev. 02 3 September 2007

6 of 12

74LVC1G386

NXP Semiconductors

3-input EXCLUSIVE-OR gate

Table 9.

Measurement points

VCC

VM

Input

VI

tr = tf

1.65 V to 1.95 V

0.5 VCC

VCC

2.0 ns

2.3 V to 2.7 V

0.5 VCC

VCC

2.0 ns

2.7 V

1.5 V

2.7 V

2.5 ns

3.0 V to 3.6 V

1.5 V

2.7 V

2.5 ns

4.5 V to 5.5 V

0.5 VCC

VCC

2.5 ns

VEXT

VCC

VI

RL

VO

DUT

RT

CL

RL

mna616

Test data is given in Table 10.

Definitions for test circuit:

RL = Load resistance.

CL = Load capacitance including jig and probe capacitance.

RT = Termination resistance should be equal to the output impedance Zo of the pulse generator.

VEXT = External voltage for measuring switching times.

Fig 6. Load circuitry for switching times

Table 10.

Test data

Supply voltage

Input

Load

VEXT

VCC

VI

CL

RL

tPLH, tPHL

1.65 V to 1.95 V

VCC

30 pF

1 k

open

2.3 V to 2.7 V

VCC

30 pF

500

open

2.7 V

2.7 V

50 pF

500

open

3.0 V to 3.6 V

2.7 V

50 pF

500

open

4.5 V to 5.5 V

VCC

50 pF

500

open

74LVC1G386_2

Product data sheet

NXP B.V. 2007. All rights reserved.

Rev. 02 3 September 2007

7 of 12

74LVC1G386

NXP Semiconductors

3-input EXCLUSIVE-OR gate

13. Package outline

Plastic surface-mounted package; 6 leads

SOT363

HE

v M A

pin 1

index

A1

2

e1

bp

c

Lp

w M B

detail X

2 mm

scale

DIMENSIONS (mm are the original dimensions)

UNIT

A1

max

bp

e1

HE

Lp

mm

1.1

0.8

0.1

0.30

0.20

0.25

0.10

2.2

1.8

1.35

1.15

1.3

0.65

2.2

2.0

0.45

0.15

0.25

0.15

0.2

0.2

0.1

OUTLINE

VERSION

REFERENCES

IEC

SOT363

JEDEC

JEITA

SC-88

EUROPEAN

PROJECTION

ISSUE DATE

04-11-08

06-03-16

Fig 7. Package outline SOT363 (SC-88)

74LVC1G386_2

Product data sheet

NXP B.V. 2007. All rights reserved.

Rev. 02 3 September 2007

8 of 12

74LVC1G386

NXP Semiconductors

3-input EXCLUSIVE-OR gate

Plastic surface-mounted package (TSOP6); 6 leads

SOT457

HE

v M A

pin 1

index

A

A1

c

3

Lp

bp

w M B

detail X

2 mm

scale

DIMENSIONS (mm are the original dimensions)

UNIT

A1

bp

HE

Lp

mm

1.1

0.9

0.1

0.013

0.40

0.25

0.26

0.10

3.1

2.7

1.7

1.3

0.95

3.0

2.5

0.6

0.2

0.33

0.23

0.2

0.2

0.1

OUTLINE

VERSION

REFERENCES

IEC

SOT457

JEDEC

JEITA

SC-74

EUROPEAN

PROJECTION

ISSUE DATE

05-11-07

06-03-16

Fig 8. Package outline SOT457 (SC-74)

74LVC1G386_2

Product data sheet

NXP B.V. 2007. All rights reserved.

Rev. 02 3 September 2007

9 of 12

74LVC1G386

NXP Semiconductors

3-input EXCLUSIVE-OR gate

14. Abbreviations

Table 11.

Abbreviations

Acronym

Description

CMOS

Complementary Metal Oxide Semiconductor

DUT

Device Under Test

ESD

ElectroStatic Discharge

HBM

Human Body Model

MM

Machine Model

TTL

Transistor-Transistor Logic

15. Revision history

Table 12.

Revision history

Document ID

Release date

Data sheet status

Change notice

Supersedes

74LVC1G386_2

20070903

Product data sheet

74LVC1G386_1

Modifications:

74LVC1G386_1

The format of this data sheet has been redesigned to comply with the new identity guidelines

of NXP Semiconductors.

Legal texts have been adapted to the new company name where appropriate.

In Section 10 Static characteristics, changed conditions for input leakage and supply

current.

20031104

Product specification

74LVC1G386_2

Product data sheet

NXP B.V. 2007. All rights reserved.

Rev. 02 3 September 2007

10 of 12

74LVC1G386

NXP Semiconductors

3-input EXCLUSIVE-OR gate

16. Legal information

16.1 Data sheet status

Document status[1][2]

Product status[3]

Definition

Objective [short] data sheet

Development

This document contains data from the objective specification for product development.

Preliminary [short] data sheet

Qualification

This document contains data from the preliminary specification.

Product [short] data sheet

Production

This document contains the product specification.

[1]

Please consult the most recently issued document before initiating or completing a design.

[2]

The term short data sheet is explained in section Definitions.

[3]

The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status

information is available on the Internet at URL http://www.nxp.com.

16.2 Definitions

Draft The document is a draft version only. The content is still under

internal review and subject to formal approval, which may result in

modifications or additions. NXP Semiconductors does not give any

representations or warranties as to the accuracy or completeness of

information included herein and shall have no liability for the consequences of

use of such information.

Short data sheet A short data sheet is an extract from a full data sheet

with the same product type number(s) and title. A short data sheet is intended

for quick reference only and should not be relied upon to contain detailed and

full information. For detailed and full information see the relevant full data

sheet, which is available on request via the local NXP Semiconductors sales

office. In case of any inconsistency or conflict with the short data sheet, the

full data sheet shall prevail.

16.3 Disclaimers

General Information in this document is believed to be accurate and

reliable. However, NXP Semiconductors does not give any representations or

warranties, expressed or implied, as to the accuracy or completeness of such

information and shall have no liability for the consequences of use of such

information.

Right to make changes NXP Semiconductors reserves the right to make

changes to information published in this document, including without

limitation specifications and product descriptions, at any time and without

notice. This document supersedes and replaces all information supplied prior

to the publication hereof.

Suitability for use NXP Semiconductors products are not designed,

authorized or warranted to be suitable for use in medical, military, aircraft,

space or life support equipment, nor in applications where failure or

malfunction of a NXP Semiconductors product can reasonably be expected to

result in personal injury, death or severe property or environmental damage.

NXP Semiconductors accepts no liability for inclusion and/or use of NXP

Semiconductors products in such equipment or applications and therefore

such inclusion and/or use is at the customers own risk.

Applications Applications that are described herein for any of these

products are for illustrative purposes only. NXP Semiconductors makes no

representation or warranty that such applications will be suitable for the

specified use without further testing or modification.

Limiting values Stress above one or more limiting values (as defined in

the Absolute Maximum Ratings System of IEC 60134) may cause permanent

damage to the device. Limiting values are stress ratings only and operation of

the device at these or any other conditions above those given in the

Characteristics sections of this document is not implied. Exposure to limiting

values for extended periods may affect device reliability.

Terms and conditions of sale NXP Semiconductors products are sold

subject to the general terms and conditions of commercial sale, as published

at http://www.nxp.com/profile/terms, including those pertaining to warranty,

intellectual property rights infringement and limitation of liability, unless

explicitly otherwise agreed to in writing by NXP Semiconductors. In case of

any inconsistency or conflict between information in this document and such

terms and conditions, the latter will prevail.

No offer to sell or license Nothing in this document may be interpreted

or construed as an offer to sell products that is open for acceptance or the

grant, conveyance or implication of any license under any copyrights, patents

or other industrial or intellectual property rights.

16.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks

are the property of their respective owners.

17. Contact information

For additional information, please visit: http://www.nxp.com

For sales office addresses, send an email to: salesaddresses@nxp.com

74LVC1G386_2

Product data sheet

NXP B.V. 2007. All rights reserved.

Rev. 02 3 September 2007

11 of 12

74LVC1G386

NXP Semiconductors

3-input EXCLUSIVE-OR gate

18. Contents

1

2

3

4

5

6

6.1

6.2

7

8

9

10

11

12

13

14

15

16

16.1

16.2

16.3

16.4

17

18

General description . . . . . . . . . . . . . . . . . . . . . . 1

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Ordering information . . . . . . . . . . . . . . . . . . . . . 1

Marking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Functional diagram . . . . . . . . . . . . . . . . . . . . . . 2

Pinning information . . . . . . . . . . . . . . . . . . . . . . 2

Pinning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Pin description . . . . . . . . . . . . . . . . . . . . . . . . . 3

Functional description . . . . . . . . . . . . . . . . . . . 3

Limiting values. . . . . . . . . . . . . . . . . . . . . . . . . . 3

Recommended operating conditions. . . . . . . . 4

Static characteristics. . . . . . . . . . . . . . . . . . . . . 4

Dynamic characteristics . . . . . . . . . . . . . . . . . . 6

AC waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Package outline . . . . . . . . . . . . . . . . . . . . . . . . . 8

Abbreviations . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Revision history . . . . . . . . . . . . . . . . . . . . . . . . 10

Legal information. . . . . . . . . . . . . . . . . . . . . . . 11

Data sheet status . . . . . . . . . . . . . . . . . . . . . . 11

Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Disclaimers . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Trademarks . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Contact information. . . . . . . . . . . . . . . . . . . . . 11

Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Please be aware that important notices concerning this document and the product(s)

described herein, have been included in section Legal information.

NXP B.V. 2007.

All rights reserved.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 3 September 2007

Document identifier: 74LVC1G386_2

You might also like

- 74LVC00A: 1. General DescriptionDocument14 pages74LVC00A: 1. General DescriptionVlad Cristia-AvramNo ratings yet

- 74AHC1G02 74AHCT1G02: 1. General DescriptionDocument11 pages74AHC1G02 74AHCT1G02: 1. General DescriptionMarcu Andrei StefanNo ratings yet

- Datasheet 74153Document17 pagesDatasheet 74153Ingga Permana0% (1)

- 74LVC08A: 1. General DescriptionDocument15 pages74LVC08A: 1. General DescriptionWalterNo ratings yet

- 74ahc Ahct1g14Document15 pages74ahc Ahct1g14Ignacio ScalisiNo ratings yet

- 74HC03 74HCT03: 1. General DescriptionDocument16 pages74HC03 74HCT03: 1. General DescriptionDistribuidorIBoolPedregalDeSantoDomingoNo ratings yet

- General Description: Quad Buffer/line Driver 3-StateDocument15 pagesGeneral Description: Quad Buffer/line Driver 3-Statesinner86No ratings yet

- 74LVC1G11: 1. General DescriptionDocument14 pages74LVC1G11: 1. General DescriptionnevdullNo ratings yet

- 74AHC1G32 74AHCT1G32: 1. General DescriptionDocument12 pages74AHC1G32 74AHCT1G32: 1. General DescriptionnevdullNo ratings yet

- 74HC02 74HCT02: 1. General DescriptionDocument16 pages74HC02 74HCT02: 1. General DescriptionCesar VilledaNo ratings yet

- 74AHC1G86 74AHCT1G86: 1. General DescriptionDocument12 pages74AHC1G86 74AHCT1G86: 1. General DescriptionKushalSwamyNo ratings yet

- Quad Bilateral Switches: Integrated CircuitsDocument10 pagesQuad Bilateral Switches: Integrated CircuitsBrzata PticaNo ratings yet

- 74 Alvc 164245Document13 pages74 Alvc 164245roozbehxoxNo ratings yet

- 74cx16839 U18 PDFDocument7 pages74cx16839 U18 PDFMarcos AurélioNo ratings yet

- 74HC107 74HCT107: 1. General DescriptionDocument20 pages74HC107 74HCT107: 1. General DescriptionDistribuidorIBoolPedregalDeSantoDomingoNo ratings yet

- 74VCX16501 Low Voltage 18-Bit Universal Bus Transceivers With 3.6V Tolerant Inputs and OutputsDocument8 pages74VCX16501 Low Voltage 18-Bit Universal Bus Transceivers With 3.6V Tolerant Inputs and OutputsFredhuiNo ratings yet

- DatasheetDocument8 pagesDatasheetMaizatul Hanisah RoziNo ratings yet

- 74HC00 74HCT00: 1. General DescriptionDocument16 pages74HC00 74HCT00: 1. General DescriptionvanlongsportNo ratings yet

- 74 HC 245Document22 pages74 HC 245Vương QuýNo ratings yet

- 74AUP1G07: 1. General DescriptionDocument19 pages74AUP1G07: 1. General DescriptionSyed Noman AhmedNo ratings yet

- General Description: Quad Bistable Transparant LatchDocument20 pagesGeneral Description: Quad Bistable Transparant LatchCesar VilledaNo ratings yet

- 74AHC125 74AHCT125: 1. General DescriptionDocument15 pages74AHC125 74AHCT125: 1. General Descriptionkitt354No ratings yet

- 74HC10-Q100 74HCT10-Q100: 1. General DescriptionDocument13 pages74HC10-Q100 74HCT10-Q100: 1. General DescriptionNelson RodriguezNo ratings yet

- 74HC32Document20 pages74HC32Ingrid XytrasNo ratings yet

- 74HC08 74HCT08: 1. General DescriptionDocument16 pages74HC08 74HCT08: 1. General DescriptionCesar VilledaNo ratings yet

- 74VCX86 Low Voltage Quad 2-Input Exclusive-OR Gate With 3.6V Tolerant Inputs and OutputsDocument7 pages74VCX86 Low Voltage Quad 2-Input Exclusive-OR Gate With 3.6V Tolerant Inputs and Outputsgame___overNo ratings yet

- 74 LV 00Document10 pages74 LV 00Brzata PticaNo ratings yet

- Data Sheet: 74AHC74 74AHCT74Document20 pagesData Sheet: 74AHC74 74AHCT74Kang JadiJaya OtodidakNo ratings yet

- Octal Bus Transceiver With 3-State Outputs: FeaturesDocument24 pagesOctal Bus Transceiver With 3-State Outputs: FeaturesLungoci AdrianNo ratings yet

- 74HC HCT4066 NXPDocument27 pages74HC HCT4066 NXPprpabst8514No ratings yet

- 74LVC1G04: 1. General DescriptionDocument20 pages74LVC1G04: 1. General DescriptionnevdullNo ratings yet

- 74LVT2244, 74LVTH2244 Low Voltage Octal Buffer/Line Driver With 3-STATE Outputs and 25 Series Resistors in The OutputsDocument9 pages74LVT2244, 74LVTH2244 Low Voltage Octal Buffer/Line Driver With 3-STATE Outputs and 25 Series Resistors in The Outputsjovares2099No ratings yet

- Data Sheet: 74HC14 74HCT14Document23 pagesData Sheet: 74HC14 74HCT14Miguel LamborghiniNo ratings yet

- 74HC244 74HCT244: 1. General DescriptionDocument18 pages74HC244 74HCT244: 1. General DescriptionCesar VilledaNo ratings yet

- General Description: Dual 4-Input AND GateDocument15 pagesGeneral Description: Dual 4-Input AND GateRizki FebriyantoNo ratings yet

- 74HC4040 74HCT4040: 1. General DescriptionDocument20 pages74HC4040 74HCT4040: 1. General DescriptionWilliamNo ratings yet

- General Description: Quad Bilateral SwitchDocument23 pagesGeneral Description: Quad Bilateral Switchtotal4321No ratings yet

- 7Z08Document7 pages7Z08André Frota PaivaNo ratings yet

- 74LVC14APWDHDocument11 pages74LVC14APWDHIlie GrecuNo ratings yet

- 74HC245 74HCT245: 1. General DescriptionDocument18 pages74HC245 74HCT245: 1. General Descriptionnadeem hameedNo ratings yet

- Quad 2-Input Data Selector/Multiplexer: IN74ACT158Document5 pagesQuad 2-Input Data Selector/Multiplexer: IN74ACT158Sahil BharatNo ratings yet

- 47HC00 NandDocument17 pages47HC00 NandWilliams Paredes CNo ratings yet

- Datasheet 74HCT04 PDFDocument4 pagesDatasheet 74HCT04 PDFCarlos RamirezNo ratings yet

- 74HC193 74HCT193: NXP SemiconductorsDocument2 pages74HC193 74HCT193: NXP SemiconductorskjfenNo ratings yet

- 74LCX125 Low Voltage Quad Buffer With 5V Tolerant Inputs and OutputsDocument13 pages74LCX125 Low Voltage Quad Buffer With 5V Tolerant Inputs and Outputsfenixtec1No ratings yet

- Quad 2-Input AND Gate: KK74HC08ADocument5 pagesQuad 2-Input AND Gate: KK74HC08Acatsoithahuong84No ratings yet

- 74HC32-Q100 74HCT32-Q100: 1. General DescriptionDocument16 pages74HC32-Q100 74HCT32-Q100: 1. General Descriptiongotcha75No ratings yet

- Nc7Sbu3157 - Fsau3157 Tinylogic Low Voltage Uhs SPDT Analog Switch With 2V Undershoot ProtectionDocument11 pagesNc7Sbu3157 - Fsau3157 Tinylogic Low Voltage Uhs SPDT Analog Switch With 2V Undershoot ProtectionAgus TabraniNo ratings yet

- All About TTL Ic 258Document7 pagesAll About TTL Ic 258AraoFilhoNo ratings yet

- HC74Document5 pagesHC74Bruno NascimentoNo ratings yet

- 74HC04 74HCT04: 1. General DescriptionDocument18 pages74HC04 74HCT04: 1. General DescriptionDistribuidorIBoolPedregalDeSantoDomingoNo ratings yet

- MM74HC245A Octal 3-STATE Transceiver: General DescriptionDocument7 pagesMM74HC245A Octal 3-STATE Transceiver: General DescriptionMubarak CeNo ratings yet

- 74LVC4245A: 1. General DescriptionDocument18 pages74LVC4245A: 1. General DescriptionLeslie StewartNo ratings yet

- Double Channel High Side Solid State RelayDocument18 pagesDouble Channel High Side Solid State RelayDan EsentherNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Gen00036-04 Wa600-6 Wheel LoaderDocument98 pagesGen00036-04 Wa600-6 Wheel LoaderJuan Araya BarrazaNo ratings yet

- Fastening SystemsDocument74 pagesFastening SystemsskyvaneNo ratings yet

- 380LC9S Performance PDFDocument21 pages380LC9S Performance PDFLuis Antonio Vega ParangueoNo ratings yet

- Case Study - RESCOMDocument43 pagesCase Study - RESCOMMahima PriyadarshiniNo ratings yet

- Resistance WeldingDocument22 pagesResistance WeldingLOKENDRA91100% (2)

- Earthquake in TaguigDocument4 pagesEarthquake in TaguigDianca Zyra Rodil-CabanelaNo ratings yet

- 2 TensionDocument28 pages2 TensionRICKY IVANNo ratings yet

- Types of PatternDocument12 pagesTypes of PatternadamNo ratings yet

- Plastic Roads: Presented By-Akash Chakole (First Year MBBS, GMC Nagpur)Document27 pagesPlastic Roads: Presented By-Akash Chakole (First Year MBBS, GMC Nagpur)Chandu CKNo ratings yet

- 6 3 AnswersDocument4 pages6 3 Answersshiwaisanxian100% (1)

- Size Matters: (Type The Document Subtitle)Document16 pagesSize Matters: (Type The Document Subtitle)SamarthGoelNo ratings yet

- Operation Guide MSBDocument8 pagesOperation Guide MSBMao RathanithNo ratings yet

- Radome Moisture TesterDocument13 pagesRadome Moisture TesterInterogator5100% (1)

- Procedures For Solar Electric (Photovoltaic Abbreviated As PV) System Design and InstallationDocument5 pagesProcedures For Solar Electric (Photovoltaic Abbreviated As PV) System Design and InstallationUmamaheshwarrao VarmaNo ratings yet

- Modern PetrochemicalsDocument179 pagesModern PetrochemicalsHani Kirmani100% (9)

- PPE Microproject Report.Document14 pagesPPE Microproject Report.JAMES BOND100% (2)

- Sop 4590Document230 pagesSop 4590Mike WilliamNo ratings yet

- EMC PartDocument67 pagesEMC PartFelix DiazNo ratings yet

- ANNEX 9 - FacilitationDocument62 pagesANNEX 9 - FacilitationSyahid Macheda100% (1)

- ReactionsDocument30 pagesReactionskaloibestNo ratings yet

- Ionic Equations & Redox ReactionsDocument6 pagesIonic Equations & Redox ReactionsAyaanNashidNo ratings yet

- Flexibility and Safety: BERNSTEIN Safety Hinge SwitchesDocument12 pagesFlexibility and Safety: BERNSTEIN Safety Hinge SwitchespiterNo ratings yet

- Copeland Scroll Compressors For Refrigeration Zs09kae Zs11kae Zs13kae Application Guidelines en GB 4214008Document24 pagesCopeland Scroll Compressors For Refrigeration Zs09kae Zs11kae Zs13kae Application Guidelines en GB 4214008Cesar Augusto Navarro ChirinosNo ratings yet

- Auditing RacfDocument57 pagesAuditing Racfசிங்கார வேலன்No ratings yet

- Sqldatagrid Symbol User'S Guide: ArchestraDocument36 pagesSqldatagrid Symbol User'S Guide: ArchestraAde SuryaNo ratings yet

- Infinique Structured Cabling Installation ChecklistDocument2 pagesInfinique Structured Cabling Installation Checklistroot75% (4)

- Kioti Daedong NX4520, NX5020, NX5520, NX6020 Tractors Service Manual 10-2019Document19 pagesKioti Daedong NX4520, NX5020, NX5520, NX6020 Tractors Service Manual 10-2019LisakolyNo ratings yet

- Física Práctica 1 MRUDocument5 pagesFísica Práctica 1 MRUPolet BarrionuevoNo ratings yet

- Wrights Offshore Hydrate Remediation Skid ArticleDocument4 pagesWrights Offshore Hydrate Remediation Skid ArticleAnonymous ItzBhUGoiNo ratings yet