Professional Documents

Culture Documents

ED Practica 1 Electrónica Digital

Uploaded by

Alexandre Pérez ReinaCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

ED Practica 1 Electrónica Digital

Uploaded by

Alexandre Pérez ReinaCopyright:

Available Formats

Electrnica Digital

Universidad de Alcal

Curso Acadmico 2014/2015

Curso 1 Cuatrimestre 2

Alumno(s)

Grupo

Puesto

Prctica 1.

Diseo e implementacin de un sistema combinacional con elementos discretos

ndice:

1. INTRODUCCIN ................................................................................................................................... 2

2. OBJETIVOS ............................................................................................................................................ 2

3. CONCEPTOS TERICOS. ..................................................................................................................... 3

4. FUNCIONALIDAD DEL MONTAJE 1. ................................................................................................. 3

4.1. DESCRIPCIN DEL MONTAJE 1. .............................................................................................. 3

4.2. DESCRIPCIN, MONTAJE Y PRUEBAS DE CADA BLOQUE. .................................................. 4

4.2.1. ENTRADA DE DATOS. .................................................................................................... 4

4.2.2. MULTIPLEXOR. BLOQUE DE SELECCIN DE DATO DE ENTRADA. ...................... 5

4.2.3. MDULO DE VISUALIZACIN. .................................................................................... 6

4.2.4. BLOQUE DETECTOR DE DATO MAYOR QUE NUEVE. ............................................. 8

4.3. SISTEMA COMPLETO. ............................................................................................................... 10

5. DESCRIPCIN DEL MONTAJE 2 ...................................................................................................... 11

-1-

Prctica 1.

Diseo e implementacin de un sistema combinacional con elementos discretos

1. INTRODUCCIN

En esta primera prctica de Electrnica Digital se implementa un sistema combinacional que

responde a unas especificaciones de diseo dadas. El diseo del mismo se aborda mediante

elementos discretos, para lo cual el alumno deber consultar los datos tcnicos que

proporciona el fabricante, para cada uno de los dispositivos escogidos. Con la informacin

proporcionada por el fabricante el alumno debe interpretar tanto los terminales de conexin de

cada dispositivo como las seales de entrada, salida y control del mismo, comprendiendo su

funcionalidad y niveles lgicos.

La prctica consiste en la realizacin de dos montajes (Montaje 1 y Montaje 2), los cuales son

de realizacin obligatoria. El Montaje 2 supone una modificacin del Montaje 1.

En la seccin 4, desarrollo delMontaje 1, se comienza con una descripcin de alto nivel del

sistema, en el que se muestra un esquema de bloques del mismo, se detallan las

especificaciones de diseo, y se definen claramente las entradas y salidas. Despus se realiza

una descripcin de cada uno de los bloques que lo componen. Aparte de las seales de

entrada y salida del sistema completo mencionado, los diferentes circuitosdisponen de

terminales de control que deben fijarse al nivel lgico correspondiente. Para la interpretacin

correcta de estos terminales, el alumno debe consultar la tabla de funcionamiento del

dispositivo proporcionada por el fabricante.

En la seccin 5 se describe la modificacin a realizar en el Montaje 1 para conseguir el

Montaje 2. Esta parte exige de una participacin mayor del alumno en el diseo.

En la prctica existen una serie de cuestiones de realizacin obligatoria que el alumno debe

responder en los espacios reservados para ello y cuyo resultado influir en la calificacin final

de la prctica.

Esta memoria deber ser impresa y cumplimentada todas las cuestiones antes de acceder al

laboratorio.

2. OBJETIVOS

El objetivo principal de esta prctica consiste en que el alumno sea capaz de analizar,

implementar y testear con xito un sistema combinacional, as como con aspectos relacionados

con el diseo de sistemas digitales. Los objetivos parciales que se pretenden lograr son los

siguientes:

Afianzar mediante la prctica los conocimientos adquiridos en las sesiones tericas

sobre diferentes mdulos combinacionales con distintas funcionalidades.

Adquirir de forma prctica la nocin de sistema combinacional, diseado a partir de

bloques independientes interconectados entre s, para cumplir unas especificaciones

concretas.

Trasladar la capacidad de analizar un sistema, desde su descripcin de alto nivel hasta

su funcionamiento en el bajo nivel del mismo, al mbito prctico en el laboratorio.

Ser capaz de buscar informacin tcnica proporcionada por el fabricante o el

diseador, y comprender dicha informacin para utilizarla en una implementacin real.

Departamento de Electrnica

Universidad de Alcal

Prctica 1.

Diseo e Implementacin de unSistema Combinacional con Elementos Discretos

3. CONCEPTOS TERICOS.

Los conceptos tericos directamente relacionados con esta prctica son los siguientes:

Fundamentos de lgica combinacional

Codificacin en binario y en BCD

Funciones de las entradas de datos, entradas de control y salidas de los circuitos

combinacionales e interpretacin de sus niveles lgicos

Funcionamiento de un multiplexor digital

Funcionamiento de un decodificador BCD-7segmentos

4. FUNCIONALIDAD DEL MONTAJE 1.

En el montaje 1 se plantea el diseo de un sistema combinacional que recibe 2 datosA y Bde

4 bits codificados en binario natural y permite, mediante una seal SEL, seleccionarcual es el

dato a serrepresentado en un display, de forma que con un nivel alto se selecciona el dato B y

con un nivel bajo el A. El dato se visualiza slo si su valor est comprendido entre 0 y 9. Si el

valor es mayor que 9 se enciende el punto del display, mientras que los segmentos a-g del

display permanecen apagados. El display es de nodo comn de forma que los segmentos y el

punto se iluminan cuando en sus entradas existe un nivel bajo.

4.1.

DESCRIPCIN DEL MONTAJE 1.

En la Figura 1se muestran un diagrama de bloques del sistemacorrespondiente al Montaje 1.

A[3:0]

(0)

S[3:0] DECODIFICADOR

BCD 7 SEG

B[3:0]

(1)

a

b

c

d

e

f

g

SEL

DETECTOR

>9

DP_on

Figura 1 Diagrama de bloques de la prctica.

En primer lugar se realiza la multiplexacin de los datos A y B en funcin del valor de la seal

SEL segn la siguiente la tabla:

SEL

0

1

S[3:0]

A[3:0]

B[3:0]

A partir del dato seleccionado (S),en el bloque DETECTOR>9 se genera una seal DP_on que

proporciona a nivel bajo siempre que S sea mayor que 9 y a nivel alto en caso contrario. Esta

seal va a ser utilizada para iluminar o apagar el punto del display y para inhibir o habilitar el

decodificador BCD a 7 segmentos:

Cuando en valor representado por el dato Sseamayor que9 (DP_on= 0), se iluminar

el punto del display a la vez que permanecen apagados todos sus segmentos

-3-

Prctica 1.

4.2.

Diseo e implementacin de un sistema combinacional con elementos discretos

Cuando en valor representado por el dato Ses menor o igual a 9 (DP_on= 1), dicho

valor se visualizar en el display y el punto permanece apagado.

DESCRIPCIN, MONTAJE Y PRUEBAS DE CADA BLOQUE.

Una vez descrito el funcionamiento del sistema, se procede a detallar cada uno de los bloques

que lo integran.

4.2.1.

ENTRADA DE DATOS.

Los datos son introducidos en el sistema por el usuario mediante microinterruptores

(microswitches), codificados en binario natural, tal y como se indica en laFigura 2.a.

Figura 2Microswitches para los datos de entrada (a). Circuito equivalente de cada interruptor (b).

Descripcin del funcionamiento.

Con los microswitches conectados como se muestra en laFigura 2.a, cada uno de los bits se

activa independientemente, de manera que en la posicinON (Cerrado) se tiene un nivel

bajo(GND) en el bit correspondiente, y un nivel alto (Vcc) en la posicin contraria.Cada

interruptor funciona individualmente como el esquema de laFigura 2.a.

Cuestin 1. De acuerdo a la Figura 3, indique la posicin (cerrado - C o abierto - A) de los

microswitches para obtener los valores decimales: A=12d y B=4 d.

A3:

A2:

A1:

A0:

B3:

B2:

B1:

B0:

Consideraciones sobre el montaje.

En el esquema de laFigura 2.a, se han configurado los microswitches de forma que con el

interruptor en la posicin inferior se tiene un nivel bajo (L) y con la posicin hacia arriba se

tiene un nivel alto (H) (vase la marca en la zona inferior). Dado que existen diferentes tipos

de microinterruptores (algunos incluso carecen de marca), se aconseja realizar una prueba

previa con el polmetro para tener claro en qu posicin del interruptor se tiene un nivel alto

(H) o bajo (L).

Departamento de Electrnica

Universidad de Alcal

Prctica 1.

Diseo e Implementacin de unSistema Combinacional con Elementos Discretos

Las resistencias determinan la corriente que circula por los microswitches, y debe tenerse en

cuenta cul es la corriente mxima que soportan para no daarlos. Se puede utilizar cualquier

valor de resistencia que se encuentre dentro del margen 1K y 10K. Para esta prctica se

elige el valor de 1K.

Pruebas.

Para comprobar que los microswitches estn correctamente conectados, configure algn dato

en cada uno de ellos y compruebe con el polmetro, u osciloscopio, que se tienen los niveles de

tensin correspondientes en cada uno de los bits. Por ejemplo, tanto en A como en B:

Configure el dato, en decimal5d (0101b) en A y compruebe que tiene los niveles en

A3A2A1A0=LHLH. Proceda igual con B.

Configure el dato, en decimal, N=10 d (1010 b) en A y compruebe que tiene los niveles

en A3A2A1A0=HLHL. Proceda igual con B.

4.2.2.

MULTIPLEXOR. BLOQUE DE SELECCIN DE DATO DE ENTRADA.

Para seleccionar el dato en la entrada se a utilizar el multiplexor 74LS157, cuyo patillaje se

muestra en la Figura 3.

2

3

5

6

11

10

14

13

1

15

74LS157

1A

1B

2A

2B

3A

3B

4A

4B

1Y

2Y

3Y

4Y

4

7

9

12

A/B

G

Figura 3 Patillaje del C.I. 74LS157.

Cuestin 2. De acuerdo con la tabla de funcionamiento del 74LS175 indicar el valor que habr

en las salidas si la en la entrada G (pin 15) hay un nivel alto. Este valor depende del nivel

lgico aplicado al pin 1?

Cuestin 3. De acuerdo con la tabla de funcionamiento del 74LS175 complete las conexiones

a realizar sobre l para implementar el multiplexor de la Figura 1.

A0

B0

A1

B1

A2

B2

A3

B3

SEL

74157

2

3

5

6

11

10

14

13

1A

1B

2A

2B

3A

3B

4A

4B

1

15

A/B

G

-5-

1Y

S0

2Y

S1

3Y

4Y

12

S2

S3

Diseo e implementacin de un sistema combinacional con elementos discretos

Prctica 1.

Cuestin 4. De acuerdo con conexin realizada en la figura de laCuestin 3.Completar la

siguiente tabla.

A3 A2 A1 A0

0 1 1 0

0 1 1 0

B3 B2 B1 B0

1 0 0 1

1 0 0 1

SEL

0

1

S3 S2 S1 S0

Consideraciones sobre el montaje.

La conexin de la seal de seleccinSEL puede realizarse conectando, con un cable, el

terminal correspondiente a Vcc o GND o bien puede hacer uso de unmicroswitch adicional.

Pruebas

Para comprobar que el mdulo realiza la multiplexacin de manera correcta, realice, por

ejemplo, las siguientes pruebas:

Compruebe que el 72LS175 est habilitado, midiendo el nivel lgico correspondiente al

pin 15 con un polmetro.

Introduzca los datos A3..A0=0110 y B3..B0=1001

Seleccione un nivel bajo en SELy compruebe que en S3..S0 se tienen los niveles

lgicos 0110.

4.2.3.

Seleccione un nivel alto en SELy compruebe que en S3..S0 se tienen los niveles

lgicos 1001.

MDULO DE VISUALIZACIN.

El mdulo de visualizacin (Figura 4) est compuesto a su vez por dos elementos: el elemento

de visualizacin propiamente dicho (en este caso un display de 7 segmentos de nodo comn)

y un driver(74LS47) para excitar dicho elemento de visualizacin.

74LS47

1

2

4

8

BI/RBO

RBI

LT

A

B

C

D

E

F

G

D3

Rpd

13

12

11

10

9

15

14

Vcc

a

b

c

d

e

f

g

VCC

Dp

7

1

2

6

4

5

3

display

Figura 4 Estructura del mdulo de visualizacin.

Descripcin del funcionamiento.

El displayutilizado para la visualizacin es de nodo comn, de forma que un nivelbajo en cada

una de sus entras (a, b..g) provoca que se encienda el correspondiente segmento. El terminal

correspondiente a la entrada DP permite controlar el encendido del punto decimal. Esta

entrada, tambin, es activa a nivel bajo (con un nivel bajo se enciende). El patillaje del display

depende del dispositivo utilizado. A nivel de ejemplo en la Figura 5.ase muestra el patillaje y

estructura interna de un display. Analizndola se obtiene la correspondencia entre los pines y

los segmentos (Figura 5.b). Para este display (de nodo comn) el terminal 3 o 14, o ambos, se

deben conectar a Vcc.

Departamento de Electrnica

Universidad de Alcal

Prctica 1.

Diseo e Implementacin de unSistema Combinacional con Elementos Discretos

1

2

13

11

7

(a)

10

9

(b)

Figura 5 display de nodo comn. a) Estructura interna. b) Correspondencia pines-segmentos.

Cuestin 5. Completar la asignacin de pines-segmentos, de forma similar a la utilizada en la

Figura 5.b, para el display adquirido por el alumno para realizar la prctica.

El 74LS47 es un decodificador BCD-7segmentos utilizado para trabajar con displays de nodo

comn.El dato de entrada tiene un tamao de cuatro bitsy proporciona 7 salidas (a-g) para

conectarlas a las correspondientes entradas de un display de 7 segmentos.

Cuestin 6.Indicar que caracteres se visualizan en el display cuando el cdigo presente en las

entradas del 74LS47 se corresponde con los valores 0111b, 0101b, 1111by 1011b. Qu

conclusin se saca del anlisis de la tabla de verdad del 74LS47.

Consideraciones sobre el montaje.

Las resistencias RPD entre el driver y las entradas del display sirven para limitar la corriente por

los diodos LED (segmentos) del display. Su valor debe garantizarse un valor comprendido

entre el mnimo y mximo de corriente del display (para que luzca y no se estropee,

respectivamente). Adems, esta corriente deber ser menor que la mxima admitida por el

driver en sus terminales de salida.

De forma aproximada, se puede calcular esta resistencia fijando una corriente para cada

segmento igual a 10mA. S, su valor vendr dado por:

5 1,5

10

350

Valores comprendidos entre 300 y 600 son admisibles para estas resistencias.

-7-

Diseo e implementacin de un sistema combinacional con elementos discretos

Prctica 1.

4.2.4.

BLOQUE DETECTOR DE DATO MAYOR QUE NUEVE.

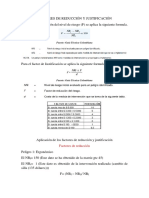

El bloque detector de nmero mayor que nueve (Figura 6) es un bloque lgico que proporciona

una salida DP_on que se pone a nivel bajocuando el valor representado por la salida (S) del

multiplexor es mayor que 9, y un nivel alto en caso contrario.

S3

S2

S1

DET ECTOR

DP_on

>9

S0

Figura 6Diagrama del bloque DETECTOR>9.

Cuestin 7.De acuerdo con el funcionamiento del bloque DETECTOR >9,complete la siguiente

tabla de verdad para obtener la salida DP_on.

Entradas

Salidas

S3

S2

S1

S0

Departamento de Electrnica

DP_on

Universidad de Alcal

Prctica 1.

Diseo e Implementacin de unSistema Combinacional con Elementos Discretos

Cuestin 8.Obtenga la funcin simplificada de DP_on.

S1S0

S3S2

00 10 11 01

00

10

11

01

Cuestin 9.Implementar utilizando puertas NAND de 2 entradas la ecuacin de laCuestin 8.

-9-

Diseo e implementacin de un sistema combinacional con elementos discretos

Prctica 1.

4.3.

SISTEMA COMPLETO.

El esquema completo del sistema combinacional se obtendr uniendo los circuitos creados en

las cuestiones anteriores.

DP_on

Vcc

330 ?

VCC

Cuestin 10.Completar el siguiente circuito para obtener el sistema de la Figura 1. Se deber

indicar el nmero de pin correspondiente a las puertas nand(74LS00) del bloque

DETECTOR>9.

display

12 S3

A/B

G

10

SEL

1k ?

VCC

1

15

A3 A2 A1 A0

B3 B2 B1 B0

S2

9

3Y

S1

7

2Y

S0

1Y

74157

1k ?

2

3

5

6

11

10

14

13

1A

1B

2A

2B

3A

3B

4A

4B

4Y

1

2

3

4

8

7

6

5

VCC

1

2

3

4

8

7

6

5

7

1

2

6

4

5

3

1

2

4

8

BI/RBO

RBI

LT

A

B

C

D

E

F

G

74LS47

13

12

11

10

9

15

14

330 ?

DETECTOR > 9

a

b

c

d

e

f

g

DISPLAY

Dp

Departamento de Electrnica

Universidad de Alcal

Prctica 1.

Diseo e Implementacin de unSistema Combinacional con Elementos Discretos

Cuestin 11.De acuerdo con el circuito de la Cuestin 10 completar la siguiente tabla:

SEL

0101 0010 0101

0101 0010

1001 1111

1001 1111

1011 0000

Dp_on

ABCDEFG

(Salidas del 74LS47)

Punto

Carcter visualizado

el display

0100100

Apagado

Una vez montado el sistema completo, compruebe el funcionamiento correcto del mismo, con

diferentes combinaciones de los datos de entrada A y B y de la seal SEL de seleccin. Se

puede comenzar con los valores indicados en la Cuestin 11.

5. DESCRIPCIN DEL MONTAJE 2

Para el Montaje 2 se va a realizar la modificacin del Montaje 1 de forma que se cambie la

forma en la que se visualiza el dato (S) de salida del multiplexor. La visualizacin se realiza en

formato decimal mostrndose las unidades en el display y las decenas se visualizan con el

punto. As, para visualizar el dato S=0101b(S= 5d), en el display se muestra el 5 y el punto se

encuentra apagado. Por su parte, para S= 1100 b(S= 12d),en el display se muestra el 2 y el

punto se enciende.

En la Figura 7 se muestra la estructura del nuevo circuito a disear y montar.Partiendo del

circuito de la Figura 1, se ha intercalado el bloque BloqueCombinacionalentre el multiplexor y el

decodificador BCD-7 segmentos. Este bloque recibe el dato S codificado en binario y

proporciona un dato de 4 bits correspondiente a las unidades de S, ms un bit que representa

a las decenas de S (0 1).Las unidades se visualizan en el display, previo paso por el

conversor BCD a 7 segmentos, y el punto debe encenderse o apagarse de la forma explicada

en el prrafo anterior.

A[3:0]

(0 )

S[3:0]

B[3:0]

CON

VER SOR

Bloque

BINARI O

UNID ADES[ 3:0]

Combinacional

DEC .

BCD 7 SEG

(1 )

SEL

DECENAS

Figura 7 Diagrama de bloque del Montaje 2.

-11-

a

b

c

d

e

f

g

Prctica 1.

Diseo e implementacin de un sistema combinacional con elementos discretos

Cuestin 12.Busque y explique cul debe ser el procedimiento a seguir para disear el Bloque

Combinacional descrito utilizando un sumador de 4 bits.Se debe justificar la base terica en la

que se basa la solucin adoptada.

Cuestin 13.Dibuje el circuito digital que implementa el bloque CONVERSOR BINARIO de la

Figura 7.

Departamento de Electrnica

12

Universidad de Alcal

Prctica 1.

Diseo e Implementacin de unSistema Combinacional con Elementos Discretos

Cuestin 14.Dibujar el circuito completo correspondiente al Montaje 2.

-13-

You might also like

- Practica3 - Liliana Andrea LopezDocument3 pagesPractica3 - Liliana Andrea LopezJuan carlos Garacia mazueraNo ratings yet

- Sistemas de control integrados en bienes de equipo y maquinaria industrial y elaboración de la documentación técnica. FMEE0208From EverandSistemas de control integrados en bienes de equipo y maquinaria industrial y elaboración de la documentación técnica. FMEE0208No ratings yet

- MultisimDocument13 pagesMultisimjosersNo ratings yet

- Andrade - Charles - (Practica de Laboratorio 10)Document10 pagesAndrade - Charles - (Practica de Laboratorio 10)Charles AndradeNo ratings yet

- Puesta en marcha de sistemas de automatización industrial. ELEM0311From EverandPuesta en marcha de sistemas de automatización industrial. ELEM0311Rating: 3 out of 5 stars3/5 (1)

- Andrade - Charles - (Practica de Laboratorio 10)Document10 pagesAndrade - Charles - (Practica de Laboratorio 10)Charles AndradeNo ratings yet

- Transformadores 3Document118 pagesTransformadores 3Eduardo Favio Lopez PalominoNo ratings yet

- Practicaa4Document8 pagesPracticaa4Juan antonio Resendiz FuentesNo ratings yet

- Equipo2 Pract#06Document9 pagesEquipo2 Pract#06EDGAR ADRIAN CRUZ CERVANTESNo ratings yet

- P3 CombinacionalesDocument7 pagesP3 CombinacionalesDrone DevotionNo ratings yet

- Trabajo Software 1Document12 pagesTrabajo Software 1Sergio Estevan Suarez DiazNo ratings yet

- Informe Practica de Laboratorio 1Document30 pagesInforme Practica de Laboratorio 1VICTOR MANUEL DELGADO CUBILLOSNo ratings yet

- Fase 2 - Estudiante Manuel OrtegonDocument17 pagesFase 2 - Estudiante Manuel OrtegonManuel OrtegonNo ratings yet

- Rreporte de Practica 3Document15 pagesRreporte de Practica 3FERNANDEZ MORALES EDSON YAHIRNo ratings yet

- Circuitos Electricos Portafolio de EvidenciasDocument10 pagesCircuitos Electricos Portafolio de EvidenciasAntonio HernandezNo ratings yet

- Reloj DigitalDocument15 pagesReloj DigitalGomer Guevara TitoNo ratings yet

- Prácticas de Laboratorio p5Document6 pagesPrácticas de Laboratorio p5Guillo YeroviNo ratings yet

- PMSD 425 TrabajofinalDocument7 pagesPMSD 425 TrabajofinalquispesaldiasdannyNo ratings yet

- Laboratorio #4Document5 pagesLaboratorio #4A jugar yaNo ratings yet

- Contador FotoeléctricoDocument12 pagesContador FotoeléctricoAlexDanielNo ratings yet

- Informe Codificador y MultiplexorDocument3 pagesInforme Codificador y MultiplexorAndres CastellanosNo ratings yet

- Informe de Laboratorio Electronica DigitalDocument7 pagesInforme de Laboratorio Electronica Digitalsebastian bustamanteNo ratings yet

- 01 Practica 01 Celda de CargaDocument6 pages01 Practica 01 Celda de CargaJorge Paredes MonesNo ratings yet

- Unidad 2 James Bend Reinoso Diaz Grupo 243004 72Document18 pagesUnidad 2 James Bend Reinoso Diaz Grupo 243004 72james reinosoNo ratings yet

- Embebidos Hoja Guia 4 2020BDocument3 pagesEmbebidos Hoja Guia 4 2020BJonathan Fernando SfNo ratings yet

- Laboratorio Numeros BinariosDocument12 pagesLaboratorio Numeros BinariosFrancisco GonzalezNo ratings yet

- Practicas de LaboratorioDocument10 pagesPracticas de LaboratorioHéctor VelásquezNo ratings yet

- Inf - Lab. - 5 Circuitos MSIDocument7 pagesInf - Lab. - 5 Circuitos MSILazaro BaldiviezoNo ratings yet

- SD Hoja Guia 10 2019BDocument3 pagesSD Hoja Guia 10 2019BCarlos AlvearNo ratings yet

- Practicas DigitalesDocument23 pagesPracticas DigitalesdavidNo ratings yet

- Julian Ramiro Lopez - Fase 2 - Análisis de Circuitos CombinacionalesDocument13 pagesJulian Ramiro Lopez - Fase 2 - Análisis de Circuitos CombinacionalesJulian LopezNo ratings yet

- Control On/off Con Banda MuertaDocument12 pagesControl On/off Con Banda MuertaJorge VargasNo ratings yet

- Infor de TTL 7404, 7408 y 7432Document15 pagesInfor de TTL 7404, 7408 y 7432frandyNo ratings yet

- Practica 1 Mod 2Document16 pagesPractica 1 Mod 2FatimaAlarconBlancoNo ratings yet

- Julian Ramiro Lopez - Unidad - 2 Fase - 2 - Analisis de Circuitos CombinacionalesDocument14 pagesJulian Ramiro Lopez - Unidad - 2 Fase - 2 - Analisis de Circuitos CombinacionalesJulian LopezNo ratings yet

- Diseno Circuito Contador Aplicado Al Sistema Seguridad Locales Respecto Su AforoDocument10 pagesDiseno Circuito Contador Aplicado Al Sistema Seguridad Locales Respecto Su AforoYurick Usca UscaNo ratings yet

- Practica 4 - EDDocument10 pagesPractica 4 - EDValeria_13No ratings yet

- Circuitos Electrónicos para La Generación de Señales Analógicas y Digitales Utilizando El Software LiveWireDocument13 pagesCircuitos Electrónicos para La Generación de Señales Analógicas y Digitales Utilizando El Software LiveWireDarwin TapuyoNo ratings yet

- Solucion GuiaDocument19 pagesSolucion GuiallensanNo ratings yet

- Diseño de Circuitos LógicosDocument13 pagesDiseño de Circuitos LógicosRonald Martínez RiveraNo ratings yet

- Entrega TrabajoDocument9 pagesEntrega Trabajojefferson anguloNo ratings yet

- Laboratorio 3.1Document7 pagesLaboratorio 3.1Jonathan LiscanoNo ratings yet

- LAB09 Máquinas de Estado-1Document8 pagesLAB09 Máquinas de Estado-1PGTENo ratings yet

- INFORME7X5Document19 pagesINFORME7X5AndreaCárdenasNo ratings yet

- Práctica 1 Compuertas LogicasDocument14 pagesPráctica 1 Compuertas Logicasleandro sanchezNo ratings yet

- Eeit Eeit-419 FormatoalumnotrabajofinalDocument6 pagesEeit Eeit-419 FormatoalumnotrabajofinalKenny Vega100% (1)

- Electronica Anexo Automatizacion IndustrialDocument107 pagesElectronica Anexo Automatizacion IndustrialIng Engelbert MolinaNo ratings yet

- PED #2 - Diseño de Sistemas Digitales Combinacionales - v2021Document3 pagesPED #2 - Diseño de Sistemas Digitales Combinacionales - v2021Guido ChambillaNo ratings yet

- Compuertas en Cascada Con VHDLDocument9 pagesCompuertas en Cascada Con VHDLIsmael SuárezNo ratings yet

- Guia Digitales II-1321657Document7 pagesGuia Digitales II-1321657JavierNo ratings yet

- Glab-S01 FinalDocument9 pagesGlab-S01 FinalCesar Agusto Choque MamaniNo ratings yet

- Practica 5Document10 pagesPractica 5Diana ObandoNo ratings yet

- Cuadernillo de PracitcasDocument40 pagesCuadernillo de PracitcasRey PersaNo ratings yet

- Prácticas de Laboratorio Sistemas Digitales 2019BDocument28 pagesPrácticas de Laboratorio Sistemas Digitales 2019BKAGGHGNo ratings yet

- Paso 2 - Grupo 8Document21 pagesPaso 2 - Grupo 8victor cardonaNo ratings yet

- Practica 1Document4 pagesPractica 1Daniel Fernando Camacho MoraNo ratings yet

- Tarea 3 Jorman Manrique B.Document13 pagesTarea 3 Jorman Manrique B.david contrerasNo ratings yet

- Tarea - 2 ElectronicaDocument27 pagesTarea - 2 ElectronicaJuan VargasNo ratings yet

- Practica Libre EspecificacionesDocument15 pagesPractica Libre EspecificacionesAlexandre Pérez ReinaNo ratings yet

- Practical Sockets Practice C and PythonDocument7 pagesPractical Sockets Practice C and PythonAlexandre Pérez ReinaNo ratings yet

- Comunicación Técnica RFEBMDocument24 pagesComunicación Técnica RFEBMAlexandre Pérez ReinaNo ratings yet

- Teoría EC T1 AmplificacionDiscreta Transparencias v51Document88 pagesTeoría EC T1 AmplificacionDiscreta Transparencias v51Alexandre Pérez ReinaNo ratings yet

- S3GG CSSDocument38 pagesS3GG CSSAlexandre Pérez ReinaNo ratings yet

- S2GP HTML CssDocument8 pagesS2GP HTML CssAlexandre Pérez ReinaNo ratings yet

- Clínic Sobre Defensas Abiertas y Ataque A Defesas Abiertas. Barcenas, Román, Cuesta y AntónDocument80 pagesClínic Sobre Defensas Abiertas y Ataque A Defesas Abiertas. Barcenas, Román, Cuesta y AntónJordi Cañadas LopezNo ratings yet

- Comunicación Técnica 225-226Document20 pagesComunicación Técnica 225-226Alexandre Pérez ReinaNo ratings yet

- Asignatura Metodología de La EnseñanzaDocument87 pagesAsignatura Metodología de La EnseñanzaAlexandre Pérez Reina100% (1)

- CT286-AEBM - Construccion Ataque Posicional-Francisco AvilaDocument10 pagesCT286-AEBM - Construccion Ataque Posicional-Francisco AvilaAlexandre Pérez ReinaNo ratings yet

- Ataque Posicional. Manolo LagunaDocument28 pagesAtaque Posicional. Manolo LagunaJordi Cañadas LopezNo ratings yet

- Ataque Posicional. Manolo LagunaDocument28 pagesAtaque Posicional. Manolo LagunaJordi Cañadas LopezNo ratings yet

- Comunicación Técnica 255-256Document24 pagesComunicación Técnica 255-256Alexandre Pérez ReinaNo ratings yet

- CT286-AEBM - Construccion Ataque Posicional-Francisco AvilaDocument10 pagesCT286-AEBM - Construccion Ataque Posicional-Francisco AvilaAlexandre Pérez ReinaNo ratings yet

- El Deporte Como Ocupación Voluntaria en ColegiosDocument2 pagesEl Deporte Como Ocupación Voluntaria en ColegiosAlexandre Pérez ReinaNo ratings yet

- Dialnet Analisis de Los Diferentes Modelos de Entrenamiento ParaP 4375000Document10 pagesDialnet Analisis de Los Diferentes Modelos de Entrenamiento ParaP 4375000Alexandre Pérez ReinaNo ratings yet

- Preparación Física en Equipos de BaseDocument8 pagesPreparación Física en Equipos de BasepfbalonmanoNo ratings yet

- Preparación Física en Equipos de BaseDocument8 pagesPreparación Física en Equipos de BasepfbalonmanoNo ratings yet

- Contraataque y Balance Defensivo Mediante Juegos-Jorge DueñasDocument3 pagesContraataque y Balance Defensivo Mediante Juegos-Jorge DueñasJordi Cañadas LopezNo ratings yet

- Preparación Física en Equipos de BaseDocument8 pagesPreparación Física en Equipos de BasepfbalonmanoNo ratings yet

- Fuerza Balonmano FSVDocument5 pagesFuerza Balonmano FSVpfbalonmanoNo ratings yet

- Teoría y Práctica Del EntrenamientoDocument1 pageTeoría y Práctica Del EntrenamientoAlexandre Pérez ReinaNo ratings yet

- 4 Diseño Tareas Entrenamiento Deportes EquipoDocument72 pages4 Diseño Tareas Entrenamiento Deportes EquipoPaulo Camelo100% (1)

- Tema 7 Punt ErosDocument59 pagesTema 7 Punt ErosAlexandre Pérez ReinaNo ratings yet

- CT279-AEBM - Inferioridades Ofensivas Alemania 2007-Alejandro LopezDocument7 pagesCT279-AEBM - Inferioridades Ofensivas Alemania 2007-Alejandro LopezAlexandre Pérez ReinaNo ratings yet

- Balonmano PlayaDocument24 pagesBalonmano PlayaMladen ParadžikNo ratings yet

- Contraataque y Balance Defensivo Mediante Juegos-Jorge DueñasDocument3 pagesContraataque y Balance Defensivo Mediante Juegos-Jorge DueñasJordi Cañadas LopezNo ratings yet

- Contraataque y Balance Defensivo Mediante Juegos-Jorge DueñasDocument3 pagesContraataque y Balance Defensivo Mediante Juegos-Jorge DueñasJordi Cañadas LopezNo ratings yet

- Ataque Posicional. Manolo LagunaDocument28 pagesAtaque Posicional. Manolo LagunaJordi Cañadas LopezNo ratings yet

- Lectura 5. Los Sofistas y SócratesDocument2 pagesLectura 5. Los Sofistas y SócratesItaty BenalcázarNo ratings yet

- Teoría Pesimista y La Conducta Del SujetoDocument9 pagesTeoría Pesimista y La Conducta Del Sujetopako222No ratings yet

- Factores de Reducción y JustificaciónDocument4 pagesFactores de Reducción y JustificaciónAlan Recalde100% (2)

- Ensayo de La Pelicula Yo Nena, Yo PrincesaDocument1 pageEnsayo de La Pelicula Yo Nena, Yo PrincesaDark SosaNo ratings yet

- Borrador Proyecto Integrador M19Document6 pagesBorrador Proyecto Integrador M19salomon a mNo ratings yet

- La Justicia Como ResultadoDocument3 pagesLa Justicia Como ResultadoMiguel Esteban FernándezNo ratings yet

- Opciones Reales y Flexividad EmpresarialDocument2 pagesOpciones Reales y Flexividad EmpresarialYaMi DarkNo ratings yet

- Definición de ReglaDocument4 pagesDefinición de ReglaAndres Valderas RosasNo ratings yet

- SoftwareNC500 PDFDocument372 pagesSoftwareNC500 PDFJorge Fernández GonzálezNo ratings yet

- Actividad 4Document3 pagesActividad 4Eddy Antonio AmbrosioNo ratings yet

- La Tierra Es Plana de Thomas Friedman Resumen Del LibroDocument6 pagesLa Tierra Es Plana de Thomas Friedman Resumen Del Librowillychavez26No ratings yet

- 3A Secundaria-Balotario de AlgebraDocument1 page3A Secundaria-Balotario de AlgebraDoris ZeladaNo ratings yet

- Une 15008Document41 pagesUne 15008Franco MenconiNo ratings yet

- EscoliosisDocument46 pagesEscoliosiscecijo0% (1)

- Cuestionario de Redes 1,2,3Document6 pagesCuestionario de Redes 1,2,3Manuel Gonzales VelazcoNo ratings yet

- Cordillera Oriental y Sierras SubandinasDocument3 pagesCordillera Oriental y Sierras SubandinasLeoNo ratings yet

- TA.2.4 - Sesión Sobre Protocolos de Atención A La Violencia y en El Uso Del Portal SiseVe para Directivos y DocentesDocument16 pagesTA.2.4 - Sesión Sobre Protocolos de Atención A La Violencia y en El Uso Del Portal SiseVe para Directivos y DocentesIsmael Fernando Avalos RojasNo ratings yet

- Autores Varios - Hegel. La Odisea Del Espiritu PDFDocument321 pagesAutores Varios - Hegel. La Odisea Del Espiritu PDFJorge A YágüezNo ratings yet

- EpistemologiaDocument11 pagesEpistemologiaKatherin RomeroNo ratings yet

- Formato InduccionDocument24 pagesFormato InduccionHECTOR100% (1)

- GUIA2MATE4Document167 pagesGUIA2MATE4Angel BGNo ratings yet

- Nirvana - Nevermind (Guitar Songbook)Document3 pagesNirvana - Nevermind (Guitar Songbook)Stone age0% (2)

- Servicio de Jardineria - Resumen EjecutivoDocument32 pagesServicio de Jardineria - Resumen EjecutivoEco Garden Pinamar0% (1)

- Systematic Layout PlanningDocument7 pagesSystematic Layout PlanningCesar Andres Sanchez InsignaresNo ratings yet

- Trabajo Orientacion VocacionalDocument9 pagesTrabajo Orientacion Vocacional9jznfhkhyrNo ratings yet

- Desconexión Moral PresentaciónDocument16 pagesDesconexión Moral PresentaciónItzel CardenasNo ratings yet

- Factores Internos y Externos Presentes en Los Procesos de Enseñanza y Aprendizaje de La Matemática y de La LectoescrituraDocument8 pagesFactores Internos y Externos Presentes en Los Procesos de Enseñanza y Aprendizaje de La Matemática y de La LectoescrituraSoledad HuánucoNo ratings yet

- Impacto AmbientalDocument55 pagesImpacto AmbientalAnonymous g1AD9ONo ratings yet

- Art. 12 La Comunicación en Grupos Pequeños.Document3 pagesArt. 12 La Comunicación en Grupos Pequeños.Edu Yitzhak Mu Mdrgon0% (1)

- Unidad Didactica y Secuencia Didactica - Nivel SecundarioDocument11 pagesUnidad Didactica y Secuencia Didactica - Nivel SecundarioYami QuirogaNo ratings yet