Professional Documents

Culture Documents

Madan H R: Phone - +91 81090 34545 / +91 90607 34545 E-Mail

Uploaded by

Madan R HonnalagereOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Madan H R: Phone - +91 81090 34545 / +91 90607 34545 E-Mail

Uploaded by

Madan R HonnalagereCopyright:

Available Formats

Madan H R

Phone +91 81090 34545 / +91 90607 34545

E-Mail madan.shaanbhog@gmail.com

Summary

Senior Consultant to Vice-Chancellor

-Chhattisgarh Swami Vivekanand Technical University, Bhilai

(Feb 2014 Till date)

Assisting the Honble Vice-Chancellor in Academic and Administrative activities

Involved in revamping of Research Cell of the University

Instrumental in getting assistance of 40 Galileo Gen II Microcontroller Kits from Intel India Higher Education

and in organizing training programs

B M S Institute of Technology, Bangalore

- Assistant Professor

Department of Electronics and Communication Engineering

(July 2013 to Jan 2014)

Responsibilities

Teaching, preparation of Lab manuals

Residential Warden, BMSIT Boys Hostel

Accomplishments

Guided seven academic projects in a short span of one semester.

Involved in execution of MoUs with Industries and educational institutions/universities (Executed 13 MoUs).

Assisting Chief Mentor of the Institute in administrative and research related matters

Served as Residential Warden at BMSIT Hostel.

Sorted out many issues relating to indiscipline and chaos and brought discipline in the college hostel.

Have a very good rapport with students who are still in communication, executing academic and research

projects under my guidance

Mentoring students in executing academic and research projects

Karnataka State Higher Education Council, Government of Karnataka - Coordinator, (On deputation

from Tumkur University)

(May 2013 June 2013)

Responsibilities

Coordination of RUSA activities

To assist the Vice-Chairman, Karnataka State Higher Education Council, Government of Karnataka

Accomplishments

Was coordinating with universities and higher education institutions across the state

Played a key role in bringing out VISION 2020 book published by Karnataka State Higher Education

Council

Was responsible in organizing 15 national seminars and conferences

Organized a seminar on Rashtriya Ucchatar Shiksha Abhiyan (RUSA)

Tumkur University - Coordinator for Center for VLSI Design (CVLSID),

Intel Embedded System Design laboratory

(November 2012 April 2013)

Responsibilities

Establishment of Center for VLSI Design Research center and Intel Embedded System Design Laboratory

Accomplishments

With the support of Honble Vice-Chancellor, established Center for VLSI Design (CVLSID)

Established Intel embedded System Design Laboratory sponsored by Intel India Higher education

Was instrumental in designing MSc in VLSI & Embedded System Design and MSc in Digital Design course

Guest LecturerDepartment of Electronics, University College of Science,

Tumkur University (August 2011 - October 2012) Promoted as Coordinator for Intel laboratory

in November 2012

Involved in teaching B.Sc PME Students

Was guiding students in final semester academic projects

Was a member of Organizing Committee in organizing National Conference in Recent Trends in

Communication Systems

RV College of Engineering - Teaching Assistant Department of ECE, RV College of Engineering,

Bengaluru

(October 2008 - August 2011)

Departmental Placement Coordinator for the academic year 2010-2011

Involved in the execution of two funded research projects

1. Project Name

:Real time rudder actuation system of autonomous ship

Client

: Naval Research Board

Duration

: 24 months

Role

: Co-principal Investigator

1. Project Name

: Power Optimization in underwater Ad Hoc Sensor Networks

Client

: Naval Research Board

Duration

: 24 months

Role

: Co-principal Investigator

100% result in all the subjects taught (theories and labs)

Was the departmental placement coordinator in the academic year 2010-11

Lecturer - MN Degree College, Bengaluru

(July 2008 - Oct 2008)

Teaching Basic Electronics and Basics of Computer Programming to BCA students

Project 1

Project Name

: Characterization of Reversible Gates

Planned Duration

: 10 months

Role

: Designer

Objectives of project

Characterize Reversible gates and to include the same in VLSI tools and execute the following:

Understanding Reversible Logic Design

Study and Analysis of Reversible circuits and Reversible gates

To learn tools that supports circuit characterization like LIBERTY.NCX supported by Synopsys

To characterize Reversible gates using tool/s that supports circuit characterization like LIBERTY.NCX

(To verify the same and add them to VLSI tools such as Cadence and Synopsys based tools)

Scope of proposed work

Design of Ideally Zero power dissipating Circuits using VLSI tools like Synopsys and Cadence based tools

To familiarize Reversible circuits (Zero Power Dissipating Circuits) to VLSI Designers

Summary of the proposed research:

Learning Circuit Characterizing tools like LIBERTY.NCX

Characterize Reversible gates which ideally dissipates zero power

Adding the same models or symbols to VLSI tools; advantage: Easier Design of Zero Power Dissipating Circuits

Necessity and advantages: Planned models / gates will be

More robust

Reliable

Flexible

Consumes very less power and

Ideally dissipates zero power.

Test and Validation includes Simulation considering all Variation Corners and dynamics.

Project 2:

Project Name

: Design and performance comparison of 6T, 8T and 9T SRAM cells

Abstract

This thesis explores the analysis and comparative study of SRAMs, focusing on the important parameters like static

noise margin (SNM), read and write noise margin, read and write delay, data retention voltage, read and write

stability and leakage current.

Duration

: One Year

Place of work

: RVCenter for Cognitive Technologies (RVCCT), Bangalore

Project 3:

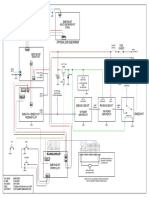

Project Name

: Automation of Railway Department using Embedded Microcontroller

Abstract

Project implements the Wireless technique and provides the easiest automation to the railway department. This is

basically made of five sub-projects, whose combination makes the railway automation still stronger.

Wireless Signaling System

Anti-collision System

Automatic Gate Control

Train Approaching Indicator

Signaling at track junction:

Main features of the project

Simple in design, Robust and highly reliable

Low power consumption, and compact size

Remote signaling lights can be monitored using only one Receiver.

High reliability, due to the usage of power semiconductor devices

Greater control range due the usage of Frequency Modulation.

Devices monitored simultaneously from a remote area ('line-of-sight arrangement not required)

Place of work

: Dr. AIT, Bangalore

Duration

: 3 months

Role

: Developer

Academic Profile

Examination

University

(Ph.D)

Tumkur University

(MBL)

National Law School of India, Bangalore

(2012 - )

Pursuing

(2013 - )

Sikkim Manipal University, Bengaluru

2012

RVCCT, Mangalore University

2010

VisvesvarayaTechnological University,

Belgaum

2008

MBA

(PROJECT MANAGEMENT)

MS

(ASIC DESIGN)

Bachelor of Engineering (ECE)

Year

Pursuing

Areas of Interest:

Reconfigurable computing

Low Power VLSI (Reversible Logic)

Circuit Characterization

SoC and NoC (system on Chip and Network on Chip)

Semiconductor memories

VLSI and Embedded system Design

Microprocessors and Microcontrollers

Digital Communication System

Wired and Wireless Communication

Publications

Papers Published in Refereed International Journals :

International Journals

1. Comparative Study of DRAM for High & Low Power CMOS process technology, M. Akshay Bhounsley1, H.

R. Madan2, H. V. Ravish Aradhya3, V. Ebenezer4, International Journal of Science Research Volume 01, Issue

03, December 2012, pp. 137-138

2. Considerations Of FinFET Based 6T SRAM Cells, M. Girish Kumar1 , H. R. Madan2, H. V. Ravish

Aradhya3 , VEbenezer4, International Journal of Science Research Volume 01, Issue 03, December 2012, pp.

134-136

3. Comparative Study of SRAM & DRAM for various CMOS process technology, M. Akshay Bhounsley11, H. R.

Madan2, H. V. RavishAradhya3, V. Ebenezer4, International Journal of Science Research Volume 01, Issue 03,

December 2012, pp. 141-143

4. Design and Performance Analysis of 8T SRAM for Different Scaled Technologies, M. F. Md.Luqman1, H. R.

Madan2, H. V.RavishAradhya3, K.Suresh4, International Journal of Science Research Volume 01, Issue 03,

December 2012, pp. 151-153

5. Design and Optimization of Reversible Carry Look Ahead Adder Circuit, Abhijith A Bharadwaj, Madan H R,

Keith Saures, H V Ravish Aradhya, International Journal of Engineering and Science Invention (IJESI), April 2014,

Received Best paper award

6. Bio-inspired route for the synthesis of spherical shaped MgO: Fe3+ nanoparticles: Structural,

Photoluminescence and Photocatalytic investigation, Madan H R, S C Sharma, H Nagabhushana,

Darukaprasad, Suresh D, Spectrochemica Acta, Molecular and Biomolecular Spectroscopy, Elsevier, Submitted

for publication October 2014, Under review, Impact Factor: 2.129

7. Facile Green Fabrication of Nanostructure ZnO Plates, Bullets, Flower, Prismatic tip, Closed pine cone: Their

Antibacterial, Antioxidant, Photoluminescent and Photocatalytic Properties, Madan H R, H Nagabhushana, S C

Sharma, D Suresh, Darukaprasad, S C Prashantha, Y S Vidya, Spectrochemica Acta, Molecular and Biomolecular

Spectroscopy, Elsevier, Submitted for publication, Submitted on December 2014, Under review, Impact

Factor: 2.129

Research Publication under progress

1. Design and optimization of Graphene based SRAM.

Involves designing a 64x8 SRAM using Graphene Nano-Ribbon FETs, at

10nm gate length and evaluation of design parameters such as power

dissipation, various capacitances, noise margin, power-delay product. (PRESENT

STATUS: Work completed. Pending documentation)

2. Design and optimization of Hybrid Reversible Carry look-ahead adder

circuit.

Involves designing a 16 bit Hybrid Carry Look-Ahead adder using reversible

logic in 10nm Graphene FET, Carbon Nano-Tube (CNTFET) andfinFET

technology. Three reversible designs are provided in comparison to the

conventional CMOS design. (PRESENT STATUS: Work completed. Pending

documentation)

3. Design and performance comparison of decomposed 1:32 De-multiplexers

Involves performance (Transistor cost, Power dissipation, input-output delay,

power delay product) comparison of multiple decomposed 1:32 Demultiplexers using Graphene Nano Ribbon FET, CNT-FET and FINFET at

10nm gate length. (PRESENT STATUS: Work completed. Pending

documentation)

4. Design of Graphene based microcontroller.

Involves designing a microcontroller using Graphene Nano-Ribbon FETs, at 10nm

gate length and evaluation

of design parameters such as power dissipation, power-delay product. (PRESENT STATUS:

Work is under

progress).

International Conferences:

1.

FPGA Implementation of SoC using softcore processors and Custom Peripherals, custom instructions for

Robotics and Automation, Anil Kumar D, Madan H R, Research & Reviews: Journal of Embedded System &

Applications, 2321 - 8533 , November 2013, pp. 01-06

National Conferences:

1. Design and Performance Analysis of 6T SRAM for Different Scaled Technologies, Md.Luqman M F,

M.GirishKumar,Madan H.R, H.V. Ravish Aradhya, Dr.K.Suresh, National conference on Recent Trends in

Communication Technology, Vol. no. 01, pp 238 244, Bangalore, January 2012

2. CMOS Realization of Reversible BCD Adder, Girish.R, AkshayBhounsley M, Madan.H.R, Mr.

H.V.RavishAradhya, Mrs. MehrunnisaBegum.S.P, National conference on Recent Trends in Communication

Technology, Vol. no. 01, pp 227 233, Bangalore, January 2012

3. Comparative Study of logic circuits based on MOSFET and FinFET under 32 nm process technology, M

Girish Kumar, Girish R, Madan H R, Mr. H V Ravish Aradhya, Mr.V Ebenezer, National conference on Recent

Trends in Communication Technology, Vol. no. 01, pp 234 237, Bangalore, January 2012

4. Comparative Study of DRAM for various CMOS process technology, AkshayBhounsley M, M D Luqman M F,

Madan H R, Mr. H V Ravish Aradhya, Mr. V Ebenezer, National conference on Recent Trends in Communication

Technology, Vol. no. 01, pp 245 251, Bangalore, January 2012

5. Cloud Security- Grand challenge for adoption of Cloud Computing, ShreyasHirethota, Srinvasa Murthy,

Madan H R, Sheshadri N, National conference on Recent Trends in Communication Technology, Vol. no. 01, pp

221 226, Bangalore, January 2012

6. CMOS Implementation of Reversible Comparators, AkshathaShrinivas, ShreyasHirethota, Madan H R,

Ravish Aradhya H V, National conference on Recent Trends in Communication Technology, Vol. no. 01, pp 252

258, Bangalore, January 2012

7. Overview of Reversible Logic, Saranya S, Ravi Raj Singh, Soumya, SapnaUpadhyay, Madan H R, National

Conference on Emerging Trends in VLSI & Embedded Systems, ISBN 978-81-928203, Oct 2013

8. Design, Analysis and Performance comparison of Finfet based and MOSFET based Carry look-ahead adder,

Madan H R, Arjun Krishna Murthy, National Symposium on Instrumentation (NSI -38) , BVB college of

Engineering,Hubli, , Oct-2013

Member

1.

Expert Committee Member, Institute of Academic and Research Council

2.

Member, Editorial Board,International Journal of Advance Research in Science and Engineering

Expert Lectures Delivered

1.

Recent Trends in VLSI Designs, Advances in Engineering & Technology (AET-2013),Institute of

Academic and Research Council, Bangalore, 2013

Awards and recognitions

Reviewer, NCKITE-2015 April 2015

1st prize -National Level Business Model Competition, RVIM, Bangalore, April 2011

1st prize in national level Science Fair, Allahabad, Nov 2001.

Best explanation award in the zonal level science fair, Pondicherry, Nov 2001.

1st prize in Zonal Level Science fairs, Pondicherry and Tirupathi, 1999 and 2000.

1st prize in state level Science Fairs thrice, 1999, 2000 and 2001.

1st prize in district level science fairs thrice, 1999, 2000 and 2001.

Taluk level SSLC topper award, BramhanaSabha, Maddur

Personal Profile:

Father

Date of Birth

RAMAMURTHY

23-June-1986

Permanent Address

:

Madan H R S/O Ramamurthy

No. 386, S I Honnalagere (Post),

Via Bharathi Nagar, C A KereHobli, MaddurTaluk,

Mandya District, Karnataka 571422

Present Address

Madan H R

No. QA 06, Behind Hanuman Mandir,

Near TV Tower, Anupamnagar, Raipur (C.G) 492 007

Can Exchange Ideas In

References

English, Kannada and Hindi.

:

Only on request

Passport

PAN

Date

January 2015

Place

Raipur

L7038432

AEGPH2720E

( Madan H R )

You might also like

- Logic Made Easy (2004)Document260 pagesLogic Made Easy (2004)api-3830039100% (28)

- Audit Iso9001 2015 ChecklistDocument23 pagesAudit Iso9001 2015 ChecklistLa Metalurgica100% (5)

- (1810) CV Aw18Document15 pages(1810) CV Aw18augiegmailNo ratings yet

- Veeru Assoc Prof ResumeDocument4 pagesVeeru Assoc Prof ResumeveerusiteNo ratings yet

- Electronic Labs 1-15Document38 pagesElectronic Labs 1-15Fexter Pérez100% (2)

- 76 - 8271423M - B FGTM-MDocument32 pages76 - 8271423M - B FGTM-MHamza_yakan967No ratings yet

- Onkyo Onwer's Manual TX-SR803 703 PDFDocument96 pagesOnkyo Onwer's Manual TX-SR803 703 PDFVidiNo ratings yet

- Quality Manual Tarento - V2.2Document36 pagesQuality Manual Tarento - V2.2Madan R Honnalagere100% (1)

- Artificial Intelligence for Future Generation RoboticsFrom EverandArtificial Intelligence for Future Generation RoboticsRabindra Nath ShawRating: 5 out of 5 stars5/5 (1)

- Project Plan For Implementation of The Quality Management SystemDocument6 pagesProject Plan For Implementation of The Quality Management SystemTomas MoralesNo ratings yet

- Power System Small Signal Stability Analysis and ControlFrom EverandPower System Small Signal Stability Analysis and ControlRating: 5 out of 5 stars5/5 (2)

- Dr. M S ShashidharaDocument10 pagesDr. M S ShashidharamsshashidharaNo ratings yet

- Arunkumart@vit - Ac.in: Doctoral Degree: PH.D in Computer Science (April 2005)Document7 pagesArunkumart@vit - Ac.in: Doctoral Degree: PH.D in Computer Science (April 2005)ArunNo ratings yet

- Rajeshwar ProfileDocument2 pagesRajeshwar ProfileengineeringwatchNo ratings yet

- Curriculum 201905 DrGKSV2Document8 pagesCurriculum 201905 DrGKSV2gowdamandaviNo ratings yet

- Ranjeet Kumar CVDocument7 pagesRanjeet Kumar CVJust Another UserNo ratings yet

- MNIT Proposal 2012Document4 pagesMNIT Proposal 2012Amlan ChakrabartiNo ratings yet

- Vaibhav Prakash (No Number)Document1 pageVaibhav Prakash (No Number)api-249472163No ratings yet

- Name: Sagar Yeruva Designation: Associate Professor Department: Computer Science and EngineeringDocument4 pagesName: Sagar Yeruva Designation: Associate Professor Department: Computer Science and EngineeringengineeringwatchNo ratings yet

- Manodipan Sahoo: ObjectiveDocument14 pagesManodipan Sahoo: ObjectiveSai Tejesh Reddy GurijalaNo ratings yet

- Linear Integrated CircuitsDocument169 pagesLinear Integrated Circuitsghatiyashivani48No ratings yet

- Rama KantDocument4 pagesRama KantSalman QureshiNo ratings yet

- Tak 2021Document7 pagesTak 2021ArunNo ratings yet

- SwatiDocument5 pagesSwatinabuNo ratings yet

- Electrical Engineering Department Motilal Nehru National Institute of Technology AllahabadDocument12 pagesElectrical Engineering Department Motilal Nehru National Institute of Technology AllahabadAakash PathakNo ratings yet

- Thesis For M.tech VlsiDocument6 pagesThesis For M.tech VlsiCollegePaperWritingServicesUK100% (2)

- Resume ECE ProfessorDocument5 pagesResume ECE ProfessorPragya Srivastava AgrawalNo ratings yet

- William Johnson Trichy 19.05 YrsDocument14 pagesWilliam Johnson Trichy 19.05 Yrsvenkiscribd444No ratings yet

- CV DEVSKiranKumar Oct'22Document4 pagesCV DEVSKiranKumar Oct'22KiranNo ratings yet

- Santosh ResumeDocument0 pagesSantosh ResumeengineeringwatchNo ratings yet

- College ResumeDocument3 pagesCollege Resumeವಿಶ್ವನಾಥ ಸಿNo ratings yet

- Final Year Project ReportDocument30 pagesFinal Year Project ReportRahul PatilNo ratings yet

- Augie Widyotriatmo, ST., MT., PH.DDocument13 pagesAugie Widyotriatmo, ST., MT., PH.DaugiegmailNo ratings yet

- Dr. Vikas Maheshwari,: Research Activity: Most of My Research Area Is Focused On VLSI Global Interconnects HavingDocument2 pagesDr. Vikas Maheshwari,: Research Activity: Most of My Research Area Is Focused On VLSI Global Interconnects Havingmaheshwarivikas1982No ratings yet

- Siddu ResumeDocument4 pagesSiddu Resumenalluri_milkyNo ratings yet

- CSE Sample RecordDocument65 pagesCSE Sample RecordKavinNo ratings yet

- Anshul Singh - 200631002 - ECDocument4 pagesAnshul Singh - 200631002 - ECSumit RajNo ratings yet

- Bachelor of Engineering: Green House Monitoring Using Sensor NetworkDocument4 pagesBachelor of Engineering: Green House Monitoring Using Sensor NetworkChirag MistryNo ratings yet

- Verilog HDL Lecture Notes: Design Digital Systems Using Xilinx ToolsDocument124 pagesVerilog HDL Lecture Notes: Design Digital Systems Using Xilinx Toolsrachitha sNo ratings yet

- Narasinga Rao Miniskar, PH.D.: M Iniskarnr@ornl - GovDocument3 pagesNarasinga Rao Miniskar, PH.D.: M Iniskarnr@ornl - GovScottNo ratings yet

- CVSVD 16.1.9Document24 pagesCVSVD 16.1.9ArulNo ratings yet

- Ercvnov 22 2012Document4 pagesErcvnov 22 2012Rajesh BathijaNo ratings yet

- Electrical Engineer Seeks Graduate StudiesDocument2 pagesElectrical Engineer Seeks Graduate StudiesIslam SahafayatNo ratings yet

- CV Vaibhav ChughDocument2 pagesCV Vaibhav ChughArnab DuttaNo ratings yet

- AJS - NJS Manual - 1Document45 pagesAJS - NJS Manual - 1darshan.vvbmaNo ratings yet

- Arushi Sonkhya SOPDocument2 pagesArushi Sonkhya SOPHarshit SinghalNo ratings yet

- Arpit NandDocument3 pagesArpit NandAnkit GuptaNo ratings yet

- Vlsi Lab Manual r16Document95 pagesVlsi Lab Manual r16chandra kiranNo ratings yet

- Dr. Mohankumar N Resume - 4jan2023Document8 pagesDr. Mohankumar N Resume - 4jan2023Mohan KumarNo ratings yet

- Hfss Mini ProjectDocument19 pagesHfss Mini Projectharsha vardhanNo ratings yet

- IITD BrochureDocument10 pagesIITD Brochurejitu_4No ratings yet

- Chetan NaikJDocument6 pagesChetan NaikJChetan Naik massandNo ratings yet

- RESUME Sukhbinder RaitDocument4 pagesRESUME Sukhbinder RaitAnushree AnilNo ratings yet

- ManasPaldhe CVDocument4 pagesManasPaldhe CVManas PaldheNo ratings yet

- Ns 2 CbeDocument2 pagesNs 2 CbeVelmani RamasamyNo ratings yet

- Su Semi - MergedDocument34 pagesSu Semi - MergedSammed HuchchannavarNo ratings yet

- Two Days Hands-On Workshop: Computer Society of India, Hyderabad ChapterDocument2 pagesTwo Days Hands-On Workshop: Computer Society of India, Hyderabad ChapterSathwika KistipatiNo ratings yet

- Vchugh ResumeDocument2 pagesVchugh ResumeVaibhav ChughNo ratings yet

- STTP OF CE On ETABSDocument3 pagesSTTP OF CE On ETABSreshmaNo ratings yet

- Indrajit De: Educational BackgroundDocument3 pagesIndrajit De: Educational BackgroundengineeringwatchNo ratings yet

- Curriculum Vitae - RadikaDocument3 pagesCurriculum Vitae - RadikaradikahendryNo ratings yet

- Guide Profile Format: ST STDocument3 pagesGuide Profile Format: ST STbrm1shubhaNo ratings yet

- Muhammad Awais: EducationDocument4 pagesMuhammad Awais: EducationsajidNo ratings yet

- Mohit Verma: ContactDocument4 pagesMohit Verma: ContactmovermNo ratings yet

- Annexure 1Document3 pagesAnnexure 1gaurav maithaniNo ratings yet

- Final Report-1Document29 pagesFinal Report-1Abiraja BNo ratings yet

- Latex Sample ResumeDocument7 pagesLatex Sample ResumeDil KumNo ratings yet

- ISO Awareness GuideDocument17 pagesISO Awareness GuideMadan R HonnalagereNo ratings yet

- Tags Are Markers To Highlight Notable Revisions in TheDocument1 pageTags Are Markers To Highlight Notable Revisions in TheMadan R HonnalagereNo ratings yet

- ISO Awareness 2014Document20 pagesISO Awareness 2014Madan R HonnalagereNo ratings yet

- Hari VayustutiDocument10 pagesHari VayustutiSanjeev Kumar100% (1)

- Quality Objectives For TarentoDocument6 pagesQuality Objectives For TarentoMadan R HonnalagereNo ratings yet

- Quality Objectives For TarentoDocument6 pagesQuality Objectives For TarentoMadan R HonnalagereNo ratings yet

- Metrics Collected in TarentoDocument12 pagesMetrics Collected in TarentoMadan R HonnalagereNo ratings yet

- ISO Awareness 2014Document20 pagesISO Awareness 2014Madan R HonnalagereNo ratings yet

- Metrics Collected in TarentoDocument12 pagesMetrics Collected in TarentoMadan R HonnalagereNo ratings yet

- Metrics Collected in TarentoDocument12 pagesMetrics Collected in TarentoMadan R HonnalagereNo ratings yet

- ISO Awareness GuideDocument17 pagesISO Awareness GuideMadan R HonnalagereNo ratings yet

- Annexures To Letter No F.No. 1-30-2020-KT Dated 26-6-2020 On DIKSHA - Content Creation Curation and Filling Gaps by STATES UTsDocument9 pagesAnnexures To Letter No F.No. 1-30-2020-KT Dated 26-6-2020 On DIKSHA - Content Creation Curation and Filling Gaps by STATES UTsMadan R HonnalagereNo ratings yet

- Taxonomy v101 IEEE PDFDocument67 pagesTaxonomy v101 IEEE PDFmarthaNo ratings yet

- Partnership Deed - AbcDocument7 pagesPartnership Deed - AbcMadan R HonnalagereNo ratings yet

- BMPaymentReceipt 4808253 3304781Document1 pageBMPaymentReceipt 4808253 3304781AviNo ratings yet

- Certificate For Madan HR For - Check Your Awareness On PayscaleDocument1 pageCertificate For Madan HR For - Check Your Awareness On PayscaleMadan R HonnalagereNo ratings yet

- Certificate For True For - PDFDocument1 pageCertificate For True For - PDFMadan R HonnalagereNo ratings yet

- Christopher Saint, Judy Saint-IC Mask Design - Essential Layout TechniquesDocument481 pagesChristopher Saint, Judy Saint-IC Mask Design - Essential Layout TechniquesPraveenNo ratings yet

- Certificate For True ForDocument1 pageCertificate For True ForMadan R HonnalagereNo ratings yet

- BMPaymentReceipt 4808253 3304781Document1 pageBMPaymentReceipt 4808253 3304781AviNo ratings yet

- BiodataDocument1 pageBiodataMadan R HonnalagereNo ratings yet

- IETE Journal paper template guidelinesDocument7 pagesIETE Journal paper template guidelinesMadan R HonnalagereNo ratings yet

- Operational Manual: Operational Steps Involved To Fill Institute's Registration Form For AY 2019-20Document9 pagesOperational Manual: Operational Steps Involved To Fill Institute's Registration Form For AY 2019-20Madan R HonnalagereNo ratings yet

- User Access - KADocument2 pagesUser Access - KAMadan R HonnalagereNo ratings yet

- Dr. Sandeep Malik's Educational Background and Career HighlightsDocument1 pageDr. Sandeep Malik's Educational Background and Career HighlightsMadan R HonnalagereNo ratings yet

- How To Write An Author Bio & Why (With Examples)Document21 pagesHow To Write An Author Bio & Why (With Examples)Madan R HonnalagereNo ratings yet

- Guide to Using the Satmotion Pocket App for PCDocument25 pagesGuide to Using the Satmotion Pocket App for PCHans Michael Estay JaraNo ratings yet

- Ambient Backscatter PDFDocument2 pagesAmbient Backscatter PDFAlekso GjakovskiNo ratings yet

- ATA 44 - Cabin Systems (Mike Tooley)Document16 pagesATA 44 - Cabin Systems (Mike Tooley)Jagbir SinghNo ratings yet

- Computer Engineering Study Plan PDFDocument2 pagesComputer Engineering Study Plan PDFDorian GrayNo ratings yet

- Revised EEE 2-2Document1 pageRevised EEE 2-2Mohammad AliNo ratings yet

- Eme158 Kit Eme158 Kit: Audio Subcarrier Kit 5.5Mhz Audio Subcarrier Kit 6.5MhzDocument1 pageEme158 Kit Eme158 Kit: Audio Subcarrier Kit 5.5Mhz Audio Subcarrier Kit 6.5MhzDUDULENo ratings yet

- JBL Vertec v4 DBX Driverack 4800 Preset SummaryDocument3 pagesJBL Vertec v4 DBX Driverack 4800 Preset Summaryulisses0% (1)

- AEM Bluetooth Printer - PpsDocument13 pagesAEM Bluetooth Printer - PpsNeeraj AggarwalNo ratings yet

- 1st To 5th Generation History of ComputerDocument11 pages1st To 5th Generation History of ComputerjanNo ratings yet

- The History of MMDSDocument4 pagesThe History of MMDSAvril BannisterNo ratings yet

- SDSV+ Build Guide PDFDocument10 pagesSDSV+ Build Guide PDFAndrii Y KuzmenkoNo ratings yet

- Punjab Group of Colleges 1st Quarter Test for Computer Science Inter Part-IDocument2 pagesPunjab Group of Colleges 1st Quarter Test for Computer Science Inter Part-IQais KaisraniNo ratings yet

- Digital Electronics Chapter 3Document39 pagesDigital Electronics Chapter 3Pious TraderNo ratings yet

- HM-2700 - Esfuerzo Cortante ResidualDocument2 pagesHM-2700 - Esfuerzo Cortante ResidualsandrexbjNo ratings yet

- Enerlux TDocument3 pagesEnerlux TrazvansasuNo ratings yet

- Aruba Ap92 DatasheetDocument4 pagesAruba Ap92 DatasheetCoreyNo ratings yet

- SP3-GT35 HMI - Human Machine Interface: FeaturesDocument2 pagesSP3-GT35 HMI - Human Machine Interface: FeaturesSEBATELEC SEBATELECNo ratings yet

- Model Answers - HW1Document6 pagesModel Answers - HW1Triệu HảiNo ratings yet

- RF Plan Release 3.0 Release NotesDocument6 pagesRF Plan Release 3.0 Release NotesMichele PastoreNo ratings yet

- 06 June 1990Document108 pages06 June 1990Monitoring TimesNo ratings yet

- Eeg1Document3 pagesEeg1ronaldoa9No ratings yet

- Senring H Series SlipRing Catalog PDFDocument74 pagesSenring H Series SlipRing Catalog PDFremeenNo ratings yet

- Agilent 8902A Measuring Receiver: Product NoteDocument8 pagesAgilent 8902A Measuring Receiver: Product Notejcfermosell100% (1)

- VumetroDocument28 pagesVumetroJavier Gallegos IbarraNo ratings yet

- 4017 & 4026Document3 pages4017 & 4026Ronny SinagaNo ratings yet

- LeafletDocument2 pagesLeafletCarlos Jose Sanchez EsparzaNo ratings yet

- Anyhertz Drive ShenzenDocument5 pagesAnyhertz Drive ShenzenJose EspinozaNo ratings yet