Professional Documents

Culture Documents

Multiplex Eo

Uploaded by

Tegui RossCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Multiplex Eo

Uploaded by

Tegui RossCopyright:

Available Formats

Sistemas Digitales - 66.

17

Trabajo Practico 1

Contador BCD de 4 dgitos con salida a display 7 segmentos

Sistemas Digitales - 66.17

Facultad de Ingeniera - UBA

1.

Objetivo

El presente Trabajo Pr

actico consta en especificar, dise

nar, describir una arquitectura,

simular, sintetizar e implementar en FPGA un sistema digital para un contador BCD

de 4 dgitos con salida a un display de 7 segmentos.

2.

Especificaciones

1. Implementar en lenguaje descriptor de hardware VHDL: un contador BCD de 4

dgitos y un controlador para un display de 7 segmentos de 4 cifras. El contador

se deber

a incrementar aproximadamente cada 1 segundo.

2. Sintetizar con la herramienta ISE la descripcion de hardware para la FPGA:

Fabricante: Xilinx

Familia: Spartan 3

Modelo: xc3s200

Encapsulado: FT256

Speed: -4

3. Implementar la descripci

on en el kit de desarrollo Spartan-3 Starter Boardde la

empresa digilent.

4. Generar un informe (no m

as de 5 hojas, sin contar el codigo) que incluya:

Diagrama en bloques, entradas y salidas de cada bloque.

Simulaciones (incluyendo algunas capturas de pantalla).

Tabla de resumen de sntesis, detallando: slices, Flip-Flops, LUTs utilizadas, Cantidad de gated-clocks (GCLK) y frecuencia maxima de reloj a la

que es operable el circuito (todos los items, salvo la frecuencia maxima de

reloj, con indicaci

on de porcentajes de utilizacion).

C

odigo fuente VHDL.

3.

Desarrollo

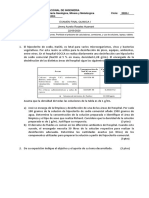

El diagrama en bloques de la arquitectura propuesta se puede observar en la figura 1.

En la misma se reconocen varios elementos, entre ellos:

Contadores

Generador de enable

Figura 1: Diagrama en bloques de la arquitectura propuesta.

Controlador de display 7-segmentos

La idea del trabajo pr

actico es implementar 4 contadores BCD. Estos deberan ser

conectados de forma tal de que generen una cuenta en formato decimal. El contador

poseera una entrada de reset para incializarlo en cero, la cual se implementara utilzando

un boton (pulsador) provisto en el kit de desarrollo. Los 4 contadores alimentaran al

controlador de display 7 segmentos, el cual se encargara de presentar en el display del

kit de desarrollo el valor de la cuenta.

3.1.

Contadores

Deberan contar de 0 a 9. Deben tener una entrada de reset que los ponga a cero y una

entrada de enable. Tendr

an una salida de 4 bits en la cual reflejaran el valor de la cuenta,

como lo muestra la figura 2.

Figura 2: Contador BCD (se instanciar

an 4, como lo muestra la figura 1).

3.2.

Generador de Enable

El objetivo de este bloque es dividir la frecuencia de reloj de la placa de 50MHz a una

frecuencia adecuada para que el contador pueda incrementar su cuenta cada aproximadamente 1 segundo. En la figura 3 se puede observar la forma de onda que tendra la

se

nal. Dicho hardware se puede implementar basandose en un contador.

Figura 3: Generador de pulsos de enable.

3.3.

Controlador de display 7-segmentos

El kit Spartan-3 Starter tiene un display de 7-segmentos de 4 caracteres el cual es

controlado por los pines de entrada/salida de la FPGA.

Como se observa en la figura 4, cada dgito comparte ocho se

nales de contol para encender cada LED individual que corresponde a un segmento del caracter. Cada caracter

tiene un

anodo asociado. Poniendo un 0 en el terminal de la FPGA que se conecta a

ese anodo, se selecciona el caracter a encenderse.

Figura 4: Conexi

on entre los I/Os de la FGPA y el display.

Ejemplo de funcionamiento:

Si se quiere escribir el n

umero 3 en la segunda cifra del display, se deberan ingresar las

se

nales como lo muestra la figura 5.

Figura 5: Estado de las se

nales para encender un 3 en la segunda cifra.

Para que el display pueda presentar los cuatro caracteres, se requiere multiplexar las

Figura 6: Secuencia de encendido de los anodos.

se

nales correspondientes a los puertos a, b, c, d, e, f, g y dp. Para ello, se debe activar

durante un tiempo cada uno de los cuatro anodos del display, como lo muestra la figura

6.

Si se logra encender los

anodos lo suficentemente rapido como para enga

nar al ojo

humano, el individuo que este mirando el display percibira que los cuatro caracteres se

encuentran contnuamente encendidos. Por otro lado, la frecuencia de encendido/apagado de los

anodos no debe ser tan elevada, pues a medida de que aumenta la frecuencia,

aumenta el comportamiento capacitivo de los LEDs que conforman el display. Una frecuencia de unos cientos de Hz se considera adecuada para operar el display.

Se propone entonces, una posible arquitectura para implementar el controlador para el

display de 7 segmentos en la figura 7.

Figura 7: Arquitectura propuesta para el controlador de display 7 segmentos.

Se reconocen varios elementos que conforman el controlador, entre ellos:

Multiplexor (MUX): selecciona cual de las entradas en formato BCD se imprimir

a seg

un lo que indica el contador.

Funcion l

ogica de 4 entradas y 8 salidas: Es la encargada de mapear los

n

umeros en formato BCD a los LEDs que deben encenderse para representar dicho

n

umero.

Funcion l

ogica de 2 entradas y 4 salidas: Es la encargada de seleccionar el

anodo seg

un el valor del contador.

Contador de 2 bits: Es el encargado de ir conmutando el anodo para mantener

los cuatro caracteres del display encendidos. La conmutacion seguira la secuencia

propuesta en la figura 6.

Generador de enable: Genera una se

nal de enable para que la conmutacion de

anodos no sea muy r

apida. (aprox. 1kHz)

Para mas informaci

on se puede consultar el manual de referencia del kit o bien el manual

de referencia del kit Nexys2. En dicho manual (kit de Nexys2 ) se explica el funcionamiento del display de otra placa de desarrollo, el cual es similar al de la placa a ser utilizada

en el trabajo pr

actico. Este material tambien se encuentra disponible en la pagina de

digilent.

4.

Material de apoyo

Para confeccionar el trabajo pr

actico, ademas de la bibliografa de la materia y el material

disponible en la p

agina web de la materia, se puede utilizar:

Archivo board top.vhd disponible en la pagina web de la materia. En dicho

archivo se muestra la implementacion de las asignaciones de pines en la FPGA.

http://www.digilentinc.com/ (pagina web del fabricante del kit).

Libro (optativo)

FPGA PROTOTYPING BY VHDL EXAMPLES - Xilinx Spartan-3 Version

Autor: Pong P. Chu A

no: 2008

Editorial: John Wiley and Sons, Inc., Hoboken, New Jersey.

ISBN 978-0-470-18531-5

5.

5.1.

Consideraciones extras

Modalidad de trabajo

Se recomienda enf

aticamente realizar un testbench (simulacion) por cada descripcion de

hardware a implementar.

Se recomienda tambien probar todo por separado, tanto para las descripciones en VHDL

como para las pruebas con el kit de desarrollo. Una vez que se haya comprobado fehacientemente que cada descripci

on funcione por separado se procede a integrarlas.

5.2.

L

ogica en el camino del reloj

Bajo ning

un concepto se aprobar

a un trabajo practico en el cual haya logica en el camino

del reloj, como lo muestra el ejemplo de la figura 8. En la misma se ve como la se

nal de

reloj, que alimenta al Bloque 1, es una AND entre la se

nal de reloj de la FPGA y

una se

nal denominada a i.

Figura 8: Ejemplo de logica en el camino del reloj.

No utilizar m

as de un dominio de reloj. Tampoco utilizar falling o rising edges del

reloj para lograr sincronizaci

on. Utilizar s

olo uno de los dos flancos en todos los

circuitos sincr

onicos que se implementen.

5.3.

Estilo de codificaci

on

No utilizar se

nales de tipo bit o bit vector. Tampoco utilizar se

nales de tipo inout y/o

buffer o se

nales numericas natural, integer, etc. para puertos de entidades.

5.4.

Forma de evaluaci

on

El informe del trabajo pr

actico se debera entregar antes de la fecha lmite dispuesta en la

pagina web de la materia. Se evaluara individualmente al alumno con el trabajo practico

funcionando y, en base a las preguntas realizadas por el docente, se fijara una nota del

trabajo pr

actico.

You might also like

- P 9Document4 pagesP 9Tegui RossNo ratings yet

- Practica 01Document8 pagesPractica 01Tegui Ross100% (3)

- Practica 3 Lab. Com.1Document6 pagesPractica 3 Lab. Com.1Tegui Ross80% (5)

- Guia para Practica N - 1: Fecha DE Elaboración Nombre DEL LumnoDocument5 pagesGuia para Practica N - 1: Fecha DE Elaboración Nombre DEL LumnoTegui RossNo ratings yet

- 5 Voltimetro LuminosoDocument5 pages5 Voltimetro LuminosoTegui RossNo ratings yet

- Final2020 1q1Document2 pagesFinal2020 1q1MichaelNo ratings yet

- Informe Análisis Microbiológico de FrutasDocument2 pagesInforme Análisis Microbiológico de FrutasPaula EmeryNo ratings yet

- Creatividad DE LA EDUCACIÓN INICIALDocument15 pagesCreatividad DE LA EDUCACIÓN INICIALMarielvis CabezaNo ratings yet

- Los DeterminantesDocument8 pagesLos DeterminantesOmar Edmundo Huaracha VizaNo ratings yet

- Streams Usando BuffersDocument11 pagesStreams Usando BuffersCesar BerrioNo ratings yet

- Instrumento-De-Evaluacion de DesempeñoDocument3 pagesInstrumento-De-Evaluacion de DesempeñoLelin lelon00No ratings yet

- IDENTIFICACIÓN DE FIBRAS TEXTILES TextilesDocument2 pagesIDENTIFICACIÓN DE FIBRAS TEXTILES TextilesMariela HuarachiNo ratings yet

- Antecedentes y Cuadro ComprativoDocument5 pagesAntecedentes y Cuadro ComprativoPamela RoaNo ratings yet

- Guía Metodológica de Educación AmbientalDocument69 pagesGuía Metodológica de Educación AmbientalMariangela PrietoNo ratings yet

- Distema de Educacion Media SuperiorDocument431 pagesDistema de Educacion Media SuperiorCory HessNo ratings yet

- Guia Nacional Oferta Capacitacion 1Document298 pagesGuia Nacional Oferta Capacitacion 1robert10_7No ratings yet

- Formulario Segundo Parcial (Mat-207)Document4 pagesFormulario Segundo Parcial (Mat-207)Javier MillerNo ratings yet

- Linea de Tiempo de La Evaluacion de La Educacion FisicaDocument3 pagesLinea de Tiempo de La Evaluacion de La Educacion FisicaGabriel MontalvanNo ratings yet

- Prototipo y Pruebas - Design ThinkingDocument22 pagesPrototipo y Pruebas - Design Thinkingjehu alanisNo ratings yet

- 5to - Ed - Física - Raúl ValverdeDocument8 pages5to - Ed - Física - Raúl ValverdeJesel NievesNo ratings yet

- Fuentes de Energía y GabinetesDocument6 pagesFuentes de Energía y GabinetesEzequiel KennedyNo ratings yet

- Ra TabuladoDocument1 pageRa TabuladoJulian TorresNo ratings yet

- ApuntesMat024base (Clases) PDFDocument138 pagesApuntesMat024base (Clases) PDFFrancisco Javier100% (1)

- 2.2. Operadores Lógicos y CuantificadoresDocument3 pages2.2. Operadores Lógicos y CuantificadoresWendyNo ratings yet

- SARRIGURENDocument4 pagesSARRIGURENGiulli Arnez Vasconcellos0% (2)

- Condiciones Básicas para Aprender A Resolver ConflictosDocument7 pagesCondiciones Básicas para Aprender A Resolver ConflictosMaria Del Carmen SuárezNo ratings yet

- La Crítica Al Concepto de Autoridad A Traves Del ArteDocument44 pagesLa Crítica Al Concepto de Autoridad A Traves Del Arteelwen1975No ratings yet

- 45-17 Becas X Puntaje 2017 PDFDocument71 pages45-17 Becas X Puntaje 2017 PDFMiguel Lo SassoNo ratings yet

- Astm 285Document8 pagesAstm 285Joel LRNo ratings yet

- Tesis Miriam Aviles y Luis Alberto GuijarroDocument178 pagesTesis Miriam Aviles y Luis Alberto GuijarroJohanRosasVazquezNo ratings yet

- PEC1 - Sociopsicologia - Del Trabajo-Set 2022 - Jun 2023Document3 pagesPEC1 - Sociopsicologia - Del Trabajo-Set 2022 - Jun 2023Andrea DuqueNo ratings yet

- Proy-2012 - Buenos ModalesDocument8 pagesProy-2012 - Buenos Modalesliliana gonzalezNo ratings yet

- Examen Oficial de Mayo 6to GradoDocument8 pagesExamen Oficial de Mayo 6to Gradomcecilia100% (1)

- Tratamiento de Las Discrepancias Ortotipográficas InglésDocument11 pagesTratamiento de Las Discrepancias Ortotipográficas InglésMaria Gabriela GuzmanNo ratings yet

- Examen Parcial-Ing IndDocument3 pagesExamen Parcial-Ing IndYasmin Vasquez SNo ratings yet