Professional Documents

Culture Documents

FPGA Realisation of SVPWM

Uploaded by

srfmlpCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

FPGA Realisation of SVPWM

Uploaded by

srfmlpCopyright:

Available Formats

14th National Conference on Technological Trends | 30 - 31, August 2013 | College of Engineering Trivandrum

FPGA Realization of Space-Vector Pulse Width Modulation for a 3-Level

Inverter

Muhamed Shereef1 , Shiny.G2

Power Electronics Research Laboratory

Dept. of Electronics and Communication Engineering

College of Engineering Trivandrum, Kerala, India

srfmlp@gmail.com1

Abstract

A simplified space-vector pulse width modulation

(SVPWM) scheme for a 3-level inverter is presented. The

method involves the mapping of reference vector in the

space vector diagram of 3-level inverter to a 2-level inverter.

60 coordinate system is used to represent space vectors instead of using cartesian coordinate system. In 60 coordinate system only integer coordinates are involved. So the

computational complexity is reduced. The proposed scheme

is simulated and verified using Xilinx system generator software.

1. Introduction

Multilevel inverters are widely used in industrial drive

applications due to their ability to produce waveforms with

improved harmonic spectrum [1, 2]. Multi level inverters

can produce variable voltages and frequencies from discrete

voltage levels using pulse width modulation (PWM) strategies. Several techniques have been developed for the implementation of PWM [3, 4]. The two main methods are Sine

triangle Pulse width Modulation (SPWM) and Space Vector Pulse Width Modulation (SVPWM) [5, 6]. SPWM is

the simple and widely used scheme which generates PWM

signals by comparison of level shifted triangular carrier signals with a sinusoidal reference waveform [7, 8]. SVPWM

involves synthesising of reference sinusoidal voltage by

switching amoung the nearest three voltage spacevectors.

SVPWM is the best technique to implement PWM due to

following advantages. 1) higher o/p voltage for the same

dc-bus voltage 2) lower switching losses and 3) Better harmonic performance.

Implementation of SVPWM scheme involves 1.sector

identification 2.determination of nearest voltage space vectors to be switched 3.determination of duration of each

switching voltage space vectors 4.determination of an op-

timum switching sequence. A new approach for sector

identification using fractal concept is proposed in [9]. The

scheme in [9] uses cartesian coordinate system for the representation of space vectors. SVPWM scheme based on 60

coordinate system has been proposed in [10, 11, 12, 13].

For the implementation of SVPWM techniques Digital

Signal Processors (DSP) are widely used [14].But DSP executes control procedures sequentially using their mathematically oriented resources. So the mutual influences of

various control procedures should no longer be neglected

in high sampling rate applications. But differ from DSP

FPGA can execute control procedures concurrently. Due

to its powerful calculation ability and flexibility, FPGA is

considered as an appropriate solution to boost system performance of a digital controller including an SVPWM algorithm [15, 16, 17].

This paper proposes the implementation of SVPWM algorithm for a 3-level inverter based on 60 coordinate system using FPGA. As compared to cartesian coordinate system the representation of space vector using 60 coordinate

system greately reduces computational complexity since

only integer coordinates are involved.

2. Proposed Scheme

SVPWM involves synthesising of reference sinusoidal

voltage(Vref ) by switching amoung the nearest three voltage space vectors. In the proposed work 60 coordinate

system is used to represent the space vectors. Suppose

Va , Vb and Vc represents the instantaneous amplitudes of

three phase reference sinusoid, 60 coordinates (m, n) of

Vref can be found using the equations given below,

Vm = Va Vb

(1)

Vn = Vb Vc

(2)

(m, n) coordinates are normalized using the division by

Vdc /(l 1). Where Vdc is the d.c link voltage and l is the

362

14th National Conference on Technological Trends | 30 - 31, August 2013 | College of Engineering Trivandrum

number of levels of inverter. Space vector representation

of a 3-level inverter using 60 coordinate system is shown

Figure. 1

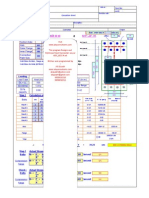

Table 1. Sector identification (1=Satisfy, 0=Notsatisfy, =Dont

care)

Sector

1

2

3

4

5

6

Vmm 0

1

0

0

0

1

1

Vnm 0

1

1

1

0

0

0

|Vmm | |Vnm |

0

1

0

1

Determination of sub hexagon to which Vref belongs.

Mapping of Vref into the inner hexagon.

Find the sector of inner hexagon to which the mapped

reference vector Vrefm belongs.

Determination of duration of switching voltage space

vectors.

Determination of an optimum switching sequence.

Determination of actual switching vectors by adding

the switching vector corresponds to the sub hexagon

center.

Figure 1. Space vector representation of a 3-level inverter in 60

coordinate system

The space vector diagram of a three-level inverter can

be viewed as the composition of one inner hexagon and

six outer sub hexagons that are the space vector diagrams

of conventional two-level inverters. Each of these six sub

hexagons, constitutes the space vector diagram of a 3-level

inverter, centers on the six apexes of the inner hexagon. Figure. 2 shows the sub hexagon centers of 3-level inverter.

2.1. Sub Hexagon Center Identification

Sub hexagon center closest to the tip of Vref is determined by comparing (m, n) coordinates of Vref with each

sub hexagon center. Comparison is done by calculating

the distance from (m, n) coordinates of Vref to each sub

hexagon center using the equation

p

d = (Vm Vmh )2 + (Vn Vnh )2 + (Vm Vmh )(Vn Vnh )

(3)

where Vmh & Vnh are the corresponding sub hexagon center. The sub hexagon center with least value of d is selected.

2.2. Mapping to 2-level space vector

The hexagon center closest to the tip of Vref is subtracted from the respective (m, n) coordinates of Vref . Suppose Vref is located in sub hexagon with center B as in

Figure. 3 then the new coordinates of mapped reference

vector(Vref m ) can be calculated as

Figure 2. Space vector of a 3-level inverter showing Sub hexagon

centers

Steps involved in the implementation of SVPWM are

Vmm = Vm 0

(4)

Vnm = Vn 1

(5)

The sector to which the Vref m belongs can be found using Table. 1

Once the sector of operation is identified phase voltage switching timings of switching vectors can be found

as in Table. 2. It should be ensured the selected vectors are

switched in an optimum sequence so that only one switching occurs when the inverter changes its state.

363

14th National Conference on Technological Trends | 30 - 31, August 2013 | College of Engineering Trivandrum

FPGA. Coupled with a capability for implementing highly

parallel arithmetic architectures, this makes the FPGA ideally suited for creating high-performance PWM controllers.

Though VHDL provides many high level abstractions and

language constructs for simulation, its synthesizable subset

is far too restrictive for system design. System Generator

is a software tool for modeling and designing FPGA-based

DSP systems in Simulink. The tool presents a high level abstract view of a DSP system, yet nevertheless automatically

maps the system to a faithful hardware implementation. The

most significant is that System Generator provides these services without substantially compromising either the quality

of the abstract view or the performance of the hardware implementation.

3.1. System Generator

Figure 3. Mapping of Vref in to inner hexagon

Table 2. Equations for determining T1 and T2 for a two level inverter

Sector

1

2

3

4

5

6

T1

Ts Vmm

Ts (Vmm + Vnm )

Ts Vnm

Ts Vmm

Ts (Vmm + Vnm )

Ts Vnm

T2

Ts Vnm

Ts Vmm

Ts (Vmm + Vnm )

Ts Vnm

Ts Vmm

Ts (Vmm + Vnm )

2.3. Generation of Actual Switching Vector

Actual switching vector is generated by adding back the

hexagon center to the calculated switching vectors as shown

in Figure. 4.

Simulink provides a powerful high level modeling environment for DSP systems, and consequently is idely used

for algorithm development and verification. System Generator maintains an abstraction level very much in keeping

with the traditional Simulink block sets, but at the same time

automatically translates designs into hardware implementations that are faithful, synthesizable, and efficient [18].

The implementation is faithful in that the system model

and hardware implementation are bit-identical and cycleidentical at ample times defined in Simulink. The implementation is made efficient through the instantiation of intellectual property (IP) blocks that provide a range of functionality from arithmetic operations to complex DSP functions [18]. These IP blocks have been carefully designed

to run at high speed and to be area efficient. In System

Generator, the capabilities of IP blocks have been extended

transparently and automatically to fit gracefully into a system level framework. For example, although the underlying IP blocks operate on unsigned integers, System Generator allows signed and unsigned fixed point numbers to be

used, including saturation arithmetic and rounding. Userdefined IP blocks can be incorporated into a System Generator model as black boxes which will be embedded by the

tool into the HDL implementation of the design.

4. Modeling with system genereator

Figure 4. Generation of Actual switching vector

3. FPGA Implementation

Field-Programmable Gate Arrays (FPGAs) have become

key components in implementing high performance digital

signal processing (DSP) systems [17]. The memory bandwidth of a modern FPGA far exceeds that of a microprocessor or DSP running at clock rates two to ten times that of the

Before developing the hardware circuit for power, control and isolation circuit based on the FPGA, the entire

system is generated with the aid of simulation package

simulink/system generator for FPGA in order to verify the

pulses and the patterns of the output pulses. The creation of

a DSP design begins with a mathematical description of the

operations needed and concludes with a hardware realization of the algorithm [18]. The hardware implementation is

rarely faithful to the original functional description instead

it is faithful enough. The challenge is to make the hardware

area and speed efficient while still producing acceptable re-

364

14th National Conference on Technological Trends | 30 - 31, August 2013 | College of Engineering Trivandrum

Table 3. Status of the top switches of each Inverter during different

Voltage levels (For A-phase)

Inverter-1

OFF

OFF

ON

Inverter-2

OFF

ON

ON

VA0 O

0

Vdc /2

Vdc

Realized switching level

0

1

2

Figure 6. Simulation model

Figure 5. 3-level Inverter by Cascading two 2-level Inverters

sults. In a typical design flow, a flow supported by System

Generator the following steps occur:

1. Describe the algorithm in mathematical terms

2. Realize the algorithm in the design environment, initially using double precision

Figure 7. Switching signals generated for 2-level operation: Top 3traces for Inverter-1 & Lower 3-traces for Inverter-2 (Modulation

index 0.25)

3. Trim double precision arithmetic down to fixed point

4. Translate the design into efficient hardware

Step 4 is error prone because it can be difficult to guarantee the hardware implements the design faithfully. System

Generator eliminates this concern by automatically generating a faithful hardware implementation.

5. Simulation and Results

5.1. 3-Level Inverter Configuration

3-Level Inverter is achieved by cascading two 2-level Inverters having same D.C link voltage of Vdc /2 as shown in

Figure. 5.

VAO , VBO and VCO represents the pole voltages of

Inverter-1. VA0 O , VB 0 O and VC 0 O represents pole voltages

of Inverter-2. Status of the top switches of the individual inverters during different voltage levels is shown in Table. 3. In case of 2-level operation ie, the reference vector

(Vref ) is in the inner hexagon, only inverter-2 is switched

and inverter-1 is clamped to zero level.

5.2. Modeling Using System Generator

The proposed algorithm is generated in front end with

the aid of system generator editor, and the sampling fre-

Figure 8. Switching signals generated for 3-level operation: Top 3traces for Inverter-1 & Lower 3-traces for Inverter-2 (Modulation

index 0.75)

quency is set to 5kHz. The entire system is shown in Figure 6.

Switching pulses generated for a modulation index of

0.25, i.e. corresponds to 2-level operation, are shown in

Figure 7. As seen, in 2-level operation, only inverter-2

is switched and inverter-1 is clamped to zero level. The

switching pulses generated for 3-level operation (modulation index = 0.75) are shown in Figure 8. Both the inverters

switch equally during 3-level operation.

6. Conclusion

This paper proposes a method for the implementation of

SVPWM in FPGA. Since the SVPWM method is based on

the 60 coordinate system instead of cartesian coordinate

system computational complexity is greatly reduced. The

scheme is simulated for a 3-level inverter. 3-level inverter is

365

14th National Conference on Technological Trends | 30 - 31, August 2013 | College of Engineering Trivandrum

realised by cascading two 2-level inverters.

References

[1] A. Nabae, I.Takahashi, and H. Akagi, A new neutral

point clamped pwm inverter, IEEE Transactions on Industry Applications, vol. 1A-17, no. 5, pp. 518523, September/October 1981.

[2] Heinz Willi Van Der Broeck, Hans-Christoph Skudelny,

and Georg Viktor Stanke, Analysis and realization of a

pulsewidth modulator based on voltage space vectors, IEEE

Transactions on Industry Applications, vol. 24, no. 1, pp.

142150, January/February 1988.

[3] J. Holtz, Pulse width modulationa survey, IEEE Trans.

Ind. Electron., vol. 39, no. 5, pp. 410420, Dec. 1992.

[4] W. Yao, H. Hu, and Z. Lu, Comparisons of space-vector

modulation and carrier based modulation of multilevel inverter, IEEE Trans. Power Electron., vol. 23, no. 1, pp.

4551, Jan. 2008.

[14] F. Blaabjerg A. M. Trzynadlowski, M. M. Bech and J. K.

Pedersen, An integral space-vectorpwmtechnique for dspcontrolled voltagesource inverters, IEEE Trans. Ind. Appl.,

vol. 35, no. 5, pp. 10911097, Jul./Aug. 1999.

[15] T. Ying-Yu and H. Hau-Jean, Fpga realization of spacevector pwm control 1c for three-phase pwm inverters, EEE

Trans. Power Electron., vol. 12, no. 6, pp. 953963, Nov.

1997.

[16] L. Wenhua C. Yuanhua L. Tian, S. Qiang and L. Jianguo,

Fpgabased universal multilevel space vector modulator,

Proc. IECON 32nd Annu. Conf, pp. 745749, 2005.

[17] P. Fioravanti C. Cecati. M. Cirstea. M. Mc. Cormick, Design of a fpga implementing a passivity-based pulsewidth

modulation, SPEEDAM 2002, pp. A2 43A2 48, 2002.

[18] Xtremedsp starter kit - spartan-3a dsp application notes and

product information available online at (www.xilinx.com),

.

[5] V. T. Somasekhar and K. Gopakumar, Three-level inverter

configuration cascading two two-level inverters, Proc. Inst.

Elect. Eng.Electr. Power Appl., vol. 150, no. 3, pp. 245254,

May 2003.

[6] A. K. Gupta and A. M. Khambadkone, A space vector

modulation scheme to reduce common mode voltage for cascaded multilevel inverters, IEEE Trans. Power Electron.,

vol. 22, no. 5, pp. 16721681, Sep. 2007.

[7] G. Carrara, S. G. Gardella, M. Marchesoni, R. Salutari, and

G. Sciutto, A new multilevel pwmmethod: A theoretical

analysis, IEEE Trans. Power Electron., vol. 7, no. 3, pp.

497505, Jul. 1992.

[8] H. Bai, Z. Zhao, S. Meng, J. Liu, and X. Sun, Comparison

of three pwm strategies-spwm, svpwm & one-cycle control,

Proc. 5th Int. Conf. Power Electron. Drive Syst., vol. 2, pp.

13131316, 2003.

[9] Anish Gopinath, Aneesh Mohamed A.S, and M.R.Baiju,

Fractal based space vector pwm for multilevel inverters a

novel approach, IEEE Transactions on Industrial Electronics, vol. 52, no. 4, pp. 12301238, April 2009.

[10] Haibing Hu Wenxi Yao and Zhengyu Lu, Comparison of

space vector modulation and carrier based modulation of

multilevel inverter, IEEE Transactions on Power Electronics, vol. 23, no. 1, pp. 4541, January 2008.

[11] N.Celanovic and Dushan Boroyevich, A fast space-vector

modulation algorithm for multilevel three-phase converters,

IEEE Transactions on Industry Applications, vol. 37, no. 2,

pp. 637641, March/April 2001.

[12] Fahai Li Sanmin Wei, Bin Wu and Congwei Liu, A general

space vector pwm control algorithm for multilevel inverters,

Proc. APEC 2003, pp. 562568.

[13] Chang Ho Choi Jae Hyeong Seo and Dong Seok Hyun, A

new simplified space vector pwm method for three-level inverters, IEEE Transactions on Industry Applications, vol.

16, no. 4, pp. 545550, July 2001.

366

You might also like

- Spline and Spline Wavelet Methods with Applications to Signal and Image Processing: Volume III: Selected TopicsFrom EverandSpline and Spline Wavelet Methods with Applications to Signal and Image Processing: Volume III: Selected TopicsNo ratings yet

- Space Vector PWM - 1Document5 pagesSpace Vector PWM - 1guanitouNo ratings yet

- Software Radio: Sampling Rate Selection, Design and SynchronizationFrom EverandSoftware Radio: Sampling Rate Selection, Design and SynchronizationNo ratings yet

- FPGA Implementation On SVPWM MLIDocument5 pagesFPGA Implementation On SVPWM MLISheetal VermaNo ratings yet

- Radio Frequency Identification and Sensors: From RFID to Chipless RFIDFrom EverandRadio Frequency Identification and Sensors: From RFID to Chipless RFIDNo ratings yet

- VLP 0401 " Space Vector PWM Using FPGA"Document6 pagesVLP 0401 " Space Vector PWM Using FPGA"ashish3179100% (1)

- Generalized Rail Clamping Sequences Based PWM (GRCPWM) Algorithm For Direct Torque Controlled Induction Motor DriveDocument22 pagesGeneralized Rail Clamping Sequences Based PWM (GRCPWM) Algorithm For Direct Torque Controlled Induction Motor DriveHari ReddyNo ratings yet

- Arduino Measurements in Science: Advanced Techniques and Data ProjectsFrom EverandArduino Measurements in Science: Advanced Techniques and Data ProjectsNo ratings yet

- De Embedding and Embedding S Parameter Networks Using A Vector Network AnalyzerDocument24 pagesDe Embedding and Embedding S Parameter Networks Using A Vector Network AnalyzerAlexander LaraNo ratings yet

- Power Systems-On-Chip: Practical Aspects of DesignFrom EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardNo ratings yet

- Kiran Gunnam, Weihuang Wang, Euncheol Kim, Gwan Choi, Mark YearyDocument6 pagesKiran Gunnam, Weihuang Wang, Euncheol Kim, Gwan Choi, Mark YearypathmakerpkNo ratings yet

- FPGA Implementation of Simplified SVPWM Algorithm For Three Phase Voltage Source InverterDocument8 pagesFPGA Implementation of Simplified SVPWM Algorithm For Three Phase Voltage Source InverterVenkata Krishna AndeyNo ratings yet

- Volume 3 - Number 1 - Tools For Microwave Radio Communications System DesignDocument13 pagesVolume 3 - Number 1 - Tools For Microwave Radio Communications System DesignArter AlayNo ratings yet

- Energies: Adaptive Wide-Area Damping Control Scheme For Smart Grids With Consideration of Signal Time DelayDocument18 pagesEnergies: Adaptive Wide-Area Damping Control Scheme For Smart Grids With Consideration of Signal Time Delaycontrol_613No ratings yet

- Cascaded Multilevel InvertersDocument6 pagesCascaded Multilevel InvertersMinhaj NaimNo ratings yet

- A Digital-Based Optimal AVR Design of Synchronous Generator Exciter Using LQR TechniqueDocument13 pagesA Digital-Based Optimal AVR Design of Synchronous Generator Exciter Using LQR Technique3KaiserENo ratings yet

- Fast-Predictive Optimal Control of NPC Multilevel ConvertersDocument9 pagesFast-Predictive Optimal Control of NPC Multilevel Converterskanda71No ratings yet

- Modif 24626-48450-1-PBDocument10 pagesModif 24626-48450-1-PBdodol garutNo ratings yet

- Design of FMCW Radars For Active Safety Applications PDFDocument5 pagesDesign of FMCW Radars For Active Safety Applications PDFAnonymous LoJy6ERXdNo ratings yet

- Simplified SVPWM Algorithm For Neutral Point Clamped 3-Level Inverter Fed DTC-IM DriveDocument6 pagesSimplified SVPWM Algorithm For Neutral Point Clamped 3-Level Inverter Fed DTC-IM DrivePasupuleti SivakumarNo ratings yet

- A Simple and Ultra-Fast DSP-Based Space Vector PWM Algorithm andDocument6 pagesA Simple and Ultra-Fast DSP-Based Space Vector PWM Algorithm andShiviAroraNo ratings yet

- A Simplified Dwell Time Computation Method For SVPDocument13 pagesA Simplified Dwell Time Computation Method For SVPFlynn RyderNo ratings yet

- Ntroduction: Fig.1. Principle Block DiagramDocument4 pagesNtroduction: Fig.1. Principle Block Diagramanant0008No ratings yet

- DSSS Synchronization SubsystemDocument21 pagesDSSS Synchronization Subsystemapi-26331790No ratings yet

- Implementation of Adaptive Viterbi DecoderDocument7 pagesImplementation of Adaptive Viterbi DecoderseventhsensegroupNo ratings yet

- Vlsi Design Approach To High-Performance Direct Torque Control of Induction Motor DrivesDocument8 pagesVlsi Design Approach To High-Performance Direct Torque Control of Induction Motor Drivesjooner45No ratings yet

- Pscad ModelingDocument21 pagesPscad ModelingSumith Wellawa100% (1)

- Multilevel Multiphase Space Vector PWM Algorithm Applied To Three-Phase ConvertersDocument7 pagesMultilevel Multiphase Space Vector PWM Algorithm Applied To Three-Phase ConvertersAthiesh KumarNo ratings yet

- Power Quality RecorderDocument8 pagesPower Quality RecorderSpiros LoutridisNo ratings yet

- Digital Scalar Pulse Width Modulation Methods For Voltage Source Inverter Fed Ac DriveDocument7 pagesDigital Scalar Pulse Width Modulation Methods For Voltage Source Inverter Fed Ac DriveijsretNo ratings yet

- Design and Implement of QPSK Modem Based On FPGADocument3 pagesDesign and Implement of QPSK Modem Based On FPGAAnil PatilNo ratings yet

- A General Space Vector PWM Algorithm For Multilevel Inverters, Including Operation in OvermodulationDocument10 pagesA General Space Vector PWM Algorithm For Multilevel Inverters, Including Operation in OvermodulationxuanthamdhqnNo ratings yet

- A Compact Ultra-Wideband Load-Pull Measurement SystemDocument6 pagesA Compact Ultra-Wideband Load-Pull Measurement Systemoğuz odabaşıNo ratings yet

- Simulation of A Space Vector PWM Controller For A Five-Level Voltage-Fed Inverter Motor DriveDocument7 pagesSimulation of A Space Vector PWM Controller For A Five-Level Voltage-Fed Inverter Motor DriveIOSRjournalNo ratings yet

- FPGA Based Implementation of Symmetrical Switching in SVPWM For Three Level NPC ConverterDocument6 pagesFPGA Based Implementation of Symmetrical Switching in SVPWM For Three Level NPC ConvertersateeshNo ratings yet

- FPGA-Based Implementation of Digital Control For A Magnetic BearingDocument6 pagesFPGA-Based Implementation of Digital Control For A Magnetic Bearingajith.ganesh2420No ratings yet

- Design and Implemation of An Enhanced Dds Based Digital Modulator For Multiple Modulation Schemes Manoj Kollam, S.A.S Krishna Chaithanya and Nagaraju Kommu IJSSAN 2011Document6 pagesDesign and Implemation of An Enhanced Dds Based Digital Modulator For Multiple Modulation Schemes Manoj Kollam, S.A.S Krishna Chaithanya and Nagaraju Kommu IJSSAN 2011John JohnstonNo ratings yet

- Modeling Heterogeneous Systems Using Systemc-Ams Case Study: A Wireless Sensor Network NodeDocument6 pagesModeling Heterogeneous Systems Using Systemc-Ams Case Study: A Wireless Sensor Network Nodesimon9085No ratings yet

- FPGA Implementation of CORDIC-Based QRD-RLS AlgorithmDocument5 pagesFPGA Implementation of CORDIC-Based QRD-RLS Algorithmsappal73asNo ratings yet

- Assignment: Application of Graphs in Computer ProgrammingDocument11 pagesAssignment: Application of Graphs in Computer ProgrammingSaran AgarwalNo ratings yet

- Lab No.2 Modeling A Micro Strip Transmission Line in ADS: Objective: TheoryDocument5 pagesLab No.2 Modeling A Micro Strip Transmission Line in ADS: Objective: Theorymuhammad jehangirNo ratings yet

- Paper-7 An Application of Direct Modulation To Generate SPWM Waveform Using VHDL For FPGA Interfaced H-Bridge Power InverterDocument6 pagesPaper-7 An Application of Direct Modulation To Generate SPWM Waveform Using VHDL For FPGA Interfaced H-Bridge Power InverterRachel WheelerNo ratings yet

- Edm CNC Paper NCDocument10 pagesEdm CNC Paper NCramjoceNo ratings yet

- IET - KCJ - Performance Evaluation of A General SVPWMDocument9 pagesIET - KCJ - Performance Evaluation of A General SVPWMKartick JanaNo ratings yet

- Automated Measurement of Frequency Response of Electrical Networks Filters and AmplifiersDocument7 pagesAutomated Measurement of Frequency Response of Electrical Networks Filters and AmplifiersDiscrete ComponentNo ratings yet

- FPGA Implementation of The Ternary Pulse Compression SequencesDocument5 pagesFPGA Implementation of The Ternary Pulse Compression SequencesvijaykannamallaNo ratings yet

- Energies 12 04332 v2Document24 pagesEnergies 12 04332 v2thinhNo ratings yet

- Internal ModelDocument15 pagesInternal ModelDiego RamirezNo ratings yet

- Digital Scalar Pulse Width Modulation Methods For Voltage Source Inverter Fed Ac DriveDocument7 pagesDigital Scalar Pulse Width Modulation Methods For Voltage Source Inverter Fed Ac DriveMuhamad Taufiq AhsanNo ratings yet

- Research Inventy: International Journal of Engineering and ScienceDocument10 pagesResearch Inventy: International Journal of Engineering and ScienceresearchinventyNo ratings yet

- National Institute of Technology: Karnataka, SurathkalDocument36 pagesNational Institute of Technology: Karnataka, SurathkalSneha JogdhankarNo ratings yet

- Design of Linear Array Transducer Using Ultrasound Simulation Program Field-IIDocument7 pagesDesign of Linear Array Transducer Using Ultrasound Simulation Program Field-IIinventyNo ratings yet

- Patch Antenna Design Using MICROWAVE STUDIODocument6 pagesPatch Antenna Design Using MICROWAVE STUDIOmayank sharmaNo ratings yet

- A Simple Space Vector PWM Generation Scheme For Any General N-Level InverterDocument9 pagesA Simple Space Vector PWM Generation Scheme For Any General N-Level InverterAhmad MqdadNo ratings yet

- FFT in SarDocument5 pagesFFT in SarBhuvanachandran ANo ratings yet

- Microprocessors and Microsystems: Ganesan R, S. Suresh, SS SivarajuDocument9 pagesMicroprocessors and Microsystems: Ganesan R, S. Suresh, SS SivarajufvijayamiNo ratings yet

- Vol. 12 No. 2 Pp. 571-579Document10 pagesVol. 12 No. 2 Pp. 571-579Abdelmalik BendaikhaNo ratings yet

- A Software Radio Architecture For Smart AntennasDocument8 pagesA Software Radio Architecture For Smart AntennasRockstar_rohithNo ratings yet

- Hardware Implementation: Branch Metric Unit (BMU)Document6 pagesHardware Implementation: Branch Metric Unit (BMU)api-19790923No ratings yet

- Introduction To Engineering AnalysisDocument8 pagesIntroduction To Engineering AnalysisSuprioNo ratings yet

- SOR (RR) of Assam 2019-20 - 19-08-2019Document164 pagesSOR (RR) of Assam 2019-20 - 19-08-2019Satyabrat Mili50% (2)

- ProVent IPC Comparison Manual LetterDocument12 pagesProVent IPC Comparison Manual Letterjack j100% (1)

- Revit MEPDocument6 pagesRevit MEPlexlox100% (1)

- Guideline On RSA ManagementDocument103 pagesGuideline On RSA ManagementAmirul BassNo ratings yet

- RAMI 4.0: An Architectural Model For Industrie 4.0Document31 pagesRAMI 4.0: An Architectural Model For Industrie 4.0Finigan JoyceNo ratings yet

- General Construction Notes:: Notes On Beams and GirdersDocument1 pageGeneral Construction Notes:: Notes On Beams and GirdersJaycee RollanNo ratings yet

- New Cisco CertificationDocument2 pagesNew Cisco Certificationsagar002100No ratings yet

- ONSemi-Developing A 25-kW SiC-Based Fast DC Charger Solution Overview1Document5 pagesONSemi-Developing A 25-kW SiC-Based Fast DC Charger Solution Overview1133514No ratings yet

- Residential Slabs and Footings Workshop 1 DayDocument1 pageResidential Slabs and Footings Workshop 1 DayredpuffNo ratings yet

- Railway Reservation SystemDocument20 pagesRailway Reservation SystemChand Kishor Prasad100% (1)

- Bachelor of Engineering With HonoursDocument6 pagesBachelor of Engineering With HonoursAllalannNo ratings yet

- Application Letter ExampleDocument7 pagesApplication Letter ExampleMarc EvalleNo ratings yet

- 3.5 T Bolier ManualDocument206 pages3.5 T Bolier Manualchandravadiyaketan150467% (3)

- Bs 6464 1984 Reinforced Plastics Pipes Fittings and Joints For Process Plants PDFDocument60 pagesBs 6464 1984 Reinforced Plastics Pipes Fittings and Joints For Process Plants PDFkais rguiguiNo ratings yet

- British Columbia Ministry of Transportation and InfrastructureDocument5 pagesBritish Columbia Ministry of Transportation and InfrastructureFarhanNo ratings yet

- 2010 SEAOC Convention ProceedingsDocument9 pages2010 SEAOC Convention ProceedingsPE EngNo ratings yet

- Robert Bosch Written Placement Exam Paper - 2008Document2 pagesRobert Bosch Written Placement Exam Paper - 2008Shiv PrakashNo ratings yet

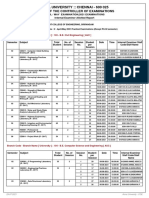

- Anna University:: Chennai - 600 025: Office of The Controller of ExaminationsDocument4 pagesAnna University:: Chennai - 600 025: Office of The Controller of ExaminationsAarthi JNo ratings yet

- Dowel Bar Size and Spacing For Rigid Pavements PDFDocument8 pagesDowel Bar Size and Spacing For Rigid Pavements PDFTim Lin100% (1)

- Hexagon MI Romax Flyer Evolve A4 EN 2021 WEBDocument2 pagesHexagon MI Romax Flyer Evolve A4 EN 2021 WEBSanjay ShelarNo ratings yet

- Assignment 7221 MD-IIIDocument2 pagesAssignment 7221 MD-IIIkalikaNo ratings yet

- 11 Steel Connection Design As Per AISC 23052014Document2 pages11 Steel Connection Design As Per AISC 23052014Ahmad Badsha Quadri67% (3)

- Oracle Aim Methodology: - R.RubiniDocument29 pagesOracle Aim Methodology: - R.RubiniRubini RajaNo ratings yet

- Os E406 - 2010 04Document131 pagesOs E406 - 2010 04Kishor ShriyanNo ratings yet

- (W. H. Mosley, R. Hulse, J. H. Bungey (Auth.) ) Rei (B-Ok - Xyz) PDFDocument441 pages(W. H. Mosley, R. Hulse, J. H. Bungey (Auth.) ) Rei (B-Ok - Xyz) PDFHamidullah Afghan100% (1)

- Advantages and Disadvantages of Reinforced Cement Concrete (R.C.C)Document5 pagesAdvantages and Disadvantages of Reinforced Cement Concrete (R.C.C)awaw awawNo ratings yet

- Lab Sheet 2 (14DKM19F1007)Document10 pagesLab Sheet 2 (14DKM19F1007)Amirul RoslanNo ratings yet

- Earthquake Resistant Masonary BuildingsDocument26 pagesEarthquake Resistant Masonary BuildingsSourabhAdikeNo ratings yet

- Sushita 172 Report (BRIDGE DESIGN)Document9 pagesSushita 172 Report (BRIDGE DESIGN)SushitaBethSenobagoNo ratings yet

- Summary of Noah Kagan's Million Dollar WeekendFrom EverandSummary of Noah Kagan's Million Dollar WeekendRating: 5 out of 5 stars5/5 (2)

- High Road Leadership: Bringing People Together in a World That DividesFrom EverandHigh Road Leadership: Bringing People Together in a World That DividesNo ratings yet

- The Millionaire Fastlane, 10th Anniversary Edition: Crack the Code to Wealth and Live Rich for a LifetimeFrom EverandThe Millionaire Fastlane, 10th Anniversary Edition: Crack the Code to Wealth and Live Rich for a LifetimeRating: 4.5 out of 5 stars4.5/5 (90)

- $100M Offers: How to Make Offers So Good People Feel Stupid Saying NoFrom Everand$100M Offers: How to Make Offers So Good People Feel Stupid Saying NoRating: 5 out of 5 stars5/5 (26)

- $100M Leads: How to Get Strangers to Want to Buy Your StuffFrom Everand$100M Leads: How to Get Strangers to Want to Buy Your StuffRating: 5 out of 5 stars5/5 (19)

- The Coaching Habit: Say Less, Ask More & Change the Way You Lead ForeverFrom EverandThe Coaching Habit: Say Less, Ask More & Change the Way You Lead ForeverRating: 4.5 out of 5 stars4.5/5 (186)

- Summary of Thinking, Fast and Slow: by Daniel KahnemanFrom EverandSummary of Thinking, Fast and Slow: by Daniel KahnemanRating: 4 out of 5 stars4/5 (117)

- Critical Thinking: How to Effectively Reason, Understand Irrationality, and Make Better DecisionsFrom EverandCritical Thinking: How to Effectively Reason, Understand Irrationality, and Make Better DecisionsRating: 4.5 out of 5 stars4.5/5 (39)

- The Leader Habit: Master the Skills You Need to Lead--in Just Minutes a DayFrom EverandThe Leader Habit: Master the Skills You Need to Lead--in Just Minutes a DayRating: 4 out of 5 stars4/5 (5)

- Broken Money: Why Our Financial System Is Failing Us and How We Can Make It BetterFrom EverandBroken Money: Why Our Financial System Is Failing Us and How We Can Make It BetterRating: 5 out of 5 stars5/5 (4)

- 12 Months to $1 Million: How to Pick a Winning Product, Build a Real Business, and Become a Seven-Figure EntrepreneurFrom Everand12 Months to $1 Million: How to Pick a Winning Product, Build a Real Business, and Become a Seven-Figure EntrepreneurRating: 4.5 out of 5 stars4.5/5 (3)