Professional Documents

Culture Documents

Comprehensive VHDL Introduction

Uploaded by

tecalexmdsOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Comprehensive VHDL Introduction

Uploaded by

tecalexmdsCopyright:

Available Formats

SynthWorks

SM

Expert VHDL Training for Hardware Design and Verification

Comprehensive VHDL Introduction

4 Days: 50% Lecture, 50% Lab

Basic Level

Overview

An in-depth introduction to VHDL and its application to design and verification of

digital hardware (FPGAs and ASIC). Provides a foundation in RTL and testbench

coding styles required by design and verification engineers who are new to VHDL.

Through a series of lectures, exercises, and labs, students will gain a strong

foundation in VHDL RTL and testbench coding techniques. Lectures contain numerous

examples that show both syntax and coding style guidelines. Exercises provide

immediate reinforcement of lecture materials. Labs give students hands-on

experience writing RTL code, writing testbenches, running your simulator, running

your synthesis tool, and programming our FPGA based lab board.

The comprehensive lecture guide provides an excellent after-class reference. Syntax

and code that is not synthesizable is specifically noted. Labs account for

approximately 50% of class time. Lab projects range from simple simulation and

synthesis coding problems to small design projects. The design projects utilize all

techniques learned in lecture and demonstrate how VHDL is used in a project

environment.

Intended Audience

Recommended as a first course in VHDL for design and verification engineers who

need an in-depth understanding of VHDL and a solid foundation in RTL and testbench

coding techniques.

Course Objectives

Upon completion of this course, students will be able to:

Understand VHDL syntax and coding styles relevant to logic design

Write VHDL RTL hardware designs using good coding practices

Understand the synthesizable subset of VHDL

Understand problematic issues in coding hardware

Use types, overloading, and conversion functions from standard VHDL packages

(std_logic_1164, numeric_std, and std_logic_arith)

Print messages in testbenches using TEXTIO

Write simple transaction-based testbenches using subprograms

Use your VHDL simulation and synthesis tools

www.SynthWorks.com

Comprehensive VHDL Introduction

Course Outline

Day 1

A Quick Introduction

Lab 1: Simple RTL and Testbench

Data Types

Operators

Concurrent Statements

Sequential Statements

Lab 2: Clock and Reset

Lab 3: RTL and Testbench

Day 2

RTL Essentials

Statemachine Coding Techniques

Lab 4: RTL Code

Data Objects

Designing with VHDL

Lab 5: Coding an FSM

Lab 6: Creating Hierarchy

Day 3

Testbench Essentials

Subprograms

Lab 7: Brute Force Testbenches

Advanced Types

VHDL IO (TextIO)

Lab 8: Transaction-based Testbench

Lab 9: Creating an FPGA (Synthesis

and device programming).

Day 4

RTL Code

Lab Review

Advanced VHDL Constructs

Lab 10: UART Transmit Data Path

Lab 11: UART Transmit Statemachine

Lab 12: Multiplier Accumulator

Take Home Labs

Digital Clock

Prerequisites

None. Offered as a first course in VHDL. It is recommended that students are familiar

with digital design.

Follow-On Courses

Students wishing to go beyond what they learned in this course should take either or

both of the following courses:

Intermediate VHDL Coding Styles for Synthesis - 2 days

VHDL Testbenches and Verification - 4 days

All of our courses can be customized to meet your specific needs. Either see our

website or contact us for details.

Training Approach

This hands-on, how-to course is taught by experienced hardware designers using a

computer driven projector. We prefer and encourage student and instructor

interaction. Questions are welcome. Bring problematic code.

Contact

To schedule a class or for more information, contact SynthWorks at 800-505-8435 or

jim@synthworks.com

Learn VHDL from a designer's perspective with SynthWorks.

Copyright 1999 thru 2005 by SynthWorks Design Inc. All rights reserved. SynthWorks is a service mark of SynthWorks Design Inc.

You might also like

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Vanguard 44 - Anti Tank Helicopters PDFDocument48 pagesVanguard 44 - Anti Tank Helicopters PDFsoljenitsin250% (2)

- EP07 Measuring Coefficient of Viscosity of Castor OilDocument2 pagesEP07 Measuring Coefficient of Viscosity of Castor OilKw ChanNo ratings yet

- Chapter1 Intro To Basic FinanceDocument28 pagesChapter1 Intro To Basic FinanceRazel GopezNo ratings yet

- Measuring Road Roughness by Static Level Method: Standard Test Method ForDocument6 pagesMeasuring Road Roughness by Static Level Method: Standard Test Method ForDannyChaconNo ratings yet

- Req Equip Material Devlopment Power SectorDocument57 pagesReq Equip Material Devlopment Power Sectorayadav_196953No ratings yet

- A. Computed Only For A 2x2 Table B. 0 Cells (,0%) Have Expected Count Less Than 5. The Minimum Expected Count Is 3,40Document1 pageA. Computed Only For A 2x2 Table B. 0 Cells (,0%) Have Expected Count Less Than 5. The Minimum Expected Count Is 3,40harvey777No ratings yet

- PCM Cables: What Is PCM Cable? Why PCM Cables? Application?Document14 pagesPCM Cables: What Is PCM Cable? Why PCM Cables? Application?sidd_mgrNo ratings yet

- The Original Lists of Persons of Quality Emigrants Religious Exiles Political Rebels Serving Men Sold For A Term of Years Apprentices Children Stolen Maidens Pressed and OthersDocument609 pagesThe Original Lists of Persons of Quality Emigrants Religious Exiles Political Rebels Serving Men Sold For A Term of Years Apprentices Children Stolen Maidens Pressed and OthersShakir Daddy-Phatstacks Cannon100% (1)

- Localization On ECG: Myocardial Ischemia / Injury / InfarctionDocument56 pagesLocalization On ECG: Myocardial Ischemia / Injury / InfarctionduratulfahliaNo ratings yet

- DBM Uv W ChartDocument2 pagesDBM Uv W ChartEddie FastNo ratings yet

- Joomag 2020 06 12 27485398153Document2 pagesJoomag 2020 06 12 27485398153Vincent Deodath Bang'araNo ratings yet

- Communicating Value - PatamilkaDocument12 pagesCommunicating Value - PatamilkaNeha ArumallaNo ratings yet

- Initial Police Report: Calamba City Police Station Brgy Real, Calamba City, Laguna E-Mail: 545-1694/545-6789 Loc 8071Document1 pageInitial Police Report: Calamba City Police Station Brgy Real, Calamba City, Laguna E-Mail: 545-1694/545-6789 Loc 8071Jurish BunggoNo ratings yet

- The Future of FinanceDocument30 pagesThe Future of FinanceRenuka SharmaNo ratings yet

- Assessing Apical PulseDocument5 pagesAssessing Apical PulseMatthew Ryan100% (1)

- Study and Interpretation of The ScoreDocument10 pagesStudy and Interpretation of The ScoreDwightPile-GrayNo ratings yet

- Actron Vismin ReportDocument19 pagesActron Vismin ReportSirhc OyagNo ratings yet

- The One With The ThumbDocument4 pagesThe One With The Thumbnoelia20_09No ratings yet

- Outlook of PonDocument12 pagesOutlook of Ponty nguyenNo ratings yet

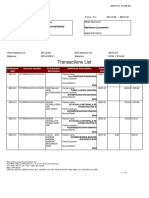

- Transactions List: Marilena Constantin RO75BRDE445SV93146784450 RON Marilena ConstantinDocument12 pagesTransactions List: Marilena Constantin RO75BRDE445SV93146784450 RON Marilena ConstantinConstantin MarilenaNo ratings yet

- 15 Miscellaneous Bacteria PDFDocument2 pages15 Miscellaneous Bacteria PDFAnne MorenoNo ratings yet

- 5045.CHUYÊN ĐỀDocument8 pages5045.CHUYÊN ĐỀThanh HuyềnNo ratings yet

- Corelink Mmu600ae TRM 101412 0100 00 enDocument194 pagesCorelink Mmu600ae TRM 101412 0100 00 enLv DanielNo ratings yet

- Aircraft Wiring Degradation StudyDocument275 pagesAircraft Wiring Degradation Study320338No ratings yet

- CHN Nutri LabDocument4 pagesCHN Nutri LabMushy_ayaNo ratings yet

- Chapter 13 Current Liabilities Test Bank Versi 2Document72 pagesChapter 13 Current Liabilities Test Bank Versi 2Slamet Tri PrastyoNo ratings yet

- Dynamic Study of Parabolic Cylindrical Shell A Parametric StudyDocument4 pagesDynamic Study of Parabolic Cylindrical Shell A Parametric StudyEditor IJTSRDNo ratings yet

- Bagian AwalDocument17 pagesBagian AwalCitra Monalisa LaoliNo ratings yet

- Concise Selina Solutions Class 9 Maths Chapter 15 Construction of PolygonsDocument31 pagesConcise Selina Solutions Class 9 Maths Chapter 15 Construction of Polygonsbhaskar51178No ratings yet

- Prediction of CBR From Index Properties of Cohesive Soils: Magdi ZumrawiDocument1 pagePrediction of CBR From Index Properties of Cohesive Soils: Magdi Zumrawidruwid6No ratings yet