Professional Documents

Culture Documents

10 1 1 128 1736

Uploaded by

thangaraj_icOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

10 1 1 128 1736

Uploaded by

thangaraj_icCopyright:

Available Formats

214

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS, VOL. CAS-34, NO. 2, FEBRUARY 1987

[2] L. 0. Chua, Stationary principles and potential functions for nonlinear

networks, J. Franklin Inst., vol. 296, no. 2, pp. 91-114, Aug. 1973.

[3] L. 0. Chua and G.-N. Lin, Nonlinear programming without computation, IEEE Trans. Circuits Syst., vol. CAS-31, pp. 182-188, Feb. 1984.

[4] L. 0. Chua and G.-N. Lin, Errata to Nonlinear programmingwithout

computation, IEEE Trans. Circuits Syst., vol. CAS-32, p. 736, July

1985.

[5] L. 0. Chua, Device modeling via nonlinear circuit elements, IEEE

Trans. Circuits Syst., vol. CAS-27,pp. 1014-1044,Nov. 1980.

[6] L. 0. Chua and P. M. Lin, Computer-Aided Analysis of Electronic Circuits:

Algorithms and Computational Techniques. EnglewoodCliffs, NJ: Prentice Hall, 1975,p. 72.

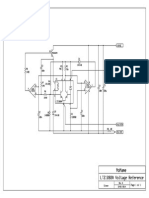

Fig. 6. Canonical nonlinearprogrammingcircuit: dynamic model.

The nonlinear programming circuit of Chua and Lin [3] is

canonical in the sensethat it provides the simplest circuit capable

of solving the nonlinear programming problem. Infinitely many

circuits, not necessarily reciprocal but each obeying the same

unifying stationary principle [2] and having the same dc solution,

can be derived from this network by bijective mappings. The

linear programming problem represents the simplest special case

of the canonical circuit, since it is reciprocal, and one can

therefore apply the stationary cocontent theorem [2] directly.

To demonstrate that the modified Hopfield linear programming network described above does indeed optimize the solution

to the problem as proposed, a network to iniplement the example

of Tank and Hopfield [l] was built, and the solution recorded.

Four linear cost functions were considered, corresponding to

different orientations of the cost plane, and in eaizh case the

experimental and theoretical results are in close agreement and

correspond to stable fixed points of the system.

Modeling Charge Injection in MOS Analog Switches

BING J. SHEU, MEMBER, IEEE,

JE-HURN SHIEH, STUDENT MEMBER, IEEE, AND

MAHESH PATIL, STUDENTMEMBER,IEEE

Abstracf --Charge injection in MOS switches has been analyzed. The

analysis has been extended to the general case of including soorce resistance and source capacitance. Universal plots of percentage channel charge

injected are presented. Normalized variables are used to facilitate usage of

the plots. A small-geometry switch, slow switching rate, and small source

resistance can help reduce the charge injection effect.

I. INTRODUCTION

One major limitation to the accuracy of a sample-and-hold

circuit is the disturbance of the sampled voltage when the MOS

switch turns off. The majority of sample-and-hold circuits are

implemented using MOS technologies because the high input

impedance of MOS devicesperforms excellent holding functions.

When the switch connecting the signal-source node and the

data-holding node is turned on, the sampling function is performed. After the switch is turned off, the data appearing in the

VI. CONCLUDING REMARKS

holding node will be held until the next operation step occurs. In

The reciprocal linear programming circuit of Tank and general, an MOS switch is not an ideal switch. A finite amount of

Hopfield [l], when modified to operate as intended, reduces to mobile charge is stored in the char+el when an MOS transistor is

the canonical nonlinear programming circuit of Chua and Lin [3] on. When the transistor turns off, the channel charge disappears

(of which it represents the si&plest special case), and has been through either the source/drain electrodes or the substrate elecshown to obey the same unifying stationary principle for nonlin- trode. The channel charge being traqsferred to the data node

superposes an error component to the sampled voltage. In adear circuits [2].

The energy function E(u) of Tank and Hopfield [l] is dition to the channel charge, the charge associated with the

simply the total cocontent function of their network. The circuit feedthrough effect of the gate-to-diffusion overlap capacitance

dynamics cause the solution to seek a minimum of E(u) which, enlarges the error voltage [l]. This charge injection phenomenon

for the canonical circuit, corresponds to the desired minimum of was identified in the early stages of switched-capacitor circuit

the cost function +(u). Allowing for nonideal behavior in the real development. Various compensation schemes [2], [3] have been

implementations of this scheme, such as that proposed by Tank used to cancel the switch charge injection to the first order.

Comprehensive understanding and detailed analysis of the switch

and Hopfield, we find that the solution still seeksout a minimum

of the total cocontent function. This may not correspond to the charge injection is needed to improve the accuracy of the MOS

desired solution of the linear programming model considered if circuits. There have been some attempts in the literature to model

the parasitic conductances are not sufficiently small, and the the switch charge injection. MacQuigg [4] made a qualitative

observation and did some SPICE simulation on a simplified case.

nonlinearity not appropriately shaped.

Sheu et al. [l] developed an analytical model corresponding to

ACKNOWLEDGMENT

infinite source capacitance. Experiments .were carried out using

The authors would like to thank T. Parker for his helpful

Manuscript receivedAugust 6,1986; revisedOctober 20, 1986.This research

comments on the manuscript.

REFERENCES

[l]

D. W. Tank and J. J. Hopfield, Simple neural optimization networks:

An A/D converter, signal decision circuit, and a linear programming

circuit, IEEE Trans. Circuits Syst., vol. CAS-33,pp. 533-541, May 1986.

is supported in part by the Defense Advanced ResearchProjects Agency

under Contract MDA903-81-C-0335.

The authors are with the Department of Electrical Engineering,and Information SciencesInstitute, University of SouthernCalifornia, Los Angeles,CA

90089.

IEEE Log Number 8612423.

0098-4094/87/0200-0214$01.00 01987 IEEE

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS, VOL. CAS-34,

215

NO. 2, FEBRUARY 1987

single transistors to verify their model. Wilson et al. [S] inserted a

two-transistor source follower stage between the interested node

and the external prober which shields the loading effect imposed

by the external prober. In this letter, analysis of the general case

of switch charge injection is described. Universal plots of switch

charge injection with normalized variables are included. Experimental results are presented.

II.

ANALYSIS

We assume that the charge pumping phenomenon due to the

capture of channel charge by the interface traps is insignificant in

this analysis. All the channel charge exits through the source and

drain electrodes when the transistor turns off. The circuit schematic corresponding to the general caseof switch charge injection

is shown in Fig. 1. Capacitance C, is the lumped capacitance

existing at the data-holding node. Resistance R, could be the

output resistance of an operational amplifier, while capacitance

Cs could be the lumped capacitance associatedwith the amplifier

output node.

Let Cc represent the total gate capacitance, including both the

channel capacitance and gate-to-source, gate-to-drain overlap

capacitances

Fig. 1. Circuit for analysisof switch chargeinjection.

OL

%h

By following the derivation presented in [l], the KCL law at node

01

-01

A and node B requires

'

'

""'1'

'

'

"""1

'

.l

'

',,I111

10

Fig. 2. Percentageof channel charge injected to the data holding node.

Sourceresistanceis assumedto be infinitely largein the plots.

Gate voltage is assumed to decreaselinearly with time from the

on-value V,

v, = v, - ut

(4)

where U is the falling rate. When the transistor is operated in the

strong inversion region,

OL

ach

1.0

.6

, , ,,,I,

, ,,,,,,

, I,,,

i:,=P(V,,-ut)(v,-v,)

where

.2 -

P=PCO;

and V,,=V,-V--V,,.

(6)

0

.Ol

.l

Here, V,, is the transistor effective threshold voltage including

the body effect. Under the condition (dVG/dtl > Idv,/dtl and

Ido,/dtl, eqs. (2) and (3) simplify to

c,~=-p(v,,-ut)(v,-vs)-~u

(7)

B =tkhE&

(4

2%

%h

1.0

I I I I I I I,

I , I 1, ,I

, I , ,,I

cc

$+c+3(v,,

S

-ut)(v,-u,)+p.

(8)

No closed-form solution to this set of equations can be found.

Numerical integration can be employed to find the results. Fig. 2

shows the calculated percentageof the channel charge injected to

the data-holding node when the source resistance is infinitely

large. A dimensionless quantity B, which is equal to f&.,/m,

01

1

1

IfitJl

10

1

.Ol

.I

has been identified as the driving force of the switch charge

injection effect. A family of curves corresponding to various

B=(VH-VTE)&~

C,/C, ratios have been plotted. When the switch turns off, the

(3

channel charge exits to the signal-source side and the data-holdFig. 3. Percentageof channel charge injected to the data holding node.

ing side under capacitive coupling and resistive conduction. In

(a) Normalized conductanceg = 1 in the plots. (b) Normalized conductance

the fast switching-off conditions, the transistor conduction chang = 5 in the plots.

216

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS, VOL. CAS-34, NO. 2, FEBRUARY 1987

REFERENCES

B.

J.

Sheu

and

C.

Hu,

Switched-induced

error voltage on a switched

PI

capacitor, IEEE J. Solid-State Circuits, vol. SC-19,pp. 519-525, Aug.

1984.

[21 R. E. Suara, P. R. Gray, and D. A. Hodges,All-MOS chargeredistribution analog-to-digitalconversiontechniques:Part II, IEEE J. Solid-State

Circuits, vol. SC-lo, pp. 379-385,Dec. 1975.

[31 R. C. Yen and P. R. Gray, An MOS switched-capacitorinstrumentation

amplifier, IEEE J. So/id-State Circuits, vol. SC-17,pp. lOO8-1013,Dec.

2L

ch

1.0

I 11,111,

- -

theoretical

-8 - + i-k

measured

, ,,,,,,I

I ,rllll-

1982.

[41

.2 -

[51

I

.O'

I '1'1'11

I

.I

I I111111

I

1

I I1'1ll

B

IO

D. MacQuigg, Residual chargeon a switchedcapacitor, IEEE J. Solid

State Circuits, vol. SC-18,pp. 811-813,Dec. 1983.

W. B. Wilson, H. 2. Massoud,E. J. Swanson,R. T. George,Jr., and R. B.

Fair, -Measurement and modeling of charge feedthroughin n-channel

MOS analog switches,IEEE J. of Solid-State Circuits, vol. SC-20, no. 6,

pp. 106-1213, Dec. 1985.

Fig. 4. Measuredand theoreticalchargeinjection results.

nel disappears very quickly. There is not enough time for the

signal-source side charge and data-holding side charge to communicate. Hence, the percentage of charge injection at the dataholding side approaches 50-percent independence of the C/C,

ratio. In the slow switching-off conditions, the communication

between the charge at the signal-source side and at the data-holding side is so strong that it tends to make the final voltages at

both sides equal. This allows the majority of channel charge to go

to the larger capacitance side.

Another important factor in characterizing the switch charge

injection is the relative magnitude of the falling rate compared

with the signal-source time constant R,C,. Normalized conductance g, which is equal to V&-/ZJR,C,, can be used to monitor

this effect. The curves corresponding to two finite g values are

shown in Fig. 3(a) and (b). Source resistance effectively offers a

leakage path for the channel charge during the switch turning-off

period. Hence, a small source resistance will greatly reduce the

amount of charge injected into the data-holding node.

Network Realizability Theory Approach to Stability

of Complex Polynomials

N. K. BOSE AND Y. Q. SHI

Abstruct -In this letter, we briefly point out that concepts in network

realizability theory provide the basis for a unified approach to stability (or,

in general, root distribution) of a polynomial witb complex coefficients.

Very recent results in the area, then, become easily interpretable. The

same approach can be exploited to prove stability results for interval

complex polynomials. The counterpart of the basic continuous system

result is stated for discrete systems, where a complex polynomial is to be

checked for absence of roots on or outside the unit circle. The suggested

procedure has capabilities for generalization to the multivariate case.

Among other advantages, savings in the computational complexity in the

implementation of stability tests on multidimensional filters emerge.

I.

INTRODUCTION

Several papers of recent vintage have originated on the root

clustering and distribution of univariate polynomials with complex coefficients. The results in [l] are concerned with the locaIII. EWERJ~NTAL REsuLTs

The transistors used in the experiments were fabricated using a tion of roots of such polynomials with respect to the principal

3+m CMOS process. The transistor gate-oxide thickness is 50.0 coordinate axis. There, the central part of the argument dwells on

mn, substrate doping is 1016 cmv3, and zero-bias threshold the use of a homotopy approach and Rouches theorem on

voltage is 0.9 V. The percentage charge injection was measured analytic functions. In 121,the complex counterpart of the Routh

table for real polynomials is developed based on the argument

against the gate voltage falIing rate ranging from 1.25X lo6 V/s

to 5 x lo8 V/s. Fig. 4 shows the measured data and theoretical principle in complex variable theory. In both [l] and [2], the

nucleus of the development depends on the decomposition of the

results. Good agreement is found.

given polynomial into the sum of two axially complementary

polynomials [l] (referred to as quasi-real and quasi-imaginary

IV. CONCLUSIONS

polynomials in [2]). In [2], the table might contain imaginary

Charge injection is one of the major limitations to the accuracy elements. In [3], a table to test for the zeros of a complex

of sample-and-hold circuits. Charge injection in MOS switches polynomial in the strict left-half plane is given, but the proof has

has been analyzed. The analysis has been extended to the general not been completed. In [3], incontrast to [2], the elements in the

case, which also includes source resistance and source capaci- table are real. A table of real elements similar but not identical to

tance. This extension makes the results useful for the various the table in [3] is also given in [lo, p. 1791.

Complex polynomials are encountered in several applications

conditions encountered in integrated circuit applications. Plots of

the percentage charge injection corresponding to various normal- [4], [5], [lo, p. 1931.Bivariate complex polynomials are also now

ized parameters are presented. The source resistance effectively

offers a leakage path for the channel charge during the switch

Manuscript received February 25, 1986; revised October 21, 1986. This

turning-off period.

research was supported in part by the National ScienceFoundation under

ACKNOWLEDGMENT

Support from G. Lewicki, V. Tyree, and the MOSIS group is

highly appreciated.

Grant ECS-8415599.,

N. K. Bose is with the Department of Electrical Engineering,Pennsylvania

State University, University Park, PA 16802.

Y. Q. Shi is with the Department of Electrical Engineering,University of

Pittsburgh, Pittsburgh, PA 15261.

IEEE Log Number 8612628.

0098-4094/87/0200-0216$01.00 01987 IEEE

You might also like

- 2602 - Basics of Multiplexers 2 - SlidesDocument10 pages2602 - Basics of Multiplexers 2 - Slidesthangaraj_icNo ratings yet

- An 345Document4 pagesAn 345thangaraj_icNo ratings yet

- IDDQ Failure Diagnosis Is Here: Ron PressDocument2 pagesIDDQ Failure Diagnosis Is Here: Ron Pressthangaraj_icNo ratings yet

- ) $$1 - ADE %ASY: #-/3) $$1 4EST - ETHODOLOGY &undamental #OnceptsDocument32 pages) $$1 - ADE %ASY: #-/3) $$1 4EST - ETHODOLOGY &undamental #OnceptsSainadh YerrapragadaNo ratings yet

- Atmel 2521 AVR Hardware Design Considerations ApplicationNote AVR042Document21 pagesAtmel 2521 AVR Hardware Design Considerations ApplicationNote AVR042thangaraj_icNo ratings yet

- Layout Design GuideDocument41 pagesLayout Design Guidethangaraj_icNo ratings yet

- Thirumanthirambook 1Document39 pagesThirumanthirambook 1jeyankarunanithiNo ratings yet

- 75 How To Stop Worrying and Start Living PDFDocument6 pages75 How To Stop Worrying and Start Living PDFFelimon Megerssa100% (2)

- App 114Document17 pagesApp 114thangaraj_icNo ratings yet

- Day3 FLEXDocument49 pagesDay3 FLEXthangaraj_ic100% (1)

- e2e.ti.comDocument3 pagese2e.ti.comthangaraj_icNo ratings yet

- Analog Layout and Grounding TechniquesDocument7 pagesAnalog Layout and Grounding TechniquesSijo XaviarNo ratings yet

- WWW Planetanalog Com DifferentialSignaling 1Document5 pagesWWW Planetanalog Com DifferentialSignaling 1thangaraj_icNo ratings yet

- App 119Document19 pagesApp 119thangaraj_icNo ratings yet

- P 1779Document4 pagesP 1779thangaraj_icNo ratings yet

- Embeddedgurus ComDocument5 pagesEmbeddedgurus Comthangaraj_icNo ratings yet

- Bhaja Govindam in TamilDocument6 pagesBhaja Govindam in Tamilthangaraj_icNo ratings yet

- Adc DNL INLDocument5 pagesAdc DNL INLNabil IshamNo ratings yet

- WWW Planetanalog Com CurrentsenseDocument6 pagesWWW Planetanalog Com Currentsensethangaraj_icNo ratings yet

- Getting The Best Out of Your Precision Design With Zero Drift Amplifiers Part 2Document7 pagesGetting The Best Out of Your Precision Design With Zero Drift Amplifiers Part 2thangaraj_icNo ratings yet

- 12b.iep Activity1 2013Document28 pages12b.iep Activity1 2013demos2011No ratings yet

- EMC and NoiseDocument47 pagesEMC and Noisethangaraj_icNo ratings yet

- AppendixDocument23 pagesAppendixthangaraj_icNo ratings yet

- Tech Note 107Document4 pagesTech Note 107thangaraj_icNo ratings yet

- Instrumentation AmplifierDocument6 pagesInstrumentation Amplifierilg1No ratings yet

- LTZ Ref BoardDocument1 pageLTZ Ref Boardthangaraj_icNo ratings yet

- Hybrid PCB Stack Up GuideDocument13 pagesHybrid PCB Stack Up Guidethangaraj_icNo ratings yet

- PCBStackups (Ott)Document18 pagesPCBStackups (Ott)krishnamohankola321No ratings yet

- Subsection 4 4 1Document6 pagesSubsection 4 4 1thangaraj_icNo ratings yet

- Agarwal A., Lang J. - Foundations of Analog and Digital Electronic Circuits - Supplemental Sections and Examples - 2005Document136 pagesAgarwal A., Lang J. - Foundations of Analog and Digital Electronic Circuits - Supplemental Sections and Examples - 2005შაქრო ტრუბეცკოიNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Lecture 1Document42 pagesLecture 1raghvendrmNo ratings yet

- ECTE324/8324: Power Engineering 1 Week 9: Lecture 9: Introduction To Power ElectronicsDocument35 pagesECTE324/8324: Power Engineering 1 Week 9: Lecture 9: Introduction To Power ElectronicsPrashant KunaNo ratings yet

- Low Power Design: Prof. A. K. SwainDocument28 pagesLow Power Design: Prof. A. K. SwainSrikanth PasumarthyNo ratings yet

- (Oxford Series in Electrical and Computer Engineering) Allen, Phillip E. - Holberg, Douglas R-CMOS Analog Circuit Design-Oxford University Press, USA (2011)Document783 pages(Oxford Series in Electrical and Computer Engineering) Allen, Phillip E. - Holberg, Douglas R-CMOS Analog Circuit Design-Oxford University Press, USA (2011)ASDFER100% (1)

- Datasheet K4013 - ToshibaSemiconductorDocument6 pagesDatasheet K4013 - ToshibaSemiconductorSofia LugoNo ratings yet

- VIPER17LN-Fixed Frequency 6W High Performance Off Line High Voltage Converter-STDocument33 pagesVIPER17LN-Fixed Frequency 6W High Performance Off Line High Voltage Converter-STbookreader1968No ratings yet

- Solutions Manual To Accompany Cmos Vlsi Design 3rd Edition 9780321149015Document36 pagesSolutions Manual To Accompany Cmos Vlsi Design 3rd Edition 9780321149015clowneryanileness.y7qst100% (51)

- Advanced Logic Synthesis: Multiple Choice QuestionsDocument16 pagesAdvanced Logic Synthesis: Multiple Choice QuestionsmanojkumarNo ratings yet

- Transistor PDFDocument14 pagesTransistor PDFMuhammad JameelNo ratings yet

- Electronics Mechanic PDFDocument41 pagesElectronics Mechanic PDFAn00pSherlock50% (6)

- A 1.5V 1.5GHz CMOS LNADocument16 pagesA 1.5V 1.5GHz CMOS LNAptt3iNo ratings yet

- Ipd06n03la Ipf06n03la Ips06n03la Ipu06n03laDocument12 pagesIpd06n03la Ipf06n03la Ips06n03la Ipu06n03laVictor QueroNo ratings yet

- Xpo CTDocument9 pagesXpo CTBambang GastomoNo ratings yet

- ME2N7002E MatsukiDocument5 pagesME2N7002E MatsukiAnderson BarbosaNo ratings yet

- Mosfet DC Analysis: Semiconductor Field Effect Transistor or MOSFET For ShortDocument41 pagesMosfet DC Analysis: Semiconductor Field Effect Transistor or MOSFET For ShortSaley SaeedNo ratings yet

- Irf 540 NsDocument11 pagesIrf 540 NsLucas PascualNo ratings yet

- Isc N-Channel MOSFET Transistor 2SK2564: DescriptionDocument2 pagesIsc N-Channel MOSFET Transistor 2SK2564: Descriptionluis silvaNo ratings yet

- Boylestad Electronics Multiple Choice Q&a ChapterDocument7 pagesBoylestad Electronics Multiple Choice Q&a ChapterDenaiya Watton LeehNo ratings yet

- NTR4101P Trench Power MOSFET: 20 V, Single P Channel, SOT 23Document6 pagesNTR4101P Trench Power MOSFET: 20 V, Single P Channel, SOT 23MoisesNo ratings yet

- Gate Ece 2003-2019 SolvedDocument900 pagesGate Ece 2003-2019 SolvedAbdul SattarNo ratings yet

- AZ2-UK: Service ManualDocument35 pagesAZ2-UK: Service ManualMinor LizanoNo ratings yet

- Service Manual: Model No. LEC32B33200Document61 pagesService Manual: Model No. LEC32B33200tidchong prakoonmongkoneNo ratings yet

- STRH12P10: Rad-Hard 100 V, 12 A P-Channel Power MOSFETDocument18 pagesSTRH12P10: Rad-Hard 100 V, 12 A P-Channel Power MOSFETHllmanDvlosNo ratings yet

- (Series in Material Science and Engineering) C.K Maiti, S Chattopadhyay, L.K Bera - Strained-Si Heterostructure Field Effect Devices-Taylor & Francis (2007)Document438 pages(Series in Material Science and Engineering) C.K Maiti, S Chattopadhyay, L.K Bera - Strained-Si Heterostructure Field Effect Devices-Taylor & Francis (2007)anup_sky88No ratings yet

- Data Sheet: PMBF4391 PMBF4392 PMBF4393Document10 pagesData Sheet: PMBF4391 PMBF4392 PMBF4393Sergio AmirabileNo ratings yet

- 3001 Elex 1Document10 pages3001 Elex 1DarthRevan23No ratings yet

- Relays and TimersDocument133 pagesRelays and Timerskarstegg100% (1)

- Mosfet AaDocument14 pagesMosfet AaNithish NithiNo ratings yet

- High Sidegated RiverDocument4 pagesHigh Sidegated RiverJulien de TotoNo ratings yet

- Mosfet Switching PCB InductanceDocument5 pagesMosfet Switching PCB InductancerajeshNo ratings yet