Professional Documents

Culture Documents

Inclusao Mult

Uploaded by

Cesar LamounierCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Inclusao Mult

Uploaded by

Cesar LamounierCopyright:

Available Formats

Professor Ney Laert Vilar Calazans -

21/junho/2013

INSTRUES PARA A AULA RELATIVA INCLUSO DO

MULTIPLICADOR NO MIPS MULTICICLO

Descrevem-se abaixo as principais modificaes necessrias para a incluso do multiplicador

serial na implementao VHDL do MIPS multiciclo. Sinais e comandos podem estar faltando e cabe ao

aluno analisar/julgar outras alteraes necessrias. Alm disto inclui-se aqui apenas a instruo MULT e

as suas auxiliares MFLO e MFHI, embora alguns dos novos sinais sejam preparados para uma incluso

futura da instruo DIVU, que fica como trabalho para os alunos.

A) Iniciar criando um projeto no ISE, com os seguintes arquivos:

- mult_div.asm e mult_div.txt (para simulao, arquivo txt lido pelo test bench)

- muti_div.vhd, cdigo VHDL com a multiplicao e diviso seriais

- mips_multiciclo.vhd, cdigo VHDL do processador

- mrStd_tb.vhd, cdigo VHDL do test bench

B) NO PACKAGE:

-

Acrescentar as quatro novas instrues no inst_type: MULTU, MFLO, MFHI.

Acrescentar 2 sinais na micro-instruo:

o start_mult_div : responsvel por inicializar (reset) a multiplicao ou a diviso

(no futuro);

o whilo : responsvel por comandar a escrita nos registradores HI e LO.

C) BLOCO DE DADOS: alterar o bloco de dados conforme o desenho abaixo:

-

Localizar o terceiro estgio do bloco de dados e

instanciar o multiplicador e o divisor. Exemplo de cdigo:

multi1:

entity work.multiplica

generic map(N=>32)

port map(clock=>ck, M1=>RA, M2=>RB,

start=>uins.start_mult_div,

produto=>produto, endop=> end_mult);

Acrescentar 1 sinal de sada no bloco de dados:

end_mult: sinaliza final da multiplicao. No

futuro, algo similar deve ser feito para a diviso.

Criar os multiplexadores para seleo das entradas

LO e HI

-

Criar os registradores LO e HI. Estes so como

qualquer registrador de 32 bits do MIPS (PC, IR, etc.).

Exemplo de cdigo para o registrador LO:

REG_LO: entity work.regnbit port map(ck=>ck,

rst=>rst, ce=>uins.whilo, D=>low, Q=>LO);

A declarao dos sinais intermedirios do desenho

devem ser includa entre a architecture e o begin do bloco de

dados/controle.

Para as instrues MFLO e MFHI, localizar o

multiplexador que implementa o sinal result e alter-lo

conforme necessrio (ver a figura ao lado). No esquecer de

alterar, no quinto estgio, o multiplexador que controla o sinal

de escrita no banco de registradores (sinal adD).

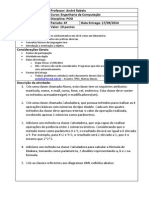

D) BLOCO DE CONTROLE: alterar o bloco de dados conforme o desenho abaixo:

Acrescentar 1 sinal de entrada no bloco de controle:

o end_mult: sinaliza final da multiplicao;

Iniciar a alterao do bloco de controle decodificando as quatro novas instrues. Vejam a

nova mquina de estados abaixo. Ela referencia alguns sinais que ainda no existem, tais como

End_div. Omita o que for necessrio na sua implementao.

Reset=1

Reset=1

(todos os

registradores

so zerados)

Sidle

Reset=0

Sfetch

CY1

Sreg

CY2

start_mult_div se

IR=MULTU/DIV

IR=(MULTU e End_mul=0) ou

(DIVU e End_div=0)

(IR=MULTU e End_mul=1)

ou (IR=DIVU e End_div=1)

Salu

wAlu

wpc, whilo

Caso geral

IR=LBU/

LW

Swbk

wreg

wpc

Sld

ce

wmdr

IR=SB/

SW

Sst

rw0, ce, wpc

bw0 se IR=SB

IR =J/JAL/JALR/JR /BEQ/

BGEZ/BLEZ/BNE

Ssalta

wpc

wreg se

IR=JAL/JALR

Alterar o estado SALU para considerar a espera pelo final ou da multiplicao ou da diviso.

Importante: deve-se colocar o sinal end_mult na lista de sensitividade (porqu?):

process(PS, i, end_mult)

Trs sinais de escrita em registradores precisam ser alterados e/ou criados:

o uins.wpc: precisa tambm ser ativado quando (PS=salu and i=MULTU and

o

o

end_mult='1') or (PS=salu and i=DIVU and end_div='1');

uins.start_mult_div: deve ser ativado quando PS=Sreg and (i=MULTU or

i=DIVU);

uins.whilo: deve ser ativado quando (PS=salu and i=MULT and

end_mult='1');

E) Arquivo top: acertar os comandos port map relativos ao bloco de dados e controle, levando-se

em considerao os novos sinais da interface de comunicao.

F) Exemplo de simulao, utilizando o arquivo de teste fornecido:

Descrio dos eventos:

1 Decodificao de uma instruo de multiplicao e a respectiva ativao do sinal

uins.start_mult_div;

2 Final da multiplicao e escrita dos resultados da multiplicao nos registradores HI e LO;

3 Execuo das instrues MFLO e MFHI para escrita nos registradores 16 ($s0) e 17 ($s1).

Apresentar para o professor o cdigo VHDL e a

simulao operando corretamente.

You might also like

- Planilha Calculo Traço ConcretoDocument1 pagePlanilha Calculo Traço ConcretoManfrinne123491% (22)

- Produtividade - Tcpo PreenchidaDocument2 pagesProdutividade - Tcpo PreenchidaAna Carolina Melo Freire de Andrade100% (4)

- MCC Exercícios+resolvidosDocument6 pagesMCC Exercícios+resolvidoshiltonbarbosa1218100% (3)

- Projeto e Implementação de Um Relógio Digital Utilizando PLDDocument5 pagesProjeto e Implementação de Um Relógio Digital Utilizando PLDWeslley AlmeidaNo ratings yet

- Extrator de DadosDocument25 pagesExtrator de DadoslfportoNo ratings yet

- DTFT Prob PDFDocument2 pagesDTFT Prob PDFCesar LamounierNo ratings yet

- Carlos Sebastião Andriani - Gestão 3.0Document2 pagesCarlos Sebastião Andriani - Gestão 3.0Cesar LamounierNo ratings yet

- Dossiê: Livro Didático 'Por Uma Vida Melhor' (Por ALAB)Document101 pagesDossiê: Livro Didático 'Por Uma Vida Melhor' (Por ALAB)SylviaRodriguesAlmeida0% (1)

- Importante Trabalho de IntroducaoDocument6 pagesImportante Trabalho de IntroducaoCesar LamounierNo ratings yet

- Lingua GensDocument13 pagesLingua GensCesar LamounierNo ratings yet

- Small TalkDocument3 pagesSmall TalkCesar LamounierNo ratings yet

- Controle Impressoes GraficosDocument1 pageControle Impressoes GraficosCesar LamounierNo ratings yet

- Aula 02Document39 pagesAula 02Cesar LamounierNo ratings yet

- Palestras Do Matutino - 05.09Document1 pagePalestras Do Matutino - 05.09Cesar LamounierNo ratings yet

- Tp01 - 2014-Antecao Data EntregaDocument4 pagesTp01 - 2014-Antecao Data EntregaCesar LamounierNo ratings yet

- Sensores IndustriaisDocument23 pagesSensores IndustriaisEduardo CazonNo ratings yet

- PPC 900 - Manual - Software de Teste de Comunicação PPCDocument11 pagesPPC 900 - Manual - Software de Teste de Comunicação PPCthvvieiraNo ratings yet

- Ensaio de PeneiramentoDocument8 pagesEnsaio de PeneiramentoVictor NascimentoNo ratings yet

- Manual Do Usuario TV Way+ V2.4Document57 pagesManual Do Usuario TV Way+ V2.4Cesar LamounierNo ratings yet

- Determinaçao Da Composiçao Granulometrica - Agregado Graúdo.Document10 pagesDeterminaçao Da Composiçao Granulometrica - Agregado Graúdo.claralisieNo ratings yet

- Agua Fria 2010Document71 pagesAgua Fria 2010priscilagodoyNo ratings yet

- Dosagemdoconcreto2ano 100713125928 Phpapp02Document64 pagesDosagemdoconcreto2ano 100713125928 Phpapp02EdmilsontedoroNo ratings yet

- Determinaçao Da Composiçao Granulometrica - Agregado Graúdo.Document10 pagesDeterminaçao Da Composiçao Granulometrica - Agregado Graúdo.claralisieNo ratings yet

- 07 - Metodo Dner - DimensionamentoDocument8 pages07 - Metodo Dner - DimensionamentoCesar LamounierNo ratings yet

- Traço de ConcretoDocument1 pageTraço de ConcretoCesar LamounierNo ratings yet

- Manual BR SAP2000Document22 pagesManual BR SAP2000Iverson_SiebertNo ratings yet

- Manual BR SAP2000Document22 pagesManual BR SAP2000Iverson_SiebertNo ratings yet

- Lista 10 PDFDocument2 pagesLista 10 PDFCesar LamounierNo ratings yet

- Programação e Controle de ObrasDocument95 pagesProgramação e Controle de ObraslucastlpNo ratings yet

- Fundaçoes I - Muro de ArrimoDocument21 pagesFundaçoes I - Muro de ArrimoCesar LamounierNo ratings yet

- Programação e Controle de ObrasDocument95 pagesProgramação e Controle de ObraslucastlpNo ratings yet

- Manual Ventilador Teto SPIRIT Bluetooth v3 (Pag Juntas)Document11 pagesManual Ventilador Teto SPIRIT Bluetooth v3 (Pag Juntas)Maycon RapozaNo ratings yet

- Metodologia Da Pesquisa Científica - Como Usar Base de Dados Da BibliotecaDocument2 pagesMetodologia Da Pesquisa Científica - Como Usar Base de Dados Da BibliotecaLuísFernandoRibeiroDeSouzaAlvesNo ratings yet

- Caracteristicas Intelbras Mibo IC4Document7 pagesCaracteristicas Intelbras Mibo IC4Ricardo LandellNo ratings yet

- Ingresso RBD - SOY REBELDE TODocument1 pageIngresso RBD - SOY REBELDE TOpcpivetezada22No ratings yet

- Desproteger Planilhas 01Document5 pagesDesproteger Planilhas 01MuLiloNo ratings yet

- Guia Do Usuário - Smart TV LGDocument211 pagesGuia Do Usuário - Smart TV LGSergio100% (1)

- Programação at Informática Web UC 14710 - Ficha 5Document2 pagesProgramação at Informática Web UC 14710 - Ficha 5Antonio CastellanosNo ratings yet

- Tutorial para Atualização Do AZBOXDocument3 pagesTutorial para Atualização Do AZBOXMiguel ClementeNo ratings yet

- EBAC - Profissão - Cientista DadosDocument10 pagesEBAC - Profissão - Cientista Dadosednei.limaNo ratings yet

- 07 Projeto de PesquisaDocument4 pages07 Projeto de PesquisaNilson MoriNo ratings yet

- Projeto Basico Rede LocalDocument9 pagesProjeto Basico Rede LocalJosé HenriqueNo ratings yet

- 71307manual de Trabalho MHDX 1016Document38 pages71307manual de Trabalho MHDX 1016Hélio AssunçãoNo ratings yet

- Quer Publicar Artigos No LinkedIn Agora Já PodeDocument4 pagesQuer Publicar Artigos No LinkedIn Agora Já PodeHelena Dias - Community Manager PortugalNo ratings yet

- Planificacao CEF TIC PDFDocument10 pagesPlanificacao CEF TIC PDFjocacoNo ratings yet

- Projeto - Sistema de Controle de Clínica MédicaDocument168 pagesProjeto - Sistema de Controle de Clínica MédicaRonny MartinsNo ratings yet

- Pesquisa Bot oDocument12 pagesPesquisa Bot oNatan MarquesNo ratings yet

- A Classe Abntex2: Documentos Técnicos e Científicos Brasileiros Compatíveis Com As Normas ABNTDocument45 pagesA Classe Abntex2: Documentos Técnicos e Científicos Brasileiros Compatíveis Com As Normas ABNTEdson VigilatoNo ratings yet

- Treinamento - Básico - Streaming Técnico KMG MS - V6Document80 pagesTreinamento - Básico - Streaming Técnico KMG MS - V6Marlon Alves SantosNo ratings yet

- Quiz - Semana 04Document8 pagesQuiz - Semana 04Shirleidy FreireNo ratings yet

- Aula 10 - TRF 1 RegiãoDocument7 pagesAula 10 - TRF 1 Regiãowess_britoNo ratings yet

- Prova WordDocument5 pagesProva WordEduardo YagamiNo ratings yet

- Como Criar Uma Instalação Silenciosa de Um Programa Com SerialDocument1 pageComo Criar Uma Instalação Silenciosa de Um Programa Com SerialAnderson LeonardoNo ratings yet

- Manual Do Usuário Da L355Document192 pagesManual Do Usuário Da L355Fernando Carmo VianaNo ratings yet