Professional Documents

Culture Documents

Sem Avi Kaj

Uploaded by

avinash_yuvarajOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Sem Avi Kaj

Uploaded by

avinash_yuvarajCopyright:

Available Formats

DIGITAL ELECTRONICS, M.

TECH (PART TIME)

INPUT CIRCUITS

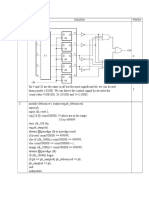

A simple input circuit consisting of a transmission gate activated by an enable (E) signal

and its complement is shown in Fig1

FIG1: (a) Input series transmission gate circuit and (b) its symbolic representation.

The incoming signal A is fed into the transmission gate through the protection network

(PN) from the bonding pad Of the chip. The enable signal is generated on-chip and

controls the gating of the input signal as

* X=A, when E=0

* X = high-impedance state, otherwise

Any unused chip input terminals should be tied to VDD or Vss using pull-up or pulldown resistors externally. Some input pad circuit modules have a built-in internal pull-up

or pull-down resistor or active load (normally-on transistor) with a resistance of 200 k

to 1 M

FIG2:. Inverting input circuit with (a) protection network, and (b) symbolic view.

AVINASH. N. J

INPUT CIRCUITS

DIGITAL ELECTRONICS, M.TECH (PART TIME)

FIG2 shows an inverting input circuit consisting of the protection network and a CMOS

inverter Typical values for VIL and VIH are 0.3VDD and 0.7 VDD, respectively for about

30% noise margins. This basic input circuit can be designed to receive TTL signals for

CMOS logic circuits by adjusting the ratio of the channel widths in Pmos and nMOS

transistors in the inverter. Figure 3 shows the principle of level shifting from TTL to

CMOS logic. In TTL, the worst-case output signal levels are

. VOL= 0.8 V

. VOH=2.0V

Therefore, input voltages less than or equal to 0.8 V should be interpreted low and input

voltages greater than or equal to 2.0 V should be interpreted high. After the input

protection circuit, the incoming signals have to be level-shifted to a desirable level,

depending on their voltage levels. For instance, if the incoming signal is from a TTL

driver, then its low voltage can be as high as 0.8 V and its high output voltage can be as

low as 2.0 V. Therefore a careful level shifting has to be done to translate such

logic levels to corresponding MOS gate voltage levels as shown in Fig. 3.

FIG 3: (a) TTL to CMOS level characteristic curve shifting and (b) the corresponding

voltage transfer

The level shifting between a TTL driver and a CMOS gate can be achieved by properly

designing the ratio between pMOS and nMOS transistors of the receiving CMOS inverter

gate. A practical method is to adjust the transistor ratio in the inverter gate such that the

saturation voltage at which both transistors operate in saturation region is set at the

midpoint between 0.8 V and 2.0 V. By using first-level models of MOS transistors, it can

be shown that the saturation voltage of the inverter gate can be expressed by

AVINASH. N. J

INPUT CIRCUITS

DIGITAL ELECTRONICS, M.TECH (PART TIME)

From these two equations, we find that

For example, if n = 3p and VTN, = -VTP= 1.0 V and VDD = 5 V, then in order to achieve

the nMOS-to-pMQS ratio must be

From the above calculation, we determine that r = 6.5 and

where VOUT , satisfies the following current equation:

Combining these two equations, we obtain

Vout = 4.97 V

AVINASH. N. J

INPUT CIRCUITS

DIGITAL ELECTRONICS, M.TECH (PART TIME)

and, hence

Likewise,

where VOut satisfies the following current equation

Combining these two equations, we obtain

Solving for VOUT and VIH yields:

VOUT= 0 206 V and VIH = 1.47 V

This design appears to meet the design objective of a level-shifting CMOS inverter,

providing logic 1 output level for TTL input voltages of up to 0.8 V (less than

VIL= 1.07V) and logic 0 output level for TTL input voltages not less than 2.0 V. The

output voltage of 0.206 V at Vin = 1.47 V is much less than the n-channel threshold

voltages of the next stage. However, to assure that the circuit would function properly

under all circumstances, careful circuit simulation should be performed by considering

the variations in process conditions, device temperature, and power supply voltage level.

Note that due to process variations, some chips can have strong pMOS (PH)-weak nMOS

(NL), or weak pMOS (PL)-strong nMOS (NH) combinations for which the level-shift

circuit performance would be somewhat different. This variation is illustrated in Fig. 4

AVINASH. N. J

INPUT CIRCUITS

DIGITAL ELECTRONICS, M.TECH (PART TIME)

FIG 4: Variation of the level-shifter VTC due to process variations

Figure 5, shows another non-inverting TTL level-shifting circuit. In this circuit, the level

shifting is accomplished in the first stage, which is followed by the second-stage inverter.

FIG 5: (a) Non-inverting TTL level-shifting circuit and (b) its symbolic view.

Figure 6, shows an input pad circuit with a Schmitt trigger circuit and a 70-k pull-down

resistor. This circuit provides a negative-going logic threshold voltage of 1 V and a

positive-going logic threshold voltage of 4 V, for a 5-V power supply.

AVINASH. N. J

INPUT CIRCUITS

DIGITAL ELECTRONICS, M.TECH (PART TIME)

FIG 6: (a) Input pad circuit with Schmitt trigger and (b) its symbolic view.

.

AVINASH. N. J

INPUT CIRCUITS

You might also like

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- MathsDocument2 pagesMathsavinash_yuvarajNo ratings yet

- Assignment 2 III BDocument3 pagesAssignment 2 III Bavinash_yuvarajNo ratings yet

- Course SyllabusDocument10 pagesCourse Syllabusavinash_yuvarajNo ratings yet

- 2021-2022 Final Individual TTDocument75 pages2021-2022 Final Individual TTavinash_yuvarajNo ratings yet

- 19ELE35 QUIZ 3C Quiz 2Document1 page19ELE35 QUIZ 3C Quiz 2avinash_yuvarajNo ratings yet

- Assignment I - III BDocument3 pagesAssignment I - III Bavinash_yuvarajNo ratings yet

- Ece Second Year 2021-2022Document77 pagesEce Second Year 2021-2022avinash_yuvarajNo ratings yet

- Digital Signal Processing LabDocument36 pagesDigital Signal Processing Labavinash_yuvarajNo ratings yet

- Assignment 2 III BDocument3 pagesAssignment 2 III Bavinash_yuvarajNo ratings yet

- EECS 373: Design of Microprocessor-Based SystemsDocument29 pagesEECS 373: Design of Microprocessor-Based Systemsavinash_yuvarajNo ratings yet

- Q.No Solution Marks 1Document4 pagesQ.No Solution Marks 1avinash_yuvarajNo ratings yet

- Digital Design: An Embedded Systems Approach Using Verilog: Sequential BasicsDocument73 pagesDigital Design: An Embedded Systems Approach Using Verilog: Sequential Basicsavinash_yuvarajNo ratings yet

- Lecture A 2.Fsm ReviewDocument14 pagesLecture A 2.Fsm Reviewavinash_yuvarajNo ratings yet

- Org 00H MOV C, P1.7 ANL C,/P1.6 MOV P1.5, C MOV C, P1.7 CPL C ANL C, P1.6 MOV P1.4, C ORL C, P1.5 MOV P1.3, C MOV C, P1.7 ANL C, P1.6 MOV P1.2, C ENDDocument1 pageOrg 00H MOV C, P1.7 ANL C,/P1.6 MOV P1.5, C MOV C, P1.7 CPL C ANL C, P1.6 MOV P1.4, C ORL C, P1.5 MOV P1.3, C MOV C, P1.7 ANL C, P1.6 MOV P1.2, C ENDavinash_yuvarajNo ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- APU CSLLT - 5 - RegistersDocument51 pagesAPU CSLLT - 5 - RegistersAli AtifNo ratings yet

- ATmega32A DataSheet Complete DS40002072ADocument339 pagesATmega32A DataSheet Complete DS40002072ALê Ngọc LongNo ratings yet

- 8255 Peripheral Study CardDocument2 pages8255 Peripheral Study CardAmber ClarkNo ratings yet

- Typical Functional Diagrams Rev0C PDFDocument76 pagesTypical Functional Diagrams Rev0C PDFñao manaoNo ratings yet

- Design of Binary Multiplier Using Adders-3017 PDFDocument5 pagesDesign of Binary Multiplier Using Adders-3017 PDFAdrian Walter JavierNo ratings yet

- Monostable MultivibratorDocument2 pagesMonostable MultivibratorsNo ratings yet

- 192 09268 0 M306nafgtfp PDFDocument295 pages192 09268 0 M306nafgtfp PDFpolitrukNo ratings yet

- Microproject of DteDocument27 pagesMicroproject of DteANON70% (10)

- Digital Systems: Dr.-Ing. Erwin Sitompul President UniversityDocument22 pagesDigital Systems: Dr.-Ing. Erwin Sitompul President UniversityUmo MedsosNo ratings yet

- SoCT SlidesDocument157 pagesSoCT SlidesLernen Deutsch A1No ratings yet

- LAB REPORT 1 Digital SystemDocument4 pagesLAB REPORT 1 Digital SystemKhairul Naim100% (1)

- Data Sheet: HEF4520B MSIDocument7 pagesData Sheet: HEF4520B MSIGoodLookingPirateNo ratings yet

- Tsu and TH - PdfsdfsdsaDocument15 pagesTsu and TH - PdfsdfsdsaasfagehejhdhdsgdfsdfgNo ratings yet

- Chapter 04 Computer Architecture and DDocument95 pagesChapter 04 Computer Architecture and DPooja VashisthNo ratings yet

- EVB-I94124ADI User ManualDocument19 pagesEVB-I94124ADI User ManualÖzcan BıyıkNo ratings yet

- Fulton ModSync Wiring DiagramDocument3 pagesFulton ModSync Wiring DiagramjrodNo ratings yet

- 74HC02 74HCT02: 1. General DescriptionDocument12 pages74HC02 74HCT02: 1. General Descriptionforeman pemudaNo ratings yet

- Experiment - 09: Aim: Tools: Methodology: Theory: Ring CounterDocument6 pagesExperiment - 09: Aim: Tools: Methodology: Theory: Ring CounteratulNo ratings yet

- Microprocessor 8085 Pin ConfigurationDocument3 pagesMicroprocessor 8085 Pin ConfigurationAvinash JainNo ratings yet

- Digital Logic Design Lab Manual: Department of Electrical Engineering, Fast-Nu, LahoreDocument115 pagesDigital Logic Design Lab Manual: Department of Electrical Engineering, Fast-Nu, LahoreQasim LodhiNo ratings yet

- FPGA PresentationDocument57 pagesFPGA PresentationPanku RangareeNo ratings yet

- Digital Electronics Lab ManualDocument57 pagesDigital Electronics Lab ManualComputer Sc & BCA DepartmentNo ratings yet

- MC14500B Industrial Control Unit Handbook 1977Document113 pagesMC14500B Industrial Control Unit Handbook 1977FLAVIO100% (1)

- Sri Balaji Resume-Full TimeDocument2 pagesSri Balaji Resume-Full TimeJate NirmalNo ratings yet

- Basic Computer Organization & DesignDocument45 pagesBasic Computer Organization & DesignSalman HadiNo ratings yet

- De Lab ManualDocument53 pagesDe Lab ManualgopiikrishnaNo ratings yet

- Lab 9 (Group 4) - 1Document11 pagesLab 9 (Group 4) - 1MUHAMMAD HUZAIFANo ratings yet

- 27 C 128Document12 pages27 C 128andrewNo ratings yet

- MCP23018/MCP23S18 I/O-extenderDocument56 pagesMCP23018/MCP23S18 I/O-extenderLarsO2No ratings yet

- Ci Placa Consul CWC 22Document60 pagesCi Placa Consul CWC 22Antonio MacedoNo ratings yet