Professional Documents

Culture Documents

Arquitecturas CISC y RISC

Uploaded by

Grety CcorahuaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Arquitecturas CISC y RISC

Uploaded by

Grety CcorahuaCopyright:

Available Formats

UNIVERSIDAD ANDINA DEL CUSCO

"Ao de la Diversificacin Productiva y del Fortalecimiento de la Educacin"

FACULTAD DE INGENIERA

ESCUELA PROFESIONAL DE INGENIERIA DE SISTEMAS

ARQUITECTURAS CISC Y

RISC

INTEGRANTES:

Anaid Jimenez Moreano

009100950c

Grety Ccorahua Yupaiccana

012100600G

Jean Marco Perez Huaman

011200086D

Felipe Herrera Huama

013100380f

Xavier Inty Curi Hualpacuna

UNIVERSIDAD ANDINA DEL CUSCO

NDICE

Introduccin....Pg. 2

1. Marco TericoPg. 3

1.1 Historia..Pg. 3

1.2 Definicin..Pg. 4

1.2.1Arquitectura CISC.....Pg. 7

1.2.2 Arquitectura RISC....Pg. 10

1.3 Diferencias entre CISC y RISC.....Pg. 13

1.4 Papel de los compiladores en un sistema RISC.Pg. 14

Conclusin...Pg. 15

Bibliografa.. Pg. 16

UNIVERSIDAD ANDINA DEL CUSCO

Introduccin

La evolucin de la arquitectura de computadores ha mostrado una tendencia

desde principios hacia una complejidad creciente del lenguaje ofrecido. Sin

embargo en 1975, los arquitectos de computadores de IBM cuestionaron, con

la construccin del 801, que la creciente complejidad fuera el camino ms

apropiado para seguir una mejor relacin coste/ rendimiento. Ya que IBM no

aireo demasiado en esta nueva filosofa, no tuvo gran recuperacin hasta que a

principios de los 80 Hennessy y Patterson (en Berkeley y Stanford) retomaron

la idea y dieron lugar al movimiento RISC (Reduced Instruction Set Computer)

en oposicin a los tradicionales ordenadores con complejos juegos de

instrucciones CISC(Complex Intruction Set Computer).

1.- Marco Terico

1.1

Historia

UNIVERSIDAD ANDINA DEL CUSCO

Al principio de la era electrnica de los ordenadores, la memoria era un

recurso muy costoso. Esto dio a la idea de que la mejor arquitectura de un

ordenador era la que permita minimizar los programas (en trminos de

memoria ocupada). Otros factores que tambin se utilizaban para medir la

calidad de una arquitectura era el nmero de bits por instruccin y la cantidad

de bits de instrucciones y de datos que se alimentaban durante la ejecucin de

programa.

Debido a la introduccin de la microprogramacin (que permiti que los

complejos circuitos lgicos de la unidad de control se reemplazaran por una

memoria con un microprograma), se volvi mucho ms barato sustituir

funciones que antes se realizaban mediante una serie de instrucciones, por

instrucciones ms complejas que entenda y ejecutaba el microprograma. Al

tener un programa menos instrucciones se conseguan dos cosas:

Menos espacio de memoria

Menos instrucciones que alimentar desde la lenta memoria, luego se

aumentaba la velocidad de ejecucin.

No obstante a medida que se incorporaban ms y ms funciones al micro

cdigo, el tamao de la microprograma fue creciendo.

Otro argumento para implementar funciones complejas de micro cdigo era que

estas funciones acortaban la gran distancia semntica que haba entre el

lenguaje mquina y los lenguajes de alto nivel, ofreciendo un mejor soporte

para los compiladores de estos lenguajes. Si la sentencia de un lenguaje de

alto nivel se poda traducir a unas nicas instrucciones mquina, la

construccin de los compiladores sera mucho ms sencilla.

UNIVERSIDAD ANDINA DEL CUSCO

2.2 Definicin

Veamos primero cual es el significado de los trminos CISC y RISC:

CISC (complex instruction set computer) Computadoras con un conjunto

de instrucciones complejo.

RISC (reduced instruction set computer) Computadoras con un conjunto

de instrucciones reducido.

Los atributos complejo y reducido describen las diferencias entre los dos

modelos de arquitectura para microprocesadores solo de forma superficial. Se

requiere de muchas otras caractersticas esenciales para definir los RISC y los

CISC tpicos. An ms, existen diversos procesadores que no se pueden

asignar con facilidad a ninguna categora determinada.

As, los trminos complejo y reducido, expresan muy bien una importante

caracterstica definitiva, siempre que no se tomen solo como referencia las

instrucciones, sino que se considere tambin la complejidad del hardware del

procesador.

UNIVERSIDAD ANDINA DEL CUSCO

Con tecnologas de semiconductores comparables e igual frecuencia de reloj,

un procesador RISC tpico tiene una capacidad de procesamiento de dos a

cuatro veces mayor que la de un CISC, pero su estructura de hardware es tan

simple, que se puede realizar en una fraccin de la superficie ocupada por el

circuito integrado de un procesador CISC.

Esto hace suponer que RISC reemplazar al CISC, pero la respuesta a esta

cuestin no es tan simple ya que:

Para aplicar una determinada arquitectura de microprocesador son

decisivas las condiciones de realizacin tcnica y sobre todo la

rentabilidad, incluyendo los costos de software.

Existan y existen razones de compatibilidad para desarrollar y utilizar

procesadores de estructura compleja as como un extenso conjunto de

instrucciones.

La meta principal es incrementar el rendimiento del procesador, ya sea

optimizando alguno existente o se desee crear uno nuevo. Para esto se deben

considerar tres reas principales a cubrir en el diseo del procesador y estas

son:

La arquitectura.

La tecnologa de proceso.

El encapsulado.

La tecnologa de proceso, se refiere a los materiales y tcnicas utilizadas en la

fabricacin del circuito integrado, el encapsulado se refiere a cmo se integra

un procesador con lo que lo rodea en un sistema funcional, que de alguna

manera determina la velocidad total del sistema.

Aunque la tecnologa de proceso y de encapsulado son vitales en la

elaboracin de procesadores ms rpidos, es la arquitectura del procesador lo

que hace la diferencia entre el rendimiento de una CPU (Control Process Unit)

y otra. Y es en la evaluacin de las arquitecturas RISC y CISC donde

centraremos nuestra atencin.

Dependiendo de cmo el procesador almacena los operando de las

instrucciones de la CPU, existen tres tipos de juegos de instrucciones:

1. Juego de instrucciones para arquitecturas basadas en pilas.

2. Juego de instrucciones para arquitecturas basadas en acumulador.

3. Juego de instrucciones para arquitecturas basadas en registros.

Las arquitecturas RISC y CISC son ejemplos de CPU con un conjunto de

instrucciones para arquitecturas basadas en registros .

UNIVERSIDAD ANDINA DEL CUSCO

I= N de instrucciones

C=N de ciclos por instruccin

Tc= Duracin de cada ciclo.

El propsito de las arquitecturas tradicionales CISC es minimizar esta

expresin haciendo ms pequeo el nmero d instrucciones a base de

instrucciones ms potentes y complejas.

UNIVERSIDAD ANDINA DEL CUSCO

2.2.1 Arquitecturas CISC:

La microprogramacin es una caracterstica importante y esencial de casi todas

las arquitecturas CISC.

La microprogramacin significa que cada instruccin de mquina es

interpretada por una microprograma localizada en una memoria en el circuito

integrado del procesador.

En la dcada de los sesentas la microprogramacin, por sus caractersticas,

era la tcnica ms apropiada para las tecnologas de memorias existentes en

esa poca y permita desarrollar tambin procesadores con compatibilidad

ascendente. En consecuencia, los procesadores se dotaron de poderosos

conjuntos de instrucciones.

Las instrucciones compuestas son decodificadas internamente y ejecutadas

con una serie de microinstrucciones almacenadas en una ROM interna. Para

esto se requieren de varios ciclos de reloj (al menos uno por microinstruccin).

Buscando aumentar la velocidad del procesamiento, se descubri en base a

experimentos que, con una determinada arquitectura de base, la ejecucin de

programas resultaban ser ms eficientes. Debido a un conjunto de

instrucciones simplificado, stas se pueden

implantar por hardware

directamente en la CPU.

20% de las instrucciones ocupa el 80% del tiempo total de ejecucin. Existen

secuencias de instrucciones simples que obtienen el mismo resultado que

secuencias complejas predeterminadas.

Los microprocesadores CISC tienen un conjunto de instrucciones que se

caracteriza por ser muy amplio y permitir operaciones complejas entre

operandos situados en la memoria o en los registros internos.

Este tipo de arquitectura dificulta el paralelismo entre instrucciones, por lo que

en la actualidad la mayora de los sistemas CISC de alto rendimiento

implementan un sistema que convierte dichas instrucciones complejas en

varias instrucciones simples, llamadas generalmente microinstrucciones.

La microprogramacin es una caracterstica importante y esencial de casi todas

las arquitecturas CISC. La microprogramacin significa que cada instruccin de

mquina es interpretada por un microprograma localizado en una memoria en

el circuito integrado del procesador. Las instrucciones compuestas son

decodificadas internamente y ejecutadas con una serie de microinstrucciones

almacenadas en una ROM interna. Para esto se requieren de varios ciclos de

reloj, al menos uno por microinstruccin. Es as entonces como los chips CISC

utilizan comandos que incorporan una gran diversidad de pequeas

instrucciones para realizar una nica operacin.

Cuando el sistema operativo o una aplicacin requieren de una de

estas acciones, enva al procesador el nombre del comando para realizarla

junto con el resto de informacin complementaria que se necesite. Pero cada

uno de estos comandos de la ROM del CISC varan de tamao y, por lo tanto,

UNIVERSIDAD ANDINA DEL CUSCO

el chip debe en primer lugar verificar cuanto espacio requiere el comando para

ejecutarse y poder as reservrselo en la memoria interna. Adems, el

procesador debe determinar la forma correcta de cargar y almacenar el

comando, procesos ambos que ralentizan el rendimiento del sistema.

Ventajas:

Objetivo: ISA amplio y verstil

Gran cantidad de instrucciones.

Instrucciones complejas.

Gran cantidad de modos de direccionamiento.

Soporta gran cantidad de tipos de datos.

Implementacin de instrucciones de alto nivel lo ms directamente posible.

Reduccin del tiempo de ejecucin de instrucciones complejas por medio de

Implementacin directa en hardware.

Compatibilidad con miembros anteriores de la familia.

Micro arquitectura ms compleja.

Instrucciones de longitud variable.

Desventajas:

Poco uso de las instrucciones y direccionamientos complejos.

Poco aprovechamiento de parte de los compiladores: no es fcil encontrar la

mejor instruccin para ejecutar una tarea.

Baja densidad de cdigo.

Accesos a memoria disminuyen velocidad de ejecucin.

Caractersticas:

Duracin en la ejecucin de las instrucciones no es homogneo.

Instrucciones multiciclo

UNIVERSIDAD ANDINA DEL CUSCO

Utiliza memoria de microprograma.

Tienen un conjunto de instrucciones que se caracteriza por ser muy

amplio y permitir operaciones complejas.

Ejemplos:

Motorola 68000 ( microprocesador CISC 16/32 -bit)

Zilog Z80 ( microprocesador de 8 bits)

Intel x86

AMD x86-64

2.2.2 Arquitecturas RISC

Es

un

tipo

de

diseo

de CPU generalmente

utilizado

en microprocesadores o micro controladores con las siguientes caractersticas

fundamentales:

1. Instrucciones de tamao fijo y presentado en un reducido nmero de

formatos.

2. Slo las instrucciones de carga y almacenamiento acceden a la memoria

de datos.

UNIVERSIDAD ANDINA DEL CUSCO

Adems estos procesadores suelen disponer de muchos registros de propsito

general.

RISC es una filosofa de diseo de CPU para computadora que est a favor de

conjuntos de instrucciones pequeas y simples que toman menor tiempo para

ejecutarse. El tipo de procesador ms comnmente utilizado en equipos de

escritorio, el x86, est basado en CISC en lugar de RISC, aunque las versiones

ms nuevas traducen instrucciones basadas en CISC x86 a instrucciones ms

simples basadas en RISC para uso interno antes de su ejecucin.

La idea fue inspirada por el hecho de que muchas de las caractersticas que

eran incluidas en los diseos tradicionales de CPU para aumentar la velocidad

estaban siendo ignoradas por los programas que eran ejecutados en ellas.

Adems, la velocidad del procesador en relacin con la memoria de

la computadora que acceda era cada vez ms alta. Esto conllev la aparicin

de numerosas tcnicas para reducir el procesamiento dentro del CPU, as

como de reducir el nmero total de accesos a memoria.

Caractersticas:

Estos microprocesadores siguen tomando como base el esquema

moderno de Von Neumann.

Las instrucciones, aunque con otras caractersticas, siguen divididas en

tres grupos:

o Transferencia.

b)

c) Control de flujo.

Operaciones.

Reduccin del conjunto de instrucciones a instrucciones bsicas

simples, con la que pueden implantarse todas las operaciones

complejas.

Arquitectura del tipo load-store (carga y almacena). Las nicas

instrucciones que tienen acceso a la memoria son 'load' y 'store'; registr

a registro, con un menor nmero de acceso a memoria.

Casi todas las instrucciones pueden ejecutarse dentro de un ciclo de

reloj. Con un control implantado por hardware (con un diseo del tipo

load-store), casi todas las instrucciones se pueden ejecutar cada ciclo de

reloj, base importante para la reorganizacin de la ejecucin de

instrucciones por medio de un compilador.

Pipeline (ejecucin simultnea de varias instrucciones). Posibilidad de

reducir el nmero de ciclos de mquina necesarios para la ejecucin de

10

UNIVERSIDAD ANDINA DEL CUSCO

la instruccin, ya que esta tcnica permite que una instruccin puede

empezar a ejecutarse antes de que haya terminado la anterior.

El hecho de que la estructura simple de un procesador RISC conduzca a una

notable reduccin de la superficie del circuito integrado, se aprovecha con

frecuencia para ubicar en el mismo, funciones adicionales:

Unidad para el procesamiento aritmtico de punto flotante.

Unidad de administracin de memoria.

Funciones de control de memoria cache.

Implantacin de un conjunto de registros mltiples.

La relativa sencillez de la arquitectura de los procesadores RISC conduce a

ciclos de diseo ms cortos cuando se desarrollan nuevas versiones, lo que

posibilita siempre la aplicacin de las ms recientes tecnologas de

semiconductores. Por ello, los procesadores RISC no solo tienden a ofrecer

una capacidad de procesamiento del sistema de 2 a 4 veces mayor, sino que

los saltos de capacidad que se producen de generacin en generacin son

mucho mayores que en los CISC.

Por otra parte, es necesario considerar tambin que:

La disponibilidad de memorias grandes, baratas y con tiempos de

acceso menores de 60 ns en tecnologas CMOS.

Mdulos SRAM (Memoria de acceso aleatorio esttica) para memorias

cache con tiempos de acceso menores a los 15 ns.

Tecnologas de encapsulado que permiten realizar ms de 120

terminales.

Esto ha hecho cambiar, en la segunda mitad de la dcada de los ochentas,

esencialmente las condiciones tcnicas para arquitecturas RISC.

La relativa sencillez de la arquitectura de los procesadores RISC conduce a

ciclos de diseo ms cortos. Por ello, los procesadores RISC no solo tienden a

ofrecer una capacidad de procesamiento del sistema de 2 a 4 veces mayor,

sino que los saltos de capacidad que se producen de generacin en generacin

son mucho mayores que en los CISC.

11

UNIVERSIDAD ANDINA DEL CUSCO

Por otra parte, es necesario considerar tambin que:

La disponibilidad de memorias.

Mdulos SRAM.

Tecnologas de encapsulado.

Ventajas:

Objetivo: Implementar el caso frecuente para ejecucin rpida.

Conjunto de instrucciones reducido y simple.

Conjunto de instrucciones ortogonal (slo una instruccin para cada

funcin).

Pocos modos simples de direccionamiento.

Pocos tipos de datos soportados.

Arquitectura load/store.

Gran nmero de registros de propsito general.

Longitud de instruccin fija.

Compiladores ms sencillos y eficientes.

Microarquitectura ms simple.

Instrucciones ms cortas, menos tiempo de acceso a memoria.

Desventajas:

Mayor nmero de lneas de cdigo para una funcin.

Compatibilidad con arquitecturas antiguas es ms difcil de mantener.

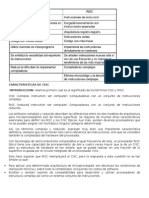

2.3 Diferencias Arquitectura RISC y CISC

La siguiente tabla esquematiza algunas de las principales caractersticas de las

arquitecturas RISC Y CISC.

12

UNIVERSIDAD ANDINA DEL CUSCO

Hoy en da, los programas cada vez ms grandes y complejos demandan

mayor velocidad en el procesamiento de informacin, lo que implica la

bsqueda de microprocesadores ms rpidos y eficientes.

Los avances y progresos en la tecnologa de semiconductores, han reducido

las diferencias en las velocidades de procesamiento de los microprocesadores

con las velocidades de las memorias, lo que ha repercutido en nuevas

tecnologas en el desarrollo de microprocesadores. Hay quienes consideran

que en breve los microprocesadores RISC (reduced instruction set computer)

sustituirn a los CISC (complex instruction set computer), pero existe el hecho

que los microprocesadores CISC tienen un mercado de software muy

difundido, aunque tampoco tendrn ya que establecer nuevas familias en

comparacin con el desarrollo de nuevos proyectos con tecnologa RISC.

La arquitectura RISC plantea en su filosofa de diseo una relacin muy

estrecha entre los compiladores y la misma arquitectura como se ver ms

adelante.

13

UNIVERSIDAD ANDINA DEL CUSCO

El compilador:

Motivos por el que los compiladores no utilizan el juego completo de

instrucciones es que levara mucho tiempo analizar en cada sentencia cual es

la instruccin o secuencia de instrucciones ms rpida o ms corta. Para

favorecer la tarea del compilador se debe ofrecer un juego de instrucciones que

sea regular.

2.3.1 Papel de los compiladores en un sistema RISC:

El compilador juega un papel clave para un sistema RISC equilibrado.

Todas las operaciones complejas se trasladan al microprocesador por medio de

conexiones fijas en el circuito integrado para agilizar las instrucciones bsicas

ms importantes. De esta manera, el compilador asume la funcin de un

mediador inteligente entre el programa de aplicacin y el microprocesador. Es

decir, se hace un gran esfuerzo para mantener al hardware tan simple como

sea posible, an a costa de hacer al compilador considerablemente ms

complicado. Esta estrategia se encuentra en clara contra posicin con las

mquinas CISC que tienen modos de direccionamiento muy complicados. En la

14

UNIVERSIDAD ANDINA DEL CUSCO

prctica, la existencia en algunos modos de direccionamiento complicados en

los microprocesadores CISC, hacen que tanto el compilador como el

microprograma sean muy complicados.

No obstante, las mquinas CISC no tienen caractersticas complicadas como

carga, almacenamiento y salto que consumen mucho tiempo, las cuales en

efecto aumentan la complejidad del compilador.

Conclusiones

Las arquitecturas RISC y CISC son ejemplos de CPU con un conjunto

de instrucciones para arquitecturas basadas en registros .

La microprogramacin es una caracterstica importante y esencial de

casi todas las arquitecturas CISC.

La microprogramacin significa que cada instruccin de mquina es

interpretada por una microprograma localizada en una memoria en el

circuito integrado del procesador.

Los microprocesadores CISC tienen un conjunto de instrucciones que se

caracteriza por ser muy amplio y permitir operaciones complejas entre

operandos situados en la memoria o en los registros internos.

Arquitecturas RISC:

RISC es una filosofa de diseo de CPU para computadora que est a

favor de conjuntos de instrucciones pequeas y simples

Instrucciones ms cortas, menos tiempo de acceso a memoria

Arquitectura load/store.

Gran nmero de registros de propsito general.

Longitud de instruccin fija.

Compiladores ms sencillos y eficientes.

15

UNIVERSIDAD ANDINA DEL CUSCO

Bibliografa

Camacho, R. (17 de Marzo de 2012). Arquitectura RISC y CISC . Obtenido de

Computo Integrado Web Site:

http://rcmcomputointegrado.blogspot.com/2012/03/arquitectura-riscy-cisc.html

Osses Anguita, E. (20 de septiembre de 2001). RISC / CISC. Obtenido de

http://pitagoras.usach.cl/~eflores/lcc/cd_arq/arquitectura/t1-risccisc.pdf

Vega, J. & Snchez, R. & Salgado, G. (2008). Arquitectura RISC vs CISC.

Octubre 14,2008, de

UNIVERSIDAD AUTONOMA METROPOLITANA

UNIDAD AZCAPOTZALCO DIVISION

CIENCIAS BASICAS E INGENIERIA Sitio

web: http://www.azc.uam.mx/publicaciones/enlinea2/num1/1-2.htm

16

You might also like

- CISC vs RISC: Arquitecturas de ProcesadoresDocument36 pagesCISC vs RISC: Arquitecturas de ProcesadoresDamian ManzabaNo ratings yet

- Programación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeFrom EverandProgramación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeNo ratings yet

- Guia para La Escritura Del Ensayo - Yolanda GamboaDocument10 pagesGuia para La Escritura Del Ensayo - Yolanda GamboaKing MobNo ratings yet

- Ejemplos partidas diario contabilidadDocument6 pagesEjemplos partidas diario contabilidadJorge Luis Ortiz Figueroa100% (1)

- Ejercicios de ReferenciasDocument4 pagesEjercicios de ReferenciasGerson TzulNo ratings yet

- Formación en bordado de piedrasDocument28 pagesFormación en bordado de piedrasJesse Mariano100% (1)

- Modelo Recibo Alquiler de CuartoDocument1 pageModelo Recibo Alquiler de Cuartojames100% (3)

- Modelo Contrato Locacion Servicios - Ingeniero ResidenteDocument4 pagesModelo Contrato Locacion Servicios - Ingeniero ResidentegabitamiaNo ratings yet

- Arquitecturas RISC y CISC: Diferencias y EjemplosDocument2 pagesArquitecturas RISC y CISC: Diferencias y Ejemplosmanuel_cruz_86No ratings yet

- Miguel Jofre S2 Tarea MicrocontroldoresDocument6 pagesMiguel Jofre S2 Tarea MicrocontroldoresMiguel JofreNo ratings yet

- UF0852 - Instalación y actualización de sistemas operativosFrom EverandUF0852 - Instalación y actualización de sistemas operativosRating: 5 out of 5 stars5/5 (1)

- Aprovechamiento RAEEDocument13 pagesAprovechamiento RAEEingdianamartinezNo ratings yet

- Procedimiento de MercadeoDocument4 pagesProcedimiento de MercadeoJOAN LAMBRANO100% (1)

- TDR Herramientas Manuales y OtrosDocument3 pagesTDR Herramientas Manuales y OtrosJonathan Garcia CalizayaNo ratings yet

- Cisk Vs RiskDocument9 pagesCisk Vs RiskWilberth Antonio Tuz SegoviaNo ratings yet

- Arquitectura RISC Vs CISCDocument9 pagesArquitectura RISC Vs CISCMinimo Peluchente JondulNo ratings yet

- Sisc RiscDocument15 pagesSisc RiscROHNNeNo ratings yet

- Arquitectura RISC Vs CISCDocument9 pagesArquitectura RISC Vs CISCRaul CrookersNo ratings yet

- 1 Arquitectura RISC Vs CISCDocument6 pages1 Arquitectura RISC Vs CISCGerald AburtoNo ratings yet

- Caracteristicas de CiscDocument3 pagesCaracteristicas de CiscWilliam Fernando Garcia100% (1)

- Arquitectura RISC Vs CISCDocument10 pagesArquitectura RISC Vs CISCVictor TomatsuNo ratings yet

- Arquitecturas CISC vs RISC: Ventajas y desventajas de ambas tecnologíasDocument6 pagesArquitecturas CISC vs RISC: Ventajas y desventajas de ambas tecnologíasyeison arteagaNo ratings yet

- Diferencia Entre Risc y CiscDocument9 pagesDiferencia Entre Risc y CiscMaria Isabel Fajardo DelgadoNo ratings yet

- MicroI TeoriaDocument48 pagesMicroI Teoriaottoniel RosarioNo ratings yet

- Arquitectura Del MicroprocesadorDocument2 pagesArquitectura Del MicroprocesadorMARVIN CASCABEL RAMIREZ SANCANo ratings yet

- Arquitectura RISC y CISCDocument10 pagesArquitectura RISC y CISCUsiel RTNo ratings yet

- Investigacion - CISC y RISCHDocument3 pagesInvestigacion - CISC y RISCHVlade RamirezNo ratings yet

- Arquitectura RISC Vs CISCDocument25 pagesArquitectura RISC Vs CISCGiacinto DimambroNo ratings yet

- 2 Características de La Arquitectura de RISC y CISCDocument6 pages2 Características de La Arquitectura de RISC y CISCLuisVillafuerteNo ratings yet

- Risc y SiscDocument4 pagesRisc y SiscJuan Carlos Chaufon Cruz100% (1)

- Arquitecturas CISC y RISC Ensayo Sobre C PDFDocument4 pagesArquitecturas CISC y RISC Ensayo Sobre C PDFOscarDavidGarciaHerreraNo ratings yet

- Arquitecturas CISC y RISC Ensayo Sobre CDocument4 pagesArquitecturas CISC y RISC Ensayo Sobre CThe vvbbNo ratings yet

- Arquitectura RISC Vs CISCDocument10 pagesArquitectura RISC Vs CISCMario SaicoNo ratings yet

- Tecnologia Risc y CiscDocument5 pagesTecnologia Risc y CiscSonia CordovaNo ratings yet

- Informe de Arquitecturas RISC Y CISCDocument13 pagesInforme de Arquitecturas RISC Y CISCJuan Carlos Romero Chalco0% (1)

- Risc Cisc DSPDocument32 pagesRisc Cisc DSPAnderson Mujica GamarraNo ratings yet

- Arquitecturas de CPU (SISC Y RISC)Document8 pagesArquitecturas de CPU (SISC Y RISC)La Presiosa AnyerNo ratings yet

- Trabajo de Investigacion#1 Suñagua Aguilar Jhonattan JosueDocument7 pagesTrabajo de Investigacion#1 Suñagua Aguilar Jhonattan JosueFabian ParraNo ratings yet

- Diferencia CISC Vs RISCDocument3 pagesDiferencia CISC Vs RISCrodri2507No ratings yet

- Risc - Cisc - Harvard - Von NewmanDocument30 pagesRisc - Cisc - Harvard - Von NewmanmajesticbufoNo ratings yet

- Arquitectura RISC vs CISCDocument4 pagesArquitectura RISC vs CISCyeison arteagaNo ratings yet

- Conjunto de Instrucciones de ComputadoraDocument5 pagesConjunto de Instrucciones de ComputadoraJohanaStylesHoranNo ratings yet

- Arquitectura Cisc Vs RiscDocument6 pagesArquitectura Cisc Vs RiscFernando ZapataNo ratings yet

- Significado de Los Términos CISC y RISCDocument8 pagesSignificado de Los Términos CISC y RISCRandy EstradaNo ratings yet

- RiseDocument7 pagesRiseDalvi JoelNo ratings yet

- Introduccion Risc y CiscDocument7 pagesIntroduccion Risc y CiscAldo ReignNo ratings yet

- Rodrigo Soto Tarea2Document6 pagesRodrigo Soto Tarea2rodrigoNo ratings yet

- Arquitectura Cisc y RiscDocument27 pagesArquitectura Cisc y RiscEucaris GarciaNo ratings yet

- Procesadores RISCDocument15 pagesProcesadores RISCRonny AláNo ratings yet

- Arquitectura CISCDocument6 pagesArquitectura CISCNayeli MayoNo ratings yet

- Actividad #5Document9 pagesActividad #5Ashley IvánNo ratings yet

- Procesadores CISC, RISC y ARM.Document11 pagesProcesadores CISC, RISC y ARM.Enrique Mendoza100% (1)

- Resumen de Arquitectura de Computadoras Unidad IDocument5 pagesResumen de Arquitectura de Computadoras Unidad IAbelardo Martinez GonzalezNo ratings yet

- Arquitecturas RISC y CISC: Diferencias clave enDocument29 pagesArquitecturas RISC y CISC: Diferencias clave enMichelle Ysa ValeraNo ratings yet

- Arquitectura CISC vs RISCDocument5 pagesArquitectura CISC vs RISCjaromero3No ratings yet

- Arquitectura RISC y Arquitectura CISCDocument5 pagesArquitectura RISC y Arquitectura CISCSebas TNo ratings yet

- Características de Las Maquinas Con Tecnología Cisc y RiscDocument4 pagesCaracterísticas de Las Maquinas Con Tecnología Cisc y RiscEdwin SalinasNo ratings yet

- Arquitectura de MicroprocesadoresDocument7 pagesArquitectura de MicroprocesadoresmayteNo ratings yet

- Risc y CiscDocument6 pagesRisc y CiscCamila CuevaNo ratings yet

- Arquitectura CISC: Conjunto de instrucciones complejasDocument6 pagesArquitectura CISC: Conjunto de instrucciones complejasLucy AndradeNo ratings yet

- Tipos de Arquitectura CiscDocument19 pagesTipos de Arquitectura CiscGabriel LvNo ratings yet

- Ensayo Arquitectura Risc y CiscDocument6 pagesEnsayo Arquitectura Risc y CiscJCARLOS_CUEVAS_No ratings yet

- Unidad 1Document26 pagesUnidad 1ALEXNo ratings yet

- Analisis de Componentes CpuDocument16 pagesAnalisis de Componentes CpuJesús Melchor Hau NohNo ratings yet

- Diferencias entre arquitecturas CISC y RISCDocument22 pagesDiferencias entre arquitecturas CISC y RISCAlex Alexyear MendozaNo ratings yet

- Arquitectura CISC enDocument18 pagesArquitectura CISC ensoldierelbalaNo ratings yet

- Arquitectura Cisc y RicsDocument2 pagesArquitectura Cisc y RicsDavid AquinoNo ratings yet

- CalidadDocument1 pageCalidadGrety CcorahuaNo ratings yet

- Estudio de MercadoDocument1 pageEstudio de MercadoGrety CcorahuaNo ratings yet

- 143691023587Document23 pages143691023587jose panta yamunaqueNo ratings yet

- Evaluacion 1 Internet de Las CosasDocument11 pagesEvaluacion 1 Internet de Las CosasWalter Bautista67% (6)

- Esa BSSC962 Esp PDFDocument33 pagesEsa BSSC962 Esp PDFGrety CcorahuaNo ratings yet

- Informe ESADocument13 pagesInforme ESAGrety CcorahuaNo ratings yet

- 2016-I Guia01Document8 pages2016-I Guia01Grety CcorahuaNo ratings yet

- Pedi TriaDocument19 pagesPedi TriaGrety CcorahuaNo ratings yet

- Esa BSSC962 Esp PDFDocument33 pagesEsa BSSC962 Esp PDFGrety CcorahuaNo ratings yet

- Plan de Tesis 12-10-2016Document45 pagesPlan de Tesis 12-10-2016Grety CcorahuaNo ratings yet

- Calculo MonografiaDocument18 pagesCalculo MonografiaGrety CcorahuaNo ratings yet

- Dispositivas de Sistemas de Informacion en Las OrganizacionesDocument22 pagesDispositivas de Sistemas de Informacion en Las OrganizacionesGrety CcorahuaNo ratings yet

- Conclusion EsDocument4 pagesConclusion EsGrety CcorahuaNo ratings yet

- Etica y ValoresDocument10 pagesEtica y ValoresGrety CcorahuaNo ratings yet

- Perú - SierraDocument39 pagesPerú - SierraGrety CcorahuaNo ratings yet

- Sistemas de Informacion en Las OrganizacionesDocument19 pagesSistemas de Informacion en Las OrganizacionesGrety CcorahuaNo ratings yet

- E06 Equilibrio de Un Cuerpo Rigido PDFDocument5 pagesE06 Equilibrio de Un Cuerpo Rigido PDFerikcalderon123No ratings yet

- Qué Es Un VolcánDocument2 pagesQué Es Un VolcánDaniel MacadanNo ratings yet

- Decisiones por el bien comúnDocument2 pagesDecisiones por el bien comúnFernando MaqueraNo ratings yet

- Cumplimiento de obligaciones civiles: elementos, modalidades y personas autorizadasDocument27 pagesCumplimiento de obligaciones civiles: elementos, modalidades y personas autorizadasCARLOS ADRIAN SANDOVAL PATZANNo ratings yet

- El Silencio Administrativo y Su Régimen en La Legislación ArgentinaDocument11 pagesEl Silencio Administrativo y Su Régimen en La Legislación Argentinafuturosabogados100% (1)

- PoderLegislativo40Document4 pagesPoderLegislativo40Rodrigo Kyrie VilcaNo ratings yet

- GuiaParctica FormulasAEMI2018 WebDocument30 pagesGuiaParctica FormulasAEMI2018 WebPedro Rodriguez PicazoNo ratings yet

- Actividad 5 - Parte I Proyecto de InnovacionDocument18 pagesActividad 5 - Parte I Proyecto de InnovacionJOHANNA KATERINE AYA CALDERONNo ratings yet

- Asistente de Gestión Human PDFDocument2 pagesAsistente de Gestión Human PDFyoanNo ratings yet

- Ejercicios. XQueryDocument5 pagesEjercicios. XQueryJuan SánchezNo ratings yet

- REQUERIMIENTOS TÉCNICOS DE JUEGOS OPERADOS POR INTERNET - OdtDocument4 pagesREQUERIMIENTOS TÉCNICOS DE JUEGOS OPERADOS POR INTERNET - Odtadriana castroNo ratings yet

- Plan de Mantenimiento FURIUSDocument1 pagePlan de Mantenimiento FURIUSBryan PerdomoNo ratings yet

- Designan Director Ejecutivo Del Programa de Desarrollo Produ Resolucion Ministerial N 0500 2022 Midagri 2127484 1Document1 pageDesignan Director Ejecutivo Del Programa de Desarrollo Produ Resolucion Ministerial N 0500 2022 Midagri 2127484 1Huanca York TimesNo ratings yet

- Errores en Wms Vehicular Diciembre 2020Document45 pagesErrores en Wms Vehicular Diciembre 2020Diego ValenzuelaNo ratings yet

- Tarea7 Etica ProfesionalDocument4 pagesTarea7 Etica Profesionaljismeily wayattNo ratings yet

- TermocuplasDocument9 pagesTermocuplasjimmyNo ratings yet

- Evidencia 4 Control de GestionDocument5 pagesEvidencia 4 Control de GestionsherylvcNo ratings yet

- Eco 6Document11 pagesEco 6Dycko Fernandez100% (1)

- Semana Del 2 Al 6 de AgostoDocument4 pagesSemana Del 2 Al 6 de AgostoMagdalena SegundoNo ratings yet

- El Laberinto Actividad Matematica FundamentalDocument5 pagesEl Laberinto Actividad Matematica FundamentalJoel HernandezNo ratings yet

- Eliminación de Interferencias en Circuitos Neumáticos Con El Método de CascadaDocument15 pagesEliminación de Interferencias en Circuitos Neumáticos Con El Método de CascadaPedro PastorNo ratings yet

- Final - Control de CalidadDocument35 pagesFinal - Control de Calidadjosimar valdesNo ratings yet

- Regresión Lineal Aplicada en FabricaciónDocument17 pagesRegresión Lineal Aplicada en FabricaciónAbdiel Abi CaamalNo ratings yet

- Manual Tecnico de CitricosDocument22 pagesManual Tecnico de CitricosMelissa HesterNo ratings yet

- 6 Casos de ResilienciaDocument3 pages6 Casos de ResilienciaRomina KrummNo ratings yet

- Lab 03 - Matlab - Introducion Al Uso de Funciones, Funciones Logicas y Estructuras de Control, Principios de ProgramacionDocument20 pagesLab 03 - Matlab - Introducion Al Uso de Funciones, Funciones Logicas y Estructuras de Control, Principios de ProgramacionWanderley Pacco CabreraNo ratings yet