Professional Documents

Culture Documents

Nodal Analysis A) Review of KCL and KVL B) Nodal Analysis Strategy C) Special Situations and Examples D) Accounting For All Unknowns

Uploaded by

JeffryGlenSitanayaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Nodal Analysis A) Review of KCL and KVL B) Nodal Analysis Strategy C) Special Situations and Examples D) Accounting For All Unknowns

Uploaded by

JeffryGlenSitanayaCopyright:

Available Formats

EECS 42 Intro.

electronics for CS Fall 2001

Lecture 6: 9/24/01 A.R. Neureuther

Lecture 8: September 24th, 2001

Nodal Analysis

Version Date 9/23/01

20 min Quiz on HW 1-4 at start

of class on Wed. 9/26

A)Review of KCL and KVL

B) Nodal Analysis Strategy

C)Special Situations and Examples

D)Accounting for All Unknowns

The following slides were derived

from those prepared by Professor

Oldham For EE 40 in Fall 01

Reading:

Schwarz and Oldham 2.3 pp. 53-58

Copyright 2001, Regents of University of California

EECS 42 Intro. electronics for CS Fall 2001

Lecture 6: 9/24/01 A.R. Neureuther

BRANCHES AND NODES

Version Date 9/23/01

Circuit with several branches connected at a node:

branch (circuit element)

i2

i1

i3

i4

KIRCHOFFs CURRENT LAW KCL:

(Sum of currents entering node) (Sum of currents leaving node) = 0

q = charge stored at node is zero. If charge is stored, for

example in a capacitor, then the capacitor is a branch and the

charge is stored there NOT at the node.

Copyright 2001, Regents of University of California

EECS 42 Intro. electronics for CS Fall 2001

Lecture 6: 9/24/01 A.R. Neureuther

Version Date 9/23/01

WHAT IF THE NET CURRENT WERE NOT ZERO?

Suppose imbalance in currents is 1A = 1 C/s (net current entering node)

Assuming that q = 0 at t = 0, the charge increase is 106 C each second

or

106 / 1.6 1019 = 6 1012 charge carriers each second

But by definition, the capacitance of a node to ground is ZERO because

we show any capacitance as an explicit circuit element (branch). Thus,

the voltage would be infinite (Q = CV).

Something has to give! In the limit of zero capacitance the accumulation

of charge would result in infinite electric fields there would be a spark

as the air around the node broke down.

Charge is transported around the circuit branches (even stored

in some branches), but it doesnt pile up at the nodes!

Copyright 2001, Regents of University of California

EECS 42 Intro. electronics for CS Fall 2001

Lecture 6: 9/24/01 A.R. Neureuther

Version Date 9/23/01

KIRCHHOFFS CURRENT LAW EXAMPLE

24 A

-4 A

10 A

Currents entering the node: 24 A

Currents leaving the node: 4 A + 10 A + i

24 = 10 + (4) + i

i = 18 A

Three statements of KCL

i in = i out

IN

i = 18 A

24 ( 4) 10 i = 0

i = 18 A

24 = 4 + 10 + i

OUT

i in = 0

ALL

i out = 0

24 4 + 10 + i = 0

i = 18 A

ALL

Copyright 2001, Regents of University of California

EQUIVALENT

EECS 42 Intro. electronics for CS Fall 2001

Lecture 6: 9/24/01 A.R. Neureuther

Version Date 9/23/01

GENERALIZATION OF KCL

Sum of currents entering and leaving a closed surface is zero

Physics 7B

Could be a big chunk of

circuit in here, e.g.,

could be a Black Box

Note that circuit branches could be inside the surface.

Copyright 2001, Regents of University of California

The surface can

enclose more

than one node

EECS 42 Intro. electronics for CS Fall 2001

Lecture 6: 9/24/01 A.R. Neureuther

Version Date 9/23/01

KIRCHHOFFS CURRENT LAW USING SURFACES

Example

surface

5 A + 2 A = i

entering

5 A

2 A

i=?

leaving

Another example

50 mA

i=7A

i?

i must be 50 mA

Copyright 2001, Regents of University of California

EECS 42 Intro. electronics for CS Fall 2001

Lecture 6: 9/24/01 A.R. Neureuther

Version Date 9/23/01

Example of the use of KCL

R1

At node X:

Current into X from the left:

(V1 - vX)/R1

V1

+

-

C1

Current out of X to the right:

vX/R2 + CdvX/dt

KCL: (V1 - vX)/R1 = vX/R2 + CdvX/dt

Given V1, This differential equation can be solved for vX(t).

Copyright 2001, Regents of University of California

R2

EECS 42 Intro. electronics for CS Fall 2001

Lecture 6: 9/24/01 A.R. Neureuther

BRANCH AND NODE VOLTAGES

Version Date 9/23/01

The voltage across a circuit element is defined as the difference

between the node voltages at its terminals

v1

v2

v2 = vd va

+

d

v e 0 (since its the

select as ref.

reference)

ground

Specifying node voltages: Use one node as the implicit reference

(the common node attach special symbol to label it)

Now single subscripts can label voltages:

e.g., vb means vb ve, va means va ve, etc.

Copyright 2001, Regents of University of California

EECS 42 Intro. electronics for CS Fall 2001

Lecture 6: 9/24/01 A.R. Neureuther

Version Date 9/23/01

KIRCHHOFFS VOLTAGE LAW (KVL)

The algebraic sum of the voltage drops around any closed loop is zero.

Why? We must return to the same potential (conservation of energy).

Voltage drop defined as the branch voltage if the + sign is encountered first;

it is (-) the branch voltage if the sign is encountered first important

bookkeeping

Path

Path

+

V1

-

drop

V2

+

rise or step up

(negative drop)

Closed loop: Path beginning and ending on the same node

Copyright 2001, Regents of University of California

Lecture 6: 9/24/01 A.R. Neureuther

Version Date 9/23/01

KVL EXAMPLE

, ,

+ v2

+

va

+

vb

Note that:

Examples of

Three closed paths:

v3

EECS 42 Intro. electronics for CS Fall 2001

+

vc

v2 = va - vb

v3 = vc - vb

Path 1:

va + v2 + v b = 0

ref. node

Path 2:

v b v3 + vc = 0

va vb

YEP!

Copyright 2001, Regents of University of California

Path 3:

va + v2 v3 + vc = 0

EECS 42 Intro. electronics for CS Fall 2001

Lecture 6: 9/24/01 A.R. Neureuther

Version Date 9/23/01

Example of the use of KVL

Voltage drop across R1 (left to right):

i R1

Voltage drop across

L1 (top to bottom):

V1

R1

L1

Ldi/dt

Starting at the bottom and walking clockwise, summing voltage drops:

-V1 + i R1 + Ldi/dt = 0

Given V1, this differential equation can be solved for i(t).

Copyright 2001, Regents of University of California

EECS 42 Intro. electronics for CS Fall 2001

Lecture 6: 9/24/01 A.R. Neureuther

Version Date 9/23/01

HOW MANY NODE EQUATIONS DO WE NEED?

The circuit is completely described by the voltage of each node and

the current through each branch. Thus the number of unknowns =

(NNODES 1) + NBRANCHES

v1

v2

+

d

v e 0 (since its the

select as ref.

reference)

ground

Since we already know the reference node voltage, we need

NNODES 1 node equations.

Write a node equation at each of the nodes except the reference node!

Copyright 2001, Regents of University of California

EECS 42 Intro. electronics for CS Fall 2001

Lecture 6: 9/24/01 A.R. Neureuther

Version Date 9/23/01

SAVE TIME IN SPECIAL CASES!

v1

v +

S

v2

+

d

R1

f

e

Eliminate either Vb or

Vc by using a surface

that encloses the voltage

source and the nodes at

is terminals.

R2

Eliminate this trivial node

by a single resistor

REQ = R1 + R2

This surfaces is a SUPERNODE.

Copyright 2001, Regents of University of California

EECS 42 Intro. electronics for CS Fall 2001

Lecture 6: 9/24/01 A.R. Neureuther

Version Date 9/23/01

EXAMPLE WITH BOTH SPECIAL CASES

R1

I1

V2

R2

c

R3

b

R4

(

Va

Va

Va + V2 )

I1

=0

R1 R2 + R3

R4

Copyright 2001, Regents of University of California

EECS 42 Intro. electronics for CS Fall 2001

Lecture 6: 9/24/01 A.R. Neureuther

Version Date 9/23/01

ACCOUNTING FOR ALL UNKNOWNS

The number of unknowns = (NNODES 1) + NBRANCHES

v1

v2

+

d

select as ref.

Node Method:

Use (NNODES 1) node equations

Then one Branch Relationship for each branch

Copyright 2001, Regents of University of California

ground

EECS 42 Intro. electronics for CS Fall 2001

Lecture 6: 9/24/01 A.R. Neureuther

Version Date 9/23/01

ACCOUNTING FOR ALL UNKNOWNS

The number of unknowns = (NNODES 1) + NBRANCHES

v1

Loop Method:

v2

+

d

select as ref.

Use one loop equation for each window in the circuit

Or in 3D use [ NBRANCH - (NNODES 1)] Loop Equations

Then one Branch Relationship for each branch

Copyright 2001, Regents of University of California

ground

You might also like

- Electrical and Electronic Principles 3 Checkbook: The Checkbook SeriesFrom EverandElectrical and Electronic Principles 3 Checkbook: The Checkbook SeriesNo ratings yet

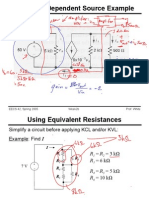

- Circuit Analysis With Dependent Sources A) Node Equations B) Equivalent Sources C) Amplifier Parameters: Gain, R, R D) Non-Ideal Op-Amp ModelDocument10 pagesCircuit Analysis With Dependent Sources A) Node Equations B) Equivalent Sources C) Amplifier Parameters: Gain, R, R D) Non-Ideal Op-Amp ModelPavanJangidNo ratings yet

- Finding Voltages in A CircuitDocument8 pagesFinding Voltages in A CircuitcassNo ratings yet

- Elec1111 03 Node Voltage Analysis PDocument9 pagesElec1111 03 Node Voltage Analysis PuploadingpersonNo ratings yet

- New Approaches to the Design and Economics of EHV Transmission Plant: International Series of Monographs in Electrical EngineeringFrom EverandNew Approaches to the Design and Economics of EHV Transmission Plant: International Series of Monographs in Electrical EngineeringNo ratings yet

- Dependent Source Problems - BerkleyDocument16 pagesDependent Source Problems - BerkleyBhaswar MajumderNo ratings yet

- Electronics 3 Checkbook: The Checkbooks SeriesFrom EverandElectronics 3 Checkbook: The Checkbooks SeriesRating: 5 out of 5 stars5/5 (1)

- Circuit W/ Dependent Source Example: Find I, I and IDocument18 pagesCircuit W/ Dependent Source Example: Find I, I and Iravi_reddy237686100% (1)

- ES Unit-1Document48 pagesES Unit-1Mazin VoraNo ratings yet

- EE42 100 Cch-Lecure11 071713-CleanDocument31 pagesEE42 100 Cch-Lecure11 071713-CleanozanistzNo ratings yet

- Lecture 5-CA I (En-115)Document28 pagesLecture 5-CA I (En-115)Aftab AhmadNo ratings yet

- Lect5 PDFDocument13 pagesLect5 PDFJoswe BaguioNo ratings yet

- Dept. of Electronics and Communication Engineering: Sem / Year: Ii / IDocument41 pagesDept. of Electronics and Communication Engineering: Sem / Year: Ii / Ivalan_carl07No ratings yet

- Example An Op Amp Circuit Analysis LectureDocument23 pagesExample An Op Amp Circuit Analysis LectureAthiyo MartinNo ratings yet

- Lab 3Document8 pagesLab 3TOP 5 GHOSTNo ratings yet

- M.M. Engineering College - Mullana: Laboratory Manual Practical Experiment Instruction SheetDocument3 pagesM.M. Engineering College - Mullana: Laboratory Manual Practical Experiment Instruction Sheetvj4249No ratings yet

- Basic Electrical EngineeringDocument181 pagesBasic Electrical EngineeringPrakash Chandran CNo ratings yet

- Module 3Document5 pagesModule 3Christine MalibiranNo ratings yet

- Bakshi Basic ElectricalDocument196 pagesBakshi Basic Electricalprakash100% (6)

- Verification of KVL and KCLDocument3 pagesVerification of KVL and KCLVarun Vadluri80% (5)

- ECE 207: Lab Report #2 Title:: Kirchhoff's Voltage and Current Laws (KVL and KCL) (DC)Document8 pagesECE 207: Lab Report #2 Title:: Kirchhoff's Voltage and Current Laws (KVL and KCL) (DC)Sajid HussainNo ratings yet

- BEE Module1 Lec 4-6Document41 pagesBEE Module1 Lec 4-6kali hembramNo ratings yet

- Topic 11.3 - Capacitance - AHLDocument50 pagesTopic 11.3 - Capacitance - AHLPaul AmezquitaNo ratings yet

- Node-Voltage or Nodal AnalysisDocument8 pagesNode-Voltage or Nodal AnalysisAqil SiddiquiNo ratings yet

- Definitions & Examples: C C C CDocument47 pagesDefinitions & Examples: C C C CSeroKeretaMasaroWidiarNo ratings yet

- 11.3 - Capacitance - AHLDocument50 pages11.3 - Capacitance - AHL王硕No ratings yet

- Ans 7 BDocument2 pagesAns 7 BBobNo ratings yet

- Quiz 2Document20 pagesQuiz 2Nathan KingNo ratings yet

- EE42 100 Cch-Lecure2 062613-FDocument45 pagesEE42 100 Cch-Lecure2 062613-FozanistzNo ratings yet

- Physics 1220/1320: Electromagnetism - Part One: ElectrostaticsDocument70 pagesPhysics 1220/1320: Electromagnetism - Part One: ElectrostaticsbeckerinskiNo ratings yet

- Overhead Line Insulators: Example 4.1Document11 pagesOverhead Line Insulators: Example 4.1e TalalNo ratings yet

- Overhead Line and Substation InsulationDocument11 pagesOverhead Line and Substation InsulationAnkat Rao RaoNo ratings yet

- M1L2 DC Network TheoremsDocument57 pagesM1L2 DC Network TheoremsChandan Pandey super cricket gamesNo ratings yet

- Example 9: Find The Thevenin Equivalent Circuit of The Network at The Terminals A-BDocument29 pagesExample 9: Find The Thevenin Equivalent Circuit of The Network at The Terminals A-Bsamuel fiifi yeboahNo ratings yet

- EEE Experiment 1Document8 pagesEEE Experiment 1SavioNo ratings yet

- Title: Capacitors: Spring 2007Document25 pagesTitle: Capacitors: Spring 2007Mukul PatelNo ratings yet

- Exercises On Kirchoffs LawDocument10 pagesExercises On Kirchoffs LawTwizerimana Jean Volta100% (1)

- Electronics Study Material For MSCDocument23 pagesElectronics Study Material For MSCiswaleha100% (1)

- Lab 6Document5 pagesLab 6Stephen BridgesNo ratings yet

- Capacitance and Dielectrics: Fall 2008 Physics 231 Lecture 4-1Document32 pagesCapacitance and Dielectrics: Fall 2008 Physics 231 Lecture 4-1Jimmy Teng100% (1)

- Unit 1 - Part 3 - D.C. Network AnalysisDocument26 pagesUnit 1 - Part 3 - D.C. Network Analysisgenius studentNo ratings yet

- BENG 3013 - Chapter 1 - DeltaDocument39 pagesBENG 3013 - Chapter 1 - DeltaWan MamatkNo ratings yet

- Kirchoff's Voltage Law (KVL) :: V V V V V V V V V VDocument7 pagesKirchoff's Voltage Law (KVL) :: V V V V V V V V V VNoor AhmedNo ratings yet

- Physics II Finals ReviewerDocument6 pagesPhysics II Finals ReviewerCarter SiyNo ratings yet

- Kirchhoff's LawsDocument3 pagesKirchhoff's Lawsabhioptimus00No ratings yet

- Lec2 BranchCurrentDocument71 pagesLec2 BranchCurrentKuro ShiroNo ratings yet

- Verification of KCL and KVLDocument3 pagesVerification of KCL and KVLCOLD FIRENo ratings yet

- Kirchoffs LawDocument22 pagesKirchoffs LawKim OpenaNo ratings yet

- Analysis of Electronic CircuitsDocument39 pagesAnalysis of Electronic CircuitsKhaled GamalNo ratings yet

- KCL and KVL LawDocument13 pagesKCL and KVL LawSundararohith JuguntaNo ratings yet

- Ohm's Law: (Essentials of Electrical and Electronics Engineering)Document5 pagesOhm's Law: (Essentials of Electrical and Electronics Engineering)Josh KingNo ratings yet

- Electric Circuit and Electronics NoteDocument34 pagesElectric Circuit and Electronics NoteEzekiel JamesNo ratings yet

- 1st Year - Basic Electrical EngineeringDocument182 pages1st Year - Basic Electrical EngineeringMurughesh MurughesanNo ratings yet

- Aee 01Document80 pagesAee 01BonviNo ratings yet

- Experiment 2 - KVL - KCLDocument3 pagesExperiment 2 - KVL - KCLDhadkane Azad HainNo ratings yet

- EEE - VIT Chennai - Lab Report - Sam Prince Franklin - 20MIS1115Document63 pagesEEE - VIT Chennai - Lab Report - Sam Prince Franklin - 20MIS1115SamNo ratings yet

- Chapter 9 Circuit AnalysisDocument33 pagesChapter 9 Circuit AnalysisRafael Añonuevo DimaculanganNo ratings yet

- CircuitAnalysis CK Tse PDFDocument49 pagesCircuitAnalysis CK Tse PDFcivaasNo ratings yet

- How To Derive The Instrumentation Amplifier Transfer FunctionDocument1 pageHow To Derive The Instrumentation Amplifier Transfer FunctionHelioBernardoNo ratings yet

- Mod 5 Book 3 Electronic Displays Electronic Digital SystemsDocument93 pagesMod 5 Book 3 Electronic Displays Electronic Digital Systemsranjit prasadNo ratings yet

- Catalog Appleton Atx Pre Series 63 Amp Plugs Sockets Cover en Us 178372Document5 pagesCatalog Appleton Atx Pre Series 63 Amp Plugs Sockets Cover en Us 178372Elsan BalucanNo ratings yet

- Training Material of Delta Outdoor Power System For Ericsson - ESOA300-FBG12 - R00Document64 pagesTraining Material of Delta Outdoor Power System For Ericsson - ESOA300-FBG12 - R00Kyaw ThuNo ratings yet

- PFC Javier Mohedano MartinezDocument88 pagesPFC Javier Mohedano MartinezmiguelpaltinoNo ratings yet

- Ee288 5bit Flashadc ProjectDocument5 pagesEe288 5bit Flashadc ProjectbearunagiriNo ratings yet

- Circuit Schematic SymbolsDocument7 pagesCircuit Schematic SymbolsRajesh KannanNo ratings yet

- Thermometrics Temperature Sensor Solutions: AmphenolDocument16 pagesThermometrics Temperature Sensor Solutions: AmphenolFernando AbadNo ratings yet

- Eaton 066167 Emt6 DB en GBDocument5 pagesEaton 066167 Emt6 DB en GBDejanNo ratings yet

- Prevectron 3® S40 ConnectDocument2 pagesPrevectron 3® S40 ConnectIndelec IndiaNo ratings yet

- Temperature Control With SCRDocument3 pagesTemperature Control With SCRRoberto Fernandez100% (3)

- Alg 7721-00Document1 pageAlg 7721-00Philippe RUBIONo ratings yet

- 5.helmholtz Coils - DDDocument6 pages5.helmholtz Coils - DDShubham BirangeNo ratings yet

- 1.Qp - Class 12 - PhysicsDocument12 pages1.Qp - Class 12 - PhysicsEMMANUEL PHILIP REJI CLASS XNo ratings yet

- K FactorDocument3 pagesK FactorsagarNo ratings yet

- ENG LiSA20-Fehlermeldungen R111Document36 pagesENG LiSA20-Fehlermeldungen R111Adarsh Manoharan100% (1)

- Weighbeam DWB40-200 TDocument4 pagesWeighbeam DWB40-200 TdassoumennNo ratings yet

- Ho Hsing Manual EnglishDocument4 pagesHo Hsing Manual EnglishvictorhpaNo ratings yet

- H556-02 QP Jun22Document28 pagesH556-02 QP Jun22Vaibhav MehraNo ratings yet

- Second Paper PDFDocument2 pagesSecond Paper PDFHrishikesh TiwaryNo ratings yet

- 210X3E Electrical 3Document1 page210X3E Electrical 3ArmandoCalderonNo ratings yet

- Eaton Moeller MCCBDocument17 pagesEaton Moeller MCCBapi-343346993No ratings yet

- Acti9 Disbo - DBXROW2FDSDocument2 pagesActi9 Disbo - DBXROW2FDSbenghoe77No ratings yet

- Electrical Vendor ListDocument11 pagesElectrical Vendor Listshantanu11181No ratings yet

- Du2018 PDFDocument362 pagesDu2018 PDFAlexNo ratings yet

- Panasonic Gp9de Chassis Th42pv60a-H-M-Mt SM (ET)Document149 pagesPanasonic Gp9de Chassis Th42pv60a-H-M-Mt SM (ET)bellelibelleNo ratings yet

- Fundamentals of Bus Bar Protection: GE MultilinDocument92 pagesFundamentals of Bus Bar Protection: GE Multilinsonu200186100% (1)

- Technical Data: Dimension Drawings (Shown: 24 kV/36 KV Disconnectors With Motor Operating Mechanism and Auxiliary Switch)Document1 pageTechnical Data: Dimension Drawings (Shown: 24 kV/36 KV Disconnectors With Motor Operating Mechanism and Auxiliary Switch)ttyNo ratings yet

- Spin Tronic SDocument24 pagesSpin Tronic Ssrinivasa.b acchuNo ratings yet

- Alonso e Finn Vol 3Document305 pagesAlonso e Finn Vol 3jerry cristianoNo ratings yet