Professional Documents

Culture Documents

45 2copies Low Power Pass

Uploaded by

Chintamaneni VijayalakshmiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

45 2copies Low Power Pass

Uploaded by

Chintamaneni VijayalakshmiCopyright:

Available Formats

ISSN (Print) : 2320 3765

ISSN (Online): 2278 8875

International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 5, May 2014

Low Power Pass Transistor Logic Flip Flop

CH.Vijayalakshmi1, S.Vijayalakshmi2, M.Vijayalakshmi3

Assistant professor, Dept. of ECE, St.Martins Engineering College, Secunderabad, Andhrapradesh, India1

Assistant professor, Dept. of ECE, St.Martins Engineering College, Secunderabad, Andhrapradesh, India2

Associate professor, Dept. of ECE, St.Martins Engineering College, Secunderabad, Andhrapradesh, India3

ABSTRACT: In this brief, a low-power flip-flop (FF) design PTLFF: Pass Transistor Logic Flip Flop is presented.

The pro-posed design successfully adopts two measures to overcome the problems associated with existing P-FF

designs. The first one is reducing the number of nMOS transistors stacked in the discharging path. The second one is

supporting a mechanism to conditionally enhance the pull down strength when input data is 1. long discharging path

problem in conventional explicit type pulse-triggered FF (P-FF) designs and achieves better speed and power

performance. Based on post-layout simulation results using TSMC CMOS 90-nm technology, the proposed design

outperforms the conventional P-FF design by using only 17 transistors. The average power delay is reduced to 3.57

W.

KEYWORDS: Flip-flop (FF), low power, pulse-triggered.

I. INTRODUCTION

Flip-flops (FFs) are the basic storage elements used extensively in all kinds of digital designs. In particular, digital

designs now a-days often adopt intensive pipelining techniques and employ many FF-rich modules such as register file,

shift register, and first in-first out. It is also estimated that the power consumption of the clock system, which consists

of clock distribution networks and storage elements, is as high as 50% of the total system power. FFs thus contribute a

significant portion of the chip area and power consumption to the overall system design [1], [2].

Pulse-triggered FF (P-FF), because of its single-latch structure, is more popular than the conventional transmission gate

(TG) and masterslave based FFs in high-speed applications. Besides the speed advantage, its circuit simplicity lowers

the power consumption of the clock tree system. A P-FF consists of a pulse generator for strobe signals and a latch for

data storage. If the triggering pulses are sufficiently narrow, the latch acts like an edge-triggered FF. Since only one

latch, as opposed to two in the conventional masterslave configuration, is needed, a P-FF is simpler in circuit

complexity. This leads to a higher toggle rate for high-speed operations [3][8]. P-FFs also allow time borrowing

across clock cycle boundaries and feature a zero or even negative setup time. Despite these advantages, pulse

generation circuitry requires delicate pulse width control to cope with possible variations in process technology and

signal distribution network. In [9], a statistical design framework is developed to take these factors into account. To

obtain balanced performance among power, delay, and area, design space exploration is also a widely used technique

[10][13].

The proposed design, as shown in Fig. 2.2, adopts two measures to overcome the problems associated with existing PFF designs. The first one is reducing the number of nMOS transistors stacked in the discharging path. The second one

is supporting a mechanism to conditionally enhance the pull down strength when input data is 1. Refer to Fig. 2.2, As

opposed to the transistor stacking design in Fig.2.1(a),(b),(c),(d) and (e), this PFF design discharging path using

PTL.Transistor N2, in conjunction with an additional transistor N3, forms a two-input pass transistor logic (PTL)-based

AND gate to control the discharge of transistor N1. Since the two

inputs to the AND logic are mostly complementary (except during the transition edges of the clock), the output node Z

is kept at zero most of the time. When both input signals equal to 0 (during the falling edges of the clock),temporary

floating at node Z is basically harmless. At the rising edges of the clock, both transistors N2 and N3 are turned on and

collaborate to pass a weak logic high to node Z, which then turns on transistor N1 by a time span defined by the delay

inverter I1. The switching power at nodeZ can be reduced due to a diminished voltage swing. Unlike the MHLLF

design , where the discharge control signal is driven by a single transistor, parallel conduction of two nMOS transistors

Copyright to IJAREEIE

www.ijareeie.com

9706

ISSN (Print) : 2320 3765

ISSN (Online): 2278 8875

International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 5, May 2014

(N2 and N3) speeds up the operations of pulse generation.With this design measure, the number of stacked transistors

along the discharging path is reduced and the sizes of transistors N1-N3 can be reduced also.

II. CONVENTIONAL P-FF DESIGNS

PF-FFs, in terms of pulse generation, can be classified as an implicit or an explicit type. In an implicit type P-FF, the

pulse generator is part of the latch design and no explicit pulse signals are generated. In an explicit type P-FF, the pulse

generator and the latch are separate . Without generating pulse signals explicitly, implicit type P-FFs is in general more

power-economical. However, they suffer from a longer discharging path, which leads to inferior timing characteristics.

Explicit pulse generation, on the contrary, incurs more power consumption but the logic separation from the latch

design gives the FF design a unique speed advantage. Its power consumption and the circuit complexity can be

effectively reduced if one pulse generator is shares a group of FFs (e.g., an n-bit register). In this brief, we will thus

focus on the explicit type P-FF designs only.

2.1(a).EP-DCO: explicit -Data closed to output Flip-Flop

Fig.2.1(a) EP-DCO

To provide a comparison, some existing P-FF designs are reviewed first. Fig. 2.1(a) shows a classic explicit P-FF

design, named data-closet- to- output (ep-DCO) . It contains a NAND-logic-based pulse generator and a semidynamic

true-single-phase-clock (TSPC) structured latch design. In this P-FF design, inverters I3 and I4 are used to latch data,

and inverters I1 and I2 are used to hold the internal node X. The pulse width is determined by the delay of three

inverters. This design suffers from a serious drawback, i.e., the internal node X is discharged on every rising edge of the

clock in spite of the presence of a static input 1. This gives rise to large switching power dissipation. To overcome

this problem, many remedial measures such as conditional capture, conditional precharge, conditional discharge, and

conditional pulse enhancement scheme have been proposed .

2.1.(b)CDFF: conditional discharged Flip- Flop

Fig.2.1(b)CDFF

Fig. 2.1(b) shows a conditional discharged (CD) technique .An extra nMOS transistor MN3 controlled by the output

signal Q_fdbk is employed so that no discharge occurs if the input data remains 1. In addition, the keeper logic for

the internal node X is simplified and consists of an inverter plus a pull-up pMOS transistor only.

Copyright to IJAREEIE

www.ijareeie.com

9707

ISSN (Print) : 2320 3765

ISSN (Online): 2278 8875

International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 5, May 2014

2.1.(c).SCDFF: Static- conditional discharged Flip-Flop

Fig.2.1(c) SCDFF

Fig. 2.1(c) shows a similar P-FF design (SCDFF) using a static conditional discharge technique . It differs from the

CDFF design in using a static latch structure. Node X is thus exempted from periodical precharges. It exhibits a longer

data-to-Q (D-to-Q) delay than the CDFF design. Both designs face a worst case delay caused by a discharging path

consisting of three stacked transistors, i.e., MN1MN3. To overcome this delay for better speed performance, a

powerful pull-down circuitry is needed, which causes extra layout area and power consumption. The modified hybrid

latch flip-flop (MHLFF).

2.1.(d).MHLFF: Modified hybrid latch flip flop

Fig. 2.1(d) also uses a static latch. The keeper logic at node X is removed. A weak pull-up transistor MP1 controlled by

the output signal Q maintains the level of node X when Q equals 0. Despite its circuit simplicity, the MHLFF design

encounters two drawbacks. First, since node X is not predischarged, a prolonged 0 to 1 delay is expected. The delay

deteriorates further, because a level-degraded clock pulse (deviated by one VT) is applied to the discharging transistor

MN3. Second, node X becomes floating in certain cases and its value may drift causing extra dc power.

Fig.2.1(d) MHLFF

2.1.(e) TSPCFF: True-single-phase-clock Flip Flop

Fig.2.1(e)TSPCFF

Copyright to IJAREEIE

www.ijareeie.com

9708

ISSN (Print) : 2320 3765

ISSN (Online): 2278 8875

International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 5, May 2014

A weak pull-up pMOS transistor MP1 with gate connected to the ground is used in the first stage of the TSPC latch.

This gives rise to a pseudo-nMOS logic style design, and the charge keeper circuit for the internal node X can be

saved.In addition to the circuit simplicity, this approach also reduces the load capacitance of node X . Second, a pass

transistor MNx controlled by the pulse clock is included so that input data can drive node Q of the latch directly (the

signal feed-through scheme).Along with the pull-up transistor MP2 at the second stage inverter of the TSPC latch, this

extra passage facilitates auxiliary signal driving from the input source to node Q. The node level can thus be quickly

pulled up to shorten the data transition delay. Third, the pull-down network of the second stage inverter is completely

removed. Instead,the newly employed pass transistor MNx provides a discharging path. The role played by MNx is

thus twofold, i.e., providing extra driving to node Q during 0 to 1 data transitions, and discharging node Q during 1 to

0 data transitions. Compared with the latch structure used in SCDFF design, the circuit savings of the proposed

design include a charge keeper (two inverters), a pull-down network (two nMOS transistors), and a control inverter.

The only extra component introduced is an nMOS pass transistor to support signal feedthrough. This scheme actually

improves the 0 to 1 delay and thus reduces the disparity between the rise time and the fall time delays.

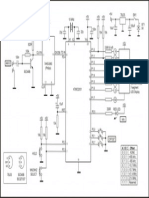

2.2 Proposed P-FF design: PTLFF: Pass Transistor Logic Flip Flop

Fig.2.2 proposed P-FF design

The proposed design, as shown in Fig. 2.2, adopts two measures to overcome the problems associated with existing PFF designs. The first one is reducing the number of nMOS transistors stacked in the discharging path. The second one

is supporting a mechanism to conditionally enhance the pull down strength when input data is 1. Refer to Fig. 2.2, As

opposed to the transistor stacking design in Fig.2.1(a),(b),(c),(d) and (e), this PFF design discharging path using

PTL.Transistor N2, in conjunction with an additional transistor N3, forms a two-input pass transistor logic (PTL)-based

AND gate to control the discharge of transistor N1. Since the two inputs to the AND logic are mostly complementary

(except during the transition edges of the clock), the output node Z is kept at zero most of the time. When both input

signals equal to 0 (during the falling edges of the clock),temporary floating at node Z is basically harmless. At the

rising edges of the clock, both transistors N2 and N3 are turned on and collaborate to pass a weak logic high to node Z,

which then turns on transistor N1 by a time span defined by the delay inverter I1. The switching power at nodeZ can be

reduced due to a diminished voltage swing. Unlike the MHLLF design , where the discharge control signal is driven by

a single transistor, parallel conduction of two nMOS transistors (N2 and N3) speeds up the operations of pulse

generation.With this design measure, the number of stacked transistors along the discharging path is reduced and the

sizes of transistors N1-N3 can be reduced also.

In this design, the longest discharging path is formed when input data is 1 while the Qbar output is 1. It steps in

when node X is discharged V TP below the VDD. This provides additional boost to node Z (from VDD-VTH to VDD). The

generated pulse is taller, which enhances the pull-down strength of transistor N1.

After the rising edge of the clock, the delay inverter I1 drives node Z back to zero through transistor N3 to shut down

the discharging path.. This means to create a pulse with sufficient width for correct data capturing, a bulky delay

inverter design, which constitutes most of the power consumption in pulse generation logic, is no longer needed. It

should be noted that this conditional pulse enhancement technique takes effects only when the FF output Q is subject to

a data change from 0 to 1. The leads to a better power performance than those schemes using an indiscriminate pulse

width enhancement approach. Another benefit of this conditional pulse enhancement scheme is the reduction in leakage

power due to shrunken transistors in the critical discharging path and in the delay inverter.

Copyright to IJAREEIE

www.ijareeie.com

9709

ISSN (Print) : 2320 3765

ISSN (Online): 2278 8875

International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 5, May 2014

III.SCHEMATIC CIRCUITS AND LAYOUTS

3.1.Conventional P-FF designs:

3.1(a)EP-DCO: explicit -Data closed to output Flip-Flop

Fig. 3(a) EP-DCO Schematic using In Tanner Tool

Fig .3(b) EP-DCO layout using in Microwind tool

3.1(b)SCDFF: Static- conditional discharged Flip-Flop

Fig. 3(c) SCDFF Schematic using In Tanner Tool.

Copyright to IJAREEIE

www.ijareeie.com

9710

ISSN (Print) : 2320 3765

ISSN (Online): 2278 8875

International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 5, May 2014

Fig .3(d) SCDFF layout using in Microwind tool

3.1(c)CDFF: conditional discharged Flip- Flop

Fig. 3(e) CDFF Schematic using In Tanner Tool.

Fig .3(f) CDFF layout using in Microwind tool

Copyright to IJAREEIE

www.ijareeie.com

9711

ISSN (Print) : 2320 3765

ISSN (Online): 2278 8875

International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 5, May 2014

3.1(d).MHLFF: Modified hybrid latch flip flop

Fig. 3(g) MHLFF Schematic using In Tanner Tool.

Fig 3(h) MHLFF layout using in Microwind tool

3.1(e).TSPCFF: True-single-phase-clock Flip Flop.

Fig. 3(i) TSPCFF Schematic using In Tanner Tool.

Copyright to IJAREEIE

www.ijareeie.com

9712

ISSN (Print) : 2320 3765

ISSN (Online): 2278 8875

International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 5, May 2014

Fig 3(j) TSPCFF layout using in Microwind tool

3.2. Proposed:

3.2.(a)PTLFF: Pass Transistor Logic Flip Flop

Fig .3.2(a) PTLFF Schematic using In Tanner Tool.

Fig 3.2(b) PTLFF layout using in Microwind tool

Copyright to IJAREEIE

www.ijareeie.com

9713

ISSN (Print) : 2320 3765

ISSN (Online): 2278 8875

International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 5, May 2014

IV.RESULTS

SIMULATION OUTPUTS:

The simulation results of above designs are shown below in the Fig. 4(a) to Fig. 4(l). A simulation window appears

with inputs and output. The power consumption is also shown on the right bottom portion of the window. If you are

unable to meet the specifications of the circuit change the transistor sizes. Generate the layout again and run the

simulations till you achieve your target delays. Depending on the input sequences assigned at the input the output is

observed in the simulation.

To demonstrate post layout simulations on various P-FF designs were conducted to obtain their performance figures.

These designs include the 6 P-FF designs shown in Fig. 3.1(b)EP-DCO, Fig. 3.1(d) SCDFF, Fig.

3.1(f)CDFF,3.1(h)MHLFF,3.2(b) to the correctness of data capturing as well as the power consumption. All designs are

further optimized subject to the tradeoffs between power and D-to-Q delay.

EP-DCO:

Figure 4(a)-Simulation output EP-DCO using Tanner Tool.

Figure 4(b) Power consumed by EP-DCO using in Microwind tool in 90nm.

SCDFF:

Figure 4(c)Simulation output SCDFF using Tanner Tool.

Copyright to IJAREEIE

www.ijareeie.com

9714

ISSN (Print) : 2320 3765

ISSN (Online): 2278 8875

International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 5, May 2014

Figure 4 (d) Power consumed by SCDFF using in Microwind tool in 90nm.

CDFF:

Figure 4(e)-Simulation output CDFF using Tanner Tool.

Figure 4(f)-Power consumed by CDFF using in Microwind tool in 90nm.

MHLFF:

Copyright to IJAREEIE

www.ijareeie.com

9715

ISSN (Print) : 2320 3765

ISSN (Online): 2278 8875

International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 5, May 2014

Figure 4(g)-Simulation output MHLFF using Tanner Tool.

Figure 4 (h)Power consumed by MHLFF using in Microwind tool in 90nm.

TSPCFF:

Figure 4(i)Simulation outputTSPCFF using Tanner Tool.

Figure 4 (j)Power consumed by TSPCFF using in Microwind tool in 90nm.

PTLFF:

Figure 4(k)Simulation output PTLFF using Tanner Tool.

Copyright to IJAREEIE

www.ijareeie.com

9716

ISSN (Print) : 2320 3765

ISSN (Online): 2278 8875

International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 5, May 2014

Figure 4 (l)-Power consumed by PTLFF using in Microwind tool in 90nm.

Table 1. Comparison of various P-FF designs

P-FF

(Pulse Trigger

Flop)

No. of transistors

Flip

EP-DCO

SCDFF

CDFF

MHLFF

TSPCFF

Proposed

PTLFF

28

31

30

19

24

17

159.3

174

173.4

128.4

163.2

117.6

9.42

9.61

9.37

1530

711.69

853.8

9.27

615

7.57

520

3.57

508

Area m

UMC CMOS-90nm

Avg. Power (W) Using

UMC CMOS-90nm

Technology.(W).

Delay(ps)

V.CONCLUSION

In this Paper, the various Flip flop design like, EP-DCO, MHLLF, SCDFF, CDFF,TSPC based P-FF &Proposed NEW

P-FF are discussed. The Pass Transistor logic Flip Flop (PTLFF) design by employing two new design measures. The

first one successfully reduces the number of transistors stacked along the discharging path by incorporating a PTLbased AND logic. The second one supports conditional enhancement to the height and width of the discharging pulse

so that the size of the transistors in the pulse generation circuit can be kept minimum. These were been also designed in

Tanner Tool& Micro wind Tool those result waveforms are also discussed. The comparison table also added to verify

the designed methods using UMC CMOS 90-nm technology. With these all results Proposed PTLFF performed speed

or power better than EP-DCO, MHLLF, SCDFF, CDFF and TSPCFF designs.

REFERENCES

[1] H. Kawaguchi and T. Sakurai, A reduced clock-swing flip-flop (RCSFF) for 63% power reduction, IEEE J. Solid-State Circuits, vol. 33, no. 5,

pp. 807811, May 1998.

[2] K. Chen, A 77% energy saving 22-transistor single phase clocking Dflip-flop with adoptive-coupling configuration in 40 nm CMOS, in Proc.

IEEE Int. Solid-State Circuits Conf., Nov. 2011, pp. 338339.

[3] E. Consoli, M. Alioto, G. Palumbo, and J. Rabaey, Conditional pushpull pulsed latch with 726 fJops energy delay product in 65 nm CMOS, in

Proc. IEEE Int. Solid-State Circuits Conf., Feb. 2012, pp. 482483.

[4] H. Partovi, R. Burd, U. Salim, F.Weber, L. DiGregorio, and D. Draper, Flow-through latch and edge-triggered flip-flop hybrid elements, in

Proc. IEEE Int. Solid-State Circuits Conf., Feb. 1996,pp. 138139.

[5] F. Klass, C. Amir, A. Das, K. Aingaran, C. Truong, R. Wang, A. Mehta,R. Heald, and G. Yee, A new family of semi-dynamic and dynamic flipflops with embedded logic for high-performance processors, IEEE J. Solid-State Circuits, vol. 34, no. 5, pp. 712716, May 1999.

[6] V. Stojanovic and V. Oklobdzija, Comparative analysis of masterslave latches and flip-flops for high-performance and low-power systems,

IEEE J. Solid-State Circuits, vol. 34, no. 4, pp. 536548,Apr. 1999.

[7] J. Tschanz, S. Narendra, Z. Chen, S. Borkar, M. Sachdev, and V. De,Comparative delay and energy of single edge-triggered and dual edge

triggered pulsed flip-flops for high-performance microprocessors, in Proc. ISPLED, 2001, pp. 207212.

[8] S. D. Naffziger, G. Colon-Bonet, T. Fischer, R. Riedlinger, T. J.Sullivan, and T. Grutkowski, The implementation of the Itanium 2

microprocessor, IEEE J. Solid-State Circuits, vol. 37, no. 11,pp. 14481460, Nov. 2002.

[9] S. Sadrossadat, H. Mostafa, and M. Anis, Statistical design frameworkof sub-micron flip-flop circuits considering die-to-die and within-die

variations, IEEE Trans. Semicond. Manuf., vol. 24, no. 2, pp. 6979,Feb. 2011.

[10] M. Alioto, E. Consoli, and G. Palumbo, General strategies to design nanometer flip-flops in the energy-delay space, IEEE Trans. Circuits

Syst., vol. 57, no. 7, pp. 15831596, Jul. 2010.

Copyright to IJAREEIE

www.ijareeie.com

9717

ISSN (Print) : 2320 3765

ISSN (Online): 2278 8875

International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 5, May 2014

[11] M. Alioto, E. Consoli, and G. Palumbo, Flip-flop energy/performance versus Clock Slope and impact on the clock network design, IEEE

Trans. Circuits Syst., vol. 57, no. 6, pp. 12731286, Jun. 2010.

[12] M. Alioto, E. Consoli, and G. Palumbo, Analysis and comparison in the energy-delay-area domain of nanometer CMOS flip-flops: Part I methodology and design strategies, IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 19, no. 5, pp. 725736, May 2011.

[13] M. Alioto, E. Consoli and G. Palumbo, Analysis and comparison in the energy-delay-area domain of nanometer CMOS flip-flops: Part II results and figures of merit, IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 19, no. 5, pp. 737750, May 2011.

[14] B. Kong, S. Kim, and Y. Jun, Conditional-capture flip-flop for statistical power reduction, IEEE J. Solid-State Circuits, vol. 36, no. 8, pp.

12631271, Aug. 2001.

[15] N. Nedovic, M. Aleksic, and V. G. Oklobdzija, Conditional precharge techniques for power-efficient dual-edge clocking, in Proc. Int. Symp.

Low-Power Electron. Design, Aug. 2002, pp. 5659.

[16] P. Zhao, T. Darwish, and M. Bayoumi, High-performance and low power conditional discharge flip-flop, IEEE Trans. Very Large Scale

Integr. (VLSI) Syst., vol. 12, no. 5, pp. 477484.

BIOGRAPHY

CH.vijayalakshmi received the Electronics Engineering P.G degree from JNTU, KAKINADA in 2012.Since 2008, She has been

working as assistant professor in the department of electronics and communication engineering for TECA,

ANUMARLAPUDI,GUNTUR DISTRICT ,ANDHRAPRADESH,INDIA. She is currently with st.martins engineering

college,dhulapally,secunderabad,India

S.Vijayalakshmi received the BE degree in Electronics and Communication Engineering from Coimbatore Institute of Engineering and

Information Technology, CBE,in 2009, the ME(VLSI Design) from Karpagam College of Engineering,CBE, in 2011.

She has published three international Journal ,she has presented three international conference and two national conference. She

has worked two years in Bannariamman Institute of Technology,Sathyamangalam-Tamilnadu and one year worked in St.Martins

Engineering College-Secunderabad.

Correspondence Author:viji_ciet58@yahoo.co.in

M.Vijaya Lakshmi received the degree in Electronics & Communication Engineering from GPREC, Kurnool in 2000, Masters in Electronics &

Communication Engineering from JNTU, Hyderabad in 2009. Presently, she is working as Associate Professor in ECE department in

St.Martins Engineering College, Secunderabad.

Copyright to IJAREEIE

www.ijareeie.com

9718

You might also like

- Low-Power Pulse-Triggered Flip-Flop Design Based On A Signal Feed-Through SchemeDocument5 pagesLow-Power Pulse-Triggered Flip-Flop Design Based On A Signal Feed-Through SchemeNano Scientific Research Centre pvt ltdNo ratings yet

- Pulse Triggered Flip Flop Design With Signal Feed Through Scheme Using Conditional Pulse Enhancement TechniqueDocument6 pagesPulse Triggered Flip Flop Design With Signal Feed Through Scheme Using Conditional Pulse Enhancement TechniqueIJSTENo ratings yet

- Enhancement Scheme Low Power Pulse Triggered Flipflop With Conditional PulseDocument14 pagesEnhancement Scheme Low Power Pulse Triggered Flipflop With Conditional PulseiaetsdiaetsdNo ratings yet

- A Low Power Single Phase Clock Distribution Using VLSI TechnologyDocument5 pagesA Low Power Single Phase Clock Distribution Using VLSI TechnologyNano Scientific Research Centre pvt ltd100% (1)

- Transactions Briefs: Low Voltage and Low Power Divide-By-2/3 Counter Design Using Pass Transistor Logic Circuit TechniqueDocument5 pagesTransactions Briefs: Low Voltage and Low Power Divide-By-2/3 Counter Design Using Pass Transistor Logic Circuit TechniquethusharajayeshNo ratings yet

- Design of Direct CPSFF Flip-Flop For Low Power ApplicationsDocument4 pagesDesign of Direct CPSFF Flip-Flop For Low Power ApplicationsWARSE JournalsNo ratings yet

- A Fully Static True-Single-Phase-Clocked Dual-Edge-Triggered Flip-Flop For Near-Threshold Voltage Operation in Iot ApplicationsDocument14 pagesA Fully Static True-Single-Phase-Clocked Dual-Edge-Triggered Flip-Flop For Near-Threshold Voltage Operation in Iot Applicationsaman shaikhNo ratings yet

- Ijoer Aug 2015 19 PDFDocument7 pagesIjoer Aug 2015 19 PDFEngineering JournalNo ratings yet

- A Review On Design A Low Power Flip Flop Based On A Signal 26bef0lyejDocument4 pagesA Review On Design A Low Power Flip Flop Based On A Signal 26bef0lyejVijay KumarNo ratings yet

- Asynchronous Data Sampling Within Clock-Gated Double Edge Triggered Flip-FlopsDocument6 pagesAsynchronous Data Sampling Within Clock-Gated Double Edge Triggered Flip-Flopsblessysara16No ratings yet

- A Hybrid Topology For Frequency Divider Using PLL ApplicationDocument6 pagesA Hybrid Topology For Frequency Divider Using PLL ApplicationParamesh WaranNo ratings yet

- Low Power CMOS Digital Circuit Design Methodologies With Reduced Voltage SwingDocument4 pagesLow Power CMOS Digital Circuit Design Methodologies With Reduced Voltage SwingMaheshNo ratings yet

- Clock Branch Shared Flip FlopDocument8 pagesClock Branch Shared Flip Flopprabhug7No ratings yet

- Implementation of 2.4 GHZ Phase Locked Loop Using Sigma Delta ModulatorDocument6 pagesImplementation of 2.4 GHZ Phase Locked Loop Using Sigma Delta ModulatorInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Finfet Based Ring OscillatorDocument6 pagesFinfet Based Ring Oscillatorrgangadhar049236No ratings yet

- Power-Delay Efficient Overlap-Based Charge-Sharing Free Pseudo-Dynamic D Flip-FlopsDocument4 pagesPower-Delay Efficient Overlap-Based Charge-Sharing Free Pseudo-Dynamic D Flip-FlopsGopi PremalaNo ratings yet

- A Partially Static High Frequency 18T Hybrid Topological Flip-Flop Design For Low Power ApplicationDocument5 pagesA Partially Static High Frequency 18T Hybrid Topological Flip-Flop Design For Low Power ApplicationRatnakarVarunNo ratings yet

- Jecet: Journal of Electronics and Communication Engineering & Technology (JECET)Document11 pagesJecet: Journal of Electronics and Communication Engineering & Technology (JECET)IAEME PublicationNo ratings yet

- A 5-Ghz Programmable Frequency Divider in 0.18-M Cmos TechnologyDocument5 pagesA 5-Ghz Programmable Frequency Divider in 0.18-M Cmos TechnologyAram ShishmanyanNo ratings yet

- A Robust Design of Highly Efficient Dynamic Comparator Using Wave PipeliningDocument4 pagesA Robust Design of Highly Efficient Dynamic Comparator Using Wave PipeliningIJARTETNo ratings yet

- BJT Pulse PDFDocument6 pagesBJT Pulse PDFmenguemengueNo ratings yet

- A New Design Technique For Low Power Dynamic Feedthrough Logic With Delay ElementDocument5 pagesA New Design Technique For Low Power Dynamic Feedthrough Logic With Delay ElementET181018 Md Maharaj KabirNo ratings yet

- Implementation of High Speed and Low Power 5T-TSPC D Flip-Flop and Its ApplicationDocument5 pagesImplementation of High Speed and Low Power 5T-TSPC D Flip-Flop and Its ApplicationJaya Chandra ManchalaNo ratings yet

- Low Power 6-Transistor Latch Design For Portable DevicesDocument16 pagesLow Power 6-Transistor Latch Design For Portable DevicesjayalakshmisnairNo ratings yet

- A Fully Static Topologically-Compressed 21-Transistor Flip-Flop With 75% Power SavingDocument8 pagesA Fully Static Topologically-Compressed 21-Transistor Flip-Flop With 75% Power SavingSaiteja GundapuNo ratings yet

- Fast Frequency Acquisition Phase-Frequency Detectors For Gsamples S Phase-Locked LoopsDocument4 pagesFast Frequency Acquisition Phase-Frequency Detectors For Gsamples S Phase-Locked LoopsGavin WangNo ratings yet

- Design and Optimization of ÷8/9 Divider in PLL Frequency Synthesizer With Dynamic Logic (E - TSPC)Document5 pagesDesign and Optimization of ÷8/9 Divider in PLL Frequency Synthesizer With Dynamic Logic (E - TSPC)himaja1No ratings yet

- 22.doc Front EndDocument58 pages22.doc Front EndGowtham SpNo ratings yet

- Analysis of Energy Efficient PTL Based Full Adders Using Different Nanometer TechnologiesDocument6 pagesAnalysis of Energy Efficient PTL Based Full Adders Using Different Nanometer TechnologiesDwarakaManeekantaAddagiriNo ratings yet

- Low Power and Area Efficient Static Differential Sense Amplifier Shared Pulse LatchDocument8 pagesLow Power and Area Efficient Static Differential Sense Amplifier Shared Pulse LatchSesharatnam KoppulaNo ratings yet

- TFETDocument4 pagesTFETSurya KalagaNo ratings yet

- A Subpicosecond Jitter PLL For Clock Generation in 0.12-: M Digital CMOSDocument4 pagesA Subpicosecond Jitter PLL For Clock Generation in 0.12-: M Digital CMOSscribdaccount078No ratings yet

- Anti-Interference Low-Power Double-Edge Triggered Flip-Flop Based On C-ElementsDocument12 pagesAnti-Interference Low-Power Double-Edge Triggered Flip-Flop Based On C-ElementsVani YamaniNo ratings yet

- Hati 2015Document6 pagesHati 2015Ahmed ShafeekNo ratings yet

- Ibm PllserdesDocument3 pagesIbm PllserdesMeeraNo ratings yet

- Quickchip Design Example 1 - A Silicon Bipolar Broadband PLL Building Block Integrated CircuitDocument7 pagesQuickchip Design Example 1 - A Silicon Bipolar Broadband PLL Building Block Integrated Circuitflo724No ratings yet

- P V F C P: V V V F P C P C P I C PDocument4 pagesP V F C P: V V V F P C P C P I C PDuc DucNo ratings yet

- A Novel High Speed and Energy Efficient 10 Transistor Full Adder DesignDocument20 pagesA Novel High Speed and Energy Efficient 10 Transistor Full Adder Designneethusebastian1989No ratings yet

- Chip IO Circuit Design - Input Ouput CircuitryDocument9 pagesChip IO Circuit Design - Input Ouput CircuitryVăn CôngNo ratings yet

- Design of All Digital Phase Locked LoopDocument4 pagesDesign of All Digital Phase Locked LoopInternational Journal of Research in Engineering and TechnologyNo ratings yet

- PLL 4Document9 pagesPLL 4vermavikki97No ratings yet

- Impact of Hybrid Pass-Transistor Logic (HPTL) On Power, Delay and Area in VLSI DesignDocument6 pagesImpact of Hybrid Pass-Transistor Logic (HPTL) On Power, Delay and Area in VLSI DesignIJMERNo ratings yet

- SeminarDocument9 pagesSeminarelaheh.hassanzadeh6No ratings yet

- Low Power Phase Locked Loop Frequency Synthesizer For 2.4 GHZ Band ZigbeeDocument7 pagesLow Power Phase Locked Loop Frequency Synthesizer For 2.4 GHZ Band ZigbeeNandish MahalingappaNo ratings yet

- Analysis and Optimization of Active Power and Delay of 10T Full Adder Using Power Gating Technique at 45 NM TechnologyDocument7 pagesAnalysis and Optimization of Active Power and Delay of 10T Full Adder Using Power Gating Technique at 45 NM TechnologyInternational Organization of Scientific Research (IOSR)No ratings yet

- Design of Integer N Frequency Divider For High Performance PLL Using 180 NM CMOS TechnologyDocument8 pagesDesign of Integer N Frequency Divider For High Performance PLL Using 180 NM CMOS Technology123abhijeetNo ratings yet

- D 119Document35 pagesD 119Mohammad Ayatullah MaktoomNo ratings yet

- 11 A Low-Power Single-Phase Clock MultibandDocument5 pages11 A Low-Power Single-Phase Clock MultibandDilip KumarNo ratings yet

- Flip Flop PDFDocument5 pagesFlip Flop PDFarevazhagunvcNo ratings yet

- Welcome To International Journal of Engineering Research and Development (IJERD)Document6 pagesWelcome To International Journal of Engineering Research and Development (IJERD)IJERDNo ratings yet

- Double Edge Triggered Feedback Flip-Flop: S. H. Rasouli, A. Amirabadi, A. S. Seyedi and A. Afzali-KushaDocument31 pagesDouble Edge Triggered Feedback Flip-Flop: S. H. Rasouli, A. Amirabadi, A. S. Seyedi and A. Afzali-KushaSanjay ChNo ratings yet

- Advances in Engineering: An International Journal (ADEIJ)Document9 pagesAdvances in Engineering: An International Journal (ADEIJ)adeijNo ratings yet

- Microelectronics Journal: Habib Rastegar, Jee-Youl RyuDocument8 pagesMicroelectronics Journal: Habib Rastegar, Jee-Youl RyuRAJAMOHANNo ratings yet

- Design of A "7490-Like" Decade-Counter Integrated Circuit, Using Gaas Mesfet DCFL Family, For Frequencies Up To 1 GHZDocument8 pagesDesign of A "7490-Like" Decade-Counter Integrated Circuit, Using Gaas Mesfet DCFL Family, For Frequencies Up To 1 GHZsoudamallarajeshNo ratings yet

- Ofc Lab Manual 2Document21 pagesOfc Lab Manual 2Shobhit JainNo ratings yet

- Blind Paper SpineDocument5 pagesBlind Paper SpineJoao PauloNo ratings yet

- A 0.0021 mm2 1.82 MW 2.2 GHZ PLL Using Time-Based Integral Control in 65 NM CMOSDocument13 pagesA 0.0021 mm2 1.82 MW 2.2 GHZ PLL Using Time-Based Integral Control in 65 NM CMOSnayakadarsh2000No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1From EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Rating: 4.5 out of 5 stars4.5/5 (3)

- STLD CourseDocument182 pagesSTLD CourseChintamaneni VijayalakshmiNo ratings yet

- 07327182Document13 pages07327182Chintamaneni VijayalakshmiNo ratings yet

- Ieee Tip05Document24 pagesIeee Tip05Chintamaneni VijayalakshmiNo ratings yet

- Phdrenotification07112016 PDFDocument1 pagePhdrenotification07112016 PDFChintamaneni VijayalakshmiNo ratings yet

- Implementation of Carry Save Adder in Radix 10 MultiplierDocument12 pagesImplementation of Carry Save Adder in Radix 10 MultiplierChintamaneni VijayalakshmiNo ratings yet

- Embedded SystemsDocument14 pagesEmbedded SystemsChintamaneni VijayalakshmiNo ratings yet

- 4 1 ECE R13 SyllabusDocument16 pages4 1 ECE R13 SyllabusAnonymous rcmeSfj5No ratings yet

- DC LAB Experiments As Per The New FormatDocument2 pagesDC LAB Experiments As Per The New FormatChintamaneni VijayalakshmiNo ratings yet

- Presentation 1Document1 pagePresentation 1Chintamaneni VijayalakshmiNo ratings yet

- 1Document7 pages1Chintamaneni VijayalakshmiNo ratings yet

- ST - Martin'S Engineering College: Department of Electronics and Communication EngineeringDocument2 pagesST - Martin'S Engineering College: Department of Electronics and Communication EngineeringChintamaneni VijayalakshmiNo ratings yet

- MPMC EceaDocument155 pagesMPMC EceaChintamaneni VijayalakshmiNo ratings yet

- DDV Tutorial NewformatDocument3 pagesDDV Tutorial NewformatChintamaneni VijayalakshmiNo ratings yet

- AC Lab Manual NewDocument66 pagesAC Lab Manual NewChintamaneni VijayalakshmiNo ratings yet

- Mechanical Lab ExpDocument5 pagesMechanical Lab ExpChintamaneni VijayalakshmiNo ratings yet

- 45 2copies Low Power PassDocument13 pages45 2copies Low Power PassChintamaneni VijayalakshmiNo ratings yet

- Eee Mid 2 Civil IibDocument3 pagesEee Mid 2 Civil IibChintamaneni VijayalakshmiNo ratings yet

- Capabilties and Transform of Seq CktsDocument27 pagesCapabilties and Transform of Seq CktsVijay Papi Reddy AllamNo ratings yet

- Dip Mid 1Document3 pagesDip Mid 1Chintamaneni VijayalakshmiNo ratings yet

- Circular: ST - Martin'S Engineering College Department of Electronics and Communication EngineeringDocument1 pageCircular: ST - Martin'S Engineering College Department of Electronics and Communication EngineeringChintamaneni VijayalakshmiNo ratings yet

- Morphological Image Processing - Part1Document59 pagesMorphological Image Processing - Part1Sudhakar Yadav100% (1)

- Management 2011 12Document174 pagesManagement 2011 12abhishekpaneriNo ratings yet

- Project Expenses Estimate:: Item ListDocument1 pageProject Expenses Estimate:: Item ListChintamaneni VijayalakshmiNo ratings yet

- HTTP WWW - Eenadupratibha.net Pratibha OnlineDesk Previous Papers SBIAugPo - PDF Path Content CSW V2 Folders 6211 SBHDocument13 pagesHTTP WWW - Eenadupratibha.net Pratibha OnlineDesk Previous Papers SBIAugPo - PDF Path Content CSW V2 Folders 6211 SBHGaini ChakravarthyNo ratings yet

- MS43 Solved Assignment2012.55192524Document9 pagesMS43 Solved Assignment2012.55192524Chintamaneni VijayalakshmiNo ratings yet

- Brochure Microwave Workshop PICT PuneDocument2 pagesBrochure Microwave Workshop PICT PuneChintamaneni VijayalakshmiNo ratings yet

- Switching FunctionsDocument44 pagesSwitching FunctionsChintamaneni VijayalakshmiNo ratings yet

- Boolean Algebra: - Also Known As Switching AlgebraDocument21 pagesBoolean Algebra: - Also Known As Switching AlgebraAnkur SinghNo ratings yet

- SeminarDocument15 pagesSeminarAkhil GuliaNo ratings yet

- Wharfadale SVP-X Users ManualDocument12 pagesWharfadale SVP-X Users ManualrdbassesNo ratings yet

- Digital Multimeter Selection GuideDocument3 pagesDigital Multimeter Selection GuideThomas VargheseNo ratings yet

- Problems in DecibelsDocument6 pagesProblems in DecibelsLara Jane ReyesNo ratings yet

- Cost EsDocument2 pagesCost EsJely Taburnal BermundoNo ratings yet

- Ayantika Khanra UG23Document42 pagesAyantika Khanra UG23Anisha GoenkaNo ratings yet

- 00 - 2 2Document10 pages00 - 2 2patitay036817No ratings yet

- Icom OPC-478PIXDocument27 pagesIcom OPC-478PIXBram HtbaratNo ratings yet

- Operacion y Mantenimiento de ReconectadoresDocument5 pagesOperacion y Mantenimiento de ReconectadoresCUAL QUIERANo ratings yet

- GZRW 30splextremeDocument2 pagesGZRW 30splextremekamil palbickiNo ratings yet

- Load Flow Analysis & Simulation On IEEE 30 Bus SystemDocument10 pagesLoad Flow Analysis & Simulation On IEEE 30 Bus SystemhakandaghanNo ratings yet

- Sonic Bomb Alarm Clock User ManualDocument5 pagesSonic Bomb Alarm Clock User ManualZariab KhanNo ratings yet

- Electrochemistry Study GuideDocument2 pagesElectrochemistry Study GuideAbhi DevathiNo ratings yet

- 1KHW001495ee Commissioning of ETL600Document16 pages1KHW001495ee Commissioning of ETL600Salvador FayssalNo ratings yet

- Is 4559 1993 PDFDocument13 pagesIs 4559 1993 PDFbaldau vermaNo ratings yet

- DT09Document10 pagesDT09Alexander OsorioNo ratings yet

- Midas Venice ManualDocument29 pagesMidas Venice Manualcb4pdfsNo ratings yet

- Electrical Engineering Department: Practical Work (Lab 2) Dee 20023 Semiconductor Devices Program: Dep / DTKDocument7 pagesElectrical Engineering Department: Practical Work (Lab 2) Dee 20023 Semiconductor Devices Program: Dep / DTKSarahmei MeiNo ratings yet

- Principles of Communications Chapter 4Document7 pagesPrinciples of Communications Chapter 4Aileen May Santillan HerreraNo ratings yet

- Analog Mod NotesDocument50 pagesAnalog Mod NotesSmriti Rai M.Tech. Dept. of Electronics Engg. IIT (BHU)No ratings yet

- David EsseiniDocument10 pagesDavid Esseiniশুভ MitraNo ratings yet

- Super Spark CatDocument2 pagesSuper Spark CatantonmboxNo ratings yet

- As 2353-1999 Pedestrian Push-Button AssembliesDocument7 pagesAs 2353-1999 Pedestrian Push-Button AssembliesSAI Global - APACNo ratings yet

- Advanced Power Electronics Corp.: AP72T02GH/JDocument6 pagesAdvanced Power Electronics Corp.: AP72T02GH/JFrancisco MataNo ratings yet

- Electrical Power Systems Wadhwa 15Document1 pageElectrical Power Systems Wadhwa 15ragupaNo ratings yet

- 8.03 Fall 2004 Problem Set 2 SolutionsDocument15 pages8.03 Fall 2004 Problem Set 2 SolutionseviroyerNo ratings yet

- Fermator VF5 - ManualDocument24 pagesFermator VF5 - ManualMohammed HussenNo ratings yet

- Lexium 32A User GuideDocument508 pagesLexium 32A User GuideDave CárdenasNo ratings yet

- Isc N-Channel MOSFET Transistor 75N08: INCHANGE Semiconductor Product SpecificationDocument2 pagesIsc N-Channel MOSFET Transistor 75N08: INCHANGE Semiconductor Product Specificationmateus santosNo ratings yet

- Dependent SourcesDocument26 pagesDependent SourcesSibtain RazaNo ratings yet