Professional Documents

Culture Documents

CSEE W4840 Embedded Lab 1 - Memory Display

Uploaded by

microbotica126Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CSEE W4840 Embedded Lab 1 - Memory Display

Uploaded by

microbotica126Copyright:

Available Formats

CSEE W4840 Embedded System Design Lab 1

Abstract

Learn to use the Altera Quartus development

environment and the SoCkit boards by implementing a

small hardware design that displays and modifies the

contents of an on-chip memory.

1 Introduction

In this lab, we are going to use the Altera SoCkit

board to implement a simple hardware design. Describe

its behavior using the Verilog language and use Alteras

Quartus tools to synthesize and program the FPGA

device. Finally, we will use a Verilog simulator to verify

and debug the design.

The circuit you program into the FPGA will display

and modify the contents of an on-chip memory. Use four

pushbuttons as inputs and eight seven-segment LED

emulator displays on VGA as outputs (actually you will

only need to use three at this time). Two push buttons

should step up and down through the sixteen RAM

locations; the other two should increment and decrement

the contents of the currently-displayed memory location.

One seven segment LED display should show the current

address (0F), two others should display the contents of

that location in hexadecimal (00FF).

You will learn to set up a project in the Altera

Quartus tool, run a Verilog simulation, and compile and

download your design to the FPGA. Verilog is a hardware

description language, and the process of using it is very

different than developing programs in C++ or Java. You

will need these skills in later labs and while you are

developing your project.

Below, we introduce the SoCkit board, show how to

start a new project from a template, add Verilog code to a

project, simulate it, and compile and download a design to

the FPGA.

2 The SoCkit Board

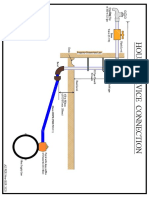

Figure 1 shows the Altera SoCkit board. It consists of

an Altera 28-nm Cyclone V (FPGA) with a Dual-core

ARM Cortex-A9 (HPS), providing powerful storage

(1GB DDR3 SDRAM on FPGA, 1GB DDR3 SDRAM on

HPS, 128MB QSPI Flash on HPS, Micro SD Card Sockit

on HPS), and connected to a variety of peripherals

including VGA output, Ethernet, audio input and output,

and USB ports. For this lab, we will use four of the eight

seven-segment LEDs on VGA, and the four black

pushbuttons. There are three micro-USB connectors on

the top of the board. The leftmost one the one nearest

the 12V DC connector is for connecting the Altera

Blaster cable to the workstation. It is through this

connection that the FPGA will be programmed, that

debugging information flows, etc. The other two USB

ports can be used in projects.

The SoCkit board holds two quartz crystal

oscillators (clock sources: little silver boxes labeled with

their frequencies). We will use the 50 MHz clock for this

lab.

The SoCkit board has built-in configuration for

testing and demonstration purpose. You can verify the

board is working properly by observing this default

behavior. Use the following procedure to power up the

SoCkit board.

Connect the USB blaster cable from the USB port on

the workstation to the USB Blaster connector on the

SoCkit board. Connect the 12V adapter to the SoCkits

power connector at the top left corner.

Power on the SoCkit board by pressing the red

ON/OFF switch in the upper left corner, the two blue

LEDs on top of the board should flash, the blue backlight

of the LCD, four LED at the bottom and the VGA output

should display an Altera/Terasic logo page.

To download our design to the FPGA, we use a

JTAG connection (JTAG is a ubiquitous standard that

stands for the IEEE Joint Test Action Group). The Altera

Quartus tool running on the workstation sends the

configuration bit stream through the USB cable to the

Cyclone V FPGA. Once programmed, the FPGA retains

its configuration as long as power is applied to the board;

it is lost when the power is turned off. We cover the

details of this process below.

3 Getting Started with Quartus

Quartus is Alteras development environment for

FPGAs. It consists of an IDE and a compiler that can

translate circuits described in Verilog into configuration

data for the FPGA. Start the Quartus IDE by running the

Quartus command. This requires the PATH and

LM_LICENSE_FILE environment variables to be set.

Altera provides a variety of reference designs for the

SoCkit. For lab 1, we modified the default SoCkit design,

which contains information about what each pin on the

FPGA is connected to and a top-level Verilog module with

a port for each pin.

Download the lab1.tar.gz file from the class website

and extract it with tar zxf lab1.tar.gz This will place the

project files, listed in Table 1, in the current directory.

Table 1: Files in the Lab1 project

Name

Role

Lab1.qpf

Quartus Project File

SoCKit_Default.qsf Pin assignments, etc.

SoCKit_Top.v

Top-level Verilog file

Reset_Delay.v

Generate reset signal

Video_Sync.v

Generate sync signal for VGA

Number_Display.v

Display one LED on VGA

Number_8_Bit.v

Display eight LEDs on VGA

VGA_Control.v

Control the display of VGA

PLL.v

Generate 25MHz clock

Lab1.qpf is the top Quartus project file. To open

the project file, use File--Open Project and select

Lab1.qpf. Once the project is opened, you can see and

change I/O pin assignments with Assignment

--Assignment Editor. Figure 2 shows this.

For Quartus to configure an FPGA, it must know

which pins on the FPGA perform what roles (i.e., what

each is named). This information is board-specific

since the pins on the FPGA can be wired to arbitrary

peripherals. The SoCKit_Default.qsf file contains this

information for the SoCKit board. SoCKit_Top.v is the

top-level Verilog module for the project, which mostly

lists the top-level ports, i.e., the Verilog names for the

pins.

Although you do not need to modify I/O pin settings

for this lab, you may need to do so in the future.

AssignmentPin Planner, shown in Figure 3, opens a

display that shows the physical location the pins on the

FPGA and their assignments.

Another way to assign pins is to start with a pin

assignment file in CSV format. While you do not need

one for this lab, you will need to do so later: go to

Assignments--Import Assignments.

You may notice theres a PLL.v file in the package.

PLL stands for Phase-Locked Loop. Its a closed-loop

frequency control system that compares the phase

difference between the input signal and the output signal

of a Voltage-controlled oscillator (VCO). Its used here to

generate customized and stable frequencies. you do not

need to generate PLL.v file for this lab(its already set up

for you), but if you are curious, go to Tool--MegaWizard

Plug-In Manager, create a new custom megafunction

variation, type in file name: PLL.v as shown in figure 4,

and configure the clk frequency to 25MHz as shown in

figure 5.

4 Compiling for the FPGA

The supplied project can be compiled and

downloaded to the board, although it does not do much.

First, make sure all the source files are included in the

project. From the Project Navigator window, click on the

Files tab, this will display the Verilog files that will be

compiled into the FPGA. To add a file, select Project-Add/Remove Files in Project. This opens the window in

Figure 6.

Select Verilog files from the pop-up window. If you have

written multiple Verilog files, add each of them. Do not

add any test benches (used for simulation) to the list of

device design files since they cannot be compiled into

hardware.

Make sure you indicate which file that contains the

Top Entity: right-click the appropriate file in the main list

of files (i.e., after you have added them, as shown in

figure 7).

Now we are ready to compile. Select Processing

--Start Compilation to start the compilation process

(Figure 8). The window on the left reports the compilation

progress. A pop-up appears when compilation completes.

If there are errors, use the Messages window to locate

them (Figure 9). As usual, the first error listed is most

trustworthy; any others may be due to earlier errors. A

compilation process usually generates some warnings.

Most are harmless, but it is worth fixing them to avoid

masking a genuine problem.

Double clicking on an error message will highlight

the suspect Verilog in the editor window. The compiler

may also display warning messages, which can be

explored in the same way. You can obtain more

information about a specific error or warning by selecting

it and pressing the F1 key.

4.1 Programming the FPGA

Once your design has been compiled, it can be

downloaded to the FPGA. Select Tools -- Programmer -Add File, and under the output folder you should see

the Lab1.sof file. After adding this file, we should also

select Add Device, and choose Soc Series V -- SOCVHPS

(shown in figure 10). A little trick: Always list the SOC

device under your output file, otherwise the download

will fail. Finally the window should display like Figure

11.

You may have to click on the Hardware Setup...

button and select the USB-Blaster cable. Make sure the

boards USB cable is plugged into the port marked

blaster (i.e., nearest the power connector).

Click the check box under Program/Configure for

the Lab1.sof file destined for the FPGA and then click

Start to download your design to the FPGA. If all goes

well, the design should spring to life.

5 Editing Verilog

The next step is to code your circuit in Verilog.

Quartus provides a good Verilog text editor, which

provides syntax highlighting, language templates, and

other aspects of a good IDE. To create a new Verilog file

in your project, select File -- New. This will bring up the

dialog in Figure 12. Select the Verilog file option and

click OK. This brings up a window where you can enter

Verilog code.

The verbose syntax of Verilog is probably unfamiliar to

you. To help, the Quartus tool provides a collection of

Verilog templates, which provide examples of various

types of Verilog constructs, such as an entity declaration,

a process statement, and an assignment statement. To use

a Verilog template, select Edit -- Insert Template. This

will open a window such as Figure 13. Select Verilog

HDL and the type of template you want. The Insert

button inserts the template in the active source file. Then

fill in the details in the template, such as the name of a

module.

6 The Lab 1 Design

Your

goal

is

to

implement

memory

display/modification circuit whose block diagram is

shown in Figure 14. Input ports are on the left; output

ports are on the right.

To add the lab1 component to the project, instantiate

it in the top-level architecture in SoCKit_Top.v

Lab1 lab_1 (.clk (OSC_50_B3B),

.key(KEY),

.hex6(hex6),

.hex5(hex5),

.hex4(hex4)

);

Here, the ports on your Lab1 module are mapped to

top level ports. The naming of these top level ports, such

as OSC_50_B3B, KEY and hex6, are all defined in the

SoCKit_Default.qsf file. The ports named in the

SoCKit_Top.v and qsf file must match.

Here, lab_1 is the name of the instance. Note that

you can pick any valid Verilog name for it; you can use

this name to refer to the instance in simulation.

Remember to disable the constant assignments to

hex4, hex5, and hex6 in the SoCKit_Top.v file when you

add your Lab1 module.

6.1 RAM

Your design should include a 168 bit RAM, but

what kind of RAM? The SoCKit board contains an

SRAM chip, an SDRAM chip, and RAM within the

FPGA itself. The SDRAM chip provides the highest

capacity but requires a complicated controller. The SRAM

chip is smaller, much simpler to use, and provides more

storage than RAM on the FPGA. However, RAM internal

to the FPGA, so-called block RAM, is the smallest,

fastest, and easiest to use. Use it for this lab.

The FPGA block RAM can be configured in many

different ways, e.g., as one big memory, as many small

regions, and as bits, bytes, or words. The easiest way to

ask for a particular type of RAM is to allow the Quartus

tool

to infer

it from the

of an array data_out);

in Verilog. Below

module

raminfr(clk,

we,use

addr,data_in,

isinput

code fromclk;which Quartus will infer a small RAM

block.

input

we;

input [3:0] addr;

input [7:0] data_in;

output [7:0] data_out;

//Declare the ram variable

reg [7:0] ram [15:0];

//variable to hold the registered read address

reg [3:0] read_addr = 4'b0;

always@(posedge clk)

begin

//write

if(we)

begin

ram[addr] <= data_in;

end

read_addr <= addr;

end

assign data_out = ram[read_addr];

endmodule

6.2 Eight-Segment LEDs

The block diagram in Figure 14 includes three eightsegment LED output decoders. Although the LEDs are

emulated on VGA, you can think of them as each segment

of each LED is connected to a pin on the FPGA. Driving

a pin low (to 0) lights the corresponding segment. Figure

15 shows how the segments are arranged. Thus, to display

a 1, drive the port to 01111001.

6.3 Keybounce

Like most switches, the buttons on the SoCKit are a

bunch of plastic designed to bring two pieces of metal

together. When a button is depressed, the piece of metal

shorts a wire to ground; otherwise, a resistor pulls the

wire to a 1 voltage. So a 0 means the button is

depressed and a 1 means it is not, so looking for when a

button has just been pushed should amount to looking for

a 1-to-0 transition.

Keybounce complicates this. Despite careful

mechanical design, most buttons bounce, meaning that

they quickly connect and disconnect a few times before

staying connected for a while. Thus, if you look for a 1to-0 transition to indicate a button press, you can easily

find many of them in a short time. Figure 16 illustrates the

problem.

The solution comes from noting fingers are much

slower than electronics; once a transition has occurred,

the next genuine change can only occur, say, at least

200ms later, so ignore any that come before then.

7 VHDL Simulation

For many reasons, hardware is trickier to design than

software. For example, the usual edit-compile-debug

cycle is longer because the hardware compiler has more

details to consider. Another reason is that the behavior of

hardware is harder to observe. It is difficult to put a print

statement in hardware, but not impossible: designers often

use LEDs as one-bit debugging outputs. It is even harder

to probe a wire inside a chip.

One way out of this conundrum is to simulate

Verilog before compiling it onto the FPGA. This is faster

than compilation and makes it easy to observe everything

going on inside your design, but can be thousands of

times slower than running the actual hardware.

7.1 Test benches and the Synthesizable Subset

There are actually two dialects of Verilog: the

complete language, which the simulator accepts, and the

synthesizable subsetwhat can be translated into

hardware. The non-synthesizable part of the language is

mostly useful for writing test benches.

You need two things to run an interesting simulation

of a system: a description of the system itself and some

input for it. This latter component is known as a test

bench and you need to write Verilog for your test bench

when you simulate a design. A test bench instantiates the

design you are testing, stimulates the design, e.g., by

applying clocks and inputs, and monitors its response. A

test bench can be thought of as a signal generator and

oscilloscope.

A test bench can use non-synthesizable Verilog

statements. The wait statement, which can delay a precise

amount of time, is typical. It is not possible to build

hardware that does this, although you can build something

that delays a precise number of clock cycles, but it is

easily done in simulation. For example, wait can be used

to provide a reset signal that goes low for 200 ns, in

Verilog, wait is expressed as #:

//Define a time scale for your simulation. 1ns is unit

time, //100ps is the resolution time.

`timescale 1ns/100ps

initial

begin

#10 resetn <=1b0;

#10 resetn <=1b1;

end

The final wait stops the process so it does not

automatically repeat and generate multiple resets.

Wait is also useful for modeling clocks. Here is a

way to generate a clock with a 40 ns period:

reg clk = 1b0;

always

#20 clk = !clk;

Wait can also be used to separate assignment

statements to generate specific input stimulus.

Initial

Begin

$display ($time, <<start simulation >>);

$monitor (%d, \t%b, \t%b, \t%b, \t%b, $time, a, b, cin);

#20 a <= 1b0;

b <= 1b0;

cin <= 1b0;

#20 a <= 1b1;

b <= 1b0;

cin <= 1b0;

#20 a <= 1b1;

b <= 1b0;

cin <= 1b1;

#20 $finish;

end

You can test this lab by using this style of code to

emulate buttons being pressed.

7.2 Simulating your design

Before the simulation, remember to initialize all

your input signals, otherwise the simulation result will

have errors. Quartus can run an external Verilog

simulator. We will use a version of Mentor Graphicss

ModelSim. It is a hassle to run the simulator the first time,

but it is much easier the second.

First, you probably need to tell Quartus where the

simulator is. Go to Tools -- Options, select EDA Tool

Options, double-click on the ModelSim-Altera line and

enter the name of the directory in which the vsim

executable resides. On our machines, this is /opt/

e4840/altera7.2/modelsim_ae/linuxaloem.

Now, tell Quartus that you want to use ModelSimAltera as the EDA simulator. With the project open,

select Assignments -- settings -- EDA tool settings and

click on Simulation. Set Tool name to ModelSimAltera.

The EDA tool settings dialog is also where you must

tell the simulator which testbench to use. Again under

EDA Tool Settings -- Simulation, specify a testbench in

the NativeLink settings area by selecting Compile test

bench, and clicking on Test Benches.

In the Test Benches dialog, click New to create a

new test bench. The name is arbitrary, but the module

name must match that in your Verilog test bench file and

the instance should be the name of the instance of the

design you are testing (e.g., modelsim). You must also

specify an execution time for your testbench. This may be

a number of us. Finally, add the Verilog file for your

testbench by selecting it and clicking Add. See Figure

17 & 18 which illustrates all of these settings.

Finally, you should be able to select Tools -- Run

Simulation Tool -- RTL Simulation to start ModelSim.

You need to have compiled your design before you start

the simulation.

If all goes well, you should see the ModelSim

window appear and a waveform viewer display the results

of the simulation shown in Figure 19. Use the zoom tools

to zoom in and out on this display and the scrollbars to

move. By default, the display will show all the signals

external to the unit under test (i.e., on the module in your

Verilog test bench file you specified earlier).

7.3 The RTL Viewer

We are designing a circuit but have been writing

textual Verilog. Quartus includes an RTL viewer that

displays your design as a schematic. Bring this up by

selecting Tools Netlist Viewers -- RTL Viewer (Figure

20). Note that this is informative but not necessary for

compilation.

8 What to turn in

Find an unsuspecting TA or instructor, show him/er

your working memory reader/editor, your running

simulation. Upload your working .v file on Courseworks.

Figure 1: The Altera SoCkit board

Figure 2: Assigning Pins Textually

Figure 3: Assigning Pins Graphically

Figure 4: create a new PLL file for clock frequency

Figure 5: configure the PLL output frequency

Figure 6: Adding files to a project

Figure 7: Indicating top-level entry

Figure 8: Compiling a design

Figure 9: Diagnosing errors

Figure 10: Select the Soc Series V device

Figure 11: Programming the FPGA

Figure 12: Creating a new Verilog file

Figure 13: Inserting a Verilog template

data_out

hex decode Number_Display

key(0)

key(1)

key(2)

key(3)

addr

data_in

we 168 RAM

Ctrl

clk

clk

hex decode Number_Display

hex decode Number_Display

Figure 14: The block diagram of lab 1

Figure 15: An Eight-segment LED display. (E.g., hex0 (0) is a, hex0 (7) is h.)

Figure 16: Keybounce illustrated. (a) The ideal response. (b) What actually happens.

Figure 17: Telling Quartus about a new test bench

Figure 18: Selecting ModelSim-Altera as the simulator and telling it about a testbench

Figure 19: Running ModelSim and observing simulation results

Figure 20: Viewing your design as a schematic

You might also like

- Spartan3E FPGA User GuideDocument14 pagesSpartan3E FPGA User GuideAbdelbacet_MHAMDINo ratings yet

- Vlsi Manual 2013-2014Document36 pagesVlsi Manual 2013-2014hr_suresh_kNo ratings yet

- Tu0116 Getting Started With Fpga DesignDocument23 pagesTu0116 Getting Started With Fpga DesignVinayak KumarNo ratings yet

- Tutorial 1 Introduction To VHDL, and ISE 10.1 On The Digilent Spartan-3E Starter Kit BoardDocument17 pagesTutorial 1 Introduction To VHDL, and ISE 10.1 On The Digilent Spartan-3E Starter Kit BoardpwjfjfjklfdsNo ratings yet

- A Beginner's Guide To MAX+plus II: Quick ReferenceDocument8 pagesA Beginner's Guide To MAX+plus II: Quick ReferenceHemantkumarNo ratings yet

- EC6612 - VLSI Design Laboratory ManualDocument39 pagesEC6612 - VLSI Design Laboratory ManualSriramNo ratings yet

- FPGA TutorialDocument10 pagesFPGA TutorialMaha IswaryaNo ratings yet

- Application SSC06 eDocument2 pagesApplication SSC06 eDragosFlorinLismanNo ratings yet

- Nexys2 ISE 12 - 2 Decoder TutorialDocument15 pagesNexys2 ISE 12 - 2 Decoder TutorialVale Conde CuatzoNo ratings yet

- Webfpga Docs Table of Contents Chapter 1 - Webfpga Quick Start GuidesDocument47 pagesWebfpga Docs Table of Contents Chapter 1 - Webfpga Quick Start GuidesyayaNo ratings yet

- VHDL FPGA Tutorial for BeginnersDocument12 pagesVHDL FPGA Tutorial for BeginnersArdser AvicoNo ratings yet

- Introduction To Xilinx ISE 8.2i: Digital Design LaboratoryDocument5 pagesIntroduction To Xilinx ISE 8.2i: Digital Design LaboratoryGanesh JayakumarNo ratings yet

- Lab 3Document14 pagesLab 3Kyoung-min SongNo ratings yet

- XilinxISE8.1SynthesisTutorial Spartan3EDocument17 pagesXilinxISE8.1SynthesisTutorial Spartan3ESathesh KNo ratings yet

- Learning FPGA and Verilog A Beginner's GuideDocument16 pagesLearning FPGA and Verilog A Beginner's GuideSaurabh Chandra MishraNo ratings yet

- Getting Started On The AT91SAM7X-EK PDFDocument16 pagesGetting Started On The AT91SAM7X-EK PDFJohn DerteanoNo ratings yet

- Lab - 06 - Timing Simulation & Design Implementation (Combinational Logic)Document11 pagesLab - 06 - Timing Simulation & Design Implementation (Combinational Logic)Muhammad SaudNo ratings yet

- Asic Prototyping TPDocument11 pagesAsic Prototyping TPsarin.gaganNo ratings yet

- Introduction To The Altera SOPC BuilderDocument29 pagesIntroduction To The Altera SOPC BuilderAmir PorterNo ratings yet

- Experiment 3. Digital Circuit Prototyping Using Fpgas: 1. ObjectivesDocument8 pagesExperiment 3. Digital Circuit Prototyping Using Fpgas: 1. ObjectivesSree ForuNo ratings yet

- Experiment 3. Digital Circuit Prototyping Using Fpgas: 1. ObjectivesDocument8 pagesExperiment 3. Digital Circuit Prototyping Using Fpgas: 1. ObjectivesSree ForuNo ratings yet

- Lab 1: FPGA Physical LayoutDocument9 pagesLab 1: FPGA Physical LayoutNeeraj GuptaNo ratings yet

- Fpga IntroDocument10 pagesFpga IntroJpradha KamalNo ratings yet

- RTL Simulation Lab ManualDocument78 pagesRTL Simulation Lab Manualswapna revuri100% (2)

- Xps Tutorial 21Document12 pagesXps Tutorial 21Quoc AnhNo ratings yet

- Hello WorldDocument5 pagesHello Worldsachin1985tNo ratings yet

- Spartan-6 LX9 MicroBoard Embedded Tutorial 1Document15 pagesSpartan-6 LX9 MicroBoard Embedded Tutorial 1Đinh LuậnNo ratings yet

- EECS150 Lab 2: Mapping Circuit Elements to FPGAsDocument15 pagesEECS150 Lab 2: Mapping Circuit Elements to FPGAsdarkdrone66No ratings yet

- Charles Darwin University: HIT332: Embedded and Mobile Systems Casuarina CampusDocument13 pagesCharles Darwin University: HIT332: Embedded and Mobile Systems Casuarina CampusNguyen Anh ThangNo ratings yet

- Digital Circuit DesignDocument61 pagesDigital Circuit DesignJavier CruzNo ratings yet

- A Complete Development Environment: Quick Start GuideDocument4 pagesA Complete Development Environment: Quick Start GuideSamNo ratings yet

- CSE370 Laboratory Assignment 8Document5 pagesCSE370 Laboratory Assignment 8Alexaa ANo ratings yet

- University of Technology Michatronics Branch: Wasan Shakir Mahmood 4 - Stage Supervisor: Layla HattimDocument13 pagesUniversity of Technology Michatronics Branch: Wasan Shakir Mahmood 4 - Stage Supervisor: Layla HattimWasan ShakirNo ratings yet

- Lab 3 (Verilog Implementation of Stop Light Controller)Document7 pagesLab 3 (Verilog Implementation of Stop Light Controller)Muhtasim Fuad JeetNo ratings yet

- My First FpgaDocument50 pagesMy First Fpgaelderpinator100% (1)

- A GAL Programmer For LINUX PCsDocument14 pagesA GAL Programmer For LINUX PCsluciednaNo ratings yet

- COE 758 - Xilinx ISE 13.4 Tutorial 2 ChipScope Pro OverviewDocument36 pagesCOE 758 - Xilinx ISE 13.4 Tutorial 2 ChipScope Pro Overviewudara11No ratings yet

- MMT Ethercat User GuideDocument20 pagesMMT Ethercat User Guide5397573No ratings yet

- Tinaware LaunchpadDocument11 pagesTinaware Launchpadryan cooper100% (1)

- Microblaze Vivado TutorialDocument24 pagesMicroblaze Vivado Tutorialashish jhaNo ratings yet

- System GeneratorDocument23 pagesSystem GeneratorJuan Carlos UribeNo ratings yet

- My First FpgaDocument47 pagesMy First FpgashadoNo ratings yet

- Readme PDFDocument5 pagesReadme PDFRyan Reas100% (1)

- NIOS CLI ToolsDocument22 pagesNIOS CLI ToolsSreeraj SkNo ratings yet

- Project 12springDocument5 pagesProject 12springFarzin GhotbiNo ratings yet

- EC8661 VLSI Design Lab Manual Regulation 2017 Anna University, ChennaiDocument43 pagesEC8661 VLSI Design Lab Manual Regulation 2017 Anna University, ChennaiDarwin75% (8)

- Lab 1 Spring 13Document3 pagesLab 1 Spring 13Kumaraguru RauNo ratings yet

- Lab 2 Introduction To VHDL and Nexys2Document18 pagesLab 2 Introduction To VHDL and Nexys2Timmy OcantoNo ratings yet

- How To Configure An Intel Agilex DesignDocument3 pagesHow To Configure An Intel Agilex DesignjackNo ratings yet

- DE0-Nano My First Fpga v1.0 PDFDocument47 pagesDE0-Nano My First Fpga v1.0 PDFedwin_killedlawNo ratings yet

- EE326 Lab 2Document25 pagesEE326 Lab 2krishneelNo ratings yet

- Assignment 3Document7 pagesAssignment 3مرتضی اللهی دهقیNo ratings yet

- De1-Soc Faq: De1 - Soc - Traning/de1 - Soc - Traning/lab /advanced - Demo/demo1 - AxiDocument5 pagesDe1-Soc Faq: De1 - Soc - Traning/de1 - Soc - Traning/lab /advanced - Demo/demo1 - AxiAhmed YasserNo ratings yet

- Commands of PDDocument18 pagesCommands of PDRA NDYNo ratings yet

- FPGA Lab Journal: Verilog Experiments on Comparators and AddersDocument98 pagesFPGA Lab Journal: Verilog Experiments on Comparators and AddersAFTAB ALINo ratings yet

- DSD Lab Manuals: Design and Testing Onboard Switches and Led'S in FpgaDocument4 pagesDSD Lab Manuals: Design and Testing Onboard Switches and Led'S in FpgaAL RIZWANNo ratings yet

- Embedded Systems Design with Platform FPGAs: Principles and PracticesFrom EverandEmbedded Systems Design with Platform FPGAs: Principles and PracticesRating: 5 out of 5 stars5/5 (1)

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Dreamcast Architecture: Architecture of Consoles: A Practical Analysis, #9From EverandDreamcast Architecture: Architecture of Consoles: A Practical Analysis, #9No ratings yet

- Manual ModeDocument3 pagesManual Modemicrobotica126No ratings yet

- Histogram: How To Read The HistogramDocument3 pagesHistogram: How To Read The Histogrammicrobotica126100% (2)

- Micro ControllerDocument221 pagesMicro ControllerkammoNo ratings yet

- LIAN 98 (En) - Protocol IEC 60870-5-102, Telegram StructureDocument7 pagesLIAN 98 (En) - Protocol IEC 60870-5-102, Telegram Structuremicrobotica126No ratings yet

- EZH2 Represses SLIT2 in Prostate CancerDocument11 pagesEZH2 Represses SLIT2 in Prostate Cancermicrobotica126No ratings yet

- Texas Instruments FootprintsDocument7 pagesTexas Instruments FootprintsSteve SmithNo ratings yet

- Sbaa 205Document33 pagesSbaa 205microbotica126No ratings yet

- Aperture: Shutter SpeedDocument3 pagesAperture: Shutter Speedmicrobotica126No ratings yet

- Mobicare BrochureDocument4 pagesMobicare Brochuremicrobotica126No ratings yet

- Running Linux on Xilinx XUP BoardDocument13 pagesRunning Linux on Xilinx XUP Boardmicrobotica126No ratings yet

- Snlu 105Document12 pagesSnlu 105microbotica126No ratings yet

- AD9984Document45 pagesAD9984microbotica126No ratings yet

- 00 PDFDocument20 pages00 PDFmicrobotica126No ratings yet

- Class Flyer Ali JanarbekDocument2 pagesClass Flyer Ali Janarbekmicrobotica126No ratings yet

- JESD204B Survival GuideDocument78 pagesJESD204B Survival Guidemicrobotica126No ratings yet

- NB2DSK01Document82 pagesNB2DSK01microbotica126100% (1)

- 26016Document6 pages26016microbotica126No ratings yet

- 127926Document58 pages127926microbotica126No ratings yet

- Mayer ASEE2012 Final 03182012Document11 pagesMayer ASEE2012 Final 03182012microbotica126No ratings yet

- Revisions C: 06JAN2012 01SEP2014Document2 pagesRevisions C: 06JAN2012 01SEP2014microbotica126No ratings yet

- Assmann: A-2014-2S-4-N-RDocument1 pageAssmann: A-2014-2S-4-N-Rmicrobotica126No ratings yet

- An 10365Document31 pagesAn 10365microbotica126No ratings yet

- Experimental Hardware - Playing With LED MatricesDocument2 pagesExperimental Hardware - Playing With LED Matricesmicrobotica126No ratings yet

- NRF51 Series Compatibility Matrix v2.1Document8 pagesNRF51 Series Compatibility Matrix v2.1microbotica126No ratings yet

- Project #1 Graphical Representations of Continuous and Discrete Time SignalsDocument4 pagesProject #1 Graphical Representations of Continuous and Discrete Time SignalspathmakerpkNo ratings yet

- CVMHA May2005Document3 pagesCVMHA May2005microbotica126No ratings yet

- 17 Smart CrowdfundingDocument10 pages17 Smart Crowdfundingmicrobotica126No ratings yet

- Introduction to Simulink Modeling of Dynamic SystemsDocument10 pagesIntroduction to Simulink Modeling of Dynamic SystemsCinthia FarfánNo ratings yet

- Reference of The PresentationDocument5 pagesReference of The Presentationmicrobotica126No ratings yet

- House Service Connection NEW BSR 2020-1Document1 pageHouse Service Connection NEW BSR 2020-1Deshraj BairwaNo ratings yet

- BCTG Guide-Love in The Time of CholeraDocument21 pagesBCTG Guide-Love in The Time of CholeraBernard MasiphaNo ratings yet

- EV1116 Manual 146251999-4DDocument32 pagesEV1116 Manual 146251999-4Danitha ferryNo ratings yet

- Audit Reveals Optimization Opportunities for Cement Ball Mill SystemDocument19 pagesAudit Reveals Optimization Opportunities for Cement Ball Mill SystemVijay Bhan100% (2)

- The Earls Sinful Quest - Lisa CampellDocument148 pagesThe Earls Sinful Quest - Lisa CampellEirini DiamantopoulouNo ratings yet

- Axminster CarpetDocument19 pagesAxminster Carpetrohit sinhaNo ratings yet

- Ruby and Pink Sapphire - IntroDocument3 pagesRuby and Pink Sapphire - Introrazanym100% (1)

- Steam TurbineDocument25 pagesSteam TurbineIshan JunejaNo ratings yet

- IRELAND - Rivers, Lakes and Mountains: Look at The Maps and Answer These QuestionsDocument2 pagesIRELAND - Rivers, Lakes and Mountains: Look at The Maps and Answer These QuestionsHannaNo ratings yet

- NPTEL Control Engineering Assignment 2 - SEO OptimizedDocument4 pagesNPTEL Control Engineering Assignment 2 - SEO OptimizedGanesh RadharamNo ratings yet

- Explore the Precambrian EraDocument3 pagesExplore the Precambrian EraArjay CarolinoNo ratings yet

- Micro Teaching Lesson Plan in ScienceDocument4 pagesMicro Teaching Lesson Plan in ScienceAB LoveriaNo ratings yet

- Operator Identities 2Document3 pagesOperator Identities 2jasmonNo ratings yet

- Overview of US Investment in NanotechnologyDocument19 pagesOverview of US Investment in NanotechnologyMaterials Research InstituteNo ratings yet

- Lectures On Quadratic FormsDocument170 pagesLectures On Quadratic FormsyusamengNo ratings yet

- Environmental Law Handbook ExampleDocument20 pagesEnvironmental Law Handbook ExampleThomson Reuters Australia100% (5)

- IMG - 0092 PSME Code 2012 90Document1 pageIMG - 0092 PSME Code 2012 90Bugoy2023No ratings yet

- June 2023 BillingDocument10 pagesJune 2023 BillingEsther AkpanNo ratings yet

- Me 6401 Kom - Uti Ans KeyDocument11 pagesMe 6401 Kom - Uti Ans Keylogeshboy007100% (1)

- Heidegger On Destruction - Chung ChinDocument16 pagesHeidegger On Destruction - Chung ChinAprilo DielovaNo ratings yet

- Price List Grand I10 Nios DT 01.05.2022Document1 pagePrice List Grand I10 Nios DT 01.05.2022VijayNo ratings yet

- Chapter 4: Input/Output Programming of 8051 CPUDocument7 pagesChapter 4: Input/Output Programming of 8051 CPUIsmailNo ratings yet

- Design Basis Events FOR Pressurised Heavy Water Reactor: Aerb Safety Guide No - Aerb/Sg/D-5Document36 pagesDesign Basis Events FOR Pressurised Heavy Water Reactor: Aerb Safety Guide No - Aerb/Sg/D-5Anuj DeoNo ratings yet

- Anotações - Seminários em Língua Inglesa - Discurso LiterárioDocument17 pagesAnotações - Seminários em Língua Inglesa - Discurso LiterárioAline MoraisNo ratings yet

- Electric Charge: Conservation and Quantization Conductors, Insulators, and Induced ChargesDocument21 pagesElectric Charge: Conservation and Quantization Conductors, Insulators, and Induced ChargesAcadGucciManeNo ratings yet

- Word Trek Lesson OutlinesDocument8 pagesWord Trek Lesson Outlinesapi-289048378No ratings yet

- Exercise - 8.1 NewDocument24 pagesExercise - 8.1 NewAkriti Sharma 757No ratings yet

- Table of PenaltiesDocument2 pagesTable of PenaltiesEzekiel FernandezNo ratings yet

- CSS9 TQ PT 3rd4thDocument8 pagesCSS9 TQ PT 3rd4thJevan Hope BaltazarNo ratings yet

- The Effects of Oar-Shaft Stiffness andDocument9 pagesThe Effects of Oar-Shaft Stiffness andValentina DiamanteNo ratings yet