Professional Documents

Culture Documents

Figure 2-1 8051 Block Diagram

Uploaded by

vineetya0 ratings0% found this document useful (0 votes)

21 views16 pages8051 Microcontroller block Diagram

Original Title

0130603864_pp02

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Document8051 Microcontroller block Diagram

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

21 views16 pagesFigure 2-1 8051 Block Diagram

Uploaded by

vineetya8051 Microcontroller block Diagram

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 16

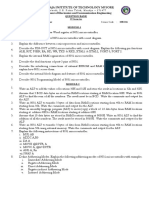

FIGURE 21

8051 block diagram

The 8051 Microcontroller, 4e

By I. Scott MacKenzie and Raphael C.-W. Phan

2007 Pearson Education, Inc.

Pearson Prentice Hall

Upper Saddle River, NJ 07458

FIGURE 22

8051 pinouts

The 8051 Microcontroller, 4e

By I. Scott MacKenzie and Raphael C.-W. Phan

2007 Pearson Education, Inc.

Pearson Prentice Hall

Upper Saddle River, NJ 07458

FIGURE 23

Driving the 8051 from a TTL oscillator

The 8051 Microcontroller, 4e

By I. Scott MacKenzie and Raphael C.-W. Phan

2007 Pearson Education, Inc.

Pearson Prentice Hall

Upper Saddle River, NJ 07458

FIGURE 24

Circuitry for I/O ports

The 8051 Microcontroller, 4e

By I. Scott MacKenzie and Raphael C.-W. Phan

2007 Pearson Education, Inc.

Pearson Prentice Hall

Upper Saddle River, NJ 07458

FIGURE 25

Relationship between oscillator clock cycles, states, and the machine cycle

The 8051 Microcontroller, 4e

By I. Scott MacKenzie and Raphael C.-W. Phan

2007 Pearson Education, Inc.

Pearson Prentice Hall

Upper Saddle River, NJ 07458

FIGURE 26

Summary of the 8031 memory spaces

The 8051 Microcontroller, 4e

By I. Scott MacKenzie and Raphael C.-W. Phan

2007 Pearson Education, Inc.

Pearson Prentice Hall

Upper Saddle River, NJ 07458

FIGURE 27

Summary of the 8051 on chip data memory

The 8051 Microcontroller, 4e

By I. Scott MacKenzie and Raphael C.-W. Phan

2007 Pearson Education, Inc.

Pearson Prentice Hall

Upper Saddle River, NJ 07458

FIGURE 28

Multiplexing the address bus (low-byte) and data bus

The 8051 Microcontroller, 4e

By I. Scott MacKenzie and Raphael C.-W. Phan

2007 Pearson Education, Inc.

Pearson Prentice Hall

Upper Saddle River, NJ 07458

FIGURE 29

Accessing external code memory

The 8051 Microcontroller, 4e

By I. Scott MacKenzie and Raphael C.-W. Phan

2007 Pearson Education, Inc.

Pearson Prentice Hall

Upper Saddle River, NJ 07458

FIGURE 210

Read timing for external code memory

The 8051 Microcontroller, 4e

By I. Scott MacKenzie and Raphael C.-W. Phan

2007 Pearson Education, Inc.

Pearson Prentice Hall

Upper Saddle River, NJ 07458

FIGURE 211

Timing for MOVX instruction

The 8051 Microcontroller, 4e

By I. Scott MacKenzie and Raphael C.-W. Phan

2007 Pearson Education, Inc.

Pearson Prentice Hall

Upper Saddle River, NJ 07458

FIGURE 212

Interface to 1K RAM

The 8051 Microcontroller, 4e

By I. Scott MacKenzie and Raphael C.-W. Phan

2007 Pearson Education, Inc.

Pearson Prentice Hall

Upper Saddle River, NJ 07458

FIGURE 213

Address decoding

The 8051 Microcontroller, 4e

By I. Scott MacKenzie and Raphael C.-W. Phan

2007 Pearson Education, Inc.

Pearson Prentice Hall

Upper Saddle River, NJ 07458

FIGURE 214

Overlapping the external code and data spaces

The 8051 Microcontroller, 4e

By I. Scott MacKenzie and Raphael C.-W. Phan

2007 Pearson Education, Inc.

Pearson Prentice Hall

Upper Saddle River, NJ 07458

FIGURE 215

8032/52 memory spaces

The 8051 Microcontroller, 4e

By I. Scott MacKenzie and Raphael C.-W. Phan

2007 Pearson Education, Inc.

Pearson Prentice Hall

Upper Saddle River, NJ 07458

FIGURE 216

Two circuits for system reset. (a) Manual reset (b) Power-on reset.

The 8051 Microcontroller, 4e

By I. Scott MacKenzie and Raphael C.-W. Phan

2007 Pearson Education, Inc.

Pearson Prentice Hall

Upper Saddle River, NJ 07458

You might also like

- 2009MCS Chapter 4Document33 pages2009MCS Chapter 4林庭宇No ratings yet

- Figure 10-1 FSK TransmitterDocument38 pagesFigure 10-1 FSK TransmitterJose Torres NuñezNo ratings yet

- Tos Epas G-11Document2 pagesTos Epas G-11Paul Senen Didulo100% (1)

- Chapter4 p1Document23 pagesChapter4 p1Mauro Onoro100% (1)

- 2009MCS Chapter 9Document43 pages2009MCS Chapter 9林庭宇No ratings yet

- Vivekananda Institute of Technology: ECE DepartmentDocument6 pagesVivekananda Institute of Technology: ECE DepartmentRam Mohan Rao MakineniNo ratings yet

- 18EC46 Question BankDocument1 page18EC46 Question Bankdinesh M.A.No ratings yet

- CH05Document38 pagesCH05Geoffrey AlleyneNo ratings yet

- Wbut Lab Exam ScheduleDocument7 pagesWbut Lab Exam ScheduleSurya MukherjeeNo ratings yet

- Indus Institute of Technology and Engineering: Class: Vi Sem (Electrical and Electronics Engg.)Document2 pagesIndus Institute of Technology and Engineering: Class: Vi Sem (Electrical and Electronics Engg.)sanchit9590No ratings yet

- 1 CH14 - IC TechnologiesDocument20 pages1 CH14 - IC Technologiesdaovanthanh_bk2007No ratings yet

- Miroprocessor and Microcontroller LaboratoryDocument130 pagesMiroprocessor and Microcontroller LaboratoryTrending TechnicsNo ratings yet

- Course Detail Format - LICDocument48 pagesCourse Detail Format - LICSamadhan ThokalNo ratings yet

- FIGURE 8-1A (A) 500-Type Telephone Set (B) 2500-Type Telephone SetDocument19 pagesFIGURE 8-1A (A) 500-Type Telephone Set (B) 2500-Type Telephone SetBhagwan DasNo ratings yet

- Testing 8051 I/O Ports LabDocument3 pagesTesting 8051 I/O Ports Lababdul.azeezNo ratings yet

- Understanding Relay Circuits and ApplicationsDocument13 pagesUnderstanding Relay Circuits and ApplicationsMartin John RamirezNo ratings yet

- Ece Syllabus s7 Kannur UniversityDocument30 pagesEce Syllabus s7 Kannur UniversitygokulnrnnkNo ratings yet

- Study of Binary Phase Shift KeyingDocument5 pagesStudy of Binary Phase Shift KeyingShivachandran NadarNo ratings yet

- Philippine electrical code 2009 downloadDocument3 pagesPhilippine electrical code 2009 downloadMark Mesa0% (2)

- Year/Sem:Iii / V Subject: Ec 1304 - Microprocessors and Microcontroller LabDocument26 pagesYear/Sem:Iii / V Subject: Ec 1304 - Microprocessors and Microcontroller LabD Geetha DuraiNo ratings yet

- 8051 Timer and Serial Interrupt Programming LabDocument2 pages8051 Timer and Serial Interrupt Programming LabM Rameez Ur RehmanNo ratings yet

- 8051 (Volume-1)Document322 pages8051 (Volume-1)Muhammad Rizwan Haider DurraniNo ratings yet

- Microcontroller Lab_RB_For CirculationDocument36 pagesMicrocontroller Lab_RB_For Circulationpanave3104No ratings yet

- Microcontroller Lab_RB_For Circulation (1)Document36 pagesMicrocontroller Lab_RB_For Circulation (1)panave3104No ratings yet

- Ee16408 Mca Vith SemDocument5 pagesEe16408 Mca Vith SemharshalNo ratings yet

- Ee8681-Microprocessor and Microcontroller Laboratory-1667857924-Ee8681 Lab Manual-NewDocument107 pagesEe8681-Microprocessor and Microcontroller Laboratory-1667857924-Ee8681 Lab Manual-NewDHEENADHAYALAN KETTAVANNo ratings yet

- MPI Lab ManualDocument49 pagesMPI Lab ManualRutvik JaimalaniNo ratings yet

- EEE Miroprocessor and Microcontroller LaboratoryDocument122 pagesEEE Miroprocessor and Microcontroller Laboratorykbmn2No ratings yet

- DC Biasing-Bjts: Dr. Talal SkaikDocument23 pagesDC Biasing-Bjts: Dr. Talal Skaikrafi absarNo ratings yet

- Electrcial Circuits Lab Manual 2-1Document79 pagesElectrcial Circuits Lab Manual 2-1اياد النعيميNo ratings yet

- 8051-Based Timer and Stopwatch Project ReportDocument15 pages8051-Based Timer and Stopwatch Project ReportJoel RachamudiNo ratings yet

- Edited Interfacing and Code ConversionDocument10 pagesEdited Interfacing and Code ConversionkesavantNo ratings yet

- Solar TrackerDocument57 pagesSolar TrackerRustum Prasad Sahu100% (4)

- 8051 Trainer DAC Sine Wave GenerationDocument3 pages8051 Trainer DAC Sine Wave GenerationshubhNo ratings yet

- Departmental Library List of Books in EC Department: Institute of Engineering and Technology, LucknowDocument43 pagesDepartmental Library List of Books in EC Department: Institute of Engineering and Technology, LucknowLakkimsetti jahnaviNo ratings yet

- RF344 EVDO RF OptimizationDocument49 pagesRF344 EVDO RF OptimizationAnonymous Pd5Lf8No ratings yet

- Third Year ECE Evaluation Scheme and Syllabus With COs PDFDocument28 pagesThird Year ECE Evaluation Scheme and Syllabus With COs PDFAnonymous eWMnRr70qNo ratings yet

- Fig. 7.1 Fixed-Bias Configuration.: Electronic Devices and Circuit Theory, 9eDocument103 pagesFig. 7.1 Fixed-Bias Configuration.: Electronic Devices and Circuit Theory, 9eNihala KhalidNo ratings yet

- 8051 Hardware TutorialsDocument24 pages8051 Hardware TutorialsHerleneNo ratings yet

- Bifurcation of The Marks of ELTR-114, E LTR-225, ELTRDocument1 pageBifurcation of The Marks of ELTR-114, E LTR-225, ELTRImran ShaukatNo ratings yet

- Change Faculty Assignments Quickly with LMSDocument2 pagesChange Faculty Assignments Quickly with LMSNishant SaxenaNo ratings yet

- MIC College of Technology: The Switch Mac Address TableDocument25 pagesMIC College of Technology: The Switch Mac Address TableVijay Kanth ThokalaNo ratings yet

- Resume of EtechstanDocument2 pagesResume of Etechstanapi-23825444No ratings yet

- Proposed Syllabus for Computer Science and EngineeringDocument44 pagesProposed Syllabus for Computer Science and EngineeringRaj RaiNo ratings yet

- Pune Vidyarthi Griha 'S College of Engineering and Technology, Pune-9Document51 pagesPune Vidyarthi Griha 'S College of Engineering and Technology, Pune-9Vaishnovi BNo ratings yet

- SCHEME - E Fourth Semester - ED, EI, EJ, EN, ET, EXDocument40 pagesSCHEME - E Fourth Semester - ED, EI, EJ, EN, ET, EXMrunal Tambe0% (1)

- Government Polytechnic Pune-16: (An Autonomous Institute of Govt. of Maharashtra)Document38 pagesGovernment Polytechnic Pune-16: (An Autonomous Institute of Govt. of Maharashtra)Somesh KumbharNo ratings yet

- Basic Analog Circuits PDFDocument39 pagesBasic Analog Circuits PDFManish KumarNo ratings yet

- BOS approved changes to B.Voc ELE, B.Voc RET and M.Voc curriculumDocument8 pagesBOS approved changes to B.Voc ELE, B.Voc RET and M.Voc curriculumYatendra Singh HadaNo ratings yet

- Rehman Zaman Updated CVDocument5 pagesRehman Zaman Updated CVRehman ZamanNo ratings yet

- 8051 MicrocontrollerDocument23 pages8051 Microcontrollerblackhorse.nerdNo ratings yet

- Maadhav IT Front PaperDocument97 pagesMaadhav IT Front PaperSRL MECHNo ratings yet

- Shree Ramchandra College of Engineering, LONIKAND, PUNE - 412 216Document1 pageShree Ramchandra College of Engineering, LONIKAND, PUNE - 412 216HarshvardhanUpadhyayNo ratings yet

- Seminar Report OnDocument5 pagesSeminar Report OnPratik BhoyarNo ratings yet

- MC Lab Manual-2024Document77 pagesMC Lab Manual-2024Mrnotorious24No ratings yet

- Refurbish Antique Telephones for Fun and Hobby: Step by Step Instructions to Take an Old Telephone and Return It to Its Original Working Order. No Electronics or Telephone Knowledge Needed.From EverandRefurbish Antique Telephones for Fun and Hobby: Step by Step Instructions to Take an Old Telephone and Return It to Its Original Working Order. No Electronics or Telephone Knowledge Needed.No ratings yet

- Photonics, Volume 4: Biomedical Photonics, Spectroscopy, and MicroscopyFrom EverandPhotonics, Volume 4: Biomedical Photonics, Spectroscopy, and MicroscopyNo ratings yet

- Machine Learning Workflow EbookDocument22 pagesMachine Learning Workflow EbookNguyen Thi Hoang GiangNo ratings yet

- Getting Started in KicadDocument52 pagesGetting Started in Kicadsilviutudose2003No ratings yet

- Atmel 42439 From Maker To Manufacture Bridging The Gap From Arduino To AVR TrainingManualDocument48 pagesAtmel 42439 From Maker To Manufacture Bridging The Gap From Arduino To AVR TrainingManualvineetyaNo ratings yet

- Washington PostDocument1 pageWashington PostvineetyaNo ratings yet

- Linux Cheatsheet BWDocument8 pagesLinux Cheatsheet BWJoshQuintonNo ratings yet

- A Brief History of MathematicsDocument362 pagesA Brief History of Mathematicsxanabras100% (30)

- MathType Training HandoutDocument24 pagesMathType Training HandoutvineetyaNo ratings yet

- Linux Cheatsheet BWDocument8 pagesLinux Cheatsheet BWJoshQuintonNo ratings yet

- 359 Mathews PDFDocument25 pages359 Mathews PDFvineetyaNo ratings yet

- ATmega328 P PDFDocument442 pagesATmega328 P PDFsreehariNo ratings yet

- Global Trends 2030: Alternative WorldsDocument160 pagesGlobal Trends 2030: Alternative WorldsOffice of the Director of National Intelligence97% (29)

- Engineering - An Introduction For High SchoolDocument170 pagesEngineering - An Introduction For High SchoolvineetyaNo ratings yet

- Project Types: Executive SummaryDocument4 pagesProject Types: Executive SummaryvineetyaNo ratings yet

- Monitoring CMTP Rom enDocument4 pagesMonitoring CMTP Rom envineetyaNo ratings yet

- NIIT Career ProgramDocument2 pagesNIIT Career Programvineetya100% (1)

- Web BrowserDocument3 pagesWeb Browserapi-3736604No ratings yet

- 6th Central Pay Commission Salary CalculatorDocument15 pages6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- Main Projects in Telecom Technologies For Engineering Students For The Year 2010-11Document29 pagesMain Projects in Telecom Technologies For Engineering Students For The Year 2010-11vineetyaNo ratings yet

- Futuring: Bruce Laduke, Futurist, Indianapolis, inDocument13 pagesFuturing: Bruce Laduke, Futurist, Indianapolis, invineetyaNo ratings yet

- Futuring: Bruce Laduke, Futurist, Indianapolis, inDocument13 pagesFuturing: Bruce Laduke, Futurist, Indianapolis, invineetyaNo ratings yet

- Blueprints For A Successful PresentationDocument117 pagesBlueprints For A Successful PresentationJan AbidNo ratings yet

- Evolution & Human BehavioralDocument396 pagesEvolution & Human Behavioralvineetya90% (20)

- Blender Quick StartDocument1 pageBlender Quick StartgNessOpzNo ratings yet

- Brain Structure & FunctionDocument24 pagesBrain Structure & Functionvineetya100% (4)

- C++ in 7 DaysDocument50 pagesC++ in 7 DaysKaran SharmaNo ratings yet

- AcroyrmnsDocument4 pagesAcroyrmnsvineetyaNo ratings yet

- Comprehen With Answers PDFDocument242 pagesComprehen With Answers PDFAkshit Mathur0% (1)

- CL-29M40MQ K16aDocument65 pagesCL-29M40MQ K16aalejandro010306No ratings yet

- Tea19161t NXPDocument46 pagesTea19161t NXPVICTOR MANUENo ratings yet

- L060 Push Pull (2UP)Document10 pagesL060 Push Pull (2UP)srikanthkmsNo ratings yet

- Holiday Testing ProcedureDocument4 pagesHoliday Testing Proceduremadhurajsh100% (1)

- Shri Guru Ram Rai Public SchoolDocument20 pagesShri Guru Ram Rai Public SchoolSanaNo ratings yet

- ELE232 - Chapter 1 - Semiconductor - Compatibility Mode - 4Document8 pagesELE232 - Chapter 1 - Semiconductor - Compatibility Mode - 4Abrar HamdiNo ratings yet

- Description: Technical DataDocument17 pagesDescription: Technical DataDhivya NNo ratings yet

- 4 Ways To Test A Transistor - WikiHowDocument12 pages4 Ways To Test A Transistor - WikiHowH ChanakyaNo ratings yet

- 2 - History of ComputersDocument9 pages2 - History of ComputersMaan CabolesNo ratings yet

- Solar Charge ControllerDocument2 pagesSolar Charge ControllerBrahmpal BhardwajNo ratings yet

- Service Manual Zenith Eee Sms2049 TVDocument9 pagesService Manual Zenith Eee Sms2049 TVDeyby GarciaNo ratings yet

- Audio Spectrum AnalyzerDocument6 pagesAudio Spectrum AnalyzerPravin MevadaNo ratings yet

- Lecture 3 - Solar Cell Technology - Overview I: Alan P. MorrisonDocument22 pagesLecture 3 - Solar Cell Technology - Overview I: Alan P. MorrisonastiChantillyNo ratings yet

- I C BUS EEPROM (2-Wire) : DatasheetDocument39 pagesI C BUS EEPROM (2-Wire) : Datasheetmarcio carvalhoNo ratings yet

- Transformer Coupled AmplifierDocument6 pagesTransformer Coupled AmplifierXyrex CalangNo ratings yet

- En Acs800-607 HW CDocument82 pagesEn Acs800-607 HW CjakkyjeryNo ratings yet

- Xtronic Org Circuit Amplifier Audio Amplifier Potency Tda729Document10 pagesXtronic Org Circuit Amplifier Audio Amplifier Potency Tda729ANTONIO PEREZNo ratings yet

- Ada 304031Document334 pagesAda 304031Amit DostNo ratings yet

- HSPICE Tutorial PDFDocument7 pagesHSPICE Tutorial PDFXman-exNo ratings yet

- HOOSEKI Campur 1Document12 pagesHOOSEKI Campur 1Anugrah Prihantoro Amd T100% (3)

- CHAPTER VII Direct Current Circuits NEWDocument20 pagesCHAPTER VII Direct Current Circuits NEWVydia Ridha AriatiNo ratings yet

- Report For A Power Supply With A Rated Output of 9.9V /1aDocument8 pagesReport For A Power Supply With A Rated Output of 9.9V /1aSend noobsNo ratings yet

- Open Elective BTech 2nd Yr 2023 24 v2Document19 pagesOpen Elective BTech 2nd Yr 2023 24 v2bhaivarun65No ratings yet

- Combiflex 1MRK 513 003 BENDocument28 pagesCombiflex 1MRK 513 003 BENRanjit RjtNo ratings yet

- DMC tz57 PDFDocument51 pagesDMC tz57 PDFRavi Chandran100% (1)

- CTAB Modification of MCM-49 Zeolite Containing HMI and Its Acylation of AnisoleDocument11 pagesCTAB Modification of MCM-49 Zeolite Containing HMI and Its Acylation of AnisoleFarida Nur AzizaNo ratings yet

- Line Follower RobotDocument16 pagesLine Follower RobotAmit KumarNo ratings yet

- GRZ100D 6F2S0851 0.8rDocument462 pagesGRZ100D 6F2S0851 0.8rTiffany BeachNo ratings yet

- Resistance Bridge Circuit AnalysisDocument7 pagesResistance Bridge Circuit AnalysisRon NecesitoNo ratings yet