Professional Documents

Culture Documents

Par PDF

Uploaded by

Jithin SOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Par PDF

Uploaded by

Jithin SCopyright:

Available Formats

Introduction

Objectives

Vedic Multiplier

Compressors

Parallel MAC unit

Future plans

Parallel Multiplier - Accumulator Based on

Vedic Mathematics

Presented by : Jithin.s (cb.en.p2vld13013)

Guided by : Mr.E.Prabhu

Amrita Viswa Vidhyapeetham

08-December-2014

1/15

Parallel Multiplier - Accumulator Based on Vedic Mathematics

Introduction

Objectives

Vedic Multiplier

Compressors

Parallel MAC unit

Future plans

Overview

1 Introduction

2

Objectives

3 Vedic Multiplier

RTL Schematic

4 Compressors

Higher Order Compressor

RTL 4:2 Compressor

Architecture

5 Parallel MAC unit

6 Future plans

s

2/15

Parallel Multiplier - Accumulator Based on Vedic Mathematics

Introduction

Objectives

Vedic Multiplier

Compressors

Parallel MAC unit

Future plans

Introduction

In Vedic mathematics multiplier is designed by using Urdhwa

Tiryakbyam.

Urdhwa Tiryakbyam is the simplest and fastest multiplication

algorithm.

Compared to modified booth multiplier algorithm Vedic

multiplier has less power dissipation and high speed operation.

By replacing modified booth with Vedic multiplier in MAC

unit performance can be improved.

2/15

Parallel Multiplier - Accumulator Based on Vedic Mathematics

Introduction

Objectives

Vedic Multiplier

Compressors

Parallel MAC unit

Future plans

Objectives

Design of Urdhwa Tiryakbyam based multiplier.

To Optimize Vedic multiplier by using compressors.

To implement parallel MAC unit by using compressor based

Vedic multipliers.

Compare the delay parameter of existing MBA based parallel

MAC with proposed architecture.

3/15

Parallel Multiplier - Accumulator Based on Vedic Mathematics

Introduction

Objectives

Vedic Multiplier

Compressors

Parallel MAC unit

Future plans

Vedic Multiplier

Vedic partial product addition stage contains number of full

adders and half adders .

Parallel Multiplier - Accumulator Based on Vedic Mathematics

4/15

Introduction

Objectives

Vedic Multiplier

Compressors

Parallel MAC unit

Future plans

RTL Schematic

RTL Schematic

Vedic multiplier

4 Bit

8 Bit

Area(um)

593.1

3026.8

Delay(ns)

1.97

3.82

5/15

Parallel Multiplier - Accumulator Based on Vedic Mathematics

Introduction

Objectives

Vedic Multiplier

Compressors

Parallel MAC unit

Future plans

Compressors

(a) Normal addition

(b) 4:2 compressor

20 percent improvement of speed.

Parallel Multiplier - Accumulator Based on Vedic Mathematics

6/15

Introduction

Objectives

Vedic Multiplier

Compressors

Parallel MAC unit

Future plans

Higher Order Compressor

Higher Order Compressor

By using 4:2 compressor : 7 XOR gate delay

By using Normal 5 bit adder : 9 XOR gate delay

Parallel Multiplier - Accumulator Based on Vedic Mathematics

7/15

Introduction

Objectives

Vedic Multiplier

Compressors

Parallel MAC unit

Future plans

RTL 4:2 Compressor

RTL 4:2 Compressor

(a) RTL Schematic 4:2

Compressor

4:2

7:2

Area(um)

73.3

251

(b) RTL Schematic 7:2

Delay(ns)

Addition

.

.52

5 Bit

.93

10 Bit

Area

81.2

267

Delay

.7

1.17

8/15

Parallel Multiplier - Accumulator Based on Vedic Mathematics

Introduction

Objectives

Vedic Multiplier

Compressors

Parallel MAC unit

Future plans

Architecture

Compressor based Vedic Multiplier

Vedic Mul.

4 Bit

Area(um)

593.1

Delay(ns)

Compressor

.

1.97

4 Bit

Area

585

Delay

1.77

9/15

Parallel Multiplier - Accumulator Based on Vedic Mathematics

Introduction

Objectives

Vedic Multiplier

Compressors

Parallel MAC unit

Future plans

Parallel MAC unit

* Booth encoder

* good timing * decrease delay

10/15

Parallel Multiplier - Accumulator Based on Vedic Mathematics

Introduction

Objectives

Vedic Multiplier

Compressors

Parallel MAC unit

Future plans

Vedic partial product addition

(b) Partial product addition

(a) Vedic encoder

11/15

Parallel Multiplier - Accumulator Based on Vedic Mathematics

Introduction

Objectives

Vedic Multiplier

Compressors

Parallel MAC unit

Future plans

Vedic encoder

(b) Partial product addition

(a) Vedic encoder

Booth encoder Delay

Partial product addition

.47ns

Vedic encoder Delay

.

1.13ns

Partial product addition

Parallel Multiplier - Accumulator Based on Vedic Mathematics

.17ns

1.07ns

12/15

Introduction

Objectives

Vedic Multiplier

Compressors

Parallel MAC unit

Future plans

Final delay comparison

100 numbers multiplication

(Vedic encoder delay + partial product addition delay )x100

(1.06+.17)x100 = 123ns

(Booth encoder delay + partial product delay )x100

(1.13 + .47)x100 = 160ns

Improvement in speed about 25 percent in proposed MAC unit.

13/15

Parallel Multiplier - Accumulator Based on Vedic Mathematics

Introduction

Objectives

Vedic Multiplier

Compressors

Parallel MAC unit

Future plans

Future plans

Design of ALU by using the proposed MAC unit and Nikhilam

Sutra based squarer circuit.

Transistor level power optimization of MAC unit by using

Gate-diffusion input (GDI) technique.

Higher order bits MAC unit development and its FPGA

implementation.

14/15

Parallel Multiplier - Accumulator Based on Vedic Mathematics

Introduction

Objectives

Vedic Multiplier

Compressors

Parallel MAC unit

Future plans

References

Young-Ho Seo, Member, IEEE, and Dong-Wook Kim, Member, IEEE, A

New VLSI Architecture of Parallel MultiplierAccumulator Based on

Radix-2 Modified Booth Algorithm, IEEE Transactions on very large scale

integration(VLSI) systems, Vol 18, No.2 February 2010.

Tiwari, Honey Durga, Ganzorig Gankhuyag, Chan Mo Kim, and Yong

Beom Cho.Multiplier design based on ancient Indian Vedic

Mathematics. In SoC Design Conference, 2008. ISOCC08.

International, vol. 2, pp. II-65. IEEE, 2008.

Sushma R. Huddar ,Sudhir Rao Rupanagudi, Kalpana M and Surabhi

Mohan,Novel High Speed Vedic Mathematics Multiplier using

Compressors. 2013 IEEE.

Devika Jaina, Kabiraj Sethi and Rutuparna Panda, Vedic Mathematics

Based Multiply Accumulate Unit .2011 International Conference on

Computational Intelligence and Communication Systems.

15/15

Parallel Multiplier - Accumulator Based on Vedic Mathematics

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Soalan Peperiksaan Matematik Tingkatan 1 Kertas 2 - (SKEMA JAWAPAN)Document8 pagesSoalan Peperiksaan Matematik Tingkatan 1 Kertas 2 - (SKEMA JAWAPAN)syukrie353% (15)

- Lesson Plan 1 - Division of Polynomials by Another PolynomialDocument3 pagesLesson Plan 1 - Division of Polynomials by Another PolynomialTheKnow04100% (3)

- MUM QuestionsDocument91 pagesMUM Questionsle dang thu ha100% (3)

- Aditya l1Document1 pageAditya l1Jithin SNo ratings yet

- VT STD CellsDocument40 pagesVT STD CellsJithin SNo ratings yet

- Medical FeesDocument3 pagesMedical FeesJithin SNo ratings yet

- InductanceDocument5 pagesInductanceJithin SNo ratings yet

- Ch3 PowerBasicsDocument46 pagesCh3 PowerBasicsJithin SNo ratings yet

- Sill LowPower2Document67 pagesSill LowPower2Jithin SNo ratings yet

- Par PDFDocument16 pagesPar PDFJithin SNo ratings yet

- Readme CardReaderDocument1 pageReadme CardReaderJithin SNo ratings yet

- Cmos Pool CircuitDocument26 pagesCmos Pool CircuitJithin SNo ratings yet

- Design Planning Strategies To Improve Physical Design Flows - Floorplanning and Power PlanningDocument11 pagesDesign Planning Strategies To Improve Physical Design Flows - Floorplanning and Power PlanningMohammed DarouicheNo ratings yet

- How To Become FatDocument1 pageHow To Become FatJithin SNo ratings yet

- MATH Q2 Lesson 32 Improper FractionDocument32 pagesMATH Q2 Lesson 32 Improper FractionJasmin Cabral100% (1)

- G7.M4.v3 Teacher EditionDocument297 pagesG7.M4.v3 Teacher EditionDox Alt100% (1)

- Operations With DecimalsDocument2 pagesOperations With DecimalsMathnasium of BentonvilleNo ratings yet

- Com - Res - 9661 Peitition For Accreditation For Political PartyDocument11 pagesCom - Res - 9661 Peitition For Accreditation For Political PartyAzceril AustriaNo ratings yet

- BI2001B - Diseño de Sistemas de Bioinstrumentación Digital: Sistemas Numéricos y CodigosDocument43 pagesBI2001B - Diseño de Sistemas de Bioinstrumentación Digital: Sistemas Numéricos y CodigosHéctor Vega SantamaríaNo ratings yet

- Factoring PracticeDocument6 pagesFactoring PracticeJeanalmiraNo ratings yet

- RD Sharma Solution Class 9 Maths Chapter 1 Number System PDFDocument25 pagesRD Sharma Solution Class 9 Maths Chapter 1 Number System PDFSaravanan MariNo ratings yet

- Math 7 Rieviewer - 1st - QuarterlyDocument11 pagesMath 7 Rieviewer - 1st - QuarterlyClarice PalattaoNo ratings yet

- Long Quiz g10Document2 pagesLong Quiz g10DanecaNo ratings yet

- 7th Grade UnpackedDocument45 pages7th Grade Unpackedapi-263084168No ratings yet

- PROGress Exam - Math4Document1 pagePROGress Exam - Math4Raymund BondeNo ratings yet

- Basics of Python Programming7Document32 pagesBasics of Python Programming7Anjum AkhtharNo ratings yet

- 7th Grade - Activity 15 - Power, Root and LogarithmsDocument4 pages7th Grade - Activity 15 - Power, Root and LogarithmsJuan D. CapadorNo ratings yet

- AB-Assignments: Object Oriented Programming (C++) Air UniversityDocument2 pagesAB-Assignments: Object Oriented Programming (C++) Air UniversityAli AhmadNo ratings yet

- Ge4 (4912) - Practice Set2 - Set A, B, C, D, E,&fDocument3 pagesGe4 (4912) - Practice Set2 - Set A, B, C, D, E,&fCrystal Mae LayeseNo ratings yet

- Expressions in JavaDocument23 pagesExpressions in JavaBrijesh JoshiNo ratings yet

- G8DLL Q1W4 Lc05aDocument13 pagesG8DLL Q1W4 Lc05aLADY ANN GRACE LAGASNo ratings yet

- Operations of Rational NumbersDocument3 pagesOperations of Rational Numbersapi-174391216No ratings yet

- Conversion QuizDocument7 pagesConversion QuizNoel IV T. BorromeoNo ratings yet

- MCQ Test On Unit 5.1 - Attempt ReviewDocument3 pagesMCQ Test On Unit 5.1 - Attempt ReviewDemo Account 1No ratings yet

- Budget of Work Math 5Document2 pagesBudget of Work Math 5Rodel AgcaoiliNo ratings yet

- DDA AlgorithmDocument5 pagesDDA AlgorithmNeha KiradNo ratings yet

- EncodersDocument8 pagesEncoderssuresh mariappanNo ratings yet

- Math Made A Bit Easier Workbook: Practice Exercises, Self-Tests, and ReviewDocument144 pagesMath Made A Bit Easier Workbook: Practice Exercises, Self-Tests, and ReviewLarry Zafran100% (3)

- Y6 Merged Maths 010620 4Document16 pagesY6 Merged Maths 010620 4Marko ZderoNo ratings yet

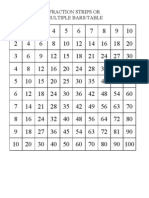

- Fraction StripsDocument5 pagesFraction StripsMohamad Aiyad RamliNo ratings yet

- Scratch2 - Step by Step - A Course in Scratch ProgrammingDocument54 pagesScratch2 - Step by Step - A Course in Scratch Programmingapi-287679928No ratings yet