Professional Documents

Culture Documents

Multiplying Two Numbers in Memory

Uploaded by

krish0 ratings0% found this document useful (0 votes)

17 views2 pagesCISC Vs RISC

Original Title

CISCnRISC

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCISC Vs RISC

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

17 views2 pagesMultiplying Two Numbers in Memory

Uploaded by

krishCISC Vs RISC

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

You are on page 1of 2

The simplest way to examine the advantages and disadvantages of RISC architecture is

by contrasting it with it's predecessor: CISC (Complex Instruction Set Computers)

architecture.

Multiplying Two Numbers in Memory

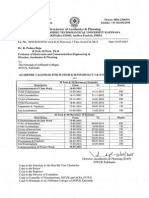

On the right is a diagram representing the storage scheme for a generic computer. The

main memory is divided into locations numbered from (row) 1: (column) 1 to (row) 6:

(column) 4. The execution unit is responsible for carrying out all computations. However,

the execution unit can only operate on data that has been loaded into one of the six

registers (A, B, C, D, E, or F). Let's say we want to find the product of two numbers - one

stored in location 2:3 and another stored in location 5:2 - and then store the product

back in the location 2:3.

The CISC Approach

The primary goal of CISC architecture is to

complete a task in as few lines of assembly as

possible. This is achieved by building processor

hardware that is capable of understanding and

executing a series of operations. For this

particular task, a CISC processor would come

prepared with a specific instruction (we'll call it

"MULT"). When executed, this instruction loads

the two values into separate registers,

multiplies the operands in the execution unit,

and then stores the product in the appropriate

register. Thus, the entire task of multiplying two

numbers can be completed with one

instruction:

MULT 2:3, 5:2

MULT is what is known as a "complex

instruction." It operates directly on the

computer's memory banks and does not require

the programmer to explicitly call any loading or storing functions. It closely resembles a

command in a higher level language. For instance, if we let "a" represent the value of 2:3

and "b" represent the value of 5:2, then this command is identical to the C statement "a

= a * b."

One of the primary advantages of this system is that the compiler has to do very little

work to translate a high-level language statement into assembly. Because the length of

the code is relatively short, very little RAM is required to store instructions. The emphasis

is put on building complex instructions directly into the hardware.

The RISC Approach

RISC processors only use simple instructions that can be executed within one clock cycle.

CISC

RISC

Emphasis on hardware

Emphasis on software

Includes multi-clock

Single-clock,

complex instructions

reduced instruction only

Memory-to-memory:

Register to register:

"LOAD" and "STORE"

"LOAD" and "STORE"

incorporated in instructions

are independent instructions

Small code sizes,

Low cycles per second,

high cycles per second

large code sizes

Transistors used for storing

Spends more transistors

complex instructions

on memory registers

what is risc? mips pipelining recent developments bibliography about this site

You might also like

- The Smith Generator BlueprintsDocument36 pagesThe Smith Generator BlueprintsZoran AleksicNo ratings yet

- Computer Architecture Question PaperDocument14 pagesComputer Architecture Question Paperheaughfrds100% (1)

- RISC Vs CISCDocument13 pagesRISC Vs CISCBehin SamNo ratings yet

- Risc VDocument5 pagesRisc VOlhaNo ratings yet

- RISC Vs CISC, Harvard V/s Van NeumannDocument35 pagesRISC Vs CISC, Harvard V/s Van NeumannVRAJ PATELNo ratings yet

- Design of A RISC Microcontroller Core in 48 HoursDocument11 pagesDesign of A RISC Microcontroller Core in 48 HoursPulkit TrivediNo ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Ansible Playbook for BeginnersDocument101 pagesAnsible Playbook for BeginnersFelix Andres Baquero Cubillos100% (1)

- Introduction To CortexM3Document15 pagesIntroduction To CortexM3krishNo ratings yet

- Audi Q5: First Generation (Typ 8R 2008-2017)Document19 pagesAudi Q5: First Generation (Typ 8R 2008-2017)roberto100% (1)

- Desana Texts and ContextsDocument601 pagesDesana Texts and ContextsdavidizanagiNo ratings yet

- Cisc Vs Risc: Multiplying Two Numbers in MemoryDocument4 pagesCisc Vs Risc: Multiplying Two Numbers in MemoryItz Sami UddinNo ratings yet

- Multiplying Two Numbers in MemoryDocument3 pagesMultiplying Two Numbers in MemoryVinita Pandey100% (1)

- RISC vs CISC: Examining the Advantages of Reduced Instruction Set ArchitecturesDocument3 pagesRISC vs CISC: Examining the Advantages of Reduced Instruction Set Architecturesvivek2585No ratings yet

- Risc Vs Cisc: Multiplying Two Numbers in MemoryDocument4 pagesRisc Vs Cisc: Multiplying Two Numbers in MemoryFiq WaggNo ratings yet

- Cisc Vs RiscDocument3 pagesCisc Vs RiscGeorgiana DanilaNo ratings yet

- The Simplest Way To Examine The Advantages and Disadvantages of RISC Architecture Is by Contrasting It With ItDocument4 pagesThe Simplest Way To Examine The Advantages and Disadvantages of RISC Architecture Is by Contrasting It With ItMushawatuNo ratings yet

- The Simplest Way To Examine The Advantages and Disadvantages of RISC Architecture Is by Contrasting It With ItDocument11 pagesThe Simplest Way To Examine The Advantages and Disadvantages of RISC Architecture Is by Contrasting It With ItsaadawarNo ratings yet

- RISC Vs CISCDocument10 pagesRISC Vs CISCbrijesh.gec21No ratings yet

- RISC vs. CISCDocument3 pagesRISC vs. CISCladukhushi09No ratings yet

- Complex Instruction Set ComputerDocument17 pagesComplex Instruction Set ComputerkangkanpaulNo ratings yet

- UNIT-1 Introduction To MicrocontrollersDocument8 pagesUNIT-1 Introduction To MicrocontrollerssupriyaNo ratings yet

- Jan Marie Veatrice M. Pacia 4-ECE: What Are Cisc and Risc Architecture? How Do They Differ From Each Other?Document6 pagesJan Marie Veatrice M. Pacia 4-ECE: What Are Cisc and Risc Architecture? How Do They Differ From Each Other?Jan Marie Veatrice PaciaNo ratings yet

- Session2 - Introduction To RISC and CISCDocument4 pagesSession2 - Introduction To RISC and CISCHillary MurungaNo ratings yet

- Risc Vs CiscDocument1 pageRisc Vs CiscPrateek SanchetiNo ratings yet

- Instruction Set ArchitectureDocument4 pagesInstruction Set ArchitectureashuNo ratings yet

- Ramesh .B ELEC 6200 Computer Architecture & Design Fall 2008Document17 pagesRamesh .B ELEC 6200 Computer Architecture & Design Fall 2008Amandeep Kaur JunejaNo ratings yet

- Structure of Computer SystemsDocument16 pagesStructure of Computer SystemsMussie KebedeNo ratings yet

- (Computer Architecture CIA-3) : (By: Nikhil Kumar Yadav) (Roll. No.: 1847241) (Date of Submission: 06-09-2019)Document8 pages(Computer Architecture CIA-3) : (By: Nikhil Kumar Yadav) (Roll. No.: 1847241) (Date of Submission: 06-09-2019)NIKHIL KUMAR YADAV 1847241No ratings yet

- 03 Cisc RiscDocument37 pages03 Cisc RiscahmedNo ratings yet

- Notes: Chapter 2: System Unit Book: Chapter 4Document8 pagesNotes: Chapter 2: System Unit Book: Chapter 4ROHAB TAHIRNo ratings yet

- CISC vs RISC: Complex vs Simple Instruction ArchitecturesDocument22 pagesCISC vs RISC: Complex vs Simple Instruction Architectureskaleab seleshiNo ratings yet

- ISA Instruction Set Architecture LessonDocument9 pagesISA Instruction Set Architecture LessonghassanNo ratings yet

- CA Lecture 10 1Document5 pagesCA Lecture 10 1kalimNo ratings yet

- Chapter 2 Lecture 6Document30 pagesChapter 2 Lecture 6Gebrie BeleteNo ratings yet

- Microcoded ArchDocument12 pagesMicrocoded ArchAnonymous pHi4dXNo ratings yet

- CISC Vs RISC and I286, I386, I486Document12 pagesCISC Vs RISC and I286, I386, I486Manash MandalNo ratings yet

- Introduction To Microprocessor and MicrocontrollerDocument19 pagesIntroduction To Microprocessor and MicrocontrollerSharanya VaidyanathNo ratings yet

- University of The People CS1104: Computer Systems Instructor: Raval Dipakkumar May 11, 2022Document4 pagesUniversity of The People CS1104: Computer Systems Instructor: Raval Dipakkumar May 11, 2022Qurtiss MayfieldNo ratings yet

- Design of 32-Bit Risc Cpu Based On Mips: Journal of Global Research in Computer ScienceDocument5 pagesDesign of 32-Bit Risc Cpu Based On Mips: Journal of Global Research in Computer ScienceAkanksha Dixit ManodhyaNo ratings yet

- LOAD A, 2:3 LOAD B, 5:2 Prod A, B STORE 2:3, ADocument2 pagesLOAD A, 2:3 LOAD B, 5:2 Prod A, B STORE 2:3, ADinesh KumarNo ratings yet

- Introduction - Unit I MCDocument35 pagesIntroduction - Unit I MCKirthi RkNo ratings yet

- The Design of A RISC Architecture and Its Implementation With An FPGADocument24 pagesThe Design of A RISC Architecture and Its Implementation With An FPGASneha AngreNo ratings yet

- Chapter 4 - Central Processing Units Is BzudhesvsDocument7 pagesChapter 4 - Central Processing Units Is Bzudhesvsrosdi jkmNo ratings yet

- Risc VDocument4 pagesRisc VOlhaNo ratings yet

- CA - 2marksDocument73 pagesCA - 2marksVishal BasugadeNo ratings yet

- AssembyDocument57 pagesAssembyOmar KamilNo ratings yet

- IntroductionDocument9 pagesIntroductionMuhammad Ghassan JawwadNo ratings yet

- What Is RISC and CISC Architecture - EdgefxkitsDocument11 pagesWhat Is RISC and CISC Architecture - EdgefxkitsjeyasuthanjNo ratings yet

- RISC vs CISC differencesDocument80 pagesRISC vs CISC differencesAKASH GHOSHNo ratings yet

- Ijsrp Apr 2012 28Document4 pagesIjsrp Apr 2012 28Adip ChyNo ratings yet

- Linux Kernel Code IntroductionDocument91 pagesLinux Kernel Code IntroductionKalimuthu VelappanNo ratings yet

- ES Unit-2Document28 pagesES Unit-2palaji pradeepNo ratings yet

- Embedded-and-Real-Time-Systems-2 Marks FinalDocument20 pagesEmbedded-and-Real-Time-Systems-2 Marks FinalranjaniNo ratings yet

- Lecture 18 - RICS and CISC PropertiesDocument8 pagesLecture 18 - RICS and CISC PropertiesPragya SinghNo ratings yet

- Grehack 2015 - Paper - Industrial Control Systems Dynamic Code InjectionDocument14 pagesGrehack 2015 - Paper - Industrial Control Systems Dynamic Code InjectionHeh MdeNo ratings yet

- Sr. No. Key Computer Architecture Computer OrganizationDocument11 pagesSr. No. Key Computer Architecture Computer OrganizationKashif ZamanNo ratings yet

- Lect 2Document5 pagesLect 2ABEGUNDE OMOLAYONo ratings yet

- CISC Vs RISC ProcessorsDocument2 pagesCISC Vs RISC ProcessorsgcoopseyNo ratings yet

- Home Work 3: Class: M.C.A SECTION: RE3004 Course Code: CAP211Document15 pagesHome Work 3: Class: M.C.A SECTION: RE3004 Course Code: CAP211Vikas GuptaNo ratings yet

- Chapter 2: Advanced Computer ArchitectureDocument101 pagesChapter 2: Advanced Computer ArchitectureTigabu Yaya100% (2)

- The Porting of Real-Time Operating System uC/OS-II On MCS-51 Series of MCUDocument3 pagesThe Porting of Real-Time Operating System uC/OS-II On MCS-51 Series of MCUpramani90No ratings yet

- 5-Harvard Architecture - CISC & RISC Architectures-10!01!2024Document18 pages5-Harvard Architecture - CISC & RISC Architectures-10!01!2024shashank.reddy5804No ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Basic Block Diagram of Op-Amp (BBDOADocument26 pagesBasic Block Diagram of Op-Amp (BBDOAkrishNo ratings yet

- Transistors and ApplicationDocument14 pagesTransistors and ApplicationkrishNo ratings yet

- Measure unknown resistances and capacitances accurately with Kelvin, Maxwell, Anderson and Schering bridgesDocument7 pagesMeasure unknown resistances and capacitances accurately with Kelvin, Maxwell, Anderson and Schering bridgeskrishNo ratings yet

- Bridge CircuitsDocument6 pagesBridge CircuitskrishNo ratings yet

- Digital Image Processing - S. Jayaraman, S. Esakkirajan and T. VeerakumarDocument112 pagesDigital Image Processing - S. Jayaraman, S. Esakkirajan and T. Veerakumarkrish100% (2)

- Communication technologies for railway stationsDocument3 pagesCommunication technologies for railway stationskrishNo ratings yet

- DEBUGGING and FeaturesDocument16 pagesDEBUGGING and FeatureskrishNo ratings yet

- Bridge CircuitsDocument6 pagesBridge CircuitskrishNo ratings yet

- Camara - OV7670Document30 pagesCamara - OV7670Carlos Oreza SanzNo ratings yet

- C 02Document22 pagesC 02krishNo ratings yet

- Electronic System Reliability Engineering PPT-c09Document15 pagesElectronic System Reliability Engineering PPT-c09krishNo ratings yet

- Academic Calendar For M. Tech & M. Pharmacy I & II Years (2015 Batch) JNTUKDocument2 pagesAcademic Calendar For M. Tech & M. Pharmacy I & II Years (2015 Batch) JNTUKkrishNo ratings yet

- Methods to estimate stakeholder views of sustainabilityDocument7 pagesMethods to estimate stakeholder views of sustainabilityAlireza FatemiNo ratings yet

- Product Data Sheet For CP 680-P and CP 680-M Cast-In Firestop Devices Technical Information ASSET DOC LOC 1540966Document1 pageProduct Data Sheet For CP 680-P and CP 680-M Cast-In Firestop Devices Technical Information ASSET DOC LOC 1540966shama093No ratings yet

- What's Wrong With American Taiwan Policy: Andrew J. NathanDocument14 pagesWhat's Wrong With American Taiwan Policy: Andrew J. NathanWu GuifengNo ratings yet

- Maharashtra Auto Permit Winner ListDocument148 pagesMaharashtra Auto Permit Winner ListSadik Shaikh50% (2)

- Sinclair User 1 Apr 1982Document68 pagesSinclair User 1 Apr 1982JasonWhite99No ratings yet

- 202112fuji ViDocument2 pages202112fuji ViAnh CaoNo ratings yet

- Emergency Management of AnaphylaxisDocument1 pageEmergency Management of AnaphylaxisEugene SandhuNo ratings yet

- C4 ISRchapterDocument16 pagesC4 ISRchapterSerkan KalaycıNo ratings yet

- Physics Derived Units and Unit Prefixes Derived UnitDocument15 pagesPhysics Derived Units and Unit Prefixes Derived UnitJohnRenzoMolinarNo ratings yet

- United-nations-Organization-uno Solved MCQs (Set-4)Document8 pagesUnited-nations-Organization-uno Solved MCQs (Set-4)SãñÂt SûRÿá MishraNo ratings yet

- Shouldice Hospital Ltd.Document5 pagesShouldice Hospital Ltd.Martín Gómez CortésNo ratings yet

- Fast Aldol-Tishchenko ReactionDocument5 pagesFast Aldol-Tishchenko ReactionRSLNo ratings yet

- SiloDocument7 pagesSiloMayr - GeroldingerNo ratings yet

- Philippine Population 2009Document6 pagesPhilippine Population 2009mahyoolNo ratings yet

- Equilibruim of Forces and How Three Forces Meet at A PointDocument32 pagesEquilibruim of Forces and How Three Forces Meet at A PointSherif Yehia Al MaraghyNo ratings yet

- Be It Enacted by The Senate and House of Representatives of The Philippines in Congress AssembledDocument2 pagesBe It Enacted by The Senate and House of Representatives of The Philippines in Congress AssembledCesar ValeraNo ratings yet

- 2020 Global Finance Business Management Analyst Program - IIMDocument4 pages2020 Global Finance Business Management Analyst Program - IIMrishabhaaaNo ratings yet

- Dolni VestoniceDocument34 pagesDolni VestoniceOlha PodufalovaNo ratings yet

- WWW - Commonsensemedia - OrgDocument3 pagesWWW - Commonsensemedia - Orgkbeik001No ratings yet

- eHMI tool download and install guideDocument19 pageseHMI tool download and install guideNam Vũ0% (1)

- Chromate Free CoatingsDocument16 pagesChromate Free CoatingsbaanaadiNo ratings yet

- Ball Valves Pentair Valves and ControlsDocument16 pagesBall Valves Pentair Valves and ControlsABDUL KADHARNo ratings yet

- Physioex 9.0 Exercise 1 Act 1Document5 pagesPhysioex 9.0 Exercise 1 Act 1Adela LhuzNo ratings yet

- Checklist of Requirements For OIC-EW Licensure ExamDocument2 pagesChecklist of Requirements For OIC-EW Licensure Examjonesalvarezcastro60% (5)

- Returnable Goods Register: STR/4/005 Issue 1 Page1Of1Document1 pageReturnable Goods Register: STR/4/005 Issue 1 Page1Of1Zohaib QasimNo ratings yet