Professional Documents

Culture Documents

VLSI Verification and Testing New

Uploaded by

vlsisiva0 ratings0% found this document useful (0 votes)

40 views2 pagesVLSI Design verification and Testing

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentVLSI Design verification and Testing

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

40 views2 pagesVLSI Verification and Testing New

Uploaded by

vlsisivaVLSI Design verification and Testing

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 2

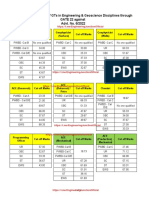

Registration Fee*

REGISTRATION FORM

Name

Designation

Organization

Address for

Communication

Faculty / Industry Persons

Rs.2290/-

Students & Full Time

Research Scholars

Accommodation (2 days)

Rs.1718/Rs. 630/-

Two Day National Workshop

*inclusive of 14.5% GST

(Registration fee Includes working lunch and snacks)

Certificate will be issued to all the registered participants. DD in favour of VIT University payable at

Phone Number

E-mail ID

Accommodation

: Yes/No

Venue

Amount

Room No. 237, Technology Tower,

DD No. & Date

Bank Name/Branch

Vellore.

on

VLSI Design

Verification and Testing

18th and 19th March 2016

VIT University, Vellore

Important Dates

Last Date for Registration : 16th-March, 2016.

Place:

Date:

Workshop Dates

Signature of Participant

Participants can also register for the workshop by filling

up an online registration form:

http://goo.gl/forms/PO1h1zLOj1

Application will be accepted on a first come first serve

basis. Number of participants is limited to 50.

Address for Correspondence

Dr. S. Sivanantham

Associate Professor

Department of Micro and Nanoelectronics

School of Electronics Engineering

VIT University, Vellore-632 014

Tamilnadu, India

: March 18-19, 2016

Organizing Coordinators

Dr. Sivanantham S, Associate Professor

Email: ssivanantham@vit.ac.in

contact No: +91 9894432359

Prof. Prayline Rajabai C, Assistant Professor

Email: prayline.c@vit.ac.in

contact No: +91 7200577872

Organized by

Department of Micro and Nanoelectronics

School of Electronics Engineering

VIT University

Vellore 632 014

Tamilnadu, India

ABOUT VIT UNIVERSITY

VIT University was established with the aim of providing quality higher education on par with international

standards. It persistently seeks and adopts innovative

methods to improve the quality of higher education on a

consistent basis. The campus has a cosmopolitan atmosphere with students from all corners of the globe. Experienced and learned teachers are strongly encouraged to

nurture the students. The global standards set at VIT in

the field of teaching and research spur us on in our relentless pursuit of excellence. In fact, it has become a

way of life for us. The highly motivated youngsters on

the campus are a constant source of pride. Our MoU

with various international universities are our major

strength.

LAB FACILITIES

VLSI Laboratory is equipped with facilities to perform

digital, analog, mixed signal and RFIC design using

EDA tools like Cadence and Synopsys (Full custom

design and ASIC design with DFT) each with 65 user

licenses; Xilinx ISE Suite, Altera Design Suite (FPGA

based system design); Synopsys TCAD Tools for simulating device performance; Hardware platforms like Al-

ABOUT THE WORKSHOP

The program is intended for the Faculty, PG students,

Basics of VLSI Testing

R & D in the field of testing and verification of VLSI

Automatic Test Pattern and Fault simulation

Design. The main objective of the program is to provide

DFT Scan and BIST methodology

Hands-on session on the following opics:

basic fundamentals of different testing and verification

methods along with hands-on practice and advances.

Fault Simulation

RESOURCE PERSONS

ATPGA

Dr. S. Sivanantham,

Test Synthesis using Cadence RTL Compiler

Scan Insertion

VIT University, Vellore.

Dr.B.Ramkumar

DFT Engineer, Bangalore

Mr.Sravan Kumar

Sr Verification Engineer, Bangalore

Test generation using Cadence EncounterTest

Research Aspects in VLSI Testing

DAY 2 : VLSI DESIGN VERIFICATION

SystemVerilog - Overview for Design Verification

Functional Verification Approaches

Prof. Prayline Rajabai C

Object-Oriented Programming

VIT University, Vellore.

Assertions

Randomization

Functional Coverage

Hands-on Training on Functional Verification

Universal Verification methodology

TOOLS USED FOR WORKSHOP

FPGA Kit and Virtex-5 OpenSPARC Evaluation Plat-

Verification : Modelsim and Cadence ncsim

form. We have partners with various semiconductor

Testing

Belgium through Europractice.

DAY 1 : VLSI TESTING

research scholars, practicing engineers and people from

tera-DE3 and DE2 FPGA board, Xilinx Spartan 3E

foundries to access technology design kits with IMEC-

TOPICS TO BE COVERED

: Encounter RTL Compiler and

Encounter Test from Cadence

You might also like

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Advanced Communication LabDocument2 pagesAdvanced Communication LabvlsisivaNo ratings yet

- ECE301 - Course IntroductionDocument17 pagesECE301 - Course IntroductionvlsisivaNo ratings yet

- Model QPDocument6 pagesModel QPvlsisivaNo ratings yet

- Test - 2 QP OnlyDocument1 pageTest - 2 QP OnlyvlsisivaNo ratings yet

- Bphy Verilog HDLDocument11 pagesBphy Verilog HDLvlsisivaNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5795)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1091)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Malavika Exam PaperDocument2 pagesMalavika Exam PaperFunds lolNo ratings yet

- 10 Minutes Check in Conversation GuideDocument3 pages10 Minutes Check in Conversation GuideAjisafe Jerry T-moneyNo ratings yet

- The Invention of AdolescenceDocument3 pagesThe Invention of AdolescenceJincy JoyNo ratings yet

- Gasal E FormDocument10 pagesGasal E FormMuhammad Nauman Hafeez KhanNo ratings yet

- MCC Fire and Emergency Progress Report 2018Document38 pagesMCC Fire and Emergency Progress Report 2018Toby VueNo ratings yet

- CIVE 430 SyllabusDocument3 pagesCIVE 430 SyllabusDouglas WentzelNo ratings yet

- Khyber Pakhtunkhwa Board of Technical Education Peshawar Examination Admission Form (WWW - Kpbte.edu - PK)Document3 pagesKhyber Pakhtunkhwa Board of Technical Education Peshawar Examination Admission Form (WWW - Kpbte.edu - PK)Jamal uddin AkakhelNo ratings yet

- How To Have Bad SexDocument28 pagesHow To Have Bad Sexlfbarbal1949100% (2)

- Revised Final Recruitment at Ksschool Website 2022Document6 pagesRevised Final Recruitment at Ksschool Website 2022Mehul PanchalNo ratings yet

- The Ideal Self at Play The Appeal of Video Games That Let You Be All You Can BeDocument9 pagesThe Ideal Self at Play The Appeal of Video Games That Let You Be All You Can BeamaliaulfahNo ratings yet

- Schedule of Events Isamme 2021-1Document7 pagesSchedule of Events Isamme 2021-1Helmi IlhamNo ratings yet

- SBP SBOTS (OG-2) 22nd Batch TestDocument1 pageSBP SBOTS (OG-2) 22nd Batch Testmuhammad waqasNo ratings yet

- Questionnaires For Primary SchoolDocument20 pagesQuestionnaires For Primary SchoolVirinahNo ratings yet

- Procedure and Schedule of SSB TestDocument18 pagesProcedure and Schedule of SSB TestAnuj PuniyaNo ratings yet

- 1 Definition of TermsDocument15 pages1 Definition of Termsاسامة محمد السيد رمضانNo ratings yet

- Drone Technology Course PresentationDocument57 pagesDrone Technology Course PresentationChristopher Salber100% (1)

- Templates For The 2019 Ipcrf ValidationDocument5 pagesTemplates For The 2019 Ipcrf ValidationKerth GalagpatNo ratings yet

- Math Project ProposalDocument4 pagesMath Project ProposalNapoleon Agbing86% (28)

- Edf1304 Assignment 1 Part 1 - Emily Greenberg - 26005123 1Document5 pagesEdf1304 Assignment 1 Part 1 - Emily Greenberg - 26005123 1api-285104874No ratings yet

- MCAT 2017 May-2018 Apr Percentiles PDFDocument2 pagesMCAT 2017 May-2018 Apr Percentiles PDFBarry HeadNo ratings yet

- 002131-1-2 A 6 CMAS TwoStarsDiverStandard-PpO2 PDFDocument3 pages002131-1-2 A 6 CMAS TwoStarsDiverStandard-PpO2 PDFregiscbarcNo ratings yet

- ONGC GATE 2022 Cut Off MarksDocument3 pagesONGC GATE 2022 Cut Off MarksSachin BhadanaNo ratings yet

- Filipino Nurses Health Beliefs Behaviors and PracticesDocument6 pagesFilipino Nurses Health Beliefs Behaviors and PracticesKathleen Lopez50% (2)

- Detailed Lesson PlanDocument2 pagesDetailed Lesson PlanClaudine Lumbre100% (1)

- Portfolio Project 2 Edu 201Document3 pagesPortfolio Project 2 Edu 201api-374199648No ratings yet

- Tieng Viet Men Yeu B - Vietnamese Level B - TextbookDocument548 pagesTieng Viet Men Yeu B - Vietnamese Level B - TextbookBen Jenkins100% (5)

- Future Simple TEST PDFDocument3 pagesFuture Simple TEST PDFagustinaNo ratings yet

- 4.2 Probability Diagrams - Tree & Venn Diagrams: Question PaperDocument7 pages4.2 Probability Diagrams - Tree & Venn Diagrams: Question PaperharshalsachdevNo ratings yet

- Unit 1 Session 7Document3 pagesUnit 1 Session 7clayNo ratings yet

- LAVANYA REFERENCE (114) New-1Document10 pagesLAVANYA REFERENCE (114) New-1RaghuNo ratings yet