Professional Documents

Culture Documents

TCA965

Uploaded by

Nacer MezghicheCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

TCA965

Uploaded by

Nacer MezghicheCopyright:

Available Formats

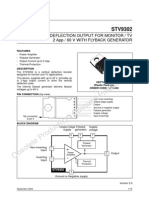

Window Discriminator

TCA 965 B

Preliminary

Bipolar IC

Features

Two window settings

direct setting of lower and upper edge

voltage (window edges)

indirect setting by window center

voltage and half window width

Adjustable hysteresis

Digital outputs with open collectors

for currents up to 50 mA

Adjustable reference voltage VStab

Type

TCA 965 B

P-DIP-14-1

Ordering Code

Package

Q67000-A8338

P-DIP-14-1

Not for new design

The window discriminator compares an input voltage to a defined voltage window. The

digital outputs show whether the input voltage is below, within or above this window.

The TCA 965 B window discriminator is especially suitable as a tracking or

compensating controller with a dead band in control engineering and for the selection of

DC voltages within a certain tolerance of the required setpoint value in measurement

engineering. When it is used as a Schmitt trigger, switching frequencies up to a typical

value of 50 kHz are possible.

Semiconductor Group

1998-02-10

TCA 965 B

Functional Description

Amplifier Amp 3 increases the voltage of the reference source R to VStab = 2 x VREF. The

amplification factor can be altered by external wiring. With direct setting of the window,

the input voltage appears on amplifier Amp 1 (V8), the upper edge voltage on

comparator K2 (V6) and the lower edge voltage on comparator K1 (V7).

With indirect setting of the window, the input voltage appears on inputs V6 and V7, while

the center voltage is connected to amplifier A1 (V8).

The voltage applied to the input (V9) of amplifier Amp 2 is subtracted symmetrically from

the output voltage of amplifier Amp 1 and added. The comparators switch with

hysteresis. The logic gates have open-collector outputs.

If the inhibit input A or B is connected to ground, output A or B will always be high.

+ VS

VREF

11

20 k

20 k

V7

10

+Amp 3

_ K1

VStab

+

4

<_ 1

Amp 1

V8

13

1

12

Amp 2

V6

8

V=1

V9

Inhibit A

Inhibit B

9

_

6

V=1

+

_ K2

14

IEB00091

Outputs A, B, C, D are open-collector

Block Diagram

Semiconductor Group

1998-02-10

TCA 965 B

Pin Configuration

(top view)

TCA 965 B

GND

14

13

12

Inhibit B

Inhibit A

11

+V S

V REF

10

V Stab

V6

V9

V7

V8

IEP00292

Pin Definitions and Functions

Pin

Symbol

Pin Function in

Direct Setting

Indirect Setting

of Window

1

2

3

4

5

GND

A

D

Inhibit A

6

7

8

9

V6

V7

V8

V9

10

11

12

13

14

VStab

+ VS

VREF

Inhibit B

C

B

Semiconductor Group

GND

Logic output A

Logic output D = A @ B (AND)

Connected to GND: logic output A = HIGH

Internal VREF = 3 V

Upper edge voltage

Lower edge voltage

Input voltage

GND

Input voltage V6/7

Input voltage V6/7

Center voltage

Half window width

Internal VStab = 6 V

Supply voltage

Connected to GND: logic output B = HIGH

Logic output C = A @ B (NAND)

Logic output B

3

1998-02-10

TCA 965 B

Absolute Maximum Ratings

Maximum ratings for ambient temperature TA = 25 to 85 C

Parameter

Symbol

Limit Values

min.

max.

Unit

Supply voltage (pin 11)

Difference in input voltage between pins 6, 7, 8

Input voltage (pins 6, 7, 8, 9)

VS

VI

VI

30

15

30

V

V

V

Output current (pins 2, 3, 13, 14)

IQ

50

mA

Output voltage (pins 2, 3, 13, 14)

independent of VS

Voltage on VREF (pin 5)

VQ

VR

30

8

V

V

Output current of stabilized voltage (pin 10)

I10

10

mA

Inhibit input voltage (pins 4, 12)

VIH

Junction temperature

Storage temperature

Tj

Tstg

55

150

125

C

C

Rth SA

80

K/W

Supply voltage

VS

4.5

30

Ambient temperature

TA

25

85

Thermal resistance system - air

P-DIP-14-1

Operating Range

Semiconductor Group

1998-02-10

TCA 965 B

Characteristics

VS = 10 V; TA = 25 C

Parameter

Symbol

Limit Values

Unit

Test

Condition

Test

Circuit

mA

V2, V13 = VQH

min. typ. max.

Current consumption

Input current

(pins 6, 7, 8)

Input current, pin 9

Input offset voltage in

direct setting of window

Input offset voltage in

indirect setting of window

Input-voltage range on

pins 6, 7, 8

Input-voltage range on

pin 9

Differential input voltage

IS

II

II

nA

50

20

400 3000 nA

VIO

20

20

mV

VIO

50

50

mV

VI

1.5

VS 1 V

VI

50

VS/2

13

13

mV

V

V

V6 (V8 V9)

(V8 + V9) V7

1

1

VI < 13 V

Reference voltage

Stabilized voltage on

pin 10

TC of reference voltage

Sensitivity of reference

voltage to supply-voltage

variation

V5

2.8

3.2

V10

V5

5.5

6

0.4

6.5

V

VS > 7.9 V

mV/K

Output reverse current

IQH

V5/VS

100 200

500 800

mV

mV

IQ = 10 mA 1

IQ = 50 mA

35

1.8

mV

V

Output saturation voltage VQL

IREF = 0

mV/V

10

Hysteresis of window

edges

Inhibit threshold

VU VL

V4, 12

18

1

22

Inhibit current

I4, 12

100

Switching frequency

fdir

find

20

50

kHz

kHz

1

2

Semiconductor Group

1998-02-10

TCA 965 B

VS

S11

11

6

RL

TCA 965B

QH2

QH3

13

QH13

14

QH14

RL

RL

RL

10

V6

V7

V8

9

9

12

V5

V10

VQL14

VQL13

VQL3

VQL2

IES00086

V4

V12

Test Circuit 1

Direct Setting of Window

Semiconductor Group

1998-02-10

TCA 965 B

VS

S11

11

RL

TCA 965B

QH2

QH3

13

QH13

14

QH14

RL

RL

RL

8

10

9

V8

V9

12

V5

V10

VQL14

VQL13

VQL3

VQL2

V6/7

IES00087

V4

V12

Test Circuit 2

Indirect Setting of Window by Center Voltage and Half Window Width

Semiconductor Group

1998-02-10

TCA 965 B

Inhibit Inputs 4,12

VS

V4,12

100

1 k

Inputs 6, 7, 8

V6,7,8

V4,12

Outputs A, B

GND

High

>7V

Not permitted

open

Normal function

> 1.8 V

Low

Input 9

1 k

V9

Outputs VREF , VStab

Outputs 2, 3, 13, 14

VStab

R

VREF

Q

IES00088

Schematic Circuit Diagrams

Semiconductor Group

1998-02-10

TCA 965 B

VS

C1

R1

10

11

6 V

6

R4

R2

TCA 965 B

R5

7 V

7

13

8 V

8

14

C2

R6

V

C3

R3

V9

9

12

R7

IES00294

To increase the switching frequency, pin 9 may be grounded

via R 7 ( V9 approx. 30...40 mV).

Application Circuit 1

Direct Setting of Lower and Upper Edge Voltages

V6 V9 = Upper edge voltage

V7 + V9 = Lower edge voltage

V8 =

Input voltage

Semiconductor Group

1998-02-10

TCA 965 B

V10

VL

VU

t

V7

IES00296

Definition of the Offset Voltage VIO

VL + VU

V 10 = -------------------- V7

2

Semiconductor Group

10

1998-02-10

TCA 965 B

V8

Upper

Edge

V6

Lower

Edge

V7

t

A

B

C

D

Inhibit A

Pin 4 on GND

1.8 V < Pin

1

0

4<7V

1

0

A

B

1

0

1

0

C

D

D

Inhibit B

Pin 12 on GND

1.8 V < Pin

A

B

12 < 7 V

A

1

0

B

C

1

0

1

0

1

0

IES00295

Application Circuit 1

Direct Setting of Lower and Upper Edge Voltages

Semiconductor Group

11

1998-02-10

TCA 965 B

VS

C1

10

R1

C2

11

R3

R5

R6

8 V

8

9 V

9

TCA 965 B

R7

V

6 V

6

13

7 V

7

14

C3

R2

12

R4

IES00297

Application Circuit 2

Indirect Setting of Window by Center Voltage and Half-Window Width V

V6 = V7 = Input voltage

V8 =

Center voltage

V9 =

Half window width

Semiconductor Group

12

1998-02-10

TCA 965 B

V10

VL

VU

V8 - V9

V10 =

VL - VU

2

- (V 8 - V 9 )

IES00299

Definition of the Offset Voltage VIO

VL + VU

V 10 = -------------------- (V 8 V 9 )

2

Semiconductor Group

13

1998-02-10

TCA 965 B

V8

Upper

Edge

V6

Lower

Edge

V7

t

B

C

D

Inhibit A

Pin 4 on GND

1.8 V < Pin

1

0

4<7V

1

0

B

B

C

1

0

1

0

C

D

D

Inhibit B

Pin 12 on GND

1.8 V < Pin

12 < 7 V

1

0

1

0

1

0

1

0

B

C

C

D

D

IED00298

Application Circuit 2

Indirect Setting of Window by Center Voltage and Half-Window Width V

Semiconductor Group

14

1998-02-10

TCA 965 B

VS

10

RL

11

R1

RL

RL

13

6

14

TCA 965B

R2

R4

3

9

R3

P = R5

V3

VH

VH

V8

V7

V6

IES00089

Application Circuit 3

Symmetrically Enlarged Edge Hysteresis in Direct Setting of Window

Calculation of Hysteresis VH

R5

V H = V 10 -----------------R4 + R5

V

V 10

10

------------------- + -------------------------------- 10 mA

R4 + R5 R1 + R2 + R3

Semiconductor Group

15

1998-02-10

TCA 965 B

VS

10

RL

11

RL

RL

R1

14

13

6

TCA 965B

R5

R3

9

1

R2

R4

V3

VH =

V9/2 - V9/1

V9/1

V9/2

V8

0

V6/7

IES00090

Application Circuit 4

Symmetrically Enlarged Edge Hysteresis in Indirect Setting of Window

Calculation of Hysteresis VH

VH = V9/2 V9/1

R 4 || R 5

V 9/1 = V 10 ------------------------------R 3 + R 4 || R 5

R4

V 9/2 = V 10 -----------------R3 + R4

Semiconductor Group

16

1998-02-10

TCA 965 B

GPD05005

P-DIP-14-1

(Plastic Dual In-line Package)

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book Package Information.

Semiconductor Group

17

Dimensions in mm

1998-02-10

You might also like

- Tca 965 BDocument18 pagesTca 965 BMichael WickertNo ratings yet

- TV Vertical Output CircuitDocument7 pagesTV Vertical Output Circuitaldo_suviNo ratings yet

- Skhi 22B DatasheetDocument9 pagesSkhi 22B DatasheetRakesh RoyNo ratings yet

- VNH2SP30-E: Automotive Fully Integrated H-Bridge Motor DriverDocument26 pagesVNH2SP30-E: Automotive Fully Integrated H-Bridge Motor DriverIan LuksNo ratings yet

- ZXCT1041 Bidirectional Precision High-Side Current Monitor: DescriptionDocument12 pagesZXCT1041 Bidirectional Precision High-Side Current Monitor: DescriptionEldhose VargheseNo ratings yet

- 74LVC08A: 1. General DescriptionDocument15 pages74LVC08A: 1. General DescriptionWalterNo ratings yet

- General Description: Dual Supply Translating Transceiver Auto Direction Sensing 3-StateDocument26 pagesGeneral Description: Dual Supply Translating Transceiver Auto Direction Sensing 3-StateJimChenNo ratings yet

- Irams10Up60A: Pd-94640 RevhDocument17 pagesIrams10Up60A: Pd-94640 RevhCleiton Da Gama GarciaNo ratings yet

- ADC0831/ADC0832/ADC0834 and ADC0838 8-Bit Serial I/O A/D Converters With Multiplexer OptionsDocument33 pagesADC0831/ADC0832/ADC0834 and ADC0838 8-Bit Serial I/O A/D Converters With Multiplexer OptionsRoy Muy GolfoNo ratings yet

- Open Loop Phase Control Circuit: DescriptionDocument7 pagesOpen Loop Phase Control Circuit: DescriptionMuhammad NajibNo ratings yet

- TL494-D PWM Duty Cycle GenerationDocument14 pagesTL494-D PWM Duty Cycle GenerationMashood NasirNo ratings yet

- Ca3260, Ca3260A: 4Mhz, Bimos Operational Amplifier With Mosfet Input/Cmos Output FeaturesDocument4 pagesCa3260, Ca3260A: 4Mhz, Bimos Operational Amplifier With Mosfet Input/Cmos Output FeaturesPaulo Cesar SimonettiNo ratings yet

- 74HC08 74HCT08: 1. General DescriptionDocument16 pages74HC08 74HCT08: 1. General DescriptionCesar VilledaNo ratings yet

- Mc74hc4051a DDocument17 pagesMc74hc4051a DroozbehxoxNo ratings yet

- STV 9302Document15 pagesSTV 9302krish8717No ratings yet

- Datasheet TDA8356Document13 pagesDatasheet TDA8356João PauloNo ratings yet

- Fan 7361Document9 pagesFan 7361Odalis CabaNo ratings yet

- Mc13281fyp PDFDocument16 pagesMc13281fyp PDFCalin LuchianNo ratings yet

- Advanced Motion Controls Dq111se20a8bdc-HDocument8 pagesAdvanced Motion Controls Dq111se20a8bdc-HElectromateNo ratings yet

- STV9302BDocument15 pagesSTV9302BcocolisoteNo ratings yet

- Panel Instrument Application NotesDocument23 pagesPanel Instrument Application Notessantosh_babar_26No ratings yet

- Low Power Dual Operational Amplifiers Az358/358CDocument13 pagesLow Power Dual Operational Amplifiers Az358/358CMarissa ValdezNo ratings yet

- 32Document3 pages32Tárcio AndréNo ratings yet

- XR 2206 V 1Document16 pagesXR 2206 V 1Leon F AceroNo ratings yet

- STV8172A: Vertical Deflection Booster For 3-A TV/Monitor Applications With 70-V Flyback GeneratorDocument14 pagesSTV8172A: Vertical Deflection Booster For 3-A TV/Monitor Applications With 70-V Flyback GeneratorJose GiudiceNo ratings yet

- Power Amplifiers For Proportional Valves: Amplifier CardsDocument5 pagesPower Amplifiers For Proportional Valves: Amplifier CardsFathi MusaNo ratings yet

- ADC0844/ADC0848 8-Bit P Compatible A/D Converters With Multiplexer OptionsDocument20 pagesADC0844/ADC0848 8-Bit P Compatible A/D Converters With Multiplexer Optionsrazali1982No ratings yet

- Isolated Flyback Switching Regulator W - 9V OutputDocument16 pagesIsolated Flyback Switching Regulator W - 9V OutputCasey DialNo ratings yet

- 5-CH BTL DRIVER FOR DVD PLAYER WITH DISC BIDIRECTIONAL DRIVER AND TWO VARIABLE REGULATORSDocument8 pages5-CH BTL DRIVER FOR DVD PLAYER WITH DISC BIDIRECTIONAL DRIVER AND TWO VARIABLE REGULATORSalbinicue1No ratings yet

- Driver Bobina de Encendido VB326SPDocument9 pagesDriver Bobina de Encendido VB326SPteroplasNo ratings yet

- Precision Phase-Locked Loop: ... The Analog Plus CompanyDocument21 pagesPrecision Phase-Locked Loop: ... The Analog Plus Companykao08No ratings yet

- Datasheet WS2801Document15 pagesDatasheet WS2801Nguyễn Trọng NghĩaNo ratings yet

- 74LVC00A: 1. General DescriptionDocument14 pages74LVC00A: 1. General DescriptionVlad Cristia-AvramNo ratings yet

- Data Sheet-IC 4017-NXP Philips PDFDocument16 pagesData Sheet-IC 4017-NXP Philips PDFGirish OniyilNo ratings yet

- 74HC10-Q100 74HCT10-Q100: 1. General DescriptionDocument13 pages74HC10-Q100 74HCT10-Q100: 1. General DescriptionNelson RodriguezNo ratings yet

- 8051 SchematicDocument37 pages8051 SchematicShabeeb Ali OruvangaraNo ratings yet

- Data SheetDocument20 pagesData SheetLuis Fernando ChiavegatiNo ratings yet

- AM5888SDocument10 pagesAM5888ScpfliegerNo ratings yet

- Datasheet NECDocument20 pagesDatasheet NECPham Trung KienNo ratings yet

- General Description: Quad Bilateral SwitchDocument23 pagesGeneral Description: Quad Bilateral Switchtotal4321No ratings yet

- Advanced Motion Controls Dq111ee20a8bdc-Qd1Document7 pagesAdvanced Motion Controls Dq111ee20a8bdc-Qd1ElectromateNo ratings yet

- Ir2181 Igbt Driver PDFDocument21 pagesIr2181 Igbt Driver PDFismifaizulNo ratings yet

- Advanced Motion Controls Dq111se20a8bdcDocument7 pagesAdvanced Motion Controls Dq111se20a8bdcElectromateNo ratings yet

- Tda 7266Document9 pagesTda 7266Nenad DejanovićNo ratings yet

- 5-channel BTL Driver for DVD player AM5868SDocument10 pages5-channel BTL Driver for DVD player AM5868SnoileksirtNo ratings yet

- Order DC servo motor controller/driver semiconductor technical data sheetDocument16 pagesOrder DC servo motor controller/driver semiconductor technical data sheetLuiz EduardoNo ratings yet

- 10-Bit and 12-Bit Binary Multiplying DACs from National SemiconductorDocument14 pages10-Bit and 12-Bit Binary Multiplying DACs from National SemiconductormicochangoNo ratings yet

- sc7001q Ay 961Document18 pagessc7001q Ay 961r2c1No ratings yet

- Advanced Motion Controls Dq111se25a20nacDocument7 pagesAdvanced Motion Controls Dq111se25a20nacElectromateNo ratings yet

- THAT2181CDocument10 pagesTHAT2181Cenzo_60No ratings yet

- Aic 1084-33PMDocument6 pagesAic 1084-33PMluismilenio3111No ratings yet

- Ta 8252 HDocument14 pagesTa 8252 HNiraj Suroopjeet0% (1)

- Digiflex® Digital Servo Drives With Canopen Interface MODEL: DC201E60A40NACDocument12 pagesDigiflex® Digital Servo Drives With Canopen Interface MODEL: DC201E60A40NACElectromateNo ratings yet

- AM5888SDocument10 pagesAM5888SproctepNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- 110 Waveform Generator Projects for the Home ConstructorFrom Everand110 Waveform Generator Projects for the Home ConstructorRating: 4 out of 5 stars4/5 (1)

- Audio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsFrom EverandAudio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- GnatusDocument36 pagesGnatusNacer Mezghiche100% (1)

- Safex - c2 - SchemaDocument1 pageSafex - c2 - SchemaNacer MezghicheNo ratings yet

- BRC 45 45 C ManualDocument6 pagesBRC 45 45 C ManualNacer MezghicheNo ratings yet

- PWM Speed Controller For Minidrill: 13 Dis 10 RST VCCDocument1 pagePWM Speed Controller For Minidrill: 13 Dis 10 RST VCCNacer Mezghiche100% (1)

- Infineon BTS6143D DS v01 00 enDocument18 pagesInfineon BTS6143D DS v01 00 enNacer MezghicheNo ratings yet

- S112 PDFDocument1 pageS112 PDFNacer MezghicheNo ratings yet

- F4P770, F4P771, F4P772, F5R700, F9q752/caregDocument1 pageF4P770, F4P771, F4P772, F5R700, F9q752/caregNacer MezghicheNo ratings yet

- Series 16VM ControlsDocument2 pagesSeries 16VM ControlsNacer MezghicheNo ratings yet

- Dossier BATERIES enDocument14 pagesDossier BATERIES enNacer Mezghiche100% (1)

- 01Document8 pages01Nacer MezghicheNo ratings yet

- USB Programátor Pro Atmel: +5V Vccint 1k 1k +5V +5V JP2 R2 R3Document1 pageUSB Programátor Pro Atmel: +5V Vccint 1k 1k +5V +5V JP2 R2 R3Nacer Mezghiche100% (1)

- vm-2120 Er Cb1eDocument4 pagesvm-2120 Er Cb1eNacer MezghicheNo ratings yet

- NTC Thermistors Technical Reference GuideDocument18 pagesNTC Thermistors Technical Reference GuideEdwin Alfredo Lopez AguirreNo ratings yet

- Toshiba 32av933n Ver. 1.00 150Document55 pagesToshiba 32av933n Ver. 1.00 150matwan29No ratings yet

- F5R700, K4m710/ess/careg/pbchDocument1 pageF5R700, K4m710/ess/careg/pbchNacer MezghicheNo ratings yet

- P 912 ADocument13 pagesP 912 ANacer MezghicheNo ratings yet

- Venas vm2120Document50 pagesVenas vm2120Nacer MezghicheNo ratings yet

- VM 2120Document60 pagesVM 2120Nacer MezghicheNo ratings yet

- P 912 ADocument13 pagesP 912 ANacer MezghicheNo ratings yet

- 001Document2 pages001Nacer Mezghiche50% (4)

- 002Document1 page002Nacer MezghicheNo ratings yet

- P 912 ADocument13 pagesP 912 ANacer MezghicheNo ratings yet

- NTC Thermistors Technical Reference GuideDocument18 pagesNTC Thermistors Technical Reference GuideEdwin Alfredo Lopez AguirreNo ratings yet

- Specification For ApprovalDocument6 pagesSpecification For ApprovalNacer MezghicheNo ratings yet

- IADC Classification Chart ExplainedDocument2 pagesIADC Classification Chart ExplainedNacer MezghicheNo ratings yet

- 50 555 Timer CircuitsDocument57 pages50 555 Timer Circuitsshahbaz_809No ratings yet

- Beckman Coulter Immage - Maintenance LogbookDocument4 pagesBeckman Coulter Immage - Maintenance LogbookNacer MezghicheNo ratings yet

- Blank Paper HouseDocument1 pageBlank Paper HousedadinotractoNo ratings yet

- O129647v - Mil BB500DXDocument64 pagesO129647v - Mil BB500DXNacer MezghicheNo ratings yet

- Stud Finder Final v1Document6 pagesStud Finder Final v1api-323825539No ratings yet

- MC059A - B Training ManualDocument26 pagesMC059A - B Training ManualfalchoniNo ratings yet

- Aquarian 1000 PlusDocument26 pagesAquarian 1000 Plussss12135No ratings yet

- WWW Jensign Com TransimpedanceampDocument12 pagesWWW Jensign Com TransimpedanceamprozehNo ratings yet

- Analog Audio Amplifier Design 1997Document12 pagesAnalog Audio Amplifier Design 1997pippopappo2000No ratings yet

- Module5 QuestionsDocument46 pagesModule5 Questionsdnes9999No ratings yet

- Electrical: ElectronicDocument100 pagesElectrical: ElectronicIver SanchezNo ratings yet

- AB32189Document2 pagesAB32189GUINo ratings yet

- CalculationsDocument15 pagesCalculationsnho_OsakaNo ratings yet

- 100 Top Operational Amplifiers Questions and Answers PDF Operational Amplifiers Questions and Answers 1 PDF FreeDocument12 pages100 Top Operational Amplifiers Questions and Answers PDF Operational Amplifiers Questions and Answers 1 PDF FreeJuan Carlos Chamalé Morales100% (1)

- CD Changer Manual - rv01Document59 pagesCD Changer Manual - rv01Sv KoNo ratings yet

- Electronics & Communication Engineering EDC Course OverviewDocument2 pagesElectronics & Communication Engineering EDC Course OverviewAli BaigNo ratings yet

- Pioneer - DEH-P3000R Multi-Cd PDFDocument68 pagesPioneer - DEH-P3000R Multi-Cd PDFaldoNo ratings yet

- Actuator LA25: User ManualDocument80 pagesActuator LA25: User Manualbrandon joel ferrer morenoNo ratings yet

- Laboratory 6 Basic Op Amp CircuitsDocument10 pagesLaboratory 6 Basic Op Amp CircuitsKamran AliNo ratings yet

- Analog-To-Digital Conversion Btech IIIDocument50 pagesAnalog-To-Digital Conversion Btech IIILisa BhagatNo ratings yet

- AD5933Document12 pagesAD5933Abubakar SidikNo ratings yet

- BLDC Motor Control Design in MATLAB/SimulinkDocument5 pagesBLDC Motor Control Design in MATLAB/SimulinkWilliam Javier Rosero VargasNo ratings yet

- Welcome To John Bedini S Web PagesDocument590 pagesWelcome To John Bedini S Web PagesKatamba Rogers100% (1)

- Some QuestionDocument7 pagesSome QuestionHasanNo ratings yet

- lm3524 PWM PDFDocument8 pageslm3524 PWM PDFIon MoldoveanuNo ratings yet

- Pulse Monitor - CMPT 340Document4 pagesPulse Monitor - CMPT 340Gilbert MiaoNo ratings yet

- Six-Port Interferometer For Direction-of-Arrival Detection SystemDocument4 pagesSix-Port Interferometer For Direction-of-Arrival Detection SystemWalter Santiago Campos ArandaNo ratings yet

- NORSOK Standard Technical Safety T 100Document51 pagesNORSOK Standard Technical Safety T 100Ho Ngoc Thanh QuangNo ratings yet

- Full Wave Rectifier Characteristics LabDocument36 pagesFull Wave Rectifier Characteristics LabTushar Kush100% (4)

- MINI PROJECT ON - "Op-Amp Based LDR Circuit": Nitte Meenakshi Institute of TechnologyDocument6 pagesMINI PROJECT ON - "Op-Amp Based LDR Circuit": Nitte Meenakshi Institute of TechnologyAntus Alok SahuNo ratings yet

- MCQS From CareerRide (Oscillators, Digital Circuits)Document10 pagesMCQS From CareerRide (Oscillators, Digital Circuits)Qaisar_mastNo ratings yet

- Mach Dien Tu Thong Tin Trinh Xuan Dung Chapter 4 RF Oscillators and Frequency Synthesizers (Cuuduongthancong - Com)Document55 pagesMach Dien Tu Thong Tin Trinh Xuan Dung Chapter 4 RF Oscillators and Frequency Synthesizers (Cuuduongthancong - Com)Vĩnh TônNo ratings yet

- Multi Stage AmplifiersDocument9 pagesMulti Stage AmplifiersMuhammed ThameemNo ratings yet

- Bipolar Transistor EvaluationDocument15 pagesBipolar Transistor Evaluationmark777markNo ratings yet