Professional Documents

Culture Documents

Device and Circuit Modeling Using Novel 3-State Quantum Dot Gate FETs PDF

Uploaded by

yashreyOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Device and Circuit Modeling Using Novel 3-State Quantum Dot Gate FETs PDF

Uploaded by

yashreyCopyright:

Available Formats

ISDRS 2007, December 12-14, 2007, College Park, MD, USA

Device and Circuit Modeling using Novel 3-State Quantum Dot Gate FETs

F. C. Jain, E. Heller*, S. Karmakar, and J. Chandy

Department of Electrical and Computer Engineering, University of Connecticut,

Storrs, CT 06269; * RSoft Design Group, Ossinings, NY 10562

Abstract: This paper presents simulation of three-state behavior recently reported in quantum dot

gate field-effect transistor (FET) structures. The model self-consistently solves Schrdinger and

Poisson equations with built-in transfer of carriers from the inversion channel to two layers of

cladded SiOx-Si quantum dots (QDs) forming the gate, predicting the intermediate state in the

transfer Id-Vg characteristic. Circuit model and simulations for a 3-bit ADC are also presented.

I. Introduction: Quantum dot (QD) gate memories have been fabricated in a number of ways

since the first reporting by Tiwari et al. [1]. During the fabrication of self-assembled quantum dot

gate nonvolatile memories, it was observed that certain FET structures exhibit a novel

intermediate state in the transfer (drain current Id-gate voltage Vg) as well as output (Id-Vd)

characteristics, not observed in conventional FETs. That is, the transfer characteristics show

three stable states ("0", "1" and "i"), where the low-current saturation state "i" is manifested over

a range of gate voltages which can be utilized for various circuit applications. These novel

bistable characteristics provide new versatility in designing multiple-valued logic [2] CMOS

circuits with significantly reduced FET counts as well as advanced analog circuit building blocks

such as comparators for designing analog-to-digital converters (ADCs).

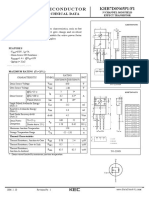

II. FET structure with two layers of SiOx-cladded Si quantum dots: Fig. 1(a) shows a typical

QD FET structure consisting of two layers of self-assembled SiOx-Si quantum dots between the

source and drain regions above the p-doped channel hosting the inversion electron channel [3].

Figure 1(b) shows the three energy band diagrams at different gate voltages and a plot of

inversion layer carrier concentration as a function of gate voltage. Note that the carriers are first

transferred to the second quantum dot layer near the gate (see Fig. 1b top right), and as the gate

voltage is further increased, the charge is located in the first quantum dot layer near the inversion

channel (see Fig. 1b bottom left). The tunneling transition rate from the channel to the

quantum dot layers is expressed by Hamiltonian in Eq.1 following Chuang et al. [4].

Pwd =

4

h

d Ht w

( f w f d ) ( Ed Ew )

(1)

w, d

Two layers of SiOx-coated Si quantum dots

Gate

Source Contact

Drain Contact

Field

Oxide

n+ Source

n+ Drain

L

p-Si

Gate Insultaor

(b)

ID

ON "High-Current

Saturation"

124

Drain

Current

Intermediate state "i"

(Low-Current Saturation)

0.84

-10

OFF

1.2 Volts/Div

VG

Gate Voltage

(a)

Fig. 1. (a) Cross-sectional schematic of a SiOx-Si quantum dot gate FET with transfer characteristics

shown in inset. (b) Simulated energy band diagrams and transfer (Id-Vg) characteristic.

ISDRS 2007 http://www.ece.umd.edu/ISDRS

978-1-4244-1892-3/07/$25.00 2007 IEEE

ISDRS 2007, December 12-14, 2007, College Park, MD, USA

In quantum dot gate FETs, the gate insulator charge is composed of discrete values as

expressed in Eq. 2 (the conventional interface charge Qox at SiOx-Si interface is not shown

as it does not relate to bistability). Thus, the threshold voltage increases in the gate voltage

range exhibiting the intermediate state i, keeping the drain current constant.

xg

x ( x )

q

dx =

xg

Cox

xQD1n1 N QD1

x nN

+ QD 2 2 QD 2 (2)

xg

xg

0

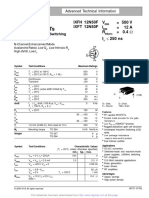

III. Circuit Model and 3-Bit ADC Simulation:

VFB = VTH

q

=

Cox

We have developed an empirical model for the QDFET that accounts for the intermediate

state i in the range of gate voltages (Vg1 and Vg2). The effective threshold voltage is

divided into three ranges corresponding to the three regions of the transfer characteristics

(see Fig. 1(a) bottom): region 1, intermediate state i, and the regular saturation part.

Using this model we have simulated a 3-bit ADC circuit in which the comparators are

comprised of a 3-state QDFET, an adjustable threshold QD gate FET, and a conventional

p-MOS. The ADC schematic is shown in Fig. 2(a) and the CADENCE simulation results

are shown in Fig. 2(b). The QDFET parameters are: L=600 nm and W=15 m with a

W/L ratio ~ 24. The crossover voltage range of the comparator can be increased by

adjusting the threshold voltage of the adjustable threshold QDFET.

A 3-bit flash ADC with Tri-state CMOS inverters replacing

Comparators and Reference resistors

(a)

(b)

CLK

Vin

QD CMOS Inverter

Vin

Over

Range

20

QDM

VTH-1

WL-1

VDD

N-MOS

VTH-1

21

QDM

VTH-2

P-MOS

Vout1

N digital

outputs

(1, i)

(1, i,

0)

WL-2

N-MOS

P-MOS VDD

NAND

Gate 1

(2N-1)

to N

encoder

Vout2

2n

QDM

VTH-3

WL-3

VDD

N-MOS

Vout3

P-MOS

(to NAND

gate)

Priortity Encoder (PE)

Fig. 2. Cadence simulation of 3-bit ADC: (a) Circuit block diagram with comparator comprised of

3-state QDFET and adjustable threshold QD FET, and a p-MOS ; and (b). ADC output waveform.

This work is supported by ONR Contracts N00014-02-1-0883 and N00014-06-1-0016, and NSFGrant ECS 0622068. Discussions with Dr. D. Purdy (ONR) and Dr. R. Khosla (NSF), and

technical assistance in processing by Dr. R. Velampati and Dr. A. Rodriguez are gratefully

acknowledged.

[1] S. Tiwari, F. Rana, K. Chan, H, Hanafi, W. Chan and D. Buchanan, Volatile and non-volatile

memories in silicon with nano-crystal storage, IEDM, pp. 521-525, Dec. 1995.

[2] T. Hanyu, M. Kameyama, A 200 MHz pipelined multiplier using 1.5 V-supply multiple valued MOS

current-mode circuits with dual-rail source-coupled logic, IEEE Journal of Solid-State Circuits vol. 30,

no. 11, (1995).

[3] F. Jain, R. Velampati, A. Rodriguez, E. Heller, E-S. Hasaneen, J. Chandy, B. I. Miller, F.

Papadimitrakopoulos, Quantum dot gate 3-state field-effect transistors and nonvolatile memory devices for

millimeter wave circuits, Int. J. Millimeter Waves and Infrared (submitted).

[4] S. Chuang, N. Holonyak, Efficient quantum well to quantum dot tunneling: Analytical

solutions, Appl. Phys. Lett., 2002; 80: 1270-1272.

ISDRS 2007 http://www.ece.umd.edu/ISDRS

You might also like

- BSIM4 Gate Leakage Model Including Source-Drain PartitionDocument4 pagesBSIM4 Gate Leakage Model Including Source-Drain PartitionalokjadhavNo ratings yet

- Gate Tunneling Current and Quantum Effects in Deep Scaled MosfetsDocument5 pagesGate Tunneling Current and Quantum Effects in Deep Scaled Mosfetsashishj1083No ratings yet

- EC3058D-VLSI Circuits and Systems Winter Semester-2020-21Document2 pagesEC3058D-VLSI Circuits and Systems Winter Semester-2020-21Gamer AnonymousNo ratings yet

- Single Electron Transistor (SET)Document8 pagesSingle Electron Transistor (SET)mokhaladNo ratings yet

- Stage 2 CapDocument4 pagesStage 2 Capnivia25No ratings yet

- Chapter 8Document43 pagesChapter 8CarolineNo ratings yet

- Lecture - MOS & MOSFET-1Document21 pagesLecture - MOS & MOSFET-1Kartika MunirNo ratings yet

- JFET transistor guideDocument17 pagesJFET transistor guideChen Chee JungNo ratings yet

- Low-Voltage CMOS Analog Bootstrapped Switch For Sample-and-Hold Circuit: Design and Chip CharacterizationDocument4 pagesLow-Voltage CMOS Analog Bootstrapped Switch For Sample-and-Hold Circuit: Design and Chip CharacterizationwhamcNo ratings yet

- Power Quality Enhancement Using VSC Based DSTATCOMDocument6 pagesPower Quality Enhancement Using VSC Based DSTATCOMSunil KumarNo ratings yet

- High Speed, Low Power Current Comparators With Hysteresis: Neeraj K. ChastaDocument12 pagesHigh Speed, Low Power Current Comparators With Hysteresis: Neeraj K. ChastanengsintanovitaNo ratings yet

- Advance Vlsi Devices and Technology Project ReportDocument14 pagesAdvance Vlsi Devices and Technology Project ReportDileep MalgireddyNo ratings yet

- IR-drop Reduction Through Combinational Circuit PartitioningDocument12 pagesIR-drop Reduction Through Combinational Circuit PartitioningPramod Reddy RNo ratings yet

- Mosfet Lab 1Document11 pagesMosfet Lab 1Pramod SnkrNo ratings yet

- (IMPRESO) A Low-Power ACDC Rectifier For Passive UHF RFID PDFDocument6 pages(IMPRESO) A Low-Power ACDC Rectifier For Passive UHF RFID PDFHaresh SinghNo ratings yet

- Logic Gates: Power and Other Logic FamilyDocument36 pagesLogic Gates: Power and Other Logic FamilybhawnaNo ratings yet

- Dual Gate BucketDocument8 pagesDual Gate BucketVigneswaran VigneshNo ratings yet

- Ch. 5 Lecture Slides For Chenming Hu Book: Modern Semiconductor Devices For ICsDocument42 pagesCh. 5 Lecture Slides For Chenming Hu Book: Modern Semiconductor Devices For ICsChenming HuNo ratings yet

- UEC750Document2 pagesUEC750Shivam SharmaNo ratings yet

- Impact of MOSFET parameters on parasitic capacitancesDocument5 pagesImpact of MOSFET parameters on parasitic capacitancesNava KrishnanNo ratings yet

- Single Electron Transistors With Sidewall Depletion Gates On A Silicon-On-Insulator Quantum WireDocument2 pagesSingle Electron Transistors With Sidewall Depletion Gates On A Silicon-On-Insulator Quantum Wire9semNo ratings yet

- I, and I, and Zref Separately We Measured Changes of AboutDocument5 pagesI, and I, and Zref Separately We Measured Changes of AboutBodhayan PrasadNo ratings yet

- Design and Implementation of 2 Bit Loaded Line Phase ShifterDocument5 pagesDesign and Implementation of 2 Bit Loaded Line Phase ShifterdhvbkhnNo ratings yet

- Hyuga SimulationDocument8 pagesHyuga SimulationJimmy MachariaNo ratings yet

- CMOS Modeling 1Document20 pagesCMOS Modeling 1telguardNo ratings yet

- GATE EC Topicwise Questions on Electronics Devices 2011-2009Document27 pagesGATE EC Topicwise Questions on Electronics Devices 2011-2009Waseem AkramNo ratings yet

- CMOS Translinear CellsDocument4 pagesCMOS Translinear CellsSumitChoudharyNo ratings yet

- Cntfet Technology Based Precision Full-Wave Rectifier Using DDCCDocument8 pagesCntfet Technology Based Precision Full-Wave Rectifier Using DDCCresearchinventyNo ratings yet

- Quantum-Mechanical Modeling and Simulation of A Novel Nano-Scale FET: Center-Channel (CC) Double-Gate (DG) MOSFETDocument6 pagesQuantum-Mechanical Modeling and Simulation of A Novel Nano-Scale FET: Center-Channel (CC) Double-Gate (DG) MOSFETanchit_virmaniNo ratings yet

- A Tutorial: Subcircuit and Verilog-A RF Circuit Simulation Models For Axial and Surface Mounted ResistorsDocument17 pagesA Tutorial: Subcircuit and Verilog-A RF Circuit Simulation Models For Axial and Surface Mounted Resistorsiarcad9403No ratings yet

- Bilotti 1966Document3 pagesBilotti 1966dycsteiznNo ratings yet

- Prework Questions For KI-1Document5 pagesPrework Questions For KI-1Danial SadiqNo ratings yet

- Slimming World, Jun 2011Document5 pagesSlimming World, Jun 2011emediageNo ratings yet

- Mathematical Driving Model of Three Phase, Two Level Inverter by (Method of Interconnected Subsystem)Document10 pagesMathematical Driving Model of Three Phase, Two Level Inverter by (Method of Interconnected Subsystem)Shashi KumarNo ratings yet

- CMOS Inverter Delay and Power Estimation for RC LoadsDocument4 pagesCMOS Inverter Delay and Power Estimation for RC LoadsTarun PrasadNo ratings yet

- CH02 Logic Design With MOSFETsDocument41 pagesCH02 Logic Design With MOSFETsMohamedNo ratings yet

- M B - P V C S G (CSG) Mosfet: Odeling of Uilt IN Otential Ariations OF Ylindrical Urrounding ATE SDocument11 pagesM B - P V C S G (CSG) Mosfet: Odeling of Uilt IN Otential Ariations OF Ylindrical Urrounding ATE SAnonymous e4UpOQEPNo ratings yet

- Single Electron Based Binary Multipliers With Overflow DetectionDocument13 pagesSingle Electron Based Binary Multipliers With Overflow Detectionprabhjot singh1No ratings yet

- DCID Experiment MergedDocument94 pagesDCID Experiment MergedSumer SainiNo ratings yet

- ABCD Matrix-A Unique Tool For Linear Two-Wire Transmission Line ModellingDocument10 pagesABCD Matrix-A Unique Tool For Linear Two-Wire Transmission Line Modellingstudent_ujjwol3163No ratings yet

- Coupling-Driven Signal Encoding Scheme For Low-Power Interface DesignDocument4 pagesCoupling-Driven Signal Encoding Scheme For Low-Power Interface DesignshastryNo ratings yet

- Low Power and High Speed D-Latch Circuit Designs Based On Carbon Nanotube FETDocument5 pagesLow Power and High Speed D-Latch Circuit Designs Based On Carbon Nanotube FETKanaga VaratharajanNo ratings yet

- EVL562 ECL523 Digital IC Design Dec2020Document3 pagesEVL562 ECL523 Digital IC Design Dec2020akash rawatNo ratings yet

- Vlsi Design - Ec - 701 - Unit - 2Document18 pagesVlsi Design - Ec - 701 - Unit - 2angelcrystl4774No ratings yet

- A Linear Programming Based Static Power Optimization Scheme For Digital CMOS Circuits AMSC 662 - Project ProposalDocument3 pagesA Linear Programming Based Static Power Optimization Scheme For Digital CMOS Circuits AMSC 662 - Project ProposalSatish Babu BodakuntaNo ratings yet

- N e W Method Bias CMOS Cascode Amplifiers: V. Vig IiDocument3 pagesN e W Method Bias CMOS Cascode Amplifiers: V. Vig IiBodhayan PrasadNo ratings yet

- Vlsi Mod3 QnADocument24 pagesVlsi Mod3 QnAsri krishnaNo ratings yet

- Vlsi Final Notes Unit4Document21 pagesVlsi Final Notes Unit4RohitParjapatNo ratings yet

- Nanocrystal Embedded MOS Non Volatile Memory Devices: Prof. C. K. SarkarDocument40 pagesNanocrystal Embedded MOS Non Volatile Memory Devices: Prof. C. K. SarkarS.R.SriramNo ratings yet

- Examples: Telegrapher's Equation: Rev 28 Jan 2013Document5 pagesExamples: Telegrapher's Equation: Rev 28 Jan 2013Muhammad RamzyNo ratings yet

- FrereDocument4 pagesFrereShufan ChanNo ratings yet

- Analysis of Diode Clamped 3-Level Inverter in 2-Stage Solar PV SystemDocument6 pagesAnalysis of Diode Clamped 3-Level Inverter in 2-Stage Solar PV SystemRinku SatapathyNo ratings yet

- Design and Implementation of Hybrid CMOS-SET Half Adder and Full Adder CircuitsDocument9 pagesDesign and Implementation of Hybrid CMOS-SET Half Adder and Full Adder CircuitsInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Predictive Optimal Control Neutral Multilevel Converters: PointDocument6 pagesPredictive Optimal Control Neutral Multilevel Converters: PointChikha SaidNo ratings yet

- Steady State Analysis of PID Controlled Boost Converter using State Space Averaging TechniqueDocument11 pagesSteady State Analysis of PID Controlled Boost Converter using State Space Averaging TechniqueSumiNo ratings yet

- MOS Theory, SPICE, CMOS Fabrication LectureDocument70 pagesMOS Theory, SPICE, CMOS Fabrication LecturePrayat Anil HegdeNo ratings yet

- Organic Light-Emitting Transistors: Towards the Next Generation Display TechnologyFrom EverandOrganic Light-Emitting Transistors: Towards the Next Generation Display TechnologyNo ratings yet

- MOS Integrated Circuit DesignFrom EverandMOS Integrated Circuit DesignE. WolfendaleNo ratings yet

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysNo ratings yet

- Hydrodynamic and Molecular Dynamics Modeling of Laser Ablation in Liquid: From Surface Melting Till Bubble FormationDocument24 pagesHydrodynamic and Molecular Dynamics Modeling of Laser Ablation in Liquid: From Surface Melting Till Bubble FormationyashreyNo ratings yet

- Nanoantenna Enhanced Terahertz Interaction of BiomoleculesDocument25 pagesNanoantenna Enhanced Terahertz Interaction of BiomoleculesyashreyNo ratings yet

- Polarized Resonant Emission of Monolayer WS Coupled With Plasmonic Sawtooth Nanoslit ArrayDocument9 pagesPolarized Resonant Emission of Monolayer WS Coupled With Plasmonic Sawtooth Nanoslit ArrayyashreyNo ratings yet

- Mwa - Exp 3Document7 pagesMwa - Exp 3yashreyNo ratings yet

- Nanoantenna Enhanced Terahertz Interaction of BiomoleculesDocument25 pagesNanoantenna Enhanced Terahertz Interaction of BiomoleculesyashreyNo ratings yet

- Question 1: Feedback - Week 3: QuizDocument3 pagesQuestion 1: Feedback - Week 3: QuizyashreyNo ratings yet

- Graphene Based Field Effect Transistors Efforts Made Towards Flexible PDFDocument12 pagesGraphene Based Field Effect Transistors Efforts Made Towards Flexible PDFyashreyNo ratings yet

- Electron Beam Lithography Designed Silver Nanodisks Used As Label Free Nano-Biosensors Based On Localized Surface Plasmon Resonance PDFDocument11 pagesElectron Beam Lithography Designed Silver Nanodisks Used As Label Free Nano-Biosensors Based On Localized Surface Plasmon Resonance PDFyashreyNo ratings yet

- A Single-Atom Transistor PDFDocument5 pagesA Single-Atom Transistor PDFyashreyNo ratings yet

- 1504 03112v1Document10 pages1504 03112v1GenNo ratings yet

- Design of ADCs and DACs Using 3-State Quantum DOT Gate FETsDocument2 pagesDesign of ADCs and DACs Using 3-State Quantum DOT Gate FETsyashreyNo ratings yet

- A Two-Qubit Logic Gate in SiliconDocument11 pagesA Two-Qubit Logic Gate in SiliconyashreyNo ratings yet

- A Two-Qubit Logic Gate in SiliconDocument11 pagesA Two-Qubit Logic Gate in SiliconyashreyNo ratings yet

- CMOS Mixed Signal Circuit Design by Jacob BakerDocument180 pagesCMOS Mixed Signal Circuit Design by Jacob BakerSharath Sogi0% (1)

- Marking Codes Small Signal Transistors and DiodesDocument40 pagesMarking Codes Small Signal Transistors and DiodesSlimane SlimaneNo ratings yet

- NTE36 & NTE37 Silicon Complementary Transistors GuideDocument2 pagesNTE36 & NTE37 Silicon Complementary Transistors GuideHarold Bedoya ValenciaNo ratings yet

- Verilog-A Implementation of SOI MOSFET-Based Amplifier and RingDocument9 pagesVerilog-A Implementation of SOI MOSFET-Based Amplifier and RingAdib ShadmanNo ratings yet

- Semiconductor KHB7D0N65P1/F1: Technical DataDocument7 pagesSemiconductor KHB7D0N65P1/F1: Technical DataDaniel DominguezNo ratings yet

- Chapter Wise QuestionsDocument2 pagesChapter Wise QuestionshjjhghgNo ratings yet

- Apt56f60b2 - Mosfet - Modelo 8Document5 pagesApt56f60b2 - Mosfet - Modelo 8Teneré Frutas e verdurasNo ratings yet

- MOSFET Operation ExplainedDocument25 pagesMOSFET Operation ExplainedRaja Nusum100% (1)

- Memory Devices, Circuits, and Subsystem DesignDocument38 pagesMemory Devices, Circuits, and Subsystem Designلطيف احمد حسنNo ratings yet

- Cap 6 Modificado PDFDocument84 pagesCap 6 Modificado PDFMilton EspinozaNo ratings yet

- Common-Base ConfigurationDocument10 pagesCommon-Base ConfigurationRakin Mohammad SifullahNo ratings yet

- Unit - 1 Power Electronics-1 PDFDocument92 pagesUnit - 1 Power Electronics-1 PDFramudureddyNo ratings yet

- ECE 321 Prelim Exam Multiple ChoiceDocument3 pagesECE 321 Prelim Exam Multiple ChoiceLoryliza M DeiparineNo ratings yet

- CH 06Document45 pagesCH 06박병준No ratings yet

- B.E. Degree Examination Analog Electric CircuitsDocument10 pagesB.E. Degree Examination Analog Electric CircuitsAPURV ANANDNo ratings yet

- Diac CharacteristicsDocument2 pagesDiac CharacteristicsElla Mae Dela CruzNo ratings yet

- Complementary Silicon Power Transistors: BD533/5/7 BD534/6/8Document4 pagesComplementary Silicon Power Transistors: BD533/5/7 BD534/6/8vali2daduicaNo ratings yet

- Lab-2: V-I Characteristics of NMOS and PMOSDocument18 pagesLab-2: V-I Characteristics of NMOS and PMOSDarsh GuptaNo ratings yet

- BJT Familiarization and CharacteristicDocument12 pagesBJT Familiarization and CharacteristicCyville AvenirNo ratings yet

- C 3198Document1 pageC 3198Kunal Kundanam100% (1)

- Isc 2SC4834: Silicon NPN Power TransistorsDocument3 pagesIsc 2SC4834: Silicon NPN Power TransistorsErwin Rolando EscobarNo ratings yet

- Mosfet: Prepared By: Gagandeep KaurDocument16 pagesMosfet: Prepared By: Gagandeep KaurGAGANNo ratings yet

- Balaji Conference PaperDocument6 pagesBalaji Conference Paperbalajibs203285No ratings yet

- EEEB273 N06 - Diff Amp FET x6Document7 pagesEEEB273 N06 - Diff Amp FET x6Juan Esteban Hernandez AlvarezNo ratings yet

- CyogenicsDocument5 pagesCyogenicsRooban SNo ratings yet

- 549287614.docx Multi-Function Tester (TC-V2.12k)Document14 pages549287614.docx Multi-Function Tester (TC-V2.12k)JoseLuisRuizNo ratings yet

- Module6 - PVT VariationDocument17 pagesModule6 - PVT Variationdilshan singhNo ratings yet

- Compact Modeling of Semiconductor Devices: MOSFET ModelingDocument82 pagesCompact Modeling of Semiconductor Devices: MOSFET ModelingAshwani JhaNo ratings yet

- SCRDocument30 pagesSCRRaghav Gupta100% (2)

- Hiperrf Power Mosfets: Ixfh 12N50F Ixft 12N50FDocument2 pagesHiperrf Power Mosfets: Ixfh 12N50F Ixft 12N50FdtramirNo ratings yet

- Silicon NPN Darlington Power Transistors: DescriptionDocument3 pagesSilicon NPN Darlington Power Transistors: DescriptionVictor HemzNo ratings yet