Professional Documents

Culture Documents

Max458 Max459

Uploaded by

giapy0000Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Max458 Max459

Uploaded by

giapy0000Copyright:

Available Formats

Not Recommended for New Designs

This product was manufactured for Maxim by an outside wafer foundry

using a process that is no longer available. It is not recommended for

new designs. The data sheet remains available for existing users.

A Maxim replacement or an industry second-source may be available.

Please see the QuickView data sheet for this part or contact technical

support for assistance.

For further information, contact Maxims Applications Tech Support.

19-0258; Rev 3; 8/99

L

MANUA

ION KIT HEET

T

A

U

L

EVA

TA S

WS DA

FOLLO

8x4 Video Crosspoint Switches with Buffers

_____________________Block Diagram

8 BUFFERED

8x4

4 75

INPUTS

SWITCH ARRAY OUTPUT DRIVERS

TEMP. RANGE

0C to +70C

40 Plastic DIP

MAX458CQH

MAX458EPL

MAX459CPL

0C to +70C

-40C to +85C

0C to +70C

44 PLCC

40 Plastic DIP

40 Plastic DIP

MAX459CQH

MAX459EPL

0C to +70C

-40C to +85C

44 PLCC

40 Plastic DIP

PIN-PACKAGE

_________________Pin Configurations

GND

GND

N.C.

DIN

CS

IN0

MAX459

N.C.

TOP VIEW

5

44 43 42 41 40

CE

Video Test Equipment

Video Security Systems

Video Editing

PART

MAX458CPL

WR

________________________Applications

______________Ordering Information

UPDATE

Data interface can be accomplished by either a 16-bit

serial or a 6-bit parallel connection. In the serial mode,

the MAX458/MAX459 are SPITM, QSPITM, and MicrowireTM

compatible. In parallel mode, the MAX458/MAX459 are

compatible with most microprocessor buses. Three-state

amplifier output capability makes it possible to multiplex

MAX458/MAX459s to form larger switch networks. The

output buffers can be disabled individually or the entire

device can be shut down to conserve power.

100MHz Unity-Gain Bandwidth

300V/s Slew Rate

Low 0.05 Differential Phase Error

Low 0.01% Differential Gain Error

Directly Drives 75 Cables

Fast 60ns Switching Time

High-Z Amplifier Output Capability

Shutdown Capability

16-Bit Serial and 6-Bit Parallel Address Modes

40-Pin DIP and 44-Pin PLCC Packages

SCLK

The MAX458/MAX459 are crosspoint switches with eight

input channels and four high-speed, buffered output

channels. The MAX458 output buffer is configured with a

gain of one, while the MAX459 buffer has a gain of two. In

each device, any one of eight input lines can be connected to any of four output amplifiers. The output buffers are

capable of driving loads of 75.

____________________________Features

IN0

75

GND

GND

75

IN6

75

AV = 2

75

GND

GND

IN7

75

OUT3

GND

SERIAL OR PARALLEL

DIGITAL INTERFACE

& CONTROL

SERIAL/PARALLEL INTERFACE

(SPI, QSPI, MICROWIRE COMPATIBLE)

37 GND

GND

10

36 OUT1

IN3

11

VCC

12

IN4

13

33 VEE

VEE

14

32 N.C.

IN5

15

31 OUT3

GND

16

30 GND

IN6

17

29 A0

35 VCC

MAX458

MAX459

34 OUT2

18

19 20 21 22 23 24 25 26 27 28

DIP on last page.

A1

AV = 2

GND

IN5

75

OUT2

D0

75

38 OUT0

IN2

D1

GND

39 GND

D2

75

GND

IN4

75

OUT1

N.C.

75

75

AV = 2

IN1

GND

D3

IN3

GND

DOUT

GND

8x4

SWITCH

ARRAY

SHDN

75

75

GND

IN2

OUT0

GND

75

AV = 2

75

IN7

GND

GND

75

IN1

PLCC

SPI and QSPI are trademarks of Motorola, Inc. Microwire is a trademark of National Semiconductor Corp.

_______________________________________________________________ Maxim Integrated Products

For free samples and the latest literature, visit www.maxim-ic.com or phone 1-800-998-8800.

For small orders, phone 1-800-835-8769.

MAX458/MAX459

_______________General Description

MAX458/MAX459

8x4 Video Crosspoint Switches with Buffers

ABSOLUTE MAXIMUM RATINGS

Operating Temperature Ranges

MAX45_C_ _ ........................................................0C to +70C

MAX45_E_ _......................................................-40C to +85C

Junction Temperature ......................................................+150C

Storage Temperature Range .............................-65C to +160C

Lead Temperature (soldering, 10sec) .............................+300C

Total Supply Voltage (VCC to VEE) .........................................12V

Positive Supply Voltage (VCC to GND).....................................6V

Negative Supply Voltage (VEE to GND) ...................................6V

Analog Input/Output Voltage ...........(VCC + 0.3V) to (VEE - 0.3V)

Digital Input Voltage ...................................(VCC + 0.3V) to -0.3V

Duration of Output Short Circuit to GND (Note 1) ......Continuous

Continuous Power Dissipation

Plastic DIP (derate 17mW/C above +70C) ..............1333mW

PLCC (derate 13mW/C above +70C) ......................1067mW

Note 1: Outputs may be shorted to any supply pin or ground as long as package power dissipation ratings are not exceeded.

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

ELECTRICAL CHARACTERISTICS

(VCC = +5V, VEE = -5V, -2V VIN +2V, output load resistor (RL) = 150, TA = TMIN to TMAX, unless otherwise noted.

Typical values are at TA = +25C.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

+2

STATIC SPECIFICATIONS

Input Voltage Range

Input Offset Voltage

-2

VOS

Any channel

Input Offset Voltage Match

VOS

VIN = 0V (Note 2)

Power-Supply Rejection Ratio

PSRR

VS = 4.75V to 5.25V

On Input Bias Current

On Input Resistance

RIN

Input programmed to one output

Input Capacitance

CIN

Input channel on or off

MAX459 (Note 4)

Output Voltage Swing

1

0.50

TA = +25C

ROUT

Disabled Output Capacitance

COUT

Positive Power-Supply Current

ICC

VIN = 0V,

all amplifiers enabled

Negative Power-Supply Current

IEE

VIN = 0V,

all amplifiers enabled

0.5

0.1

1.0

0.25

0.70

TA = +25C

TA = TMIN to TMAX

TA = +25C

TA = TMIN to TMAX

2.0

2

Disabled Output Resistance

A

pF

0.1

TA = TMIN to TMAX

mV

1.0

TA = +25C

mV

dB

5

5.0

TA = TMIN to TMAX

VIN = 1kHz sine wave

VIN = 10MHz sine wave

MAX458

MAX459

ROUT

10

60

VOUT

Enabled Output Resistance

15

20

50

VIN = 0V, input programmed to one output

MAX458 (Note 3)

TA = TMIN to TMAX

IIN

DC Voltage Gain Accuracy

TA = +25C

60

50

50

40

3

0.05

4.0

1.0

1.0

12

75

65

M

k

pF

85

100

75

90

mA

mA

Positive Supply Current in

Shutdown

15

26

mA

Negative Supply Current in

Shutdown

12

mA

2.0

Logic Input High Voltage

VIH

(Note 5)

Logic Input Low Voltage

VIL

(Note 5)

0.8

_______________________________________________________________________________________

8x4 Video Crosspoint Switches with Buffers

(VCC = +5V, VEE = -5V, -2V VIN +2V, output load resistor (RL) = 150, TA = TMIN to TMAX, unless otherwise noted.

Typical values are at TA = +25C.)

MAX

UNITS

Logic Input High Current

PARAMETER

SYMBOL

IIH

(Note 3)

CONDITIONS

10

Logic Input Low Current

IIL

(Note 3)

10

Logic Output High Voltage

VOH

ISOURCE = 400A (Note 5)

Logic Output Low Voltage

VOL

ISINK = 700A (Note 5)

MIN

TYP

4.0

V

0.5

DYNAMIC SPECIFICATIONS

Differential Gain Error (Note 6)

DG

Differential Phase Error (Note 6)

DG

MAX458

0.01

MAX459

0.13

MAX458

0.05

MAX459

0.14

MAX458

Slew Rate

SR

MAX459

Positive transition

200

Negative transition

150

Positive transition

300

Negative transition

250

MAX458, RL = 75

100

MAX459, RL = 150

90

%

degrees

V/s

Bandwidth (-3dB)

BW

MHz

Input Noise Density

en

f = 10kHz

20

nV/Hz

Settling Time

tS

To 0.1% of final value (Note 7)

40

ns

Amplifier Disable Time

tAOFF

100

ns

Amplifier Enable Time

tAON

120

ns

Channel Switching Time

tCSW

60

ns

Channel Switching Propagation Delay

tCPD

50

ns

Switching Transient Glitch

See Typical Operating Characteristics

100

mVp-p

Adjacent Channel Crosstalk

(Note 8)

-65

dB

Non-Adjacent Channel Crosstalk

(Note 9)

-65

dB

All-Hostile Crosstalk

(Note 10)

-55

dB

All-Hostile Off Isolation

(Note 11)

-60

dB

Note 2: Defined as the DC offset shift when switching between input channels for a given output.

Note 3: Voltage Gain Accuracy for MAX458 calculated as (VOUT - VIN) @ (VIN = +2V) - (VOUT - VIN) @ (VIN = -2V)

4V

Note 4: Voltage Gain Accuracy for MAX459 calculated as (VOUT/2 - VIN) @ (VIN = +1V) - (VOUT/2 - VIN) @ (VIN = -1V)

2V

Note 5: All logic levels are guaranteed over the range of VS = 4.75V to 5.25V.

Note 6: Differential phase and gain measured with a 40 IRE (285.7mV), 3.58MHz sine wave superimposed on a linear ramp of 0 IRE

to 100 IRE (714.3mV). The IRE scale is a linear scale for measuring, in arbitrary IRE units, the relative amplitudes of the various components of a television signal (from the Television Engineering Handbook, edited by K. Blair Benson, McGraw

Hill). This system defines 100 IRE as reference white, 0 IRE as the blanking level, and -40 IRE as the sync peak. The equipment used for the test signal generated 714.3mV (100 IRE) as reference white and -285.7mV (-40 IRE) as sync. The modulation used was 285.7mV (40 IRE), which conforms to the EIA color signal standards.

Note 7: For MAX458, step input from +2V to 0V; for MAX459, step input from +1V to 0V. All unused channels grounded and all

unused amplifiers disabled.

Note 8: Test input channel programmed to an output and grounded through a 75 resistor. Adjacent input is programmed to an

adjacent output and driven by a 10MHz, 4Vp-p sine wave.

Note 9: Same as Note 6 above, except driven input and output are not adjacent to test input/output.

Note 10: All inputs but the test input are driven by a 10MHz 4Vp-p sine wave. All outputs except the test output are connected to driven inputs.

Note 11: Same as Note 9 above, except with test channel programmed off.

_______________________________________________________________________________________

MAX458/MAX459

ELECTRICAL CHARACTERISTICS (continued)

MAX458/MAX459

8x4 Video Crosspoint Switches with Buffers

TIMING CHARACTERISTICS (Note 12)

(VCC = +5V, VEE = -5V, -2V VIN +2V, output load resistor (RL) = 150, TA = TMIN to TMAX, unless otherwise noted.)

PARAMETER

SYMBOL

PARALLEL-MODE TIMING (see Figure 1)

Address to WR Fall Setup Time

tADS

Address to WR Rise Hold Time

tADH

CE Fall to WR Fall Setup Time

tCES

CE Rise to WR Rise Hold Time

tCEH

WR Pulse Width Low

tWR

Data to WR Rise Setup Time

tDS

Data to WR Rise Hold Time

tDH

WR Rise to UPDATE Fall Setup Time

tWRS

UPDATE Pulse Width Low

tUP

UPDATE Rise to WR Fall Setup Time

tUPS

CONDITIONS

MIN

MAX

UNITS

20

ns

ns

ns

ns

40

ns

50

ns

ns

ns

40

ns

25

ns

SERIAL-MODE TIMING (see Figure 6)

SCLK to CS Fall

CS Fall to SCLK Rise

tCSO

ns

tCSS

35

ns

SCLK Pulse Width High

tCH

50

ns

SCLK Pulse Width Low

tCL

30

ns

DIN to SCLK Rise Setup Time

tDS

50

ns

DIN to SCLK Rise Hold Time

tDH

SCLK Fall to DOUT

SCLK Rise to CS Rise

CS Rise to SCLK Rise

CS Pulse Width High

tDO

tCSH

ns

30

ns

tCS1

20

ns

tCSW

100

ns

Note 12: Timing Characteristics are guaranteed by design.

ns

200

_______________________________________________________________________________________

8x4 Video Crosspoint Switches with Buffers

MAX458

GAIN vs. FREQUENCY

-4

0

PHASE

-6

36

72

40

20

0.1

20 40 60 80 100 120 140

10

MAX458/459 Fg TOC6

10

D1

IN5

IN2

20mV/div

(analog)

IN2

+200mV

-200mV

100ns/div

100

MAX459

SMALL-SIGNAL PULSE RESPONSE

INPUT MAX458/459 Fg TOC8

INPUT

UPDATE

MAX458/459 Fg TOC3

100

+200mV

-200mV

+100mV

OUTPUT

OUTPUT

180

100 250

0.1

5V

25ns/div

10

CHANNEL SWITCH TRANSIENT

MAX458

SMALL-SIGNAL PULSE RESPONSE

-15V

FREQUENCY (MHz)

OUT

MAX458

LARGE-SIGNAL PULSE RESPONSE

1V/div

0.1

GND

FREQUENCY (MHz)

GND

144

D0 & D2

FREQUENCY (MHz)

2V/div

108

144

MAX458/459 Fg TOC9

0.1

72

108

180

100 250

10

36

INPUT

-120

OUTPUT IMPEDANCE ()

MAX458/459 Fg TOC7

-80

MAX458/459 Fg TOC2

AMPLITUDE (dB)

-40

0.01

0

PHASE

OUTPUT IMPEDANCE vs. FREQUENCY

CROSSTALK vs. FREQUENCY

10

FREQUENCY (MHz)

TEMPERATURE (C)

40

-100mV

10ns/div

+200mV

OUTPUT

-60 -40 -20 0

PHASE (DEGREES)

60

0

-2

GAIN

6

PHASE (DEGREES)

IEE

GAIN

MAX458/459 Fg TOC5

10V/div

(digital)

AMPLITUDE (dB)

80

MAX458/459 Fg TOC4

ICC

CURRENT (mA)

MAX458/459 Fg TOC1

100

MAX459

GAIN vs. FREQUENCY

AMPLITUDE (dB)

POWER SUPPLY CURRENT

vs. TEMPERATURE

-200mV

10ns/div

_______________________________________________________________________________________

MAX458/MAX459

__________________________________________Typical Operating Characteristics

(TA = +25C, unless otherwise noted.)

MAX458/MAX459

8x4 Video Crosspoint Switches with Buffers

______________________________________________________________Pin Description

PIN

NAME

FUNCTION

DIP

PLCC

DIN

2, 4, 6, 8,

14, 16, 18,

27, 33, 35

3, 5, 8, 10,

16, 18, 20,

30, 37, 39

GND

IN0

Analog Input Channel 0

IN1

Analog Input Channel 1

IN2

Analog Input Channel 2

11

IN3

Analog Input Channel 3

10, 31

12, 35

VCC

Positive Power Supply (+5V). Connect both VCC pins to the positive supply.

Serial Data Input

Ground

11

13

IN4

Analog Input Channel 4

12, 29

14, 33

VEE

Negative Power Supply (-5V). Connect both VEE pins to the negative supply.

13

15

IN5

Analog Input Channel 5

15

17

IN6

Analog Input Channel 6

17

19

IN7

Analog Input Channel 7

19

21

SHDN

Shutdown, active high. Connect to GND if not used.

20

22

DOUT

Serial Data Output used for daisy-chaining devices.

21

23

D3

Parallel Digital Channel Input Address Bit 3

22

25

D2

Parallel Digital Channel Input Address Bit 2

23

26

D1

Parallel Digital Channel Input Address Bit 1

24

27

D0

Parallel Digital Channel Input Address Bit 0

25

28

A1

Parallel Digital Amplifier Output Address Bit 1

26

29

A0

Parallel Digital Amplifier Output Address Bit 0

28

31

OUT3

Amplifier 3 Analog Output

30

34

OUT2

Amplifier 2 Analog Output

32

36

OUT1

Amplifier 1 Analog Output

34

38

Amplifier 0 Analog Output

36

40

37

41

38

42

OUT0

CE

WR

UPDATE

39

43

40

44

SCLK

CS

2, 6, 24, 32

N.C.

Chip Enable, used in parallel mode. Keep high for serial operation.

Write Low, latches input registers in parallel mode. Hold high for serial operation.

Update Low, latches amplifier registers in parallel mode. Hold high for serial operation.

Serial Clock

Not Internally Connected

Chip Select, used in serial operation. Hold high for parallel mode of operation.

Note: All GND pins must be grounded for optimum crosstalk performance.

_______________________________________________________________________________________

8x4 Video Crosspoint Switches with Buffers

MAX458/MAX459

2

3

IN0

75

4

5

IN1

75

MAX458

MAX459

IN2

75

8

35

IN3

75

34

OUT0

75

75

0.1F

10

11

VCC

IN4

OUT0

ENABLE

33

75

0.1F

12

VEE

13

IN5

14

DOUT

39

15

IN6

DIN

20

75

40

75

CS

19

16

SERIAL INTERFACE

SCLK

SHDN

17

IN7

75

18

IN0

32

OUT1

75

IN7

OUT1

ENABLE

IN0

75

31

30

IN7

0.1F

VCC

OUT2

75

75

OUT2

ENABLE

IN0

29

28

IN7

OUT

ENABLE 4

24

D0

23

D1

PIN NUMBERS APPLY TO DIP PACKAGE.

22

D2

21

D3

OUT3

ENABLE

26

0.1F

OUT3

75

VEE

75

27

38

37

36

25

A0 A1

CE

WR UPDATE

PARALLEL INTERFACE

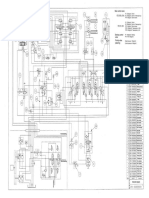

Figure 1. Block Diagram and Typical Operating Circuit

_______________________________________________________________________________________

MAX458/MAX459

8x4 Video Crosspoint Switches with Buffers

ANALOG INPUTS

IN0

IN7

UPDATE

WR

INPUT

REGISTER

1

SWITCH

REGISTER

1

CONTROL

CE

OUT0

8-1 MUX

SWITCH

REGISTER

2

CONTROL

INPUT

REGISTER

2

8-1 MUX

OUT1

A0

A1

SWITCH

REGISTER

3

CONTROL

INPUT

REGISTER

3

8-1 MUX

OUT2

SWITCH

REGISTER

4

CONTROL

D0

D1

D2

D3

INPUT

REGISTER

4

MAX458

MAX459

8-1 MUX

L = TRANSPARENT

H = LATCHED

CS = HIGH, SCLK = DIN = LOW

Figure 2. Parallel-Logic Block Diagram

8

_______________________________________________________________________________________

OUT3

8x4 Video Crosspoint Switches with Buffers

Analog Section

The MAX458/MAX459 video crosspoint switches consist

of a high-speed 32 (8x4) switch array with wide-bandwidth line drivers (Figure 1). This design allows makebefore-break switching to reduce output noise and

glitches, but the inputs will not short together. It also provides high input impedance and low input capacitance,

so no input buffer amplifier is needed. However,

because different transistors provide gain depending on

the input selection, the DC offset voltage shifts slightly

when a new input is switched in. The change in offset

voltage is typically 3mV.

All output buffers will drive back-terminated 50, 75,

or higher impedance lines with up to 100pF capacitance. The amplifier outputs can be disabled, which is

useful for creating large arrays. When disabled, the

MAX458 presents an output impedance of approximately 1M. The MAX459 disabled output impedance

is 1k (to ground), due to the internal feedback resistors used to achieve the gain of two.

During power-on, if CS and UPDATE are held high, all

output amplifiers are disabled. In a large array, this

feature prevents two ON paralleled amplifiers from distorting each others signals. The amplifiers can be programmed to come up in any state simultaneously at any

time after power-on. See the Creating Large Arrays

section.

DIN

CS

SCLK

UPDATE

MAX458

MAX459

SHUTDOWN

19

20

A1

A0

Output Amplifier Selected

H

H

L

H

2

3

Table 2. Input Selection

D2

D1

D0

Input Channel Selected

40 V

CC

39

38

UPDATE

CE

A0

26

D0

AMPLIFIER SELECT A0

25 AMPLIFIER SELECT A1

24 DATA BIT D0

D1

23 DATA BIT D1

SHDN

D2

22 DATA BIT D2

DOUT

D3

21

A1

Table 1. Amplifier Selection

D3

37 WRITE

36

CHIP ENABLE (SELECT)

WR

Digital SectionParallel Mode

The MAX458/MAX459 have two register banksan

input register and a switch register (Figure 2). Each of

these registers is either latched (when the control input

is high) or transparent (when the control

input

is low).

The input register is controlled by WR and CE

and

is

selected

by

the

decode

of

A0

and

A1.

If

both

W

R

and

CE are low, the input register selected by A0 and A1 is

transparent, and the state of D0D3 is presented to the

switch register. The other three input registers remain

latched. If D0D3 change before UPDATE is asserted

(goes low), the new data (the changed

D0D3)

will then

be latched in the switch register. If WR or CE is high, all

input registers are latched and their data is presented

DATA BIT D3

Pin numbers apply to DIP package.

Figure 3. Parallel Connection (only logic pins shown)

7

Disable output amplifier

selected by A0, A1.

Table 3. Writing Data

FUNCTION

CE WR UPDATE

H

X

H

Device not selected or is operating in seriX

H

H

al mode. Both registers are latched.

Data in input registers passes through

H

X

L

switch registers. Output reflects data in

X

H

L

input registers.

Input register of selected amplifier is transparent. Switch registers are latched. Other

L

L

H

input registers are latched.

All switch registers and selected input register are transparent. Selected amplifier (choL

L

L

sen by state of A0, A1) reflects input data.

Other amplifiers reflect data that had been

latched into the input registers previously.

_______________________________________________________________________________________

MAX458/MAX459

_______________Detailed Description

MAX458/MAX459

8x4 Video Crosspoint Switches with Buffers

to their switch registers. As long as either WR or CE is

high, the input register will not change. The switch register

will

pass any new data on the falling transition of

UPDATE.

Each register of the switch-register

bank

controls the

inputs to one amplifier. With UPDATE low, the switch

registers are transparent and switch connection

conis

trolled by the input register. However, if UPDATE is

high, the switch register is latched and any change in

data by the input register will not affect the amplifier

output state. Two register banks are used so that data

can be loaded into input registers without affecting the

switch/amplifier selection. This allows amplifiers to be

programmed and then changed simultaneously. When

the registers are not latched, they are made transparent.

Use data bit D3 to disable the amplifier selected by

A0A1 and place its output in high-impedance mode.

As an example, the code to disable OUT0 is as follows:

Pin Name: D3 D2 D1 D0 A1 A0

Input Code: 1 X X X 0 0

When operating in parallel mode, CS must be wired high

and SCLK and DIN should be grounded, as shown in

Figure 3. Refer to Figure 4 for the correct timing relationships.

A0/A1

Digital SectionSerial Mode

The MAX458/MAX459 use a three-wire serial interface

that is compatible with SPI, QPSI and Microwire interfaces.Serial

shown

mode,

in Figure 5, is enabled

when WR, UPDATE, and CE are held high and CS goes

low. Figures 6 and 7 show serial-mode timing. Figure 8

shows the MAX458/MAX459 configured for serial operation. Figure 9 shows the Microwire connection, and

Figure 10 shows the SPI/QSPI connection.

The serial output, DOUT, allows cascading of two or

more crosspoint switches to create larger arrays. The

data at DOUT is delayed by 16 cycles plus one clock

pulse width

at DIN. DOUT changes

on SCLKs falling

edge when CS is low. When CS is high, DOUT remains

in the state of the last data bit.

The MAX458/MAX459 input data in 16-bit blocks. SPI

and Microwire interfaces output data in 8-bit blocks,

thereby requiring two write cycles to input data. The

QSPI interface allows variable word lengths from 8 to 16

bits and can be loaded into the crosspoint in one write

cycle. SPI and Microwire limit clock rates to 2MHz, while

the QSPI maximum clock rate is 4MHz.

ADDRESS VALID

tADS

tADH

CE

tCES

tCEH

tWR

WR

tDS

D0D3

tDH

tUPS

DATA VALID

tWRS

UPDATE

tUP

Figure 4. Parallel-Mode Timing

10

______________________________________________________________________________________

8x4 Video Crosspoint Switches with Buffers

IN7

ONE

SHOT

ANALOG INPUTS

IN

0

SWITCH

REGISTER

0

CLK

CONTROL INPUT

CS

MAX458/MAX459

IN0

DIN

8-1 MUX

OUT0

D

Q

16-BIT

SHIFT

REGISTER

SWITCH

REGISTER

1

SCLK

8-1 MUX

OUT1

MAX458

MAX459

0

SWITCH

REGISTER

2

8-1 MUX

OUT2

Q

D

OUT

0

SWITCH

REGISTER

3

8-1 MUX

OUT3

DOUT

L = TRANSPARENT

H = LATCHED

WR = CE = UPDATE = HIGH

Figure 5. Serial-Mode Logic Block Diagram

______________________________________________________________________________________

11

MAX458/MAX459

8x4 Video Crosspoint Switches with Buffers

tCSW

tCSH

CS

tCSS

tCS0

tCH

tCS1

tCL

SCLK

tDH

tDS

DIN

D0

D3 (OUT3)

D2 (OUT3)

tD0

D1 (OUT0)

D0 (OUT0)

DOUT

D3

DATA FROM PREVIOUS WRITE CYCLE

D2

D1

D0

D3

Figure 6. Serial-Mode Timing

CS

SCLK

DIN

D3

D2

D1

D0

D3

D2

OUT3

D1

D0

D3

D2

OUT2

D1

D0

D3

D2

OUT1

D1

D0

D1

D0

OUT0

DOUT

D3

D2

D1

D0

D3

DATA FROM PREVIOUS WRITE CYCLE

D2

D1

D0

D3

D2

D1

D0

D3

D2

Figure 7. Serial-Mode Data Sequence

SERIAL

DATA IN

DIN

CS

SERIAL

CLOCK

UPDATE

38

VCC

WR

37

VCC

CE

36

VCC

A0

26

A1

25

D0

19

SERIAL

DATA OUT

20

CHIP SELECT

39

SCLK

MAX458

MAX459

40

MAX458

MAX459

SCLK

SK

DIN

SO

CS

I/O

DOUT

MICROWIRE

PORT

SI

24

D1

23

SHDN

D2

22

DOUT

D3

21

THE DOUT-SI CONNECTION IS NOT REQUIRED FOR

WRITING TO THE MAX458/MAX459, BUT MAY BE USED

FOR DATA-ECHO PURPOSES.

Pin numbers apply to DIP package.

Figure 8. Serial Connection (only logic pins shown)

12

Figure 9. Microwire Connection

______________________________________________________________________________________

D3

8x4 Video Crosspoint Switches with Buffers

MAX458/MAX459

IN_

SCK

DIN

MOSI

CS

I/O

DOUT

SPI/QSPI

PORT

RETURN

CURRENT

MOSO

IN_

CPOL = 0, CPHA = 0

THE DOUT-MOSO CONNECTION IS NOT REQUIRED FOR

WRITING TO THE MAX458/MAX459, BUT MAY BE USED

FOR DATA-ECHO PURPOSES.

Figure 10. SPI/QSPI Connection

__________Applications Information

Grounding and Bypassing,

PC Board Layout

As with all analog circuits, good PC board layout, proper grounding, and careful component selection are crucial for realizing the full AC performance of high-speed

amplifiers such as the MAX458/MAX459. For optimal

performance:

1) Use a large, low-impedance analog ground plane.

With multilayer boards, the ground plane(s) should

be located on the layer that does not contain signal

traces. Connect all GND pins to the analog ground

plane.

2) Minimize trace area at the circuits critical high-impedance nodes to prevent unwanted signal coupling.

Surround analog inputs with an AC ground trace

(bypassed DC power supply, etc.). The analog input

pins of the MAX458/MAX459 have been separated

with AC ground pins (GND, VCC, VEE) to minimize

parasitic coupling, which can degrade crosstalk.

3) Connect the coaxial-cable shield to the ground side

of the 75 terminating resistor at the ground plane

to further reduce crosstalk (Figure 11).

4) Bypass all power-supply pins directly to the ground

plane with 0.1F ceramic capacitors placed as

close to the supply pins as possible. For high-current loads, you may need 10F tantalum or aluminum-electrolytic capacitors in parallel with the

0.1F ceramics. Keep capacitor lead lengths as

short as possible to minimize series inductance; surface-mount chip capacitors are ideal.

GROUND PLANE

MAX458

MAX459

SCLK

RETURN

CURRENT

Figure 11. Low-Crosstalk Layout. Return current from termination resistor does not flow through the ground plane.

Creating Larger Arrays

The MAX458/MAX459 assume a high-impedance state

on power-up if the inputs are not being programmed to

any particular state during that time. They also are in a

high-impedance state when disabled. This feature

makes it possible to create larger arrays than 8x4 without special programming, other than ensuring that your

program doesnt turn on two paralleled outputs simultaneously. Testing has shown no degradation of differential gain or phase when the outputs are connected in

parallel.

The MAX458/MAX459s input registers remain active during shutdown, which allows the crosspoint to be programmed while the devices are shut down. As a result, all

outputs may be simultaneously brought to any state,

including disabled. Just program all of the MAX458/

MAX459s into shutdown, and enter the program of your

choice by selecting the desired inputs and outputs. Taking

SHDN low takes the device(s) out of shutdown.

A power-on reset circuit causes the output amplifiers to

power up in the

disabled

whether or not SHDN

mode,

is applied, if UPDATE and CS are high.

The number of MAX458s that can be paralleled is limited by capacitive loading on each output, which must

not exceed 100pF. Each input presents approximately

7pF of load, and each output presents approximately

12pF. Therefore, the MAX458/MAX459 will drive a maximum of 14 inputs, or 7 outputs and 2 inputs, or any

other combination resulting in less than a 100pF load.

Adding isolation resistors enables more MAX458s to be

paralleled (see the Driving Capacitive Loads section).

______________________________________________________________________________________

13

MAX458/MAX459

8x4 Video Crosspoint Switches with Buffers

Driving Capacitive Loads

When driving loads greater than 100pF, you may need

a capacitance compensating resistor in series with the

output of each affected amplifier. The required resistor

will depend on load as well as capacitance. For 150

or higher load resistances and capacitance up to

1000pF, use a 2.4 resistor. For 100 loads, use a

4.7 resistor.

If an output amplifier is loaded with a pure capacitance

or with the inputs of other MAX458/MAX459s, the resistors will cause no degradation of gain or other performance because of the high impedance of the

crosspoints. However, resistive loads may cause a

reduction in gain.

Daisy-Chaining Devices

The serial output, DOUT, allows cascading of two or

more crosspoint switches to create larger arrays. The

data at DOUT is the DIN data delayed by 16 cycles

plus one clock

on SCLKs falling

width. DOUT changes

edge when CS is low. When CS is high, DOUT remains

in the state of the last data bit.

Any number of MAX458/MAX459 crosspoint switches

can be daisy-chained by connecting the DOUT of one

device to the DIN of the next device in the chain, as

shown

in Figure 12. For proper timing, ensure that both

tCSS (CS low to SCLK high) and tCL are greater than

tDO + tDS.

DOUT is a TTL-compatible output with an active pull

up. It does not become high impedance when CS is

high.

CS

SCLK

SERIAL

DATA

INPUT

DOUT

DIN

40

MAX458

39

MAX459

28

OUT3

30

OUT2

32

OUT1

20

34

OUT0

40

MAX458 39

MAX459

28

30

32

DOUT

20

34

Figure 12. 16x4 Crosspoint Switch Using Serial "Daisy Chain"

Connection

14

______________________________________________________________________________________

8x4 Video Crosspoint Switches with Buffers

MAX458/MAX459

____Pin Configurations (continued)

TOP VIEW

DIN 1

40 CS

GND 2

39 SCLK

IN0 3

GND 4

IN1 5

38 UPDATE

MAX458

MAX459

37 WR

36 CE

GND 6

35 GND

IN2 7

34 OUT0

GND 8

33 GND

IN3 9

32 OUT1

V CC 10

31 V CC

IN4 11

30 OUT2

V EE 12

29 V EE

IN5 13

28 OUT3

GND 14

27 GND

IN6 15

26 A0

GND 16

25 A1

IN7 17

24 D0

GND 18

23 D1

SHDN 19

22 D2

DOUT 20

21 D3

DIP

______________________________________________________________________________________

15

MAX458/MAX459

8x4 Video Crosspoint Switches with Buffers

________________________________________________________Package Information

DIM

A

A1

A2

A3

B

B1

C

D

D1

E

E1

e

eA

eB

L

D1

E

A2

A3

E1

INCHES

MAX

MIN

0.200

0.015

0.175

0.125

0.080

0.055

0.020

0.016

0.065

0.045

0.012

0.008

2.075

2.025

0.090

0.050

0.625

0.600

0.575

0.525

0.100 BSC

0.600 BSC

0.700

0.150

0.120

15

0

MILLIMETERS

MIN

MAX

5.08

0.38

3.18

4.45

1.40

2.03

0.41

0.51

1.14

1.65

0.20

0.30

51.44

52.71

1.27

2.29

15.24

15.88

13.34

14.61

2.54 BSC

15.24 BSC

17.78

3.05

3.81

0

15

21-348A

A1

e

L

40-PIN PLASTIC

DUAL-IN-LINE

PACKAGE

eA

B1

eB

DIM

A2

C

D1 D

B1

D2

B

A

A1

A2

A3

B

B1

C

D

D1

D2

D3

e

INCHES

MAX

MIN

0.180

0.165

0.110

0.100

0.156

0.145

0.020

0.021

0.013

0.032

0.026

0.011

0.009

0.695

0.685

0.655

0.650

0.630

0.590

0.500 REF

0.050 REF

MILLIMETERS

MIN

MAX

4.19

4.57

2.54

2.79

3.68

3.96

0.51

0.33

0.53

0.66

0.81

0.23

0.28

17.40

17.65

16.51

16.64

14.99

16.00

12.70 REF

1.27 REF

21-350A

A3

D3

D1

D

16

A1

A

44-PIN PLASTIC

LEADED CHIP

CARRIER

PACKAGE

______________________________________________________________________________________

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- CAT Programming ManualDocument258 pagesCAT Programming ManualDuy Kha95% (108)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Fuel D13Document12 pagesFuel D13Eduardo Pai Tocarlo90% (40)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Speeduino Manual PDFDocument58 pagesSpeeduino Manual PDFgiapy0000No ratings yet

- MCP 2551Document24 pagesMCP 2551senguttuvelNo ratings yet

- Bosch System Basis Chip Cy329 Product SummaryDocument6 pagesBosch System Basis Chip Cy329 Product SummaryPijai TDMNo ratings yet

- Pinout Denso Hyundai Megatruck2010Document1 pagePinout Denso Hyundai Megatruck2010giapy0000No ratings yet

- PLC Overview 4104euen0802Document40 pagesPLC Overview 4104euen0802Jeevan JyotiNo ratings yet

- 25 MR-100 Hyd-DiagDocument1 page25 MR-100 Hyd-Diaggiapy0000No ratings yet

- VOLVO 7748542 US Installation EMS 2 D13 PDFDocument62 pagesVOLVO 7748542 US Installation EMS 2 D13 PDFSIVARAMANJAGANATHANNo ratings yet

- Electric Diagram For SR-250 Upper1Document1 pageElectric Diagram For SR-250 Upper1giapy0000No ratings yet

- User'S Manual: PIC-P26J50 Proto Development BoardDocument19 pagesUser'S Manual: PIC-P26J50 Proto Development Boardgiapy0000100% (1)

- Preamp PDFDocument1 pagePreamp PDFgiapy0000No ratings yet

- L Series: Engineered To SaveDocument8 pagesL Series: Engineered To Savegiapy0000No ratings yet

- Manualegcp2 26174 BDocument234 pagesManualegcp2 26174 BINGRgomezNo ratings yet

- Ic 900 PDFDocument100 pagesIc 900 PDFShubra DebNo ratings yet

- 6068hf 485 Manual-EngineDocument160 pages6068hf 485 Manual-Enginegiapy0000No ratings yet

- Pic 14000Document153 pagesPic 14000MarkoStankovicNo ratings yet

- Manual Pic 18F2550Document430 pagesManual Pic 18F2550Pancho NuncioNo ratings yet

- Speeduino Manual PDFDocument58 pagesSpeeduino Manual PDFgiapy0000No ratings yet

- Manual de Partes Del Motor Cat c9Document127 pagesManual de Partes Del Motor Cat c9jalb80% (5)

- Product Manual 04176 (Revision G, 8/2015) : Proact™ Ii Electric Powered Actuator and DriverDocument33 pagesProduct Manual 04176 (Revision G, 8/2015) : Proact™ Ii Electric Powered Actuator and DriverpayNo ratings yet

- Gold Capacitors: Electric Double Layer CapacitorsDocument28 pagesGold Capacitors: Electric Double Layer Capacitorsgiapy0000No ratings yet

- R"i 1 - F'y" Uo: LB II IftDocument2 pagesR"i 1 - F'y" Uo: LB II Iftgiapy0000No ratings yet

- Release Sd2 EngDocument12 pagesRelease Sd2 Enggiapy0000No ratings yet

- 275kw Diesel Generator Datasheet J275u (English)Document4 pages275kw Diesel Generator Datasheet J275u (English)giapy0000No ratings yet

- Koler Power Systems 20 - 2000kW - Operation - Manual PDFDocument80 pagesKoler Power Systems 20 - 2000kW - Operation - Manual PDFTấn Dũng BùiNo ratings yet

- m0698 - Power Mode Bypass Controller To Suit Komatsu Hd785-5 and Hd785-7 VehiclesDocument16 pagesm0698 - Power Mode Bypass Controller To Suit Komatsu Hd785-5 and Hd785-7 Vehiclesgiapy0000No ratings yet

- VHP750 XHP750WCAT零件手册Document66 pagesVHP750 XHP750WCAT零件手册giapy000050% (2)

- Active Filter-1 PDFDocument7 pagesActive Filter-1 PDFammerNo ratings yet

- ECG ProjectDocument34 pagesECG Projectsamsai888No ratings yet

- AN521 Microchip Interfacing To AC Power LinesDocument4 pagesAN521 Microchip Interfacing To AC Power LinesLEONO_MAXNo ratings yet

- Easy Add-On Projects For Spectrum Zx81 and AceDocument189 pagesEasy Add-On Projects For Spectrum Zx81 and AceArkinuxNo ratings yet

- DC Motor Drive Using GTO Based DC-DC ConverterDocument20 pagesDC Motor Drive Using GTO Based DC-DC ConverterMridul MishraNo ratings yet

- Efficient Resonantly Enhanced Mach-Zehnder Optical Modulators On Lithium NiobateDocument185 pagesEfficient Resonantly Enhanced Mach-Zehnder Optical Modulators On Lithium NiobateDr-Mandeep SinghNo ratings yet

- Computer and Interfacing Chapter Six Pin and Clock GeneratorDocument78 pagesComputer and Interfacing Chapter Six Pin and Clock GeneratormigadNo ratings yet

- CN0251 Analog AD7192Document6 pagesCN0251 Analog AD7192Said AhnicheNo ratings yet

- Ads 1256Document43 pagesAds 1256yaser2005100% (2)

- Ch.7 Data AcquisitionDocument9 pagesCh.7 Data AcquisitionaattishNo ratings yet

- AD694Document12 pagesAD694Asghar AliNo ratings yet

- Kim 2012Document7 pagesKim 2012smartp499No ratings yet

- Lecture 3 Single Stage AmplifiersDocument76 pagesLecture 3 Single Stage Amplifierstranhieu_hcmutNo ratings yet

- A Low Phase Noise Tri-Band LO Generation For Ku and E Band Radios For Backhauling Point-to-Point ApplicationsDocument4 pagesA Low Phase Noise Tri-Band LO Generation For Ku and E Band Radios For Backhauling Point-to-Point ApplicationsrinsonNo ratings yet

- AnalogPrecisionMeasurements DOC 95011Document19 pagesAnalogPrecisionMeasurements DOC 95011upali01No ratings yet

- 6.302 Feedback SystemsDocument6 pages6.302 Feedback Systemsinalcanzable20004289No ratings yet

- Arb 704Document11 pagesArb 704JustTimNo ratings yet

- Quint-Ups/ 1ac/ 1ac/500vaDocument34 pagesQuint-Ups/ 1ac/ 1ac/500vaAndrei GroperNo ratings yet

- A Peak Hold Energy Readout Circuit For Use With Pyroelectric Laser Energy MonitorsDocument3 pagesA Peak Hold Energy Readout Circuit For Use With Pyroelectric Laser Energy Monitorspasargad135106No ratings yet

- Isppac 10: Features Functional Block DiagramDocument23 pagesIsppac 10: Features Functional Block DiagramFaiber CalderonNo ratings yet

- Design and Analysis of Flipped Voltage Follower FollowerDocument5 pagesDesign and Analysis of Flipped Voltage Follower FollowerMadhur GuptaNo ratings yet

- Op Amp Precision Design-DC ErrorsDocument14 pagesOp Amp Precision Design-DC ErrorsSougata DasNo ratings yet

- PH Sensor ReportDocument7 pagesPH Sensor ReportRajasekar PanneerselvamNo ratings yet

- Elliott Sound Products: 24 dB/Octave 2/3-Way Linkwitz-Riley Electronic CrossoverDocument9 pagesElliott Sound Products: 24 dB/Octave 2/3-Way Linkwitz-Riley Electronic CrossoverPramudya Ksatria BudimanNo ratings yet

- Precision Rectifier CircuitsDocument13 pagesPrecision Rectifier CircuitsWaqas PervaizNo ratings yet

- Read Only Contactless Identification Device: em MicroelectronicDocument7 pagesRead Only Contactless Identification Device: em MicroelectronicAntonio PereiraNo ratings yet

- EXP4Document9 pagesEXP4Rohan__MakwanaNo ratings yet

- Analog Verilog, Verilog-A TutorialDocument26 pagesAnalog Verilog, Verilog-A Tutorialbhokal_bhokalNo ratings yet

- Analysis and Suppression of SSN Noise Coupling Between Power Ground Plane Cavities Through Cutouts in Multilayer Packages and PCBs PDFDocument12 pagesAnalysis and Suppression of SSN Noise Coupling Between Power Ground Plane Cavities Through Cutouts in Multilayer Packages and PCBs PDFApikShafieeNo ratings yet

- Hardwarex: Andrew P. Hill, Peter Prince, Jake L. Snaddon, C. Patrick Doncaster, Alex RogersDocument19 pagesHardwarex: Andrew P. Hill, Peter Prince, Jake L. Snaddon, C. Patrick Doncaster, Alex RogersAlicia GordonNo ratings yet