Professional Documents

Culture Documents

Fibonacci Codes For Crosstalk Avoidance: Sireesha Kondapalli, Dr. Giri Babu Kande

Uploaded by

Pronadeep BoraOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Fibonacci Codes For Crosstalk Avoidance: Sireesha Kondapalli, Dr. Giri Babu Kande

Uploaded by

Pronadeep BoraCopyright:

Available Formats

IOSR Journal of Electronics and Communication Engineering (IOSR-JECE)

e-ISSN: 2278-2834,p- ISSN: 2278-8735.Volume 8, Issue 3 (Nov. - Dec. 2013), PP 09-15

www.iosrjournals.org

Fibonacci Codes for Crosstalk Avoidance

1

Sireesha Kondapalli, 2Dr. Giri Babu Kande

PG Student (M.Tech VLSI), Dept. Of ECE, Vasireddy Venkatadri Ins. Tech., Nambur, Guntur, AP, India

2

Professor & Head, Dept. Of ECE, Vasireddy Venkatadri Ins. Tech., Nambur, Guntur, AP, India

Abstract: In the deep sub micrometer CMOS process technology, the interconnect resistance, length, and interwire capacitance are increasing significantly, which contribute to large on-chip interconnect propagation

delay. Data transmitted over interconnect determine the propagation delay and the delay is very significant

when adjacent wires are transitioning in opposite directions (i.e., crosstalk transitions) as compared to

transitioning in the same direction. Propagation delay across long on-chip buses is significant when adjacent

wires are transitioning in opposite direction (i.e., crosstalk transitions) as compared to transitioning in the same

direction. By exploiting Fibonacci number system, we propose a family of Fibonacci coding techniques for

crosstalk avoidance, relate them to some of the existing crosstalk avoidance techniques, and show how the

encoding logic of one technique can be modified to generate code words of the other technique.

Keywords: On-chip bus, crosstalk, Fibonacci coding.

I.

Introduction

The advancement of very large scale integration (VLSI) technologies has been following Moores law

for the past several decades: the number of transistors on an integrated circuit is doubling every two years and

the channel length is scaling at the rate of 0.7/3 years. It was not long ago when VLSI design marched into the

realm of Deep Submicron (DSM) processes, where the minimum feature size is well below 1 m. These

advanced processes enable designers to implement faster, bigger and more complex designs. With the increase

in complexity, System on Chip (SoC), Network on Chip (NoC) and Chip-level Multiprocessing (CMP) based

products are now readily available commercially.

Some major challenges in DSM technologies include design productivity, manufacturability, power

consumption, dissipation and interconnect delay. High design cost and long turn-around time are often caused

by the growth in design complexity. A high design complexity results from a growth in transistor count and

speed, demand for increasing functionality, low cost requirements, short time-to market and the increasing

integration of embedded analog circuits and memories. Poor manufacturability is often a direct result of

reduction in feature size. As the feature size gets smaller, the design becomes very sensitive to process variation,

which greatly affects yield, reliability and testability. To address these issues, new design flows and

methodologies are implemented to improve the efficiency of the designs. IC foundries are adding more design

rules to improve the design robustness. For many high densities, a high speed DSM design, power consumption

is a major concern. Increasing transistor counts, chip speed, and greater device leakage are driving up both

dynamic and static power consumption.

In the meanwhile, however, DSM technologies also present new challenges to designers on many

different fronts such as (i) scale and complexity of design, verification and test; (ii) circuit modeling and (iii)

processing and manufacturability. Innovative approaches are needed at both the system level and the chip level

to address these challenges and mitigate the negative effects they bring.

II.

On-Chip Crosstalk Avoidance

Capacitive crosstalk has become a major determinant of the total power consumption and delay of onchip busses. Figure.1 illustrates a simplified on-chip bus model with crosstalk. In the figure, CL denotes the load

capacitance, which includes the receiver gate capacitance and also the parasitic wire-to-substrate parasitic

capacitance. CI is the inter-wire coupling capacitance between adjacent signal lines of the bus. In practice, this

bus structure is typically modeled as a distributed RC network, which includes the non-zero resistance of the

wire as well It has been shown that for DSM processes, CI is much greater than CL [61]. Based on the energy

consumption and delay models given in the bus energy consumption can be derived as a function of the total

crosstalk over the entire bus. The worst case delay, which determines the maximum speed of the bus, is limited

by the maximum crosstalk that any wire in the bus incurs. It has been shown that reducing the crosstalk boosts

the bus performance significantly different approaches have been proposed for crosstalk reduction in the context

of bus interconnects. Some schemes focus on reducing the energy consumption, some focus on minimizing the

delay and other schemes address both.

www.iosrjournals.org

9 | Page

Fibonacci Codes for Crosstalk Avoidance

Figure 1 simplified on-chip bus model with crosstalk

The simplest approach to address the inter-wire crosstalk problem is to shield each signal using

grounded conductors. Khatri et al. in [1, 2] proposed a layout fabric that alternatively inserts one ground wire

and one power wire between every signal wire, i.e., the wires are laid out as . . . VSGSVSGSVS . . . , where S

denotes a signal wire, G denotes a ground wire and V denotes a power wire. Any signal wire has a static (V or

G) wire on each side, and hence, when it switches, it needs to charge a capacitance of value of 2CI .

Figure 2 A Fabric Based Design

This fabric also enforces a design rule that metal wires on a given layer run perpendicular to wires on

layers above or below. The fabric has the advantage of improved predictability in parasitic capacitance and

inductance. It automatically provides a low resistance power and ground network as well. Such a fabric results

in a decrease in wiring density. Even though the fabric appears to require a large area overhead, experimental

results show that on average, the circuit size grows by only 3% if the circuit is implemented as a network of

medium-sized programmable logic arrays (PLAs). In theworst case, however, the circuit size can be more than

200%of the conventional layout. Figure 2 illustrates such a fabric-based design. Khatri et al. [1] also provides

discussions on wire removal in networks of Programmable Logic Arrays (PLA)

Crosstalk avoidance bus encoding techniques manipulate the input data before transmitting them on the

bus. Bus encoding can eliminate certain undesirable data patterns and thereby reduce or eliminate crosstalk, with

much lower area overhead than the aforementioned straightforward shielding techniques [36, 88, 90, 99, 100].

These types of codes are referred to as crosstalk avoidance codes (CACs) or self shielding codes. Depends on

their memory requirements, CACs can be further divided into two categories: memory less codes and memorybased codes. Memory based coding approaches generate a codeword based on the previously transmitted code

and the current data word to be transmitted [34, 100]. On the receiver side, data is recovered based on the

received code words from the current and previous cycles. The memory less coding approaches use a fixed code

book to generate code words to transmit. The codeword is solely dependent on the input data. The decoder in the

receiver uses the current received codeword as the only input in order to recover the data.

Among all the memory less CACs proposed, two types of codes have been heavily studied. The first is

called forbidden pattern free (FPF) code and the second type of code has the property that between any two

adjacent wires in the bus, there will be no transition in opposite directions in the same clock cycle. Different

names have been used in the literatures for the second type of codes. In this paper, we refer these codes as

forbidden transition free (FTF) CACs. Both FPF-CACs and FTF-CACs yield the same degree of delay reduction

as passive shielding while requiring much less area overhead. Theoretically, the FPF-CAC has slightly better

overhead performance that the FTF-CAC. In practice, for large size bus, this difference is negligible.

III.

Fibonacci Binary Numeral System

A numeral system is a framework where numbers are represented by numerals in a consistent

manner [5]. The most commonly used numeral system in digital design is the binary numeral system, which

uses powers of two as the basis. For a number v, its binary representation is defined in Eq. 1. The binary

numeral system is complete and unambiguous, which means that each number has one and only one

representation in the binary numeral system.

www.iosrjournals.org

10 | Page

Fibonacci Codes for Crosstalk Avoidance

Equation 1

The Fibonacci-based numeral system N(Fm, {0, 1}) is the numeral system that uses Fibonacci

sequence as the basis. The definition of the Fibonacci sequence [3] is given in Eq. 2. A number v is represented

as the summation of some Fibonacci numbers, and no Fibonacci number is in the summation more that once, as

indicated in Eq. 2.

Equation 2

Similar to the binary numeral system, the Fibonacci-based numeral system is complete, and therefore

any number v can be represented in this system. However, the Fibonacci-based numeral system is ambiguous.

As an example, there are six 7-digit vectors in the Fibonacci numeral system for the decimal number 19:

{0111101, 0111110, 1001101, 1001110, 1010001, 1010010}. For clarity, we refer to a vector in the binary

numeral system as a binary vector or binary code; a vector in the Fibonacci numeral system is referred to as a

Fibonacci vector or Fibonacci code. All the Fibonacci vectors that represent the same value are defined as

equivalent vectors.

The n-bit binary vector can represent numbers in the range of [0, 2n1], and therefore a total of 2n

values can be represented by n-bit binary vectors. we know that the range of an m-bit Fibonacci vector is [0,

fm+21], where the minimum value 0 corresponds to all the bits dk being 0, and the maximum value

corresponds to all dk being 1. Hence a total of fm+2 distinct values can be represented by m-bit Fibonacci

vectors.

We first propose a coding scheme that converts the input data to a forbidden pattern free Fibonacci

vector. The code is near-optimal since the required overhead is no more than 1 additional bit, compared to the

theoretical lower bound given The coding algorithm is developed based on a result that states that any number v

can be represented in FNS, in an FPF manner. In order to prove this result, we first derive the following

corollaries:

The following twom-bitFibonacci vectors are equivalent: dmdm1 d301 and dmdm1 d310. In

other words, dmdm1 d301 dmdm1 d310.

Proof Since f2 = f1 = 1, it is obvious that the last two digits are interchangeable

Figure 3 CPF encoding algorithm

www.iosrjournals.org

11 | Page

Fibonacci Codes for Crosstalk Avoidance

Fig Nff encoding algorithm

Fig CRF encoding process

Figure. 3 show that an m-bit FPF vector is generated in m stages. Each stage outputs one bit of the

output vector (dk ) and the remainder (rk ) that is the input to the following stage. In the kth stage, the input rk+1

is compared to two Fibonacci numbers fk+1 and fk. If rk+1 fk+1, dk is coded as 1; If rk+1 < fk , dk is coded as

0; If the value rk+1 is in between, dk is coded to the same value as dk+1. The remainder is computed as rk+1

dk fk . We shall refer the ranges [ fk+1, fk+2), ( fk , fk+1) and [0, fk) as the force-1 zone, gray zone and force-0

zone of the kth stage respectively. The most significant bit (MSB) stage is slightly different from other stages

since no bit proceeds it. It encodes dm by comparing the input v with only one Fibonacci number, fm+1.

The decoder is a straightforward implementation of Eq. 2 which converts the Fibonacci vector back to the

binary vector The correctness of Algorithm can be proven by showing that if after the kth stage, the partially

generated output vector dm dk+1dk is FPF, then adding the output of the (k 1)th stage, dk1 will not

introduce a forbidden pattern

Figure 4 Encoder and Decoder Implementation

www.iosrjournals.org

12 | Page

Fibonacci Codes for Crosstalk Avoidance

Figure 5 FPF Code book & all implementations code book

Figure 6 FSM Chart Implementation

Figure 7 Matlab Design

www.iosrjournals.org

13 | Page

Fibonacci Codes for Crosstalk Avoidance

IV.

Results and Conclusions

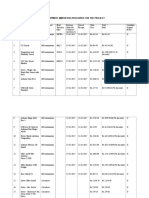

We proposed a family of Fibonacci coding techniques for crosstalk avoidance by exploiting Fibonacci

number system. Figure 8 & 9 Show the Simulated Waveform and RTL schematic of the proposed FTF Codec.

Crosstalk avoidance codes are shown to be able to reduce the inter-wire crosstalk and therefore boost the

maximum speed on the data bus. They have the advantage of consuming less area overhead than shielding

techniques. Even though several different types of codes have been proposed in the past few years, no mapping

scheme was given which facilitates the CODEC implementation. Compounded by the nonlinear nature of the

CAC, the lack of a solution to the systematic construction of the CODEC has hampered the wide use of CAC in

practice. In this paper, we give what we believe is the first solution to this problem. We showed that data can be

coded to a forbidden pattern free vector in the Fibonacci numeral system. We first give a straightforward

mapping algorithm that produces a set of FPF codes with near-optimal cardinality. The area overhead of this

coding scheme is near the theoretical lower bound. The CODEC based on this coding scheme is systematic and

has very low complexity. The size of the CODEC grows quadratically with the data bus size as opposed to

exponentially in a brute forced implementation. Our systemic coding scheme allows the code design of

arbitrarily large busses without having to resort to bus partitioning

We showed the inter-dependency among the proposed techniques and provided a formal procedure to

convert a codeword set into another codeword set. We also related our proposed techniques with some of the

existing crosstalk avoidance coding techniques. The proposed techniques eliminate crosstalk completely, but not

inductance. The worst-case inductance occurs when adjacent lines transition in the same direction. We plan to

come up with a suitable mechanism to minimize the inductance effects using Fibonacci codes in future.

We can further propose an improved coding scheme which yields a set of FPF codes with maximum cardinality.

The area overhead of this optimal coding scheme matches the theoretical lower bound. We gave the

corresponding modification in the CODEC design as well. This paper also discusses issues associated with

CODEC implementations. We proposed a modified coding scheme that eliminates the MSB stage in the encoder

and simplifies the decoder side as well. The modification reduces the total gate count and improves the CODEC

speed.

Figure 8 CPF simulation waveform

Nff simulation waveform

www.iosrjournals.org

14 | Page

Fibonacci Codes for Crosstalk Avoidance

Figure 9 RTL Schematic of the Designed Model

Acknowledgements

The authors would like to thank the anonymous reviewers for their comments which were very helpful

in improving the quality and presentation of this paper.

References

[1]

[2]

[3]

[4]

[5]

[6]

[7]

[8]

[9]

[10]

[11]

[12]

S.P. Khatri Cross-talk Noise Immune VLSI Design using Regular Layout Fabrics, PhD thesis, University of California at

Berkeley, Berkeley, California, 1999.

S.P. Khatri, A. Mehrotra, R.K. Brayton, Ralf H.J.M. Otten, and A.L. Sangiovanni-Vincentelli. A novel vlsi layout fabric for deep

sub-micron applications, In Proceedings of Design Automation Conference, pages 491496. IEEE, 1999.

F. Caignet, S. Delmas-Bendhia, and E. Sicard, The challenge of signal integrity in deep-submicrometer CMOS technology, Proc.

IEEE, vol. 89, no. 4, pp. 556573, Apr. 2001.

D. Pamunuwa, L.-R. Zheng, and H. Tenhunen, Maximizing throughput over parallel wire structures in the deep submicrometer

regime, IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 11, no. 2, pp. 224243, Apr. 2003.

R. Arunachalam, E. Acar, and S. Nassif, Optimal shielding/spacing metrics for low power design, in Proc. IEEE Comput. Soc.

Annu. Symp. VLSI, 2003, pp. 167172.

B. Victor and K. Keutzer, Bus encoding to prevent crosstalk delay, in Proc. IEEE/ACM Int. Conf. Comput.-Aided Design, 2001,

pp. 5763.

C. Duan, A. Tirumala, and S. Khatri, Analysis and avoidance of crosstalk in on-chip buses, in Proc. Hot Interconnects, 2001, pp.

133138.

P. Subramanya, R. Manimeghalai, V. Kamakoti, and M. Mutyam, A bus encoding technique for power and cross-talk

minimization, in Proc. IEEE Int. Conf. VLSI Design, 2004, pp. 443448.

M. Stan and W. Burleson, Limited-weight codes for low power I/O, in Proc. IEEE/ACM Int. Workshop Low Power Design,

1994, pp. 209214.

M. Mutyam, Preventing crosstalk delay using Fibonacci representation, in Proc. IEEE Int. Conf. VLSI Design, 2004, pp. 685

688.

C. Duan, C. Zhu, and S. Khatri, Forbidden transition free crosstalk avoidance codec design, in Proc. Design Autom. Conf., 2008,

pp. 986991.

C. Duan, V. C. Calle, and S. Khatri, Efficient on-chip crosstalk avoidance codec design, IEEE Trans. Very Large Scale Integr.

(VLSI) Syst., vol. 17, no. 4, pp. 551560, Apr. 2009.

www.iosrjournals.org

15 | Page

You might also like

- Crosstalk & Power Reduction in On Chip-VLSI Interconnect by Using Bus Encoding TechniqueDocument10 pagesCrosstalk & Power Reduction in On Chip-VLSI Interconnect by Using Bus Encoding TechniqueRohit SinghNo ratings yet

- Signal Integrity: From High-Speed to Radiofrequency ApplicationsFrom EverandSignal Integrity: From High-Speed to Radiofrequency ApplicationsNo ratings yet

- High Performance Data Bus Encoding Technique in DSM TechnologyDocument5 pagesHigh Performance Data Bus Encoding Technique in DSM TechnologyBreixo HarguindeyNo ratings yet

- Performance Enhancement by Bidirectional Buffer Insertion in Vlsi InterconnectsDocument9 pagesPerformance Enhancement by Bidirectional Buffer Insertion in Vlsi Interconnectsrajnid_1No ratings yet

- Design Challenges in Subthreshold Interconnect CircuitsDocument19 pagesDesign Challenges in Subthreshold Interconnect CircuitsshastryNo ratings yet

- Layout Design of CMOS Buffer To Reduce Area and PowerDocument4 pagesLayout Design of CMOS Buffer To Reduce Area and PowerIJIRSTNo ratings yet

- Analysis, Reduction and Avoidance of Crosstalk On VLSI ChipsDocument8 pagesAnalysis, Reduction and Avoidance of Crosstalk On VLSI Chipsjubincb2No ratings yet

- Crosstalk:: Antenna Crosstalk and Reliability ChecksDocument13 pagesCrosstalk:: Antenna Crosstalk and Reliability Checkssharath_mbNo ratings yet

- Phase 2 ReportDocument59 pagesPhase 2 ReportMurugeswariNo ratings yet

- Wei - Links - Chapter02 Energy-Efficient Design of High-Speed LinksDocument39 pagesWei - Links - Chapter02 Energy-Efficient Design of High-Speed LinksDaniel WeinfeldNo ratings yet

- Network Coding, Algebraic Coding, and Network Error CorrectionDocument5 pagesNetwork Coding, Algebraic Coding, and Network Error CorrectionSaissi NadiaNo ratings yet

- Optimal Positions of Twists in Global On-Chip Differential InterconnectsDocument9 pagesOptimal Positions of Twists in Global On-Chip Differential InterconnectsSudhakar SpartanNo ratings yet

- Lower-Power: LayoutDocument11 pagesLower-Power: LayoutmturadagiNo ratings yet

- Efficient On-Chip Crosstalk Avoidance CODEC DesignDocument10 pagesEfficient On-Chip Crosstalk Avoidance CODEC DesignHari BabuNo ratings yet

- Error Control Schemes For Networks: An Overview: A A A BDocument16 pagesError Control Schemes For Networks: An Overview: A A A BFariz AhdiatamaNo ratings yet

- Design and Analysis of Different Circuits Using DCVSL & Static CMOS TechniqueDocument7 pagesDesign and Analysis of Different Circuits Using DCVSL & Static CMOS TechniqueGRD JournalsNo ratings yet

- Imp 2Document7 pagesImp 2sohailasghar_tNo ratings yet

- Prediction and Comparison of High-Performance On-Chip Global InterconnectionDocument13 pagesPrediction and Comparison of High-Performance On-Chip Global InterconnectionVimala PriyaNo ratings yet

- VLSI: Techniques For Efficient Standard Cell Placement: Aditi Malik Deepak Kumar Arora Sanjay KumarDocument5 pagesVLSI: Techniques For Efficient Standard Cell Placement: Aditi Malik Deepak Kumar Arora Sanjay KumarKumar KumarNo ratings yet

- Staggered Latch Bus A Reliable Offset Switched Architecture For Long On-Chip InterconnectDocument6 pagesStaggered Latch Bus A Reliable Offset Switched Architecture For Long On-Chip InterconnectApikShafieeNo ratings yet

- Signal Integrity PDFDocument21 pagesSignal Integrity PDFmosa totahNo ratings yet

- Research Article: Redundant Logic Insertion and Latency Reduction in Self-Timed AddersDocument13 pagesResearch Article: Redundant Logic Insertion and Latency Reduction in Self-Timed Adderssweety_1No ratings yet

- Three-Dimensional Integrated Circuits: Performance, Design Methodology, and CAD ToolsDocument6 pagesThree-Dimensional Integrated Circuits: Performance, Design Methodology, and CAD ToolsRajesh GoyatNo ratings yet

- Joint Coding-Precoding With Low-Complexity Turbo-DecodingDocument11 pagesJoint Coding-Precoding With Low-Complexity Turbo-DecodingSumala G LakshmiNo ratings yet

- Inductive Coupling Aware Explicit Cross-Talk and Delay Formula For On-Chip VLSI RLCG Interconnects Using Difference Model ApproachDocument6 pagesInductive Coupling Aware Explicit Cross-Talk and Delay Formula For On-Chip VLSI RLCG Interconnects Using Difference Model Approachsiva007kotiNo ratings yet

- Cdma Thesis PDFDocument7 pagesCdma Thesis PDFcyndiruppelspringfield100% (1)

- Design of A CMOS Tapered Cascaded Multistage Distributed AmplifierDocument10 pagesDesign of A CMOS Tapered Cascaded Multistage Distributed Amplifierindresh.vermaNo ratings yet

- Turbo Codes: Farah Ilyas Vohra (TC-28), Shafaq Mustafa (TC-13), Sabieka Rizvi (TC-61) and Zainab Qazi (TC-11)Document5 pagesTurbo Codes: Farah Ilyas Vohra (TC-28), Shafaq Mustafa (TC-13), Sabieka Rizvi (TC-61) and Zainab Qazi (TC-11)Zainab QaziNo ratings yet

- 3 Transceiver DesignDocument6 pages3 Transceiver DesignUtsav PopliNo ratings yet

- 06982195Document13 pages06982195JubinNo ratings yet

- Methodology For Efficient Substrate Noise Analysis in Large-Scale Mixed-Signal CircuitsDocument14 pagesMethodology For Efficient Substrate Noise Analysis in Large-Scale Mixed-Signal Circuits원성규No ratings yet

- 2010 Globe AhmedDocument5 pages2010 Globe AhmedahmedabdullaNo ratings yet

- Application and Analysis of Approximate Bus and Shift-Invert Encoding Technique For Image Data Transfer Over Serial BusDocument11 pagesApplication and Analysis of Approximate Bus and Shift-Invert Encoding Technique For Image Data Transfer Over Serial BusIJRASETPublicationsNo ratings yet

- DSTC Layering Protocols in Wireless Relay NetworksDocument14 pagesDSTC Layering Protocols in Wireless Relay NetworksepannirselvamNo ratings yet

- A Fibonacci Coding Technique To Avoid Crosstalk On On-Chip Data BusDocument4 pagesA Fibonacci Coding Technique To Avoid Crosstalk On On-Chip Data BusRahul YadavNo ratings yet

- Wavepipelined InterconnectsDocument5 pagesWavepipelined InterconnectsbibincmNo ratings yet

- Building Wireless Sensor Networks: Application to Routing and Data DiffusionFrom EverandBuilding Wireless Sensor Networks: Application to Routing and Data DiffusionNo ratings yet

- Signal Integrity Analysis in PCB for High Speed Digital Circuit DesignDocument8 pagesSignal Integrity Analysis in PCB for High Speed Digital Circuit DesignsalehNo ratings yet

- Inter Frame Bus EncodingDocument5 pagesInter Frame Bus EncodingvinumvNo ratings yet

- Assignment 5: NFC-Institute of Engineering and Technology, MultanDocument13 pagesAssignment 5: NFC-Institute of Engineering and Technology, Multanabdullah noorNo ratings yet

- VLSI Interconnect Survey Addressing High-Performance On-Chip TechniquesDocument6 pagesVLSI Interconnect Survey Addressing High-Performance On-Chip TechniquesMohamed YousufNo ratings yet

- Research Article Adaptive Joint Lossy Source-Channel Coding For Multihop Iot NetworksDocument15 pagesResearch Article Adaptive Joint Lossy Source-Channel Coding For Multihop Iot NetworkssqdqsdNo ratings yet

- A Parallel Genetic Algorithm For Performance-Driven VLSI RoutingDocument28 pagesA Parallel Genetic Algorithm For Performance-Driven VLSI RoutingNaveen ChaubeyNo ratings yet

- A Review On Codec's For Crosstalk Avoidance in VLSI InterconnectsDocument3 pagesA Review On Codec's For Crosstalk Avoidance in VLSI InterconnectsEditor IJRITCCNo ratings yet

- Qam ThesisDocument4 pagesQam ThesisMichelle Shaw100% (1)

- Paper 12 PDFDocument5 pagesPaper 12 PDFdollyNo ratings yet

- Introduction To High-Speed Digital Design Principles: BackgroundDocument10 pagesIntroduction To High-Speed Digital Design Principles: BackgroundGuilherme AFNo ratings yet

- Error Correction Scheme For Wireless Sensor NetworksDocument8 pagesError Correction Scheme For Wireless Sensor NetworksJournal of TelecommunicationsNo ratings yet

- Small Cell In-Band Wireless Backhaul in Massive MIMO Systems: A Cooperation of Next-Generation TechniquesDocument31 pagesSmall Cell In-Band Wireless Backhaul in Massive MIMO Systems: A Cooperation of Next-Generation Techniqueshendra lamNo ratings yet

- Variation Tolerant Clock Distribution Network For NomicroprocessorDocument8 pagesVariation Tolerant Clock Distribution Network For NomicroprocessorKhadar BashaNo ratings yet

- Optical Interconnection Technology in Switches, Routers and Optical Cross ConnectsDocument7 pagesOptical Interconnection Technology in Switches, Routers and Optical Cross Connectsexample xxNo ratings yet

- Three Dimensional CMOS Devices and Integrated Circuits: JakubDocument8 pagesThree Dimensional CMOS Devices and Integrated Circuits: JakubGauri Shankar SinghNo ratings yet

- Design and Test Strategies for 2D/3D Integration for NoC-based Multicore ArchitecturesFrom EverandDesign and Test Strategies for 2D/3D Integration for NoC-based Multicore ArchitecturesNo ratings yet

- Simulation of A CDMA Systems Using Linear Prediction and MUD (Matlab)Document44 pagesSimulation of A CDMA Systems Using Linear Prediction and MUD (Matlab)Raj Kumar100% (2)

- IC Interconnect AnalysisDocument316 pagesIC Interconnect AnalysisRavi Singh0% (1)

- Multicast Routing in WSNDocument5 pagesMulticast Routing in WSNajyshowNo ratings yet

- COMPUTER COMMUNICATION NETWORKS MODULESDocument17 pagesCOMPUTER COMMUNICATION NETWORKS MODULESSanjay SinhaNo ratings yet

- Paralle ProcessingDocument8 pagesParalle ProcessingRavi RavikiranNo ratings yet

- LEACH Ad HocDocument10 pagesLEACH Ad HocHimadri BhattacharjeeNo ratings yet

- JESD204C primer introduces new high-speed serial link standardDocument3 pagesJESD204C primer introduces new high-speed serial link standardPronadeep BoraNo ratings yet

- AXI vs AHB: Understanding the Differences Between the Two Popular ARM Bus ProtocolsDocument3 pagesAXI vs AHB: Understanding the Differences Between the Two Popular ARM Bus ProtocolsPronadeep Bora100% (2)

- SerDes - WikipediaDocument3 pagesSerDes - WikipediaPronadeep BoraNo ratings yet

- What Is JESD204 and Why Should We Pay Attention To ItDocument3 pagesWhat Is JESD204 and Why Should We Pay Attention To ItPronadeep BoraNo ratings yet

- Valid Documents List PDFDocument2 pagesValid Documents List PDFAnoop DubeyNo ratings yet

- UARTDocument24 pagesUARTPronadeep BoraNo ratings yet

- 8b - 10b Encoding - WikipediaDocument8 pages8b - 10b Encoding - WikipediaPronadeep BoraNo ratings yet

- EDN - Understanding Layers in The JESD204B Specification - A High Speed ADC Perspective, Part 2 - EDNDocument8 pagesEDN - Understanding Layers in The JESD204B Specification - A High Speed ADC Perspective, Part 2 - EDNPronadeep BoraNo ratings yet

- Demystifying Deterministic Latency Within JESD204B Converters - Electronic DesignDocument11 pagesDemystifying Deterministic Latency Within JESD204B Converters - Electronic DesignPronadeep BoraNo ratings yet

- SMDP - Project - Final - Proposal - NIT - N - Draft PDFDocument17 pagesSMDP - Project - Final - Proposal - NIT - N - Draft PDFPronadeep BoraNo ratings yet

- Amukh Expre CertifDocument1 pageAmukh Expre CertifPronadeep BoraNo ratings yet

- Asynchronous FIFO Basics for Safe Clock Domain CrossingDocument40 pagesAsynchronous FIFO Basics for Safe Clock Domain CrossingPronadeep Bora100% (1)

- 2quickly Implement JESD204BDocument4 pages2quickly Implement JESD204BPronadeep BoraNo ratings yet

- UART SpecDocument24 pagesUART SpecPronadeep BoraNo ratings yet

- AMBA AHB AXI Interview Questions Verification Guide PDFDocument2 pagesAMBA AHB AXI Interview Questions Verification Guide PDFPronadeep BoraNo ratings yet

- Difference Between AHB and AXI - Difference BetweenDocument2 pagesDifference Between AHB and AXI - Difference BetweenPronadeep BoraNo ratings yet

- SMDP C2SDSixmonthlyProgressFinalDocument4 pagesSMDP C2SDSixmonthlyProgressFinalPronadeep BoraNo ratings yet

- AMBA AHB Protocol PresentationDocument45 pagesAMBA AHB Protocol Presentationachanta1291% (11)

- Six Monthly Progress-Annexures (Tables)Document6 pagesSix Monthly Progress-Annexures (Tables)Pronadeep BoraNo ratings yet

- Six Monthly Progress-FormatDocument3 pagesSix Monthly Progress-FormatPronadeep BoraNo ratings yet

- Utilization Certificate - SMDP-1Document1 pageUtilization Certificate - SMDP-1Pronadeep BoraNo ratings yet

- Asynchronous FIFO Basics for Safe Clock Domain CrossingDocument40 pagesAsynchronous FIFO Basics for Safe Clock Domain CrossingPronadeep Bora100% (1)

- V2 - Proforma For Submitting 6 MONTHLY REPORTDocument9 pagesV2 - Proforma For Submitting 6 MONTHLY REPORTPronadeep BoraNo ratings yet

- WHMS NitnDocument14 pagesWHMS NitnPronadeep BoraNo ratings yet

- Current Project StatusDocument1 pageCurrent Project StatusPronadeep BoraNo ratings yet

- AQMS NitnDocument11 pagesAQMS NitnPronadeep BoraNo ratings yet

- Quotations For Components Required For SMDP ProjectDocument2 pagesQuotations For Components Required For SMDP ProjectPronadeep BoraNo ratings yet

- Element14equipments PDFDocument1 pageElement14equipments PDFPronadeep BoraNo ratings yet

- Nit Nagaland - Pmod - Quote - DG - CoreelDocument1 pageNit Nagaland - Pmod - Quote - DG - CoreelPronadeep BoraNo ratings yet

- Digilent LABSeupimentsDocument1 pageDigilent LABSeupimentsPronadeep BoraNo ratings yet

- Elektric Schematic - RH 400 400013Document290 pagesElektric Schematic - RH 400 400013Vikranth ReddyNo ratings yet

- 205 Unit 1 L04 Superposition TheoremDocument5 pages205 Unit 1 L04 Superposition TheoremBINOSHI SAMUVELNo ratings yet

- Lecture-2 Introduction To Process Control Part 2Document25 pagesLecture-2 Introduction To Process Control Part 2HATAM TALAL ALINo ratings yet

- Catalog Excerpt-VariTrans P 27000-En-KnickDocument8 pagesCatalog Excerpt-VariTrans P 27000-En-KnicksanimariNo ratings yet

- Kool & the Gang Backline RequirementsDocument11 pagesKool & the Gang Backline RequirementsPaul GunterNo ratings yet

- PADS Standard Plus Evaluation GuideDocument204 pagesPADS Standard Plus Evaluation GuideDavid MittmannNo ratings yet

- QSC RMX1450 PDFDocument7 pagesQSC RMX1450 PDFJohnny Tenezaca DuarteNo ratings yet

- Vantage: Installation and Operating InstructionsDocument2 pagesVantage: Installation and Operating InstructionsAngel Quijano ArmengolNo ratings yet

- Mammano - Designing Stable Control LoopsDocument33 pagesMammano - Designing Stable Control LoopsRakesh SandarativjuNo ratings yet

- User Manual: Using The Induction Cooker Preparing For Use Use Below CookwareDocument2 pagesUser Manual: Using The Induction Cooker Preparing For Use Use Below Cookwarephanikumar_nsrNo ratings yet

- DLC Da+dg Aw03Document336 pagesDLC Da+dg Aw03zotya54No ratings yet

- Notebook Spotlight: A Notebook of Desire That Features A Synthesis of Power and SophisticationDocument21 pagesNotebook Spotlight: A Notebook of Desire That Features A Synthesis of Power and Sophisticationxavier refourNo ratings yet

- Module 8 Three Phase Systems v3Document43 pagesModule 8 Three Phase Systems v3Pao CastillonNo ratings yet

- IEGCDocument80 pagesIEGCMonika SharmaNo ratings yet

- Siemens MS 43Document20 pagesSiemens MS 43Rómulo Simón Lizarraga León100% (1)

- Users Manual Mcs-51Document28 pagesUsers Manual Mcs-51Subkhan KholiqiNo ratings yet

- Novo Documento Do Microsoft Office WordDocument9 pagesNovo Documento Do Microsoft Office WordVictor José PauloNo ratings yet

- Wave Optics Animation - PpsDocument20 pagesWave Optics Animation - Ppsaleena'No ratings yet

- XDVDocument54 pagesXDVnachiket1234No ratings yet

- 3264 - 01 - 02 - FU Steering Control Unit Handwheel, Type 105-106Document20 pages3264 - 01 - 02 - FU Steering Control Unit Handwheel, Type 105-106MariosNo ratings yet

- IAT-II Question Paper With Solution of 15EC53 Verilog HDL Nov-2017 - Sunil Kumar K.H PDFDocument10 pagesIAT-II Question Paper With Solution of 15EC53 Verilog HDL Nov-2017 - Sunil Kumar K.H PDFKavyashreeMNo ratings yet

- Real-Time Implementation of Hydroelectric Power Plant Using PLC and ScadaDocument4 pagesReal-Time Implementation of Hydroelectric Power Plant Using PLC and ScadaJosephNo ratings yet

- Manual de Servicio de Equipo de Sonido de Radio mp3Document46 pagesManual de Servicio de Equipo de Sonido de Radio mp3daniel perezNo ratings yet

- Cinemate: Universal Remote ControlDocument19 pagesCinemate: Universal Remote ControlTamara SamanthaNo ratings yet

- Features General Description: 3A, 12V, Synchronous-Rectified Buck ConverterDocument21 pagesFeatures General Description: 3A, 12V, Synchronous-Rectified Buck ConverterVeronica GonzalezNo ratings yet

- 7SR11 and 7SR12 - Argus Complete Technical ManualDocument406 pages7SR11 and 7SR12 - Argus Complete Technical ManualAndré Eiti KobayashiNo ratings yet

- Infrared people counter counts entriesDocument3 pagesInfrared people counter counts entriesthisissanjay100% (1)

- RadiosByHallicrafters PDFDocument236 pagesRadiosByHallicrafters PDFJosue Hernandez Gutierrez100% (2)

- Electrolytic CellDocument6 pagesElectrolytic CellJohn Israel R. CatedralNo ratings yet

- CARA PEMASANGAN RADIO KERETA DALAM 40 HURUFDocument6 pagesCARA PEMASANGAN RADIO KERETA DALAM 40 HURUFamir akmalNo ratings yet