Professional Documents

Culture Documents

07a30401 Pulse and Digital Circuits

Uploaded by

andhracollegesCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

07a30401 Pulse and Digital Circuits

Uploaded by

andhracollegesCopyright:

Available Formats

www.andhracolleges.

com The Complete Information About Colleges in Andhra Pradesh

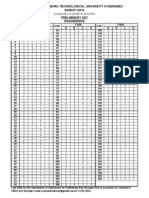

Code No: 07A30401 Set No. 1

II B.Tech I Semester Regular Examinations, November 2008

PULSE AND DIGITAL CIRCUITS

( Common to Electrical & Electronic Engineering and Electronics &

Instrumentation Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

www.andhracolleges.com

⋆⋆⋆⋆⋆

1. (a) Explain the response of RC low pass circuit for exponestial input signal

(b) Derive the expression for percentage till for a square wave output of Rc high

pass circuit. [8+8]

2. (a) Design a diode clamper to restore a d.c level of +3 Volts to an input sinusoidal

signal of peak value 10Volts. Assume drop across diode is 0.6 volts as shown

in the figure 2a.

Figure 2a

(b) Compare series diode clipper and shunt diode clipper. [8+8]

www.andhracolleges.com

3. (a) Explain the phenomenon of latching in a transistor

(b) Define the following for a transistor switch

i. Rise time

ii. Fall time

iii. Storage time

iv. Delay time. [8+8]

4. (a) Explain different triggering methods of binary circuits.

(b) A collector coupled Fixed bias binary uses NPN transistors with hF E = 100.

The circuit parameters are VCC = 12v, VBB = -3v, RC = 1k Ω, R1 = 5k Ω,

and R2 = 10 k Ω. Verify that when one transistor is cut-off the other is in

saturation. Find the stable state currents and voltages for the circuit. Assume

for transistors VCE(sat) = 0.3V and VBE(sat) = 0.7V. [8+8]

5. (a) In a current sweep circuit, explain how linearity correction is made through

adjustment of driving waveform.

(b) Write the basic mechanism of transistor television sweep circuit. [16]

6. (a) What is the condition to be met for pulse synchronization?

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: 07A30401 Set No. 1

(b) Describe synchronization with 2:1 frequency division with neat waveforms.

(c) Define the terms phase delay and phase jitter. [4+8+4]

7. (a) What is a sampling gate.

(b) Illustrate the principle of sampling gates with series and parallel switches and

compare them.

www.andhracolleges.com

(c) Draw the circuit diagram of unidirectional diode gate and explain its operation.

[16]

8. (a) Draw the circuit diagram of diode - resistor logic AND gate and explain its

operation.

(b) Design a transistor inverter circuit (NOT gate) with the following specifica-

tions. VCC = VBB = 10V, icsat = 10mA; hf emin = 30; the input is varying

between 0 and 10V. Assume typical junction voltages of npn silicon transistor.

[16]

⋆⋆⋆⋆⋆

www.andhracolleges.com

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

2 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

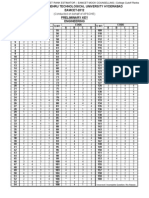

Code No: 07A30401 Set No. 2

II B.Tech I Semester Regular Examinations, November 2008

PULSE AND DIGITAL CIRCUITS

( Common to Electrical & Electronic Engineering and Electronics &

Instrumentation Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

www.andhracolleges.com

⋆⋆⋆⋆⋆

1. (a) A symmetrical square wave whose peak-to-peak amptitude id 2V and whose

average value is zero as applied to on Rc integrating circuit. The time constant

is equals to half -period of th esquare wave find the peak to peak value of the

output amplitude

(b) Describe the relationship between rise time and RCtime constant of a low pass

RC circuit. [8+8]

2. (a) Determine Vo for the network shown in fugure 2a for the given waveform

.Assume ideal diodes.

www.andhracolleges.com Figure 2a

(b) Explain negative peak clipper with and without reference voltage.

3. (a) For a common emitter circuit Vcc = 10V, RC = 1kΩ IB =0.2A. Determine

i. The valve of hF E (min) for saturation to occor

ii. If Rc is changed to 220Ω, will the transistor be saturated

(b) Explain the phenomenon of latching in a transistor.

[8+8]

[8+8]

4. Draw the circuit diagram for Schmitt trigger and explain its operation. What are

the applications of the above circuit? Derive the expressions for UTP and LTP.

[16]

5. Explain the basic principal of Miller and Bootstrap time base generators and also

derive the equations for sweep speed error. [16]

6. (a) With the help of a circuit diagram and waveforms explain frequency division

of an a stable multivibrator with pulse signals.

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: 07A30401 Set No. 2

(b) Explain with the help of block diagram and waveforms for acheiving division

of relaxation devices without phase jitter. [8+8]

7. (a) Distinguish between sampling gates and logic gates?

(b) Explain the operation of a chopper amplifier with neat block diagram and

waveforms.

(c) Distinguish between unidirectional and bidirectional gates. [4+8+4]

www.andhracolleges.com

8. (a) Draw the circuit diagram of diode-transistor logic NOR gate and explain its

operation.

(b) Draw the output waveform X for the given inputs figure 8b

Figure 8b

⋆⋆⋆⋆⋆

www.andhracolleges.com

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

2 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: 07A30401 Set No. 3

II B.Tech I Semester Regular Examinations, November 2008

PULSE AND DIGITAL CIRCUITS

( Common to Electrical & Electronic Engineering and Electronics &

Instrumentation Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

www.andhracolleges.com

⋆⋆⋆⋆⋆

1. (a) Explain about RLC Ringing Circuit

(b) Explain RC double differentiator circuit. [8+8]

2. (a) T=1000 µ sec

V= 10 V

Duty cycle = 0.2

i. Sketch waveform with voltage levels at steady state figure 2(a)iii

ii. Forward and reverse direction tilt

iii. Af / Ar

www.andhracolleges.com Figure 2(a)iii

(b) Write a short note on non- linear wave shaping.

3. Explain the following

(a) Storage and transition times of the diode as a switch

(b) Switching times of the transistor.

4. What is a monostable multivibrator? Explain with the help of a neat circuit di-

agram the principle of operation of a monostable multivibrator, and derive an

[12+4]

[8+8]

expression for pulse width. Draw the wave forms at collector and Bases of both

transistors. [16]

5. (a) Define sweep time and restoration time of a voltage time base waveform. What

is the difference between sweep and sawtooth waveforms?

(b) In the transistor bootstrap circuit, Vcc = 25V, VEE = − 15V, R = 10kΩ, RE

= 15kΩ, RB = 150 kΩ, C= 0.05 µF, C1 = 100 µF. The gating waveform has

a duration TG =300 µSec. The transistor parameters are hie = 1.1 kΩ, hre =

2.5 × 10−4 kΩ, hf e = 50, hoe = 1/40

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: 07A30401 Set No. 3

i. Draw the waveforms of ic , and vo , labeling all current and voltage levels.

ii. What is the slope error of the sweep?

iii. What is the sweep speed and the maximum value of the sweep voltage?

iv. What is the retrace time Tr for C to discharge completely?

v. Calculate the recovery time T1 for C1 to recharge completely. [16]

6. (a) With the help of a circuit diagram and waveforms, explain frequency division

www.andhracolleges.com

of an astable multivibrator with pulse signals.

(b) The relaxation oscillator, when running freely, generates an output signal of

peak - to - peak amplitude 100V and frequency 1 kHz. Synchronizing pulses

are applied of such amplitude that at each pulse the breakdown voltage is

lowered by 20V. Over what frequency range may the sync pulse frequency be

varied if 1 : 1 synchronization is to result? If 5 : 1 synchronization is to be

obtained (fP /fS = 5), over what range of frequency may the pulse source be

varied? [16]

7. (a) Explain the operation of a six - diode gate.

(b) Write the applications of sampling gates.

(c) Briefly describe the chopper amplifier and sampling scope. [16]

8. (a) Compare the Resistor Transistor logic and Diode Transistor logic families

(b) Explain the wired AND logic with the help of circuit diagram.

[8+8]

⋆⋆⋆⋆⋆

www.andhracolleges.com

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

2 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: 07A30401 Set No. 4

II B.Tech I Semester Regular Examinations, November 2008

PULSE AND DIGITAL CIRCUITS

( Common to Electrical & Electronic Engineering and Electronics &

Instrumentation Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

www.andhracolleges.com

⋆⋆⋆⋆⋆

1. (a) Obtain the response of RC high pass cirucit for an exponential i/p lignal

(b) A square wave whose peak-to-peak valve is IV, exterds I 0.5V w.r.t. to ground.

The half period is O.iSec this voltage impressed upon an RC differentating

circuit whose time constant is 0.2 sec. Determine the maximum and minimum

valves of the l/p voltages int eh steady state. [8+8]

2. (a) The input voltage vi to the two level clipper shown in figure 2a varies linearly

from 0 to 75 V. Sketch the output voltage vo to the same time scale as the

input voltage. Assume Ideal diodes.

www.andhracolleges.com Figure 2a

(b) Explain positive peak voltage limiters below reference level.

3. (a) Explain with relevant diagram the various transistor switching times

(b) Explain the storage and transition times of the diode as a switch.

4. Explain about various switching conditions of Schmitt trigger.

5. (a) What are the methods of generating a time base waveform? Explain each

method.

[12+4]

[8+8]

[16]

(b) Derive the expression Mathematical relationship between sweep speed error,

Displacement error and transmission error for an exponential sweep circuit.

[16]

6. (a) Describe frequency division employing a transistor a stable multivibrator with

waveforms.

(b) Describe frequency division employing a transistor monostable multivibrator

with waveforms. [8+8]

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: 07A30401 Set No. 4

7. (a) Describe the working of a four diode gate with necessary diagrams and equa-

tions.

(b) For the four diode gate, RL = RC = 100k Ω and that R2 = 2kΩ, RF = 50Ω.

For Vs = 25V, compute gain A, Vmin and (Vc )min . Compute (Vn )min for V

= Vmin .

[16]

www.andhracolleges.com

8. (a) Define positive and negative logic system

(b) Define fan-In, fan-out

(c) Draw and explain the circuit diagram of a diode OR gate for positive logic.

[4+4+8]

⋆⋆⋆⋆⋆

www.andhracolleges.com

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

2 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

You might also like

- Polycet 2014 ST Certificatates Verification DatesDocument1 pagePolycet 2014 ST Certificatates Verification DatesandhracollegesNo ratings yet

- Eamcet 2014 Engineering Key SolutionsDocument42 pagesEamcet 2014 Engineering Key Solutionsandhracolleges100% (1)

- Eamcet Agriculture Last Ranks Cutoffs Andhracolleges Eamcet 2013 CutoffsDocument3 pagesEamcet Agriculture Last Ranks Cutoffs Andhracolleges Eamcet 2013 Cutoffsandhracolleges33% (3)

- Polycet2014 Web Counselling NotificationDocument2 pagesPolycet2014 Web Counselling NotificationandhracollegesNo ratings yet

- Andhracollege Eamcet 2014 Engineering Question Paper With Key SolutionsDocument62 pagesAndhracollege Eamcet 2014 Engineering Question Paper With Key Solutionsandhracolleges50% (4)

- EAMCET 2014 Agriculture & Medical Preliminary Answer KeysDocument1 pageEAMCET 2014 Agriculture & Medical Preliminary Answer KeysLohith_EnggNo ratings yet

- JEE Main Advanced 2014 Paper I Maths Paper Answer SolutionsDocument4 pagesJEE Main Advanced 2014 Paper I Maths Paper Answer Solutionsandhracolleges100% (1)

- Polycet 2014 SC BC Oc Certificatates Verification DatesDocument1 pagePolycet 2014 SC BC Oc Certificatates Verification DatesandhracollegesNo ratings yet

- ICET 2014 Preliminary Key Primary Key AndhracollegesDocument2 pagesICET 2014 Preliminary Key Primary Key AndhracollegesandhracollegesNo ratings yet

- Eamcet 2014 Engineering Jntu Preliminary Key AndhracollegesDocument1 pageEamcet 2014 Engineering Jntu Preliminary Key AndhracollegesandhracollegesNo ratings yet

- JEE Advanced 2014 Paper I PHYSICS Paper Answer SolutionsDocument6 pagesJEE Advanced 2014 Paper I PHYSICS Paper Answer SolutionsandhracollegesNo ratings yet

- Polycet 2014 Question PaperDocument24 pagesPolycet 2014 Question PaperandhracollegesNo ratings yet

- JEE Main Advanced Paper I Answer Key 25 May 2014Document1 pageJEE Main Advanced Paper I Answer Key 25 May 2014andhracollegesNo ratings yet

- JEE Advanced 2014 Paper I Chemistry Paper Answer SolutionsDocument4 pagesJEE Advanced 2014 Paper I Chemistry Paper Answer SolutionsandhracollegesNo ratings yet

- Eamcet 2014 Medical Question Paper With Key Solutions AndhracollegesDocument62 pagesEamcet 2014 Medical Question Paper With Key Solutions Andhracollegesandhracolleges100% (1)

- Eamcet 2014 Engineering Key Solutions AndhracollegesDocument42 pagesEamcet 2014 Engineering Key Solutions Andhracollegesandhracolleges75% (8)

- Eamcet 2012 Medical PaperDocument60 pagesEamcet 2012 Medical Paperandhracolleges100% (1)

- Eamcet 2014 Medical Question Paper AndhracollegesDocument62 pagesEamcet 2014 Medical Question Paper Andhracollegesandhracolleges100% (1)

- Eamcet 2012 Engineering PaperDocument62 pagesEamcet 2012 Engineering Paperandhracolleges100% (1)

- Eamcet 2012 Engineering Paper KeyDocument1 pageEamcet 2012 Engineering Paper KeyandhracollegesNo ratings yet

- Eamcet 2013 Engineering PaperDocument62 pagesEamcet 2013 Engineering Paperandhracolleges0% (1)

- Eamcet 2012 Engineering Paper KeyDocument1 pageEamcet 2012 Engineering Paper KeyandhracollegesNo ratings yet

- Eamcet 2012 Medical Paper KeyDocument1 pageEamcet 2012 Medical Paper KeyandhracollegesNo ratings yet

- Eamcet 2011 Engineering PaperDocument61 pagesEamcet 2011 Engineering PaperandhracollegesNo ratings yet

- Eamcet 2013 Medical PaperDocument62 pagesEamcet 2013 Medical PaperandhracollegesNo ratings yet

- Eamcet 2010 Medical PaperDocument63 pagesEamcet 2010 Medical PaperandhracollegesNo ratings yet

- Eamcet 2009 Engineering Chemistry PaperDocument16 pagesEamcet 2009 Engineering Chemistry PaperandhracollegesNo ratings yet

- Eamcet 2007 Engineering PaperDocument13 pagesEamcet 2007 Engineering Paperandhracolleges100% (1)

- Eamcet 2008 Engineering PaperDocument62 pagesEamcet 2008 Engineering PaperandhracollegesNo ratings yet

- Eamcet 2006 Engineering PaperDocument14 pagesEamcet 2006 Engineering PaperandhracollegesNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Ccim Fee Refund FormDocument1 pageCcim Fee Refund FormMohammad ShafiqueNo ratings yet

- Managing Information for Better DecisionsDocument12 pagesManaging Information for Better DecisionsTosin WilliamsNo ratings yet

- 2007 Output Stops RemovedDocument45 pages2007 Output Stops RemovedAisyah DzulqaidahNo ratings yet

- Blasting and Painting of Sheds, Pipes, Pipe Fittings, Vessels and Tanks DailyDocument3 pagesBlasting and Painting of Sheds, Pipes, Pipe Fittings, Vessels and Tanks DailyEjike Francis ChizobaNo ratings yet

- ASTM 210cDocument1 pageASTM 210cDodi SuhendraNo ratings yet

- Solar Powered Automatic Toilet LightDocument10 pagesSolar Powered Automatic Toilet LightarwinNo ratings yet

- Feature Setup Description: Software Basic Data Mcs - TCBCDocument77 pagesFeature Setup Description: Software Basic Data Mcs - TCBCAlexis MauricioNo ratings yet

- HGS HSM SL 20 007 - Adjustment of Valve ClearanceDocument66 pagesHGS HSM SL 20 007 - Adjustment of Valve Clearanceajshsu5682No ratings yet

- Strategic Human Resource Management and The HR ScorecardDocument20 pagesStrategic Human Resource Management and The HR ScorecardRajat JainNo ratings yet

- Sop Flower Arrangement in HotelDocument2 pagesSop Flower Arrangement in HotelwawahalimNo ratings yet

- Types of Camera AnglesDocument2 pagesTypes of Camera AnglesMaJudith JavilloNo ratings yet

- Net HSMDocument4 pagesNet HSMJosé Tudela de la RosaNo ratings yet

- IT Act 2000 overview objectives featuresDocument3 pagesIT Act 2000 overview objectives featuresalpanshiNo ratings yet

- B2B ApiDocument350 pagesB2B ApiratnavelpNo ratings yet

- Parts Catalog TT75, TT55 NEW HOLLANDDocument360 pagesParts Catalog TT75, TT55 NEW HOLLANDrogerio97% (35)

- Week 6: Practice Challenge 1 - Charts: InstructionsDocument7 pagesWeek 6: Practice Challenge 1 - Charts: InstructionskiranNo ratings yet

- wndw3 Print PDFDocument520 pageswndw3 Print PDFbryanth9No ratings yet

- Nested Group PowerShellDocument3 pagesNested Group PowerShellNeha SinghNo ratings yet

- United States Patent (19) : HoferDocument7 pagesUnited States Patent (19) : Hoferjoel marshallNo ratings yet

- Samsung DRAM Module Handling Guide - 1128 - 10090119049407 PDFDocument9 pagesSamsung DRAM Module Handling Guide - 1128 - 10090119049407 PDFreza_azadNo ratings yet

- HTML5 Element Cheatsheet 2019Document1 pageHTML5 Element Cheatsheet 2019vVvNo ratings yet

- Envea Dusty Manual enDocument26 pagesEnvea Dusty Manual enmikiNo ratings yet

- Complete Checklist for Manual Upgrades to Oracle Database 12c R1Document27 pagesComplete Checklist for Manual Upgrades to Oracle Database 12c R1Augustine OderoNo ratings yet

- 1281 - Fire Extinguisher and Fire Safety Products Brochure S - tcm431-48382Document16 pages1281 - Fire Extinguisher and Fire Safety Products Brochure S - tcm431-48382Cv. muda karya jayaNo ratings yet

- BUK9Y53-100B DatasheetDocument12 pagesBUK9Y53-100B Datasheetisomeso21No ratings yet

- MDN 1508DSDocument108 pagesMDN 1508DSdocazanNo ratings yet

- Dekut Teaching Practice ManualDocument20 pagesDekut Teaching Practice Manualstephen njorogeNo ratings yet

- Marketing Research of Pre-Start-UpDocument2 pagesMarketing Research of Pre-Start-UpafsalpkgroupNo ratings yet

- SKFDocument26 pagesSKFRahul ParikhNo ratings yet

- Qtiplot Manual enDocument390 pagesQtiplot Manual enjovita georgeNo ratings yet