Professional Documents

Culture Documents

Rr720203 Vlsi Design

Uploaded by

andhracollegesCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Rr720203 Vlsi Design

Uploaded by

andhracollegesCopyright:

Available Formats

www.andhracolleges.

com The Complete Information About Colleges in Andhra Pradesh

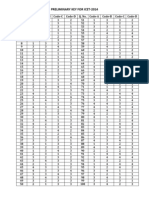

Code No: RR420203 Set No. 1

IV B.Tech II Semester Supplimentary Examinations, May 2008

VLSI DESIGN

(Electrical & Electronic Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

⋆⋆⋆⋆⋆

www.andhracolleges.com

1. (a) Find gm and rds for an n-channel transistor with

VGS = 1.2V; Vtn = 0.8V; W/L = 10; µnCox = 92 µA/V2 and VDS = Veff +

0.5V

The out put impedance constant. λ = 95.3 × 10−3 V−1

(b) Explain the term Figure of merit of a MOS Transistor. [10+6]

2. (a) With neat sketches explain how resistors and capacitors are fabricated in p-

well process.

(b) With neat sketches explain how resistors and capacitors are fabricated in n-

well process. [8+8]

3. Design a stick diagram for the PMOS logic shown below [16]

Y = (A + B).C

4. Design a layout diagram for the CMOS logic shown below [16]

www.andhracolleges.com

Y = (A + B + C)

5. Calculate ON resistance from VDD to GND for the given inverter circuit shown in

Figure 5, If n-channel sheet resistance is 104 Ω per square. [16]

Figure 5

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: RR420203 Set No. 1

6. With neat sketch explain clearly the architecture of the PROM. [16]

7. With respect to synthesis process explain the following terms.

(a) Flattening

(b) Factoring.

(c) Mapping. [6+5+5]

www.andhracolleges.com

8. Mention different growth technologies of the thin oxides and explain about any one

technique. [16]

⋆⋆⋆⋆⋆

www.andhracolleges.com

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

2 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: RR420203 Set No. 2

IV B.Tech II Semester Supplimentary Examinations, May 2008

VLSI DESIGN

(Electrical & Electronic Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

⋆⋆⋆⋆⋆

www.andhracolleges.com

1. (a) Explain with neat sketches the Drain and Transfer characteristics of n-channel

enhancement MOSFET.

(b) With neat sketches explain the transfer characteristics of a CMOS inverter.

2. (a) Compare between CMOS and bipolar technologies.

(b) With neat sketches explain nMOS fabrication process.

3. Design a stick diagram for the NMOS logic shown below

[10+6]

[8+8]

[16]

Y = (A + B + C)

4. Design a layout diagram for nMOS inverter. [16]

5. Calculate the gate capacitance value of 5µm technology minimum sized transistor

with gate to channel capacitance value is 4 × 10−4 pF/µm2 . [16]

www.andhracolleges.com

6. (a) What are the advantages and disadvantages of the reconfiguration.

(b) Mention different advantages of Anti fuse Technology. [8+8]

7. (a) What is the goal of VHDL synthesis step in design flow?

(b) Explain how register transfer level description provides optimized synthesis

netlist. [8+8]

8. Clearly explain the wire bonding technology of the die bonding. [16]

⋆⋆⋆⋆⋆

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

1 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: RR420203 Set No. 3

IV B.Tech II Semester Supplimentary Examinations, May 2008

VLSI DESIGN

(Electrical & Electronic Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

⋆⋆⋆⋆⋆

www.andhracolleges.com

1. (a) With neat sketches explain the formation of the inversion layer in P-channel

Enhancement MOSFET.

(b) An NMOS Transistor is operated in the triode region with the following pa-

rameters VGS = 4V ; Vtn = 1V ; VDS = 2V ; W/L = 100; µnCox = 90 µA/V 2 .

Find its drain current and drain source resistance.

2. With neat sketches explain BICMOS fabrication in an p-well process.

3. Design a stick diagram for the CMOS logic shown below

[8+8]

[16]

[16]

Y = (AB + CD)

4. Design a layout diagram for two input CMOS NOR gate. [16]

5. Calculate the gate capacitance value of 5µm technology minimum sized transistor

with gate to channel capacitance value is 4 × 10−4 pF/µm2 . [16]

6. With neat sketch explain clearly the architecture of the PROM. [16]

www.andhracolleges.com

7. Mention about various types of simulators used in ASIC design flow and clearly

discuss about the significance of each simulator. [16]

8. Explain clearly the molecular beam epitaxy method. [16]

⋆⋆⋆⋆⋆

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

1 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: RR420203 Set No. 4

IV B.Tech II Semester Supplimentary Examinations, May 2008

VLSI DESIGN

(Electrical & Electronic Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

⋆⋆⋆⋆⋆

www.andhracolleges.com

1. (a) With neat sketches explain the Drain characteristics of p-channel Enhance-

ment MOSFET.

(b) An p-MOS Transistor is operated in the Active region with the following

parameters VGS = −4.5V ; Vtp = −1V ; W/L = 95; µnCox = 95 µA/V 2 .

Find its drain current and drain source resistance.

3. Design a stick diagram for two input CMOS NAND and NOR gates.

[8+8]

2. With neat sketches explain how Diodes and Resistors are fabricated in Bipolar

process. [16]

[16]

4. Design a layout diagram for the PMOS logic shown below [16]

Y = (AB) + (CD)

5. Calculate ON resistance from VDD to GND for the given inverter circuit shown in

Figure 5, If n-channel sheet resistance is 104 Ω per square. [16]

www.andhracolleges.com

Figure 5

6. Implement 2-bit comparator using PROM. [16]

7. What is need for RTL simulation? Clearly explain RTL simulation flow in the

ASIC design flow and also mention few leading simulation tools. [16]

8. Explain about the following packaging design considerations.

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: RR420203 Set No. 4

(a) Electrical considerations.

(b) Mechanical design consideration. [8+8]

⋆⋆⋆⋆⋆

www.andhracolleges.com

www.andhracolleges.com

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

2 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

You might also like

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Sedra8e Solvedproblems ch09-2 PDFDocument24 pagesSedra8e Solvedproblems ch09-2 PDFJoh CheNo ratings yet

- Eamcet Agriculture Last Ranks Cutoffs Andhracolleges Eamcet 2013 CutoffsDocument3 pagesEamcet Agriculture Last Ranks Cutoffs Andhracolleges Eamcet 2013 Cutoffsandhracolleges33% (3)

- Polycet2014 Web Counselling NotificationDocument2 pagesPolycet2014 Web Counselling NotificationandhracollegesNo ratings yet

- JEE Advanced 2014 Paper I PHYSICS Paper Answer SolutionsDocument6 pagesJEE Advanced 2014 Paper I PHYSICS Paper Answer SolutionsandhracollegesNo ratings yet

- Eamcet 2014 Engineering Jntu Preliminary Key AndhracollegesDocument1 pageEamcet 2014 Engineering Jntu Preliminary Key AndhracollegesandhracollegesNo ratings yet

- ICET 2014 Preliminary Key Primary Key AndhracollegesDocument2 pagesICET 2014 Preliminary Key Primary Key AndhracollegesandhracollegesNo ratings yet

- Eamcet 2014 Engineering Key Solutions AndhracollegesDocument42 pagesEamcet 2014 Engineering Key Solutions Andhracollegesandhracolleges75% (8)

- JEE Main Advanced 2014 Paper I Maths Paper Answer SolutionsDocument4 pagesJEE Main Advanced 2014 Paper I Maths Paper Answer Solutionsandhracolleges100% (1)

- Polycet 2014 ST Certificatates Verification DatesDocument1 pagePolycet 2014 ST Certificatates Verification DatesandhracollegesNo ratings yet

- Polycet 2014 SC BC Oc Certificatates Verification DatesDocument1 pagePolycet 2014 SC BC Oc Certificatates Verification DatesandhracollegesNo ratings yet

- JEE Main Advanced Paper I Answer Key 25 May 2014Document1 pageJEE Main Advanced Paper I Answer Key 25 May 2014andhracollegesNo ratings yet

- EAMCET 2014 Agriculture & Medical Preliminary Answer KeysDocument1 pageEAMCET 2014 Agriculture & Medical Preliminary Answer KeysLohith_EnggNo ratings yet

- JEE Advanced 2014 Paper I Chemistry Paper Answer SolutionsDocument4 pagesJEE Advanced 2014 Paper I Chemistry Paper Answer SolutionsandhracollegesNo ratings yet

- Eamcet 2014 Medical Question Paper AndhracollegesDocument62 pagesEamcet 2014 Medical Question Paper Andhracollegesandhracolleges100% (1)

- Eamcet 2014 Medical Question Paper With Key Solutions AndhracollegesDocument62 pagesEamcet 2014 Medical Question Paper With Key Solutions Andhracollegesandhracolleges100% (1)

- Polycet 2014 Question PaperDocument24 pagesPolycet 2014 Question PaperandhracollegesNo ratings yet

- Andhracollege Eamcet 2014 Engineering Question Paper With Key SolutionsDocument62 pagesAndhracollege Eamcet 2014 Engineering Question Paper With Key Solutionsandhracolleges50% (4)

- Eamcet 2012 Engineering Paper KeyDocument1 pageEamcet 2012 Engineering Paper KeyandhracollegesNo ratings yet

- Eamcet 2014 Engineering Key SolutionsDocument42 pagesEamcet 2014 Engineering Key Solutionsandhracolleges100% (1)

- Eamcet 2013 Engineering PaperDocument62 pagesEamcet 2013 Engineering Paperandhracolleges0% (1)

- Eamcet 2012 Medical Paper KeyDocument1 pageEamcet 2012 Medical Paper KeyandhracollegesNo ratings yet

- Eamcet 2011 Engineering PaperDocument61 pagesEamcet 2011 Engineering PaperandhracollegesNo ratings yet

- Eamcet 2012 Medical PaperDocument60 pagesEamcet 2012 Medical Paperandhracolleges100% (1)

- Eamcet 2009 Engineering Chemistry PaperDocument16 pagesEamcet 2009 Engineering Chemistry PaperandhracollegesNo ratings yet

- Eamcet 2012 Engineering Paper KeyDocument1 pageEamcet 2012 Engineering Paper KeyandhracollegesNo ratings yet

- Eamcet 2010 Medical PaperDocument63 pagesEamcet 2010 Medical PaperandhracollegesNo ratings yet

- Eamcet 2006 Engineering PaperDocument14 pagesEamcet 2006 Engineering PaperandhracollegesNo ratings yet

- Eamcet 2012 Engineering PaperDocument62 pagesEamcet 2012 Engineering Paperandhracolleges100% (1)

- Eamcet 2013 Medical PaperDocument62 pagesEamcet 2013 Medical PaperandhracollegesNo ratings yet

- Eamcet 2008 Engineering PaperDocument62 pagesEamcet 2008 Engineering PaperandhracollegesNo ratings yet

- Eamcet 2007 Engineering PaperDocument13 pagesEamcet 2007 Engineering Paperandhracolleges100% (1)

- Bipolar Junction TransistorDocument18 pagesBipolar Junction TransistorPritam Keshari SahooNo ratings yet

- Slides Ch2 Devices PDFDocument28 pagesSlides Ch2 Devices PDFSatya SahaNo ratings yet

- SavantIC TO-220Fa NPN Power Transistor SpecificationDocument3 pagesSavantIC TO-220Fa NPN Power Transistor SpecificationdavidNo ratings yet

- IRF MOSFET Power TransistorsDocument1 pageIRF MOSFET Power TransistorsDAVE.A.H. SIGINo ratings yet

- Fabrication of CMOS Integrated Circuits: Dae Hyun Kim Eecs Washington State UniversityDocument34 pagesFabrication of CMOS Integrated Circuits: Dae Hyun Kim Eecs Washington State Universityfouzia_qNo ratings yet

- MDS1525Document5 pagesMDS1525mirandowebsNo ratings yet

- NTE36 & NTE37 Silicon Complementary Transistors GuideDocument2 pagesNTE36 & NTE37 Silicon Complementary Transistors GuideHarold Bedoya ValenciaNo ratings yet

- Explain in Brief Flash Memory - : - Sram and DramDocument4 pagesExplain in Brief Flash Memory - : - Sram and DramDivjot BatraNo ratings yet

- Complementary Silicon Power Darlington TransistorsDocument4 pagesComplementary Silicon Power Darlington TransistorsJose ReyesNo ratings yet

- Assignment 1Document2 pagesAssignment 1mid_cycloneNo ratings yet

- Understanding Transistor ActionDocument10 pagesUnderstanding Transistor ActionKurt CargoNo ratings yet

- NPN Epitaxial Silicon Transistor: High Voltage Switch Mode ApplicationDocument1 pageNPN Epitaxial Silicon Transistor: High Voltage Switch Mode ApplicationFrancisco Meza BenavidezNo ratings yet

- Problem 1 - Static Discipline: ( 2 Pages)Document7 pagesProblem 1 - Static Discipline: ( 2 Pages)Night OwlNo ratings yet

- Beee Important QuestionsDocument5 pagesBeee Important Questionssai pranayNo ratings yet

- VLSI BasicsDocument3 pagesVLSI BasicsAlok YadavNo ratings yet

- (English) How A MOSFET Works - With Animation! - Intermediate Electronics (DownSub - Com)Document4 pages(English) How A MOSFET Works - With Animation! - Intermediate Electronics (DownSub - Com)Egis ShegaNo ratings yet

- Lec 1 PDFDocument24 pagesLec 1 PDFJamius SiamNo ratings yet

- 3DigitalLogicFamilies 1Document26 pages3DigitalLogicFamilies 1sakthirsivarajanNo ratings yet

- Performance and Variability-Aware SRAM Design For Gate-All-Around Nanosheets and Benchmark With FinFETs at 3nm Technology NodeDocument4 pagesPerformance and Variability-Aware SRAM Design For Gate-All-Around Nanosheets and Benchmark With FinFETs at 3nm Technology NodeThiago Henrique SantosNo ratings yet

- Unit 13: Chapter 3 - Combinational Logic DesignDocument40 pagesUnit 13: Chapter 3 - Combinational Logic DesignVani YamaniNo ratings yet

- BLHeli Supported Atmel ESCsDocument38 pagesBLHeli Supported Atmel ESCsGustavo BouretNo ratings yet

- Vlsidesign MCQDocument18 pagesVlsidesign MCQAkanksha DixitNo ratings yet

- Body EffectDocument2 pagesBody EffectAtharva Lele100% (1)

- Analytical Transient Response and Propagation Delay Evaluation of The CMOS Inverter For Short-Channel DevicesDocument5 pagesAnalytical Transient Response and Propagation Delay Evaluation of The CMOS Inverter For Short-Channel DevicesSANT SARANNo ratings yet

- NTE2380 & NTE2381 Complementary MOSFETsDocument3 pagesNTE2380 & NTE2381 Complementary MOSFETsOdelis Castro PérezNo ratings yet

- Welcome To EE 130/230M Integrated Circuit DevicesDocument11 pagesWelcome To EE 130/230M Integrated Circuit Devicesnithin UppalapatiNo ratings yet

- 1994 Rohm Short Form CatalogDocument417 pages1994 Rohm Short Form Catalogmcu89s51No ratings yet

- 15A04802 Low Power VLSI Circuits & SystemsDocument1 page15A04802 Low Power VLSI Circuits & SystemsMALLAVARAPU NARASAREDDYNo ratings yet

- 200 mW NPN Transistor SpecificationDocument2 pages200 mW NPN Transistor SpecificationVũ Huy Nhật MinhNo ratings yet