Professional Documents

Culture Documents

Cad Lab Cmos Inverter PDF

Uploaded by

pcjoshi02Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Cad Lab Cmos Inverter PDF

Uploaded by

pcjoshi02Copyright:

Available Formats

Suraj Kamya: CAD Lab Exp-02

1 of 4

http://kamyasuraj.blogspot.in/p/cad-lab-exp-02.html

Suraj Kamya

kamyasuraj@yahoo.com +91-9871989941

Home

Classroom Resource

Blog Archive

Labs

MATLAB Tutorials

Workshops

Contact

Follow by Email

EXPERIMENT 02

November (1)

April (1)

Resource & Downloads

CAD Lab Exp-02

2015 (2)

PCB Lab

Questions

Publications

Objective

a.) Transient Analysis of CMOS Inverter using step input.

b.) Transient Analysis of CMOS Inverter using pulse input.

c.) DC Analysis (VTC) of CMOS Inverter.

Software used QUCS (Quite Universal Circuit Simulator)

Followers

with Google Friend Connect

Theory

About Me:

Assistant Professor

IIMT Group of Colleges,

Greater Noida.

July,2014 - Current

MATLAB Consultant

DUCAT, Noida

June, 2013 - July 2014

Linked-in Profile

MATLAB Central Author

Profile

MATLAB Video Lectures

CMOS inverters (Complementary NOSFET Inverters) are some of the most widely used and

adaptable MOSFET inverters used in chip design. They operate with very little power loss and at

relatively high speed.

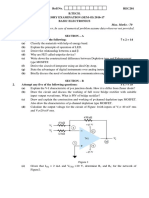

A CMOS inverter contains a PMOS and a NMOS transistor connected at the drain and gate

terminals, a supply voltage VDD at the PMOS source terminal, and a ground connected at the NMOS

source terminal, were VIN is connected to the gate terminals and VOUT is connected to the drain

terminals.(See diagram)

Already a member? Sign in

The circuit below is the simplest CMOS logic gate.

Total Pageviews

869 1

Members (11)

When a low voltage (0 V) is applied at the input, the top transistor (P-type) is conducting

(switch closed) while the bottom transistor behaves like an open circuit.

Therefore, the supply voltage (5 V) appears at the output.

Conversely, when a high voltage (5 V) is applied at the input, the bottom transistor (N-type)

is conducting (switch closed) while the top transistor behaves like an open circuit.

Hence, the output voltage is low (0 V).

The function of this gate can be summarized by the following table:

Input Output

High Low

Low High

The output is the opposite of the input - this gate inverts the input.

Notice that always one of the transistors will be an open circuit and no current flows from

the supply voltage to ground.

Transistor Switch Model

The switch model of the MOSFET transistor is defined as follows:

MOSFET Condition MOSFET State of

MOSFET

NMOS

Vgs<Vtn

OFF

NMOS

Vgs>Vtn

ON

PMOS

Vsg<Vtp

OFF

PMOS

Vsg>Vtp

ON

When VIN is low, the NMOS is "off", while the PMOS stays "on": instantly charging VOUT to logic

04/03/2016 01:30 PM

Suraj Kamya: CAD Lab Exp-02

2 of 4

http://kamyasuraj.blogspot.in/p/cad-lab-exp-02.html

high. When Vin is high, the NMOS is "on and the PMOS is "on: draining the voltage at VOUT to logic

low.

1.

2.

3.

4.

5.

Procedure

Select the components from the library & connect the circuit as shown in figure.

Set simulation parameters for DC & Transient simulation; set parameters as shown wherever required. (Enter timing

values)

Start the Simulation.

Insert the Cartesian Coordinate & Tabular entities to analyse results.

Select the output parameters to display on visual entities.

Circuit diagrams & Output waveforms

Figure a) DC analysis, VTC characteristics of CMOS inverter.

Figure b) Output Waveform DC analysis, VTC characteristics of CMOS inverter.

04/03/2016 01:30 PM

Suraj Kamya: CAD Lab Exp-02

3 of 4

http://kamyasuraj.blogspot.in/p/cad-lab-exp-02.html

Figure c) Transient analysis of CMOS Inverter using Rectangular Pulse.

Figure d) Output Waveform of Transient analysis of CMOS Inverter using Rectangular Pulse.

Figure e) Transient analysis of CMOS Inverter using Step Pulse.

04/03/2016 01:30 PM

Suraj Kamya: CAD Lab Exp-02

4 of 4

http://kamyasuraj.blogspot.in/p/cad-lab-exp-02.html

Figure f) Output Waveform of Transient analysis of CMOS Inverter using Step Pulse.

Recommend this on Google

No comments:

Post a Comment

Comment as:

Publish

Notify me

Home

Subscribe to: Posts (Atom)

Template images by Airyelf. Powered by Blogger.

04/03/2016 01:30 PM

You might also like

- GEHealthcare Education TiP App Library CT AutomA SmartmA TheoryDocument5 pagesGEHealthcare Education TiP App Library CT AutomA SmartmA Theoryfelix perezNo ratings yet

- GSM Gateway User ManualDocument19 pagesGSM Gateway User ManualKen RoseNo ratings yet

- Open MRI Scanner APERTO LucentDocument2 pagesOpen MRI Scanner APERTO LucentnylashahidNo ratings yet

- CT Acr 464 Phantom: Leverage A Sophisticated Design To Comply With Guidelines, and MoreDocument2 pagesCT Acr 464 Phantom: Leverage A Sophisticated Design To Comply With Guidelines, and MoreRogelio Pérez Argüello50% (2)

- M1vj5000tr10en1 PDFDocument81 pagesM1vj5000tr10en1 PDFMuhammad Firdaus0% (2)

- Elscint: CT Twin Flash - Data SheetDocument13 pagesElscint: CT Twin Flash - Data SheetCarlos R. SanchezNo ratings yet

- Daily QA™ 3 User's GuideDocument40 pagesDaily QA™ 3 User's Guideruben50% (2)

- Adaptive Segmentation Algorithm Based On Level Set Model in Medical ImagingDocument9 pagesAdaptive Segmentation Algorithm Based On Level Set Model in Medical ImagingTELKOMNIKANo ratings yet

- QA of LINAC MachinesDocument11 pagesQA of LINAC MachinesWaqar AhmedNo ratings yet

- Hitachi Medical Systems America, Inc.: OASIS Mark II - Standard DetailsDocument30 pagesHitachi Medical Systems America, Inc.: OASIS Mark II - Standard DetailsismailNo ratings yet

- High Frequency X-RayDocument8 pagesHigh Frequency X-RayAshish ChauhanNo ratings yet

- X-Ray Generator Circuits GuideDocument24 pagesX-Ray Generator Circuits GuideThyago MangueiraNo ratings yet

- Siemens: Klinoskop With Explorator HDocument7 pagesSiemens: Klinoskop With Explorator HRichu UhcirNo ratings yet

- Acspl Software Guide Revision 3 00Document353 pagesAcspl Software Guide Revision 3 00Zlatko Slavov50% (2)

- Catalogo IAE 2018-SpanishDocument39 pagesCatalogo IAE 2018-SpanishRezme MbarekNo ratings yet

- Dynamitron - October 2016 - WebDocument12 pagesDynamitron - October 2016 - WebChilmy Coklat SusuNo ratings yet

- Quality Assurance of Computed and Digital Radiography SystemsDocument6 pagesQuality Assurance of Computed and Digital Radiography SystemsYuda FhunkshyangNo ratings yet

- 2014 02 28 Item 2 AERB IBA Radiation Safety AspectsDocument27 pages2014 02 28 Item 2 AERB IBA Radiation Safety AspectsSUBHANo ratings yet

- Kew Snap: Instruction ManualDocument24 pagesKew Snap: Instruction ManualClaudio CostaNo ratings yet

- ULTRASONIX-Sonix OPDocument2 pagesULTRASONIX-Sonix OPWaheed MidoNo ratings yet

- 2012 Microscope LiteratureDocument8 pages2012 Microscope Literaturekostia1No ratings yet

- SIMIND ManualDocument64 pagesSIMIND ManualMariana CarvalhoNo ratings yet

- Service Manual Philips LCD Monitor 150P4 PDFDocument80 pagesService Manual Philips LCD Monitor 150P4 PDFEngr. Irfan JamshedNo ratings yet

- Electrocardiografo IVY BIOMEDICAL 7800 (Manual)Document53 pagesElectrocardiografo IVY BIOMEDICAL 7800 (Manual)Kaira Romero VivancoNo ratings yet

- ENG - 6916000203 - Rev11 (Technical Manual)Document102 pagesENG - 6916000203 - Rev11 (Technical Manual)l.n.a.92No ratings yet

- 2007 Sep-15 PDFDocument16 pages2007 Sep-15 PDFShine PrabhakaranNo ratings yet

- Space Vector Modulation of Multi-Level and Multi-Module Converters For High Power ApplicationsDocument176 pagesSpace Vector Modulation of Multi-Level and Multi-Module Converters For High Power ApplicationsharkoneneNo ratings yet

- Amplivox CA 850-2 ManualDocument55 pagesAmplivox CA 850-2 ManualPraistonNo ratings yet

- Mi-4498 - Iqspect Minimizng Dose - 152085439Document20 pagesMi-4498 - Iqspect Minimizng Dose - 152085439Huang XinbeiNo ratings yet

- Truebeam CollimationDocument6 pagesTruebeam Collimationzhen yongjieNo ratings yet

- Elekta Infinity™ BrochureDocument12 pagesElekta Infinity™ BrochureDC ShekharNo ratings yet

- Fischer X-Ray Florescence TesterDocument10 pagesFischer X-Ray Florescence TesterTravis WoodNo ratings yet

- Opt For Performance and Price: Mobilediagnost OptaDocument4 pagesOpt For Performance and Price: Mobilediagnost OptaBiomedica vmNo ratings yet

- Lecture 2: RF Power: DR G Burt Lancaster University EngineeringDocument33 pagesLecture 2: RF Power: DR G Burt Lancaster University EngineeringTheano XirouchakiNo ratings yet

- Canon CT Scanner Aquilion Lightning 16 Row 32 Slic - 230621 - 220413Document8 pagesCanon CT Scanner Aquilion Lightning 16 Row 32 Slic - 230621 - 220413louis louisNo ratings yet

- HF-110A and HF-110AM: Operator I Installation I Service ManualDocument41 pagesHF-110A and HF-110AM: Operator I Installation I Service ManualVremedSoluCionesNo ratings yet

- Reference Book: Stewart C.bushong: by Huzaifa Atique Sir Syed University of Engineering & TechnologyDocument20 pagesReference Book: Stewart C.bushong: by Huzaifa Atique Sir Syed University of Engineering & TechnologyquickdannyNo ratings yet

- MIM Service Manual v5 0Document374 pagesMIM Service Manual v5 0Iranildo BarbosaNo ratings yet

- High Performance CT For All: Philips MX 16-Slice CT ConfigurationDocument12 pagesHigh Performance CT For All: Philips MX 16-Slice CT ConfigurationAliali MohamedNo ratings yet

- Sumo Robot PCB AssemblyDocument15 pagesSumo Robot PCB AssemblyBayu Kresna WiratamaNo ratings yet

- FCR Users GuideDocument58 pagesFCR Users GuideNelson J Silva ANo ratings yet

- Stonelith V5Document9 pagesStonelith V5Wistara Zavier Wahyu100% (1)

- Truck X Ray MachineDocument2 pagesTruck X Ray MachinehusnikhalilNo ratings yet

- UNIDOSwebline User ManualDocument122 pagesUNIDOSwebline User Manualchintya_cuteNo ratings yet

- Inspection Report-Siemens Sensation 64Document3 pagesInspection Report-Siemens Sensation 64tivoxNo ratings yet

- Dixion EngDocument24 pagesDixion Engiman hilmanNo ratings yet

- IFM-500 service manual repair guideDocument82 pagesIFM-500 service manual repair guiderudyvarsaNo ratings yet

- P-PPC40-510-001 05 PPC40 User's GuideDocument19 pagesP-PPC40-510-001 05 PPC40 User's GuideFisica TacuaremboNo ratings yet

- Specifications For S8V High-Performance Color System: The Pinoeer of Color Doppler Ultrasound in China Product OverviewDocument14 pagesSpecifications For S8V High-Performance Color System: The Pinoeer of Color Doppler Ultrasound in China Product Overviewscuby6600% (1)

- Site Pre-Planning Guidelines Xstrahl 200Document78 pagesSite Pre-Planning Guidelines Xstrahl 200Олександр КорнійчукNo ratings yet

- Product Information: Rotanode™ E79016XDocument14 pagesProduct Information: Rotanode™ E79016XKamilNo ratings yet

- Pansw Ecg Trunk CableDocument13 pagesPansw Ecg Trunk CableAdam LiuNo ratings yet

- Instruction Manual: X-Ray Dose Meter / Exposure Time MeterDocument13 pagesInstruction Manual: X-Ray Dose Meter / Exposure Time MeterRafa TejedaNo ratings yet

- Optima NM/CT 640: Nuclear Medicine Imaging SystemDocument147 pagesOptima NM/CT 640: Nuclear Medicine Imaging SystemarielcondorizarateNo ratings yet

- Luminos Fusion: The 2-In-1 System That Fits Your Needs and Fits Your BudgetDocument16 pagesLuminos Fusion: The 2-In-1 System That Fits Your Needs and Fits Your BudgeteryNo ratings yet

- X-Ray Tube Assembly Installation Manual 133228-000Document64 pagesX-Ray Tube Assembly Installation Manual 133228-000Patou PatriceNo ratings yet

- E-Cube Line Up CatalogDocument16 pagesE-Cube Line Up CatalogJose QuiscaNo ratings yet

- CM X-Ray Film Processor PPDocument19 pagesCM X-Ray Film Processor PPamelia kartikaNo ratings yet

- Active Disturbance Rejection Control for Nonlinear Systems: An IntroductionFrom EverandActive Disturbance Rejection Control for Nonlinear Systems: An IntroductionNo ratings yet

- 7 Limbs of StateDocument8 pages7 Limbs of Statepcjoshi02No ratings yet

- Crystal DefectsDocument7 pagesCrystal Defectspcjoshi02No ratings yet

- B.Tech EC Syllabus 3rd YearDocument35 pagesB.Tech EC Syllabus 3rd Yearpcjoshi02No ratings yet

- OpAmp ExampleDocument16 pagesOpAmp ExampleYi Ming Tan100% (1)

- Asm 1Document5 pagesAsm 1Jagan RajendiranNo ratings yet

- B.Tech EC Final YearDocument18 pagesB.Tech EC Final Yearpcjoshi02No ratings yet

- Time: 3 Hours Max. Marks: 70 Note: Be Precise in Your Answer. in Case of Numerical Problem Assume Data Wherever Not ProvidedDocument2 pagesTime: 3 Hours Max. Marks: 70 Note: Be Precise in Your Answer. in Case of Numerical Problem Assume Data Wherever Not Providedpcjoshi02No ratings yet

- Electronics Engineering SyllabusDocument1 pageElectronics Engineering Syllabuspcjoshi02No ratings yet

- Attempt All Sections. If Require Any Missing Data Then Choose SuitablyDocument3 pagesAttempt All Sections. If Require Any Missing Data Then Choose Suitablypcjoshi02No ratings yet

- Bipolar Junction TransistorsDocument50 pagesBipolar Junction Transistorspcjoshi02No ratings yet

- Electronics Engineering SyllabusDocument1 pageElectronics Engineering Syllabuspcjoshi02No ratings yet

- OpAmp ExampleDocument16 pagesOpAmp ExampleYi Ming Tan100% (1)

- Advance Digital Design Using VeilogDocument99 pagesAdvance Digital Design Using Veilogpcjoshi02No ratings yet

- Memorijski SustaviDocument70 pagesMemorijski SustaviKarlo KneževićNo ratings yet

- 31 Analysis Design Asynchronous Sequential Circuits PDFDocument72 pages31 Analysis Design Asynchronous Sequential Circuits PDFpcjoshi02No ratings yet

- Biquad Filter PDFDocument5 pagesBiquad Filter PDFpcjoshi02No ratings yet

- Memorijski SustaviDocument70 pagesMemorijski SustaviKarlo KneževićNo ratings yet

- Memorijski SustaviDocument70 pagesMemorijski SustaviKarlo KneževićNo ratings yet

- Biquad Filter Design PDFDocument5 pagesBiquad Filter Design PDFpcjoshi02No ratings yet

- Research Methodology MCQ of Pune UniversityDocument22 pagesResearch Methodology MCQ of Pune UniversityABHIJIT S. SARKAR86% (21)

- AddadadaDocument2 pagesAddadadapcjoshi02No ratings yet

- Research-Methods MCQ BookletDocument17 pagesResearch-Methods MCQ Bookletbecbellary73% (11)

- Suraj PDFDocument8 pagesSuraj PDFpcjoshi02No ratings yet

- ECD Lab NEC 752Document17 pagesECD Lab NEC 752pcjoshi02No ratings yet

- Patient Monitoring with GSMDocument8 pagesPatient Monitoring with GSMpcjoshi02No ratings yet

- Assembling and Running An 8051 ProgramDocument5 pagesAssembling and Running An 8051 Programpcjoshi02No ratings yet

- ECD Lab NEC 752Document17 pagesECD Lab NEC 752pcjoshi02No ratings yet

- 8051 Instruction SetDocument5 pages8051 Instruction Setpcjoshi02No ratings yet

- CAD LAB Experiments PDFDocument58 pagesCAD LAB Experiments PDFpcjoshi02No ratings yet

- GM 8.8L Engine Serv PartsDocument84 pagesGM 8.8L Engine Serv PartsKevin DampmanNo ratings yet

- CB SCV NovDocument2 pagesCB SCV NovAhmed Abd ElkaderNo ratings yet

- FA87Document5 pagesFA87IFLYNo ratings yet

- Robertsons Catalogue 2014 Section 08Document38 pagesRobertsons Catalogue 2014 Section 08Cornelius SebastianNo ratings yet

- Renault Koleos BrochureDocument4 pagesRenault Koleos BrochureArreva7474No ratings yet

- Control ComponentsDocument74 pagesControl ComponentsJothi PriyaNo ratings yet

- Memory Built-In Self-Repair Using Redundant WordsDocument7 pagesMemory Built-In Self-Repair Using Redundant Wordsaditya_pundirNo ratings yet

- BetastarDocument66 pagesBetastarSamuel MorenoNo ratings yet

- Wall Mounted CHW FCU CatalogueDocument48 pagesWall Mounted CHW FCU Cataloguesaw1511985No ratings yet

- 2 3+Steering+SystemDocument74 pages2 3+Steering+SystembledmikifrNo ratings yet

- Ficha Tecnica Siemens 6es7223-1ph32-0xb0Document3 pagesFicha Tecnica Siemens 6es7223-1ph32-0xb0ferbaq48No ratings yet

- Solar Agro Sprayer: Non-Polluting Pesticide ApplicatorDocument4 pagesSolar Agro Sprayer: Non-Polluting Pesticide ApplicatormanikantaNo ratings yet

- Instruction Manual: Operates With ISO9001 Certified Quality SystemDocument13 pagesInstruction Manual: Operates With ISO9001 Certified Quality SystemdomagojNo ratings yet

- NMDC Limited Hyderabad: Slurry Pipeline, Iron Ore Beneficiation Plant, Pellet Plant and Water Pipeline ProjectDocument935 pagesNMDC Limited Hyderabad: Slurry Pipeline, Iron Ore Beneficiation Plant, Pellet Plant and Water Pipeline Projectarindam_925024954No ratings yet

- 1104D-44Tg2 1104D-44Tg3 Electropak: SeriesDocument10 pages1104D-44Tg2 1104D-44Tg3 Electropak: SeriesDede R KurniawanNo ratings yet

- Moog G122-829-001 - Catalog1Document2 pagesMoog G122-829-001 - Catalog1Jean-Roch JacquesNo ratings yet

- Install and operate your air conditionerDocument56 pagesInstall and operate your air conditionerIvan CaicedoNo ratings yet

- Simple Machines ExercisesDocument3 pagesSimple Machines Exercisesyensy morel ureñaNo ratings yet

- Prodvx Appc-10dskplDocument1 pageProdvx Appc-10dskplJavier NavarroNo ratings yet

- Seilzugschalter Kiepe PRS GBDocument30 pagesSeilzugschalter Kiepe PRS GBPatricio TamayoNo ratings yet

- Spigot Saddles: Frialen Safety FittingsDocument2 pagesSpigot Saddles: Frialen Safety FittingsAlbertoNo ratings yet

- Massey FERGUSONDocument67 pagesMassey FERGUSONvivek6020100% (4)

- Safety inspection checklist for bar cutting and bending machineDocument14 pagesSafety inspection checklist for bar cutting and bending machinepartha50% (2)

- SKI-DOO Engine Leak Test (SUMMIT X) - Shop Manual - 04cciLAAQ - SM11Y015S01 - enDocument5 pagesSKI-DOO Engine Leak Test (SUMMIT X) - Shop Manual - 04cciLAAQ - SM11Y015S01 - enHannu LeinonenNo ratings yet

- How To Read Capacitance Values On A Capacitor - B - DummiesDocument4 pagesHow To Read Capacitance Values On A Capacitor - B - DummiesVikas KumarNo ratings yet

- SONY LCD TV Bravia KLV-S26A10Document80 pagesSONY LCD TV Bravia KLV-S26A10Ricardo Chaman ChavezNo ratings yet

- Operating Manual: LKHSP Self-Priming Centrifugal PumpDocument15 pagesOperating Manual: LKHSP Self-Priming Centrifugal Pumppablo ortizNo ratings yet

- Workshop Manual Octavia Engine Mechanics 1Document72 pagesWorkshop Manual Octavia Engine Mechanics 1Shriram Iyer100% (2)

- AVA5-50FX Product SpecificationsDocument5 pagesAVA5-50FX Product SpecificationsPhi FeiNo ratings yet

- Omeik MotorDocument2 pagesOmeik MotornmulyonoNo ratings yet