Professional Documents

Culture Documents

Lab #1 FPGA

Uploaded by

Oscar SevCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lab #1 FPGA

Uploaded by

Oscar SevCopyright:

Available Formats

UNIVERSIDAD NACIONAL DE INGENIERA

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Dept. Sist. Digitales y Telecomunicaciones

Electrnica Digital I

Prctica No. 1. Introduccin al entorno ISE de Xilinx

Datos de la prctica

Carrera

Semestre

Tipo de Prctica

Asignatura

Unidad Temtica

N Alumnos por prctica

Nombre del Profesor

Nombre(s) de Alumno(s)

Tiempo estimado

Comentarios

INGENIERA ELECTRNICA

Grupo

Laboratorio

Simulacin

Fecha

Electrnica Digital I

2

N Alumnos por reporte

1.

2.

Vo. Bo. Profesor

Objetivo

Familiarizar al usuario en el uso del ambiente de software integrado

Xilinx ISEv14.7 Project Navigator y el kit de desarrollo Basys2

mediante la creacin de un programa de lgica combinacional y su

respectiva simulacin.

Medios a utilizar

Por cada prctica y por cada puesto de laboratorio, los materiales a

utilizar es:

Cantidad

1

1

1

Descripcin

Computadora

Tarjeta de desarrollo Basys2 Digilent

Software Xilinx ISE Webpackv14.7

Introduccin

Los circuitos digitales presentan dos estados, un estado se aproxima a

cero volts (low) y el otro estado suministra el voltaje (high) y se pueden

procesar en nmeros binarios, en este caso 1 o 0.

Los circuitos digitales pueden estar conectados entre s por medio de

compuertas digitales bsicas: OR, NOR, AND y tambin por medio de las

compuertas no bsicas como NAND, NOR, OR exclusiva y NOR exclusiva.

En esta prctica de laboratorio se implementan las compuertas: AND,

UNIVERSIDAD NACIONAL DE INGENIERA

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Dept. Sist. Digitales y Telecomunicaciones

Electrnica Digital I

OR y XOR. El programa consiste en describir tres salidas c, d y e como la

combinacin lgica de las entradas a y b. As, c = a+b, d = a*b y e = a

b.

Actividades previas

Completar la tabla de las compuertas bsicas AND, OR y XOR con las

ecuaciones descritas anteriormente.

Entradas

a

0

0

1

1

b

0

1

0

1

Salidas

d

Desarrollo de la prctica

Creacin de un proyecto en Project Navigator

1. Abrir Xilinx-ISE.

2. Cerrar cualquier programa que est abierto (File Close Project).

3. Abrir un nuevo proyecto (File New Project). Escribir el nombre del

proyecto y presionar en la pestaa Next.

UNIVERSIDAD NACIONAL DE INGENIERA

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Dept. Sist. Digitales y Telecomunicaciones

Electrnica Digital I

4. Asegurar que las propiedades del proyecto son iguales a la de la

figura y presionar la pestaa Next.

UNIVERSIDAD NACIONAL DE INGENIERA

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Dept. Sist. Digitales y Telecomunicaciones

Electrnica Digital I

5. En la siguiente ventana, clic en la pestaa Finish.

6. Crear una nueva fuente. En la ventana Sources clic derecho en la

carpeta y seleccionar New Source y presionar Next.

UNIVERSIDAD NACIONAL DE INGENIERA

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Dept. Sist. Digitales y Telecomunicaciones

Electrnica Digital I

7. Elegir la opcin VHDL Module, en File name escribir Compuertas y

presionar Next.

8. En la siguiente ventana definimos las entradas y salidas del mdulo.

Las variables a y b estn definidas como entradas (input) y las

variables c, d y e como salida (output).

UNIVERSIDAD NACIONAL DE INGENIERA

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Dept. Sist. Digitales y Telecomunicaciones

Electrnica Digital I

9. Clic en todas las dems opciones: Next Finish.

10. En la ventana Sources verificar que aparezca el dispositivo y el

mdulo principal.

11. En

la ventana de edicin aparece las partes del cdigo VHDL, en el

cual contienen las libreras, la entidad y la arquitectura.

Libreras

Entidad

Arquitectura

12. Guardar los cambios en el cdigo, realizados en el paso anterior.

UNIVERSIDAD NACIONAL DE INGENIERA

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Dept. Sist. Digitales y Telecomunicaciones

Electrnica Digital I

13. Seleccionar el mdulo principal en la ventana Sources.

14. En Processes, elegir Synthesize-XST en el ms desplegable, clic

derecho en la opcin Check Syntax y elegir Rerun All.

15. En la ventana Console, verificar que aparezca el siguiente mensaje.

Nota: El proceso verifica que no haya errores de sintaxis, de haberlo hay

que corregir.

UNIVERSIDAD NACIONAL DE INGENIERA

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Dept. Sist. Digitales y Telecomunicaciones

Electrnica Digital I

Simulacin de un circuito digital

Durante la simulacin en HDL, el software verifica la funcionalidad y la

temporizacin del circuito como parte del proceso de diseo. Primero

hay que tener una descripcin del circuito a realizar a travs del

lenguaje VHDL. La simulacin es un proceso iterativo, es decir que

puede ser un proceso repetitivo hasta que la funcionalidad del tiempo y

del diseo sea satisfactorio.

1. Una vez verificado la sintaxis, el siguiente paso sera la simulacin,

en el cual crearemos un nuevo archivo VHDL del tipo VHDL Test

Bench. Para poder hacerlo se agrega una nueva fuente New

Source y escogemos el tipo de archivo el cual llamaremos

Compuertas_tb.

2. En Design, escoger en modo Simulation.

UNIVERSIDAD NACIONAL DE INGENIERA

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Dept. Sist. Digitales y Telecomunicaciones

Electrnica Digital I

3. Aparece en la ventana principal lo siguiente

4. Comentar las lneas referentes a circuitos de reloj con las lneas --.

5. Aadir las siguientes lneas despus del cometario --Insert

stimulus here y antes de la sentencia end.

a <=

b <=

wait

a <=

b <=

wait

a <=

b <=

wait

a <=

b <=

wait

'0';

'1';

for 100

'1';

'0';

for 100

'1';

'1';

for 100

'0';

'0';

for 100

ns;

ns;

ns;

ns;

6. Seleccionar Compuertas_tb.vhd en la ventana Sources.

UNIVERSIDAD NACIONAL DE INGENIERA

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Dept. Sist. Digitales y Telecomunicaciones

Electrnica Digital I

7. Clic derecho en Behavioral Check Syntax Processes Rerun All.

Aparece la siguiente ventana, clic en Yes.

8. Verificar que aparezca un

en Behavioral Check Syntax, elegir la

opcin Simulate Behavioral Model y clic derecho en Run.

9. Aparece la ventana ISim Simulator donde se muestra la forma de

onda de los estmulos agregados en el paso 6.

UNIVERSIDAD NACIONAL DE INGENIERA

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Dept. Sist. Digitales y Telecomunicaciones

Electrnica Digital I

Utilizar la herramienta Zoom to Full View para ver la vista completa de la

simulacin, que se encuentra a la derecha en la barra de herramientas

del panel de simulacin.

En la ventana Wave Window donde se visualiza la configuracin de las

formas de onda, que contienen la lista de las seales y su forma de

onda1.

10. Mover la lnea amarilla sobre las formas de onda (de color verde) y

ver en el cuadro Value que los valores de las seales cambian.

Comprobar que las formas de onda de la figura anterior

corresponden a las tablas de verdad de las compuertas bsicas

hechas en el cdigo.

Asignacin de los pines en la tarjeta Basys2

1. En el modo Implementation, dar clic derecho en Compuertas.vhd y

elegir New Source...

1

Ms

informacin?

Visita

http://www.xilinx.com/support/documentation/sw_manuals/xilinx12_2/plugin_ism.pd

f

UNIVERSIDAD NACIONAL DE INGENIERA

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Dept. Sist. Digitales y Telecomunicaciones

Electrnica Digital I

2. Elegir la opcin Implementation Constraints File, en File Name

escribir Compuertas, clic en Next Finish.

3. En la ventana Sources, verificar que la nueva fuente que acabamos

de crear aparece debajo del mdulo principal.

UNIVERSIDAD NACIONAL DE INGENIERA

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Dept. Sist. Digitales y Telecomunicaciones

Electrnica Digital I

4. Dar doble click en el archivo Compuertas.ucf y aparecer un editor

de texto en blanco en la ventana principal

5. Escribir lo siguiente en el archivo .ucf

net

net

net

net

net

"a"

"b"

"c"

"d"

"e"

loc

loc

loc

loc

loc

=

=

=

=

=

"L3" ;

"P11";

"P7" ;

"M11";

"M5" ;

6. Seleccionar en la ventana Sources el mdulo

Compuertas.vhd, en la ventana Processes elegir

Programming File y doble clic en la opcin Rerun All.

principal

Generate

UNIVERSIDAD NACIONAL DE INGENIERA

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Dept. Sist. Digitales y Telecomunicaciones

Electrnica Digital I

7. Verificar que aparezca el smbolo

en los procesos

seleccionamos en el paso anterior de la ventana Processes.

que

8. Verificar que en la ventana Console aparezca el siguiente mensaje:

Programacin del chip de FPGA

UNIVERSIDAD NACIONAL DE INGENIERA

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Dept. Sist. Digitales y Telecomunicaciones

Electrnica Digital I

1. Conectar el kit de entrenamiento Basys2 mediante el

cable USB a la computadora, elegir las opciones para

que la computadora lo instale automticamente.

2. Buscar en el Inicio todos los programasDigilent

3. Si el kit est conectado correctamente se indicar en la siguiente

ventana.

4. En la pestaa Browse buscar el archivo Compuertas.bit en el

directorio que guardamos a la hora de crear el proyecto (ver en la

parte superior de ISE) y pulsar Program.

5. Cambiar de posicin los switches SW1 y SW0 (las variables de

entrada a y b) y comprobar que los LEDs actan correctamente (LD2

como OR, LD1 como AND, y LD0 como XOR).

6. Estas lneas significan la ubicacin de las entradas y las salidas en la

tarjeta Basys2. Las entradas son los switches

UNIVERSIDAD NACIONAL DE INGENIERA

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Dept. Sist. Digitales y Telecomunicaciones

Electrnica Digital I

7. y las salidas las visualizaremos con los leds.

Actividades propuestas

Prctica

Llene la tabla de verdad segn las ecuaciones dadas y realice la

descripcin de las combinaciones lgicas en un programa de VHDL.

Verifique que la sintaxis del programa es correcta utilizando los pasos

descritos anteriormente incluyendo su simulacin.

x

0

0

0

0

1

1

1

1

Entradas

y

z

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

Salidas

a=( x + y )z

1

1

1

0

1

0

1

0

b=x y z

UNIVERSIDAD NACIONAL DE INGENIERA

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Dept. Sist. Digitales y Telecomunicaciones

Electrnica Digital I

Actividades de aprendizaje

1. En una compuerta and de 2 entradas; si en una de sus entradas

recibe un 0 y en la otra un 1, Cul es su salida?

2. Si una compuerta Nand recibe las mismas seales de entrada de la

pregunta anterior, Cul es su salida?

3. Explique por qu es til simular un sistema o un circuito. Considera

importante simular un circuito electrnico descrito con programacin?

4. Cuando hacemos la simulacin de un circuito, es necesario

especificar la magnitud del retardo entre las seales de entrada y las

seales de salida? Justifique su repuesta.

5. Qu sucede si cambia los tiempos de temporizacin? Cambiar #100

a #50 en el programa que hizo en la prctica.

Reporte de Laboratorio

El reporte se entregara en un archivo comprimido y deber incluir:

Tabla de verdad de las variables.

Descripcin de las ecuaciones con compuertas lgicas.

Descripcin de las ecuaciones en VHDL.

Verificacin del programa en ISE. Utilice las capturas de pantalla

(tecla: PRTSC) para explicar el procedimiento.

Resultados de la simulacin.

You might also like

- Manual de Uso Redmine PDFDocument30 pagesManual de Uso Redmine PDFOscar Ignacio Ozzkitar100% (2)

- Banco de Preguntas para El Examen Complexivo - Metodologia - Desarrollo de SoftwareDocument12 pagesBanco de Preguntas para El Examen Complexivo - Metodologia - Desarrollo de SoftwareJinna Salazar Vasquez100% (1)

- 34 Proyectos Sencillos de ElectronicaDocument156 pages34 Proyectos Sencillos de ElectronicaPablo Andrés83% (153)

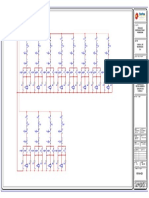

- Diagrama de Iluminación InteriorDocument1 pageDiagrama de Iluminación InteriorOscar SevNo ratings yet

- D-BD2 Diagrama Panel Comederos Hembra PCRH-01-Model3 PDFDocument1 pageD-BD2 Diagrama Panel Comederos Hembra PCRH-01-Model3 PDFOscar SevNo ratings yet

- Diagrama Panel Comederos de PollosDocument1 pageDiagrama Panel Comederos de PollosOscar SevNo ratings yet

- PVC ConduitDocument5 pagesPVC ConduitCarlosTamayoCamposNo ratings yet

- Transistor BJT Respuesta en FrecuenciaDocument6 pagesTransistor BJT Respuesta en FrecuenciaOscar SevNo ratings yet

- BombasDocument10 pagesBombasflorvianneyNo ratings yet

- Fibra24 - Rafael GumucioDocument11 pagesFibra24 - Rafael GumucioBrian RomanNo ratings yet

- Curso NodeJs Basico ESTE ESTA BUENO PARA APRENDERDocument39 pagesCurso NodeJs Basico ESTE ESTA BUENO PARA APRENDEReliezerNo ratings yet

- QRG - Glencore - Planificacion IiDocument81 pagesQRG - Glencore - Planificacion IiddonosoNo ratings yet

- Proyecto 3 CIMENTACIONESDocument6 pagesProyecto 3 CIMENTACIONESElliot UretaNo ratings yet

- Ing. SistemasDocument16 pagesIng. SistemasRosa BacaNo ratings yet

- Carpeta Pedag Ra 2018 OkDocument26 pagesCarpeta Pedag Ra 2018 OkMarco AntonioNo ratings yet

- PLM SostenibleDocument7 pagesPLM SostenibleCristian Felipe AcostaNo ratings yet

- DayanaDocument10 pagesDayanadayana argel borjaNo ratings yet

- Manual MI 2892 Power Master - EspañolDocument210 pagesManual MI 2892 Power Master - EspañolGustavo Pacheco Aparcana67% (3)

- Factores Que Influyen en La Produccion de Anis Año 2013 20141Document138 pagesFactores Que Influyen en La Produccion de Anis Año 2013 20141Mizhii DeiizitaNo ratings yet

- BSD EspañolDocument6 pagesBSD EspañolRODOLFONo ratings yet

- SanchisRequenaEster GN v6Document23 pagesSanchisRequenaEster GN v6estersanchisNo ratings yet

- Resumen Análisis InternoDocument4 pagesResumen Análisis InternoMark Ale Molina BermúdezNo ratings yet

- Guarapachon INTRODUCCION - OBJETIVOS - CONCLUSIONESDocument3 pagesGuarapachon INTRODUCCION - OBJETIVOS - CONCLUSIONESAndrés Lesmes ZamoraNo ratings yet

- Manual OpenDsDocument13 pagesManual OpenDszuputrusNo ratings yet

- Resitencia EstudiantilDocument2 pagesResitencia EstudiantilAntonio Cueva EstradaNo ratings yet

- Sistemas Electricos de Los Autos COMPLETODocument23 pagesSistemas Electricos de Los Autos COMPLETOEmmanuel sanchez “basket98”No ratings yet

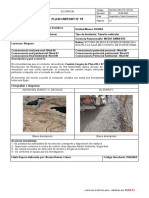

- Flash Report N 75Document1 pageFlash Report N 75Angie MendozaNo ratings yet

- Silberschatz 2002 Fundamentos Bases Datos PP 1 16Document18 pagesSilberschatz 2002 Fundamentos Bases Datos PP 1 16fanyNo ratings yet

- Confi. Estrategica-Scania Final Tarde.Document4 pagesConfi. Estrategica-Scania Final Tarde.Fanny Giovanna Vera AllendeNo ratings yet

- Beas-Flyer-13 2 SpanishDocument8 pagesBeas-Flyer-13 2 SpanishCarlos Davila EcheverriaNo ratings yet

- TOMOGRAFIA0001Document19 pagesTOMOGRAFIA0001Nataly FloresNo ratings yet

- Abreviaturas de Los Edificios Del RUM - Rev Agosto 2022Document4 pagesAbreviaturas de Los Edificios Del RUM - Rev Agosto 2022Carlos FrancoNo ratings yet

- De Mis Hijos Aprendí 212 Historias para EnamorarteDocument346 pagesDe Mis Hijos Aprendí 212 Historias para EnamorarteWally FernándezNo ratings yet

- Silabo de Innovacion Tecnologica de Granos y Tuberculos - ModificadoDocument12 pagesSilabo de Innovacion Tecnologica de Granos y Tuberculos - ModificadoAnonymous ZMaG6DnQ3No ratings yet

- Tarjeta de Adquisición de DatosDocument9 pagesTarjeta de Adquisición de DatosnalleyNo ratings yet

- PROC-G-005 Procedimiento para Atención de Quejas, Apelaciones y No-ConformidadesDocument7 pagesPROC-G-005 Procedimiento para Atención de Quejas, Apelaciones y No-ConformidadesEmily BrockNo ratings yet

- Semana #04 Literarura Empresarial y TecnologicaDocument4 pagesSemana #04 Literarura Empresarial y TecnologicaKarol Sandoval MurayariNo ratings yet

- Trabajo Final - Ing. IndustrialDocument56 pagesTrabajo Final - Ing. IndustrialJuancaNo ratings yet