Professional Documents

Culture Documents

Solar Power Anti-Islanding and Control

Uploaded by

okasinskiCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Solar Power Anti-Islanding and Control

Uploaded by

okasinskiCopyright:

Available Formats

May 2012

Solar Power Anti-Islanding and Control

Theory: Phase Locked Loops belong to a class of nonlinear

circuits that have been studied extensively [1]. When phase

detection is accomplished using a multiplier, the secondorder nonlinear equation can be solved explicitly. PLLs are

used in communications circuits, such as Global Positioning

Systems (GPS) to make a narrow band filter centered about

the carrier frequency. The noise filter, while not part of the

lower frequency phase control loop, is used to eliminate

out of band noise. For this problem, the carrier signal is the

60 Hz mains and it is not particularly noisy, although it may

have some harmonic distortion. The mains frequency is

tightly controlled so that various generators on the grid can

be easily synchronized. The main signal to be eliminated by

the noise filter is the double frequency, 120 Hz, component

that is output by the phase detector. The digital filter used

here reduces this unwanted signal by nearly 40 dB. The

average value of the mains fundamental is detected using

the quadrature signal from the VCO, which is synchronized

to the mains. The following logic is used to indicate that

synchronization has begun; that is, it sets a software flip-flop:

Problem: When connecting a solar power source to the

AC mains it is possible to supply power to the local area in

the event of a power outage. While your neighbors might

be happy with this behavior, it is a hazard to utility workers

attempting to restore power. This affect, called islanding,

must be eliminated in the Grid Tie Inverter design. If a phaselocked oscillator synchronizes the inverter output to the line;

then a power outage results in the inverter synchronizing to

its self. The frequency will then drift out of tolerance, signaling

a power outage. This article describes how to achieve this

design goal using a digital controller and Intusofts DSP

Designer to simulate the digital design and generate some

of the necessary code.

Testing the anti-islanding feature: The U.S.

National Electric Code, NEC, defines a test using a resonant

circuit at the inverter input, which has a Q of 3 at the inverter

maximum power level. The circuit is adjusted so that removal

of the mains power will not be detected instantly. The inverter

will not be overloaded so that in the absence of special

detection circuitry, the solar power will electrify the local grid.

VlinAvg > 78 Volts (86 VRMS) and

abs(frequency-60) < 1) and

(abs)phase < .025 radians (1.4 degrees)

The flip-flop is reset when:

abs(frequency-60) > 2) or

VlinAvg < 72 Volts (79 VRMS)

Block Diagram: Figure 1 is a block diagram of the line

Sin

VCO

Frequency

Control

Cos

ADC

A

A*B

Mains

Noise

Filter

Phase

PI

Controller

Phase

Detectors

A

A*B

B

Noise

Filter

Digital Control Series

VlineAvg

Figure 1, Block Diagram

synchronizing system. Notice that the operation of this system

doesnt depend upon the NEC test condition. The idea is to

synchronize the inverter using a phase-locked-loop, PLL

[1]. If the grid is only supplied by the Inverter, then no error

signal is developed at the phase detector and the frequency

will drift toward zero. When it gets below some pre-defined

limit, the Inverter is shut off until mains power is restored; at

which time the PLL syncs up and solar power generation is

resumed. The logic gets a bit more complex when a battery

backup is included, requiring a switch to isolate the grid from

the backup loads. The traditional PLL controller consists

of a multiplier to detect the phase error, followed by a PI

controller. The large second harmonic signal must be filtered

to reduce non-linearity in the voltage-controlled oscillator,

VCO, and to allow meaningful measurement of phase error,

frequency and line voltage.

The first reset condition accomplishes the antiislanding function when the Inverter is supplying

power to the grid, and the second condition signals

a grid power loss when in standby. The sine output

of the VCO is used to switch synchronous rectifiers

used to transfer power between the grid and the

backup system when a backup battery is present.

Backup systems require transferring power in either

direction to account for load phase shift (motors)

and battery charging, so the use of synchronously

switched rectifiers is required.

Selecting Sample Rates: High sample rates

give improved accuracy but require longer digital

word lengths. Constraining word lengths to 16

bits allows the use of very low cost and low power

digital controllers. For this problem, the sine-cosine

generator is run at the Inverter switching frequency,

which is 25 kHz, a 40 microseconds. That resolves

the line voltage to about 2.5 Volts at zero crossing for

a 120 Volt RMS line. But the PLL can be sampled at

a much lower rate, greater than or equal to 10 times

its loop bandwidth. The communication system for this DSP

runs at 1 kHz, which meets this criteria.

DSP Equations: The DSP equations are formed using a

matrix algebra approach. A SPICE simulator is used to build

up the matrix from the simulation schematics net list. Then

the matrix is ordered from top to bottom, first using unwanted

states, then using the states that need to be computed,

and finally using states that are available as inputs. For a

linear system, the right-hand side of the matrix is constant.

When this matrix is arranged in a triangular form, it can be

solved repeatedly at each sample time by using backward

substitution.

http://www.intusoft.com/dsp/matrix_solution.pdf

Each row in the backward substitution is formed using a

multiply-accumulate series. Scaling is accomplished by

Digital Control Series

scaling the matrix constants up by 2^radix. When the multiply

accumulate is finished, the result is multiplied by 2^-radix and

saved. These saved results are the desired state solutions

and their values are used in subsequent state computations.

All of this can be automated so the only thing that must

be supplied is the radix parameter. The magnitude of the

resulting coefficients lie between 1 and 2^15. If larger than

2^15, the multiply cant be done using 16-bit integers. As the

coefficients approach 1, the pole-zero placement accuracy

is compromised.

programmers language for smoke! It might seem that using

saturation limits in intermediate calculations is a good idea.

However, it is permissible to have intermediate overflows as

long as the resulting state variable doesnt overflow. See:

http://www.intusoft.com/dsp/dsp.pdf pg 16

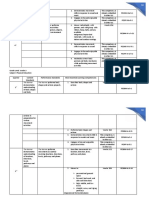

Phase Detector and Filter: The phase detector uses

a multiplier in the classical PLL approach. The filter is a 2nd

order elliptic filter with 1dB ripple and 20 dB attenuation. The

s-plane roots can be calculated using:

www.intusoft.com/filter.htm.

The cutoff frequency is adjusted so the filter notch is at 120

Hz in order to minimize the 2nd harmonic noise. Figure 2

shows the digital realization converting the s-plane roots to

direct programming coefficients using the parameter block

shown in Table 1. An extra pole was added to further reduce

the noise without impacting the PI controller performance.

The circuit was turned into a SPICE subcircuit and added to

a user library. Code was generated for the DSP version of

the circuit [2].

Scaling: Each linear block in the system must be scaled;

that is, the radix and sampling frequency need to be selected.

Sampling frequencies come from a limited set of real time

interrupts. For this problem, they are either 40 kHz or 1 kHz.

Here are the blocks to be scaled:

1. ADC, this block is sampled at 40 kHz because that

is the Inverter switching rate. It is used both here

and for the Inverter control system.

2. PLL noise filter sample rate uses the 1 kHz sample

rate. This is because it is the lowest available

interrupt rate that is greater than 10 times

the PLL bandwidth.

3. Noise filter sampling also uses the 1 kHz

interrupt and sets radix=10

4. The VCO is sampled at 40 kHz because its

sine output is used as the Inverter set point.

Internal scaling uses radix=13.

5. The multiplier is a non-linear block that is

computed at the PLL sample rate. Since it

is non-linear, its solution does not use the

matrix solution technique and is:

Vmul= ((Vline)*(long)zic)/1571

=(((Vline*(long)zic)>>10)*5340)>>13

Vcp

First Stage

Tsample=40 usec

zipd

SUM2

A5

ZDELAY

Z - 1

zopd

X15

K1 = b0

K2 = 1

X13

K1 = a*gain

K2 = 1

zi10

K1

SUM2

2

K1

zo10

X5

K1 = -a2

K2 = -a1

V7

unknown

X14

K1 = b1

K2 = b2

zi32

Z - 1

A6

ZDELAY

tsample = {T}

ic = 0

zo32

Second Stage Tsample=1 msec

Figure 2, Noise Filter

Table 1, Parameters

Parameters

gain=.1

Radix=13

onee=2^Radix; sets quantizing levels

T=1m

Tsc=40u

Fc=37.1; adjust for minimum at 120 Hz

DR=-.5148;pole real part

DI=.9424;pole imaginary part

NR=0; zero real part

NI=3.205; zero imaginary part

BW=2*3.14159*Fc

There is no single right answer to the scaling problem. The

trick is to avoid the wrong answers. Aggressive scaling will

adjust maximum state values close to saturation limits. At

the same time, the quantizing noise will be reduced because

the dynamic range is maximized. If saturation occurs, the

control system can produce unexpected results. Thats

K2

SUM2

SUM2

K2

A7

ZDELAY

tsample = {T}

ic = 0

K2

SUM2

Z - 1

K1

K2

K1

K1

K2

The A to D converter outputs an unsigned 12-bit

value. For DSPs using 10 bits, it is shifted left by 2

places before being used. Subtracting 2048 makes

it a signed number (Vline), accounting for the Vref/2

offset. Casting zic to a long forces the first product

to be a long so that the result doesnt underflow.

The result is automatically changed back to a 16-bit

integer by the C compiler because thats the data

type of Vmul. The 1571 value scales the peak signal

used in the noise filter and accounts for the ADC input

signal conditioning gain. The equation is re-arranged

to eliminate the division as show in 5 above(1/1530

= 5340*2^-23). The noise filter gain is set to prevent

saturation within the filter by using simulation results.

Similarly, the gain of the shaping network is set to

prevent saturation of the internal frequency state

and fine-tunes the over-all loop response. Again, the

adjustment relies on simulation results. The initial condition

of the frequency state is set so the shaping network output,

Vfreq, is 377 rad/sec (2*pi*60 Hz). With that scaling, the gain

of the VCO integrators is Vfreq*Tsc, where Tsc is the sinecosine sampling period.

X12

SUM2

K1 = .01

K2 = .99

ph

Digital Control Series

BW2=BW*BW

D2=1

D1 = -2*DR

D0=DR*DR+DI*DI

N2=1

N1=2*NR

N0=NI*NI+NR*NR

* Quantized Coefficients below

a=floor(onee*D0/N0+.5)/onee

a0=D0*BW2 + D1/T*BW+D2/T/T

a1=-floor(onee*(D1/T*BW+2*D2/T/T)/a0+.5)/onee

a2=floor(onee*D2/T/T/a0+.5)/onee

b0=floor(onee*(N0*BW2 + N1/T*BW+N2/T/T)/a0+.5)/onee

b1=-floor(onee*(N1/T*BW+2*N2/T/T)/a0+.5)/onee

b2=floor(onee*N2/T/T/a0+.5)/onee

ci

K1

A1

ZDELAY

tsample = 40u

ic = 8192

K1

SUM2

K1

SUM2

V1

K2

zos

Z^-1

Notice that B1 and B2 equations were scaled to work with integers.

k2

transient when the VCO phase is 180 degrees out of phase

with the line. At 500msec a line failure is simulated by

connecting the

1

Z^-1

frequency

sine-cosine oscillator. Two integrators are cascaded with the

gain controlled using a non-linear block in series with each

integrator. One of the integrators uses the delayed output for

2 reasons:

1. The total phase lag around the loop must exceed

180 degrees to make an oscillator.

2. The equations need to be broken up to avoid

solving simultaneous equations, so the gain

constants can be used directly.

void vco(void)

{

si= (long)((((long)freq*zoc)>>13)*2684) >> 13 ;

zis=si+zos;

ci = (long)((((long)freq*zis)>>13)*2684) >> 13;

zic=zoc-ci;

zoc=zic;

zos=zis;

if(zos > 8192) {

zos = 8192;

zoc=0;

}

}

v14

v(ph)

v7

Frequency

The VCO: The VCO is implemented using an algorithmic

An automatic gain control, AGC, limiter is used to keep the

oscillation at a constant level. A simple peak detector is used,

its contained within the Zdelay model. Figure 4 shows the

SPICE model and Table 21 shows the C-language code.

59.0

Frequency

zif

Figure 3, PI Controller with Frequency Test Point

Table 2, VCO source code

zic

K2

A3

ZDELAY

tsample = 1m

ic = {ic}

zof

Z^-1

A2

ZDELAY

tsample = 40u

ic = 0

Figure 4, VCO

Plot1

frequency in Hertz

ph

(v(k)*v(zoc)*{Tsc}+.5)

SUM2

K2

Simulation Results: Figure 5 shows the startup

X9

SUM2

K1 = -gain

K2 = Wcn*T

X8

SUM2

K1 = -gain

K2 = .9995

K1

B2

Voltage

K2

zoc

X2

SUM2

K1 = 1

K2 = 1

si

SUM2

The PI Controller: A simple PI controller shown in Figure

3 sets up the control loop. Notice that the internal integrator

has a signal that is proportional to frequency, and it will be

used later on in the anti-islanding logic.

B1

Voltage

X1

SUM2

K1 = -1

K2 = 1

zis

(v(k)*v(zis)*{Tsc}+.5)

1

2

55.0

Vavg Line

51.0

Phase

3

47.0

43.0

Sync

100m 300m 500m 700m 900m

time in seconds

Figure 5, Simulation Results

VCO output to the line input. Notice the frequency drifting out

of tolerance in less than .5 second because the integration

constant, Figure 3 X8:K2, was set slightly less than 1, forcing

the output to decay toward 0 with no error signal.

Test Results: Real time programming is fraught with

unexpected behavior. Thats why; even with the best tools it

takes orders of magnitude more time to program a line of

code. For this problem, several stumbling blocks needed to

be resolved.

1. The 1msec sampled difference equations are

interrupted by the 40 msec interrupt service

request (ISR). Both the 40 msec and 1 msec ISR

use the MAC accumulators. (These implement

special DSP functions for multiply-accumulate.)

Therefore, the 40 msec ISRs needs to push

Digital Control Series

these accumulators onto the stack. When this

is omitted, the resultant VCO signal is erratic.

2. The 60 Hz sync signal test was originally:

1. A new more efficient Z-Transform model that

guarantees convergence

2. Decomposition of the SPICE matrix for DSP code

generation

3. Generic C-Code generation

4. Assembly code for selected DSPs

if((zis > 0) && (zos < 0)){

LATBbits.LATB8 = 0;

}

else if((zis < 0) && (zos > 0)){

LATBbits.LATB8 = 1;

}

and it was changed to:

if((zis > 0) && (zos <= 0)){

LATBbits.LATB8 = 0;

}

else if((zis < 0) && (zos >= 0)){

LATBbits.LATB8 = 1;

}

because the occasional time when zos was

equal to zero caused the sync signal to fail.

3. The 3rd order input filter was originally setup to

first do the elliptic filter section followed by the

first order pole. Both filters were to be done in

the 1ms ISR. However, 1 msec is too granular for

synchronization. And the elliptic filter couldnt be

solved in the 40usec ISR. The filter was revised

to place the pole before the elliptic filter and was

solved in the 40 usec ISR. That combination

satisfied the accuracy and scaling requirements.

4. The PLL gain is proportional to the magnitude of

the input signal. To eliminate gain changes with

power line voltage, the line signal was passed

through limiting code. The limiter includes a

25-sample lockout to de-bounce the output.

References:

[1] Phaselock Techniques, Floyd M. Gardner

[2] Downloads of the detailed design are

available at www.intusoft.com/DigitalPLL.zip.

All of these seemingly minor problems required 2 days

to resolve (6 days real time!) and produced only 40

lines of C code (plus about 100 lines DSP Designer

code).

A test signal was generated using the 40 usec ISR

and was input to the PLL at 60.0962 Hz. Test code

was used to measure peak and RMS noise, using the

deviation of the zos (sine signal) when the sync signal

switched. Results for 1000 samples were:

Peak deviation: 3.9%

RMS deviation: .75%

The test code remains in the source code[2] and can

be activate by including the

#define TESTERROR

line.

Summary: Converting analog technology into a digital

implementation is made easier using Z-Transform models

with SPICE simulation. Moreover, automatic code generation

using a matrix-based solution relieves the designer of

the excruciating job of scaling each multiply-accumulate

operation. It uniquely eliminates unused states by ordering

the unneeded states at the top of the matrix so that backward

substitution ends with the last required stateit simply

doesnt solve for unused states.

These features are unique to ICAP/4 DSP Designer; to

recap:

You might also like

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- 86 Lockout Relay Wiring DiagramDocument4 pages86 Lockout Relay Wiring Diagramokasinski50% (2)

- CIRED2013 0044 FinalDocument4 pagesCIRED2013 0044 FinalokasinskiNo ratings yet

- 86 Lockout Relay Wiring DiagramDocument4 pages86 Lockout Relay Wiring Diagramokasinski50% (2)

- 1MRK502002-UENA en REG 100 Series User S Guide - Part ADocument84 pages1MRK502002-UENA en REG 100 Series User S Guide - Part AokasinskiNo ratings yet

- Influence of Large-Scale PV On Voltage Stability of Sub-Transmission SystemDocument14 pagesInfluence of Large-Scale PV On Voltage Stability of Sub-Transmission SystemokasinskiNo ratings yet

- TechRef ElmGenstatDocument28 pagesTechRef ElmGenstatokasinskiNo ratings yet

- Wind Grid IntegrationDocument4 pagesWind Grid IntegrationokasinskiNo ratings yet

- Development and Validation of WECC Variable Speed Wind Turbine Dynamic Models For Grid Integration StudiesDocument8 pagesDevelopment and Validation of WECC Variable Speed Wind Turbine Dynamic Models For Grid Integration StudiesokasinskiNo ratings yet

- Power Quality Level in 110 KV Networks in The Czech RepublicDocument4 pagesPower Quality Level in 110 KV Networks in The Czech RepublicokasinskiNo ratings yet

- 106 Antila Full PaperDocument6 pages106 Antila Full PaperokasinskiNo ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- SABRE MK-3 CFT Gel SpecDocument1 pageSABRE MK-3 CFT Gel Specseregio12No ratings yet

- Bacacay South Hris1Document7,327 pagesBacacay South Hris1Lito ObstaculoNo ratings yet

- Analytical Chem Lab #3Document4 pagesAnalytical Chem Lab #3kent galangNo ratings yet

- Surgery - 2020 With CorrectionDocument70 pagesSurgery - 2020 With CorrectionBaraa KassisNo ratings yet

- Current Concepts in Elbow Fracture Dislocation: Adam C Watts, Jagwant Singh, Michael Elvey and Zaid HamoodiDocument8 pagesCurrent Concepts in Elbow Fracture Dislocation: Adam C Watts, Jagwant Singh, Michael Elvey and Zaid HamoodiJoão Artur BonadimanNo ratings yet

- Cam 18 Test 3 ListeningDocument6 pagesCam 18 Test 3 ListeningKhắc Trung NguyễnNo ratings yet

- 10 Killer Tips For Transcribing Jazz Solos - Jazz AdviceDocument21 pages10 Killer Tips For Transcribing Jazz Solos - Jazz Advicecdmb100% (2)

- General Chemistry 2 Q1 Lesson 5 Endothermic and Exotheric Reaction and Heating and Cooling CurveDocument19 pagesGeneral Chemistry 2 Q1 Lesson 5 Endothermic and Exotheric Reaction and Heating and Cooling CurveJolo Allexice R. PinedaNo ratings yet

- Aakriti 1Document92 pagesAakriti 1raghav bansalNo ratings yet

- User Manual PM3250Document80 pagesUser Manual PM3250otavioalcaldeNo ratings yet

- DMIT - Midbrain - DMIT SoftwareDocument16 pagesDMIT - Midbrain - DMIT SoftwarevinNo ratings yet

- Ci Thai RiceDocument4 pagesCi Thai RiceMakkah Madina riceNo ratings yet

- Segregation in CastingDocument17 pagesSegregation in CastingAsmaa Smsm Abdallh78% (9)

- Pantalla MTA 100Document84 pagesPantalla MTA 100dariocontrolNo ratings yet

- PE MELCs Grade 3Document4 pagesPE MELCs Grade 3MARISSA BERNALDONo ratings yet

- Ducted Split ACsDocument31 pagesDucted Split ACsHammadZaman100% (1)

- Participants ListDocument13 pagesParticipants Listmailway002No ratings yet

- Curriculum Guide Ay 2021-2022: Dr. Gloria Lacson Foundation Colleges, IncDocument9 pagesCurriculum Guide Ay 2021-2022: Dr. Gloria Lacson Foundation Colleges, IncJean Marie Itang GarciaNo ratings yet

- Agency Canvas Ing PresentationDocument27 pagesAgency Canvas Ing Presentationkhushi jaiswalNo ratings yet

- BIAN How To Guide Developing Content V7.0 Final V1.0 PDFDocument72 pagesBIAN How To Guide Developing Content V7.0 Final V1.0 PDFميلاد نوروزي رهبرNo ratings yet

- Electronic Spin Inversion: A Danger To Your HealthDocument4 pagesElectronic Spin Inversion: A Danger To Your Healthambertje12No ratings yet

- BJAS - Volume 5 - Issue Issue 1 Part (2) - Pages 275-281Document7 pagesBJAS - Volume 5 - Issue Issue 1 Part (2) - Pages 275-281Vengky UtamiNo ratings yet

- Expression of Interest (Consultancy) (BDC)Document4 pagesExpression of Interest (Consultancy) (BDC)Brave zizNo ratings yet

- 1995 Biology Paper I Marking SchemeDocument13 pages1995 Biology Paper I Marking Schemetramysss100% (2)

- Final Selection Criteria Tunnel Cons TraDocument32 pagesFinal Selection Criteria Tunnel Cons TraMd Mobshshir NayeemNo ratings yet

- Experiment - 1: Batch (Differential) Distillation: 1. ObjectiveDocument30 pagesExperiment - 1: Batch (Differential) Distillation: 1. ObjectiveNaren ParasharNo ratings yet

- Knee JointDocument28 pagesKnee JointRaj Shekhar Singh100% (1)

- Retail Banking Black BookDocument95 pagesRetail Banking Black Bookomprakash shindeNo ratings yet

- Module6 Quiz1Document4 pagesModule6 Quiz1karthik1555No ratings yet

- UM-140-D00221-07 SeaTrac Developer Guide (Firmware v2.4)Document154 pagesUM-140-D00221-07 SeaTrac Developer Guide (Firmware v2.4)Antony Jacob AshishNo ratings yet