Professional Documents

Culture Documents

Chandigarh University, Gharuan

Uploaded by

Ankit KumarOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Chandigarh University, Gharuan

Uploaded by

Ankit KumarCopyright:

Available Formats

CHANDIGARH UNIVERSITY, GHARUAN

Experiment-5

Aim: - To design, simulate and synthesize

a) SR Flip Flop

b) T Flip Flop

c) JK Flip Flop

Apparatus: - Xilinx ISE

Theory: a) SR Flip Flop: A flip-flop circuit can be constructed from two NAND gates or two NOR gates. These flip-flops are

shown in Figure. Each flip-flop has two outputs, Q and Q, and two inputs, set and reset. This type

of flip-flop is referred to as an SR flip-flop.

Truth Table: CLK

QBAR

NO CHANGE

NO CHANGE

NO CHANGE

NO CHANGE

Code: library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity sr_ff is

Port ( s,r,clk: in STD_LOGIC;

q,qbar: out STD_LOGIC);

end sr_ff;

architecture Behavioral of sr_ff is

begin

process(s,r,clk)

variable temp : std_logic;

begin

if(clk='1')then

if(s='0' and r='0')then

temp:=temp;

32

CHANDIGARH UNIVERSITY, GHARUAN

elsif(s='0' and r='1')then

temp:='0';

elsif(s='1' and r='0')then

temp:='1';

else

temp:='Z';

end if;

end if;

q<=temp;

qbar<=not temp;

end process;

end Behavioral;

Output: -

b) JK Flip Flop

Theory: 33

CHANDIGARH UNIVERSITY, GHARUAN

A JK flip-flop is a refinement of the SR flip-flop in that the indeterminate state of the SR type is

defined in the JK type. Inputs J and K behave like inputs S and R to set and clear the flip-flop (note

that in a JK flip-flop, the letter J is for set and the letter K is for clear).

Truth Table: CLK

QBAR

NO CHANGE

NO CHANGE

NO CHANGE

NO CHANGE

Not(Q0)

Not(Q)

Code: library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity jk_ff is

Port ( j,k,clk : in STD_LOGIC;

q,qbar : out STD_LOGIC);

end jk_ff;

architecture Behavioral of jk_ff is

begin

process(j,k,clk)

variable temp : std_logic;

begin

if(clk='1')then

if(j='0' and k='0')then

temp:=temp;

elsif(j='0' and k='1')then

temp:='0';

elsif(j='1' and k='0')then

temp:='1';

else

temp:=not temp;

end if;

end if;

q<=temp;

qbar<=not temp;

end process;

end Behavioral;

34

CHANDIGARH UNIVERSITY, GHARUAN

Output: -

c) T Flip Flop: Theory: The T flip-flop is a single input version of the JK flip-flop. The T flip-flop is obtained from the JK

type if both inputs are tied together. The output of the T flip-flop toggles with each clock pulse.

Truth Table: CLK

QBAR

NO CHANGE

NO CHANGE

NO CHANGE

NO CHANGE

Not(Q0)

Not(Q)

Code: library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity tff is

Port ( t,clk : in STD_LOGIC;

35

CHANDIGARH UNIVERSITY, GHARUAN

q,qbar: out STD_LOGIC);

end tff;

architecture Behavioral of tff is

begin

process(clk)

variable tmp: STD_LOGIC :='0';

begin

if(clk='1' and clk'event) then

if t='0' then

tmp:=tmp;

elsif t='1' then

tmp:=not (tmp);

end if;

end if;

q<=tmp;

qbar<=not tmp;

end process;

end Behavioral;

Output: -

36

You might also like

- 3 Bit Asynchronous Counter Using JK Flip Flop: Program VHDLDocument4 pages3 Bit Asynchronous Counter Using JK Flip Flop: Program VHDLsanthiniNo ratings yet

- Bascule JKDocument9 pagesBascule JKOussema HamzaNo ratings yet

- VLSI Design - Encoders, Decoders, Multiplexers and DemultiplexersDocument19 pagesVLSI Design - Encoders, Decoders, Multiplexers and DemultiplexersEffecure HealthcareNo ratings yet

- DSD Unit-5Document43 pagesDSD Unit-5R.c.Raghavendra ReddyNo ratings yet

- VHDL SequentialDocument5 pagesVHDL SequentialSAKETSHOURAVNo ratings yet

- Lecture 7Document27 pagesLecture 7rahulNo ratings yet

- VERILOG CODE - Single Page PDFDocument1 pageVERILOG CODE - Single Page PDFAnuj PatelNo ratings yet

- EXP-11 and 12Document10 pagesEXP-11 and 12Aryan SharmaNo ratings yet

- VHDL code for basic flip flops & comparatorDocument3 pagesVHDL code for basic flip flops & comparatorNaveen NegiNo ratings yet

- Flip FlopsDocument4 pagesFlip FlopsAditya PNo ratings yet

- Decade CounterDocument3 pagesDecade Countergiridhar chikkaNo ratings yet

- Experiment:-6 Implementation of All The Flip-Flops 6 (A) SR Flip-FlopDocument12 pagesExperiment:-6 Implementation of All The Flip-Flops 6 (A) SR Flip-Floptechworld611No ratings yet

- VHDFFDocument4 pagesVHDFFAmirul AsyrafNo ratings yet

- Lab9Document10 pagesLab9Nrusingha Prasad PandaNo ratings yet

- VHDL Code For D FF Using Behavior ModelDocument20 pagesVHDL Code For D FF Using Behavior ModelAdithya ChakilamNo ratings yet

- Verilog Coding For Digital SystemDocument12 pagesVerilog Coding For Digital SystemBalajeNo ratings yet

- Part 6Document5 pagesPart 6bmbsnpNo ratings yet

- HACETTEPE UNIVERSITY ELE227 FUNDAMENTALS OF DIGITAL SYSTEMS LABORATORYDocument4 pagesHACETTEPE UNIVERSITY ELE227 FUNDAMENTALS OF DIGITAL SYSTEMS LABORATORYMehmethan Ayrım0% (1)

- VHDL For SR Flip-FlopDocument4 pagesVHDL For SR Flip-Flopsyazo93No ratings yet

- HDL Programming Verilog VHDL D Flip FlopDocument8 pagesHDL Programming Verilog VHDL D Flip FlopVikyNo ratings yet

- 06 - DFC10093 (Subchapter 2.3)Document23 pages06 - DFC10093 (Subchapter 2.3)Navinaash Chanthra SegaranNo ratings yet

- Experiment No 3Document20 pagesExperiment No 3Ako C SeanNo ratings yet

- Emb 2Document7 pagesEmb 2ballmerNo ratings yet

- DLD Assignment 9Document29 pagesDLD Assignment 9Nikhita EvuriNo ratings yet

- Understanding Flip-FlopsDocument11 pagesUnderstanding Flip-Flopsamiethurgat100% (2)

- Build Sequential Logic CircuitsDocument31 pagesBuild Sequential Logic CircuitsNavinaash Chanthra SegaranNo ratings yet

- Sequential ExampleDocument11 pagesSequential ExampleAmit JadhavNo ratings yet

- DSD Print 1Document11 pagesDSD Print 1FS TamimNo ratings yet

- Sequential Circuits Hardware Description Language: LectureDocument38 pagesSequential Circuits Hardware Description Language: LecturemarwaNo ratings yet

- JK FF TestbenchDocument3 pagesJK FF Testbenchapi-26691029No ratings yet

- D Flip-Flop: VHDL CodeDocument37 pagesD Flip-Flop: VHDL CodeVenkata Nagasai2000No ratings yet

- E Cad Lab ManualDocument51 pagesE Cad Lab ManualRajesh DoradlaNo ratings yet

- VHDocument2 pagesVHleonardo perezNo ratings yet

- VHDL Code For FlipflopDocument8 pagesVHDL Code For FlipflopLuisNo ratings yet

- Tarea 4Document9 pagesTarea 4Gabriel RoqueNo ratings yet

- Exp-6 20pec005Document8 pagesExp-6 20pec005ajay nareshNo ratings yet

- Flip FlopsDocument6 pagesFlip FlopsRahul PendyalaNo ratings yet

- Digital System Lab Week 10: VHDL Code For 4bit BCD Up Counter Using JK Flip FlopDocument4 pagesDigital System Lab Week 10: VHDL Code For 4bit BCD Up Counter Using JK Flip FlopARTI RAWATNo ratings yet

- ASM Algorithmic State Machine and VHDL ModelsDocument11 pagesASM Algorithmic State Machine and VHDL ModelsDeepakNo ratings yet

- VHDL 3 - Sequential Logic Circuits: Reference: Roth/John Text: Chapter 2Document29 pagesVHDL 3 - Sequential Logic Circuits: Reference: Roth/John Text: Chapter 2Soni NsitNo ratings yet

- Exp No: 01 Date: 25.09.12 Modeling and Simulation of Flipflops (JK, SR, D, T) Using Verilog HDLDocument9 pagesExp No: 01 Date: 25.09.12 Modeling and Simulation of Flipflops (JK, SR, D, T) Using Verilog HDLSrinandhini NandyNo ratings yet

- Unit 3Document34 pagesUnit 3Amitav DasNo ratings yet

- Ejemplos VHDL Latch: Ieee Ieee STD - LOGIC - 1164Document6 pagesEjemplos VHDL Latch: Ieee Ieee STD - LOGIC - 1164MoriartyNo ratings yet

- (D, T, RS, JK) Along With Testbench.: ASSIGNMENT: Design & Verify The Operation Flip-FlopsDocument9 pages(D, T, RS, JK) Along With Testbench.: ASSIGNMENT: Design & Verify The Operation Flip-FlopsAkshatNo ratings yet

- Basic Gates ProgramDocument34 pagesBasic Gates ProgramJoychandra LoukrakpamNo ratings yet

- Contador 0-59 en VHDLDocument12 pagesContador 0-59 en VHDLkattyNo ratings yet

- Lab 7: VHDL 16-Bit ShifterDocument6 pagesLab 7: VHDL 16-Bit ShifterAvinash VikramNo ratings yet

- Experiment 4Document10 pagesExperiment 4Akshat AgarwalNo ratings yet

- Flip-Flop DDocument7 pagesFlip-Flop DEdwin GavilanezNo ratings yet

- Design and verification of sequential circuits using Verilog HDLDocument26 pagesDesign and verification of sequential circuits using Verilog HDLAakanksha SharmaNo ratings yet

- TKHTS2Document5 pagesTKHTS2Ngọc ThuNo ratings yet

- L10 Ex RegisterDocument36 pagesL10 Ex RegisterusitggsipuNo ratings yet

- Experiment 9 (Flip Flops)Document7 pagesExperiment 9 (Flip Flops)groupidb3100% (3)

- The Clocked RS Flip-FlopDocument4 pagesThe Clocked RS Flip-Flopabhisheksikka17No ratings yet

- Proiect - Structuri FPGADocument10 pagesProiect - Structuri FPGACrocoduluNo ratings yet

- ArchL-Sequential Logic-03Document41 pagesArchL-Sequential Logic-03Ajax KrausNo ratings yet

- Model Flip-Flops, Registers & Latch VHDLDocument6 pagesModel Flip-Flops, Registers & Latch VHDLRahul MishraNo ratings yet

- VHDL Code For Flipflop – D, JK, SR, TDocument12 pagesVHDL Code For Flipflop – D, JK, SR, TSaurabh BhiseNo ratings yet

- The Spectral Theory of Toeplitz Operators. (AM-99), Volume 99From EverandThe Spectral Theory of Toeplitz Operators. (AM-99), Volume 99No ratings yet

- Experiment-8: Aim: Design, Synthesis and Simulation of Binary To Excess3 Code Converter. TheoryDocument3 pagesExperiment-8: Aim: Design, Synthesis and Simulation of Binary To Excess3 Code Converter. TheoryAnkit KumarNo ratings yet

- Experiment-9: AIM: Design, Analysis and Simulation of Johnson Counter. Theory: Logic DiagramDocument2 pagesExperiment-9: AIM: Design, Analysis and Simulation of Johnson Counter. Theory: Logic DiagramAnkit KumarNo ratings yet

- Awgn ChannelDocument19 pagesAwgn ChannelAnkit KumarNo ratings yet

- Punjab Jee 6th JulyDocument46 pagesPunjab Jee 6th JulyAnkit KumarNo ratings yet

- Network BasicDocument47 pagesNetwork BasicSyed HamdanNo ratings yet

- DataflowDocument8 pagesDataflowAnkit KumarNo ratings yet

- Chapter 12 - LCD and KeyboardDocument27 pagesChapter 12 - LCD and KeyboardAnkit KumarNo ratings yet

- AOOPs Theory and Lab SyllabusDocument6 pagesAOOPs Theory and Lab SyllabusAnkit KumarNo ratings yet

- Chapter 11 InterruptsDocument29 pagesChapter 11 InterruptsAnkit Kumar50% (2)

- Academic Calender For Odd & Even Sem 2016-2017Document6 pagesAcademic Calender For Odd & Even Sem 2016-2017Ankit KumarNo ratings yet

- Jee Data (Deepak)Document358 pagesJee Data (Deepak)Ankit Kumar0% (1)

- PIC 16 Notes For ReferenceDocument46 pagesPIC 16 Notes For ReferenceAnkit KumarNo ratings yet

- 15% With Modified DiagramDocument63 pages15% With Modified DiagramAnkit KumarNo ratings yet

- Basics NetworkingDocument15 pagesBasics NetworkingBirhanu AtnafuNo ratings yet

- Data Required by Gurdeep SirDocument10 pagesData Required by Gurdeep SirAnkit KumarNo ratings yet

- EE198B - Wireless Battery Charger PDFDocument21 pagesEE198B - Wireless Battery Charger PDFV'nod Rathode BNo ratings yet

- Computer NetworkDocument7 pagesComputer NetworkAnkit KumarNo ratings yet

- AmitDocument22 pagesAmitAnkit KumarNo ratings yet

- Twelfth International Multi Conference On Information ProcessingDocument2 pagesTwelfth International Multi Conference On Information ProcessingAnkit KumarNo ratings yet

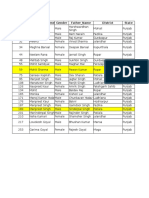

- S. No. Candidate - Name Gender Father - Name District StateDocument4 pagesS. No. Candidate - Name Gender Father - Name District StateAnkit KumarNo ratings yet

- BE ClusterheadDocument15 pagesBE ClusterheadAnkit KumarNo ratings yet

- S. No. Candidate - Name Gender Father - Name District StateDocument4 pagesS. No. Candidate - Name Gender Father - Name District StateAnkit KumarNo ratings yet

- AbstractDocument21 pagesAbstractAnkit KumarNo ratings yet

- Wireless Charging of Mobile Phones Using MicrowavesDocument15 pagesWireless Charging of Mobile Phones Using MicrowavesAnkit Kumar100% (1)

- Sandeep - 6 7 2016Document3 pagesSandeep - 6 7 2016Ankit KumarNo ratings yet

- All ExpDocument29 pagesAll ExpAnkit KumarNo ratings yet

- Wireless Battery Charger DesignDocument11 pagesWireless Battery Charger DesignAnkit KumarNo ratings yet

- Network BasicDocument47 pagesNetwork BasicSyed HamdanNo ratings yet

- Quality of Service Overview - QcfintroDocument18 pagesQuality of Service Overview - QcfintroDwi UtomoNo ratings yet