Professional Documents

Culture Documents

Informe 1 Definitivo

Uploaded by

Vanneza CifuentesCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Informe 1 Definitivo

Uploaded by

Vanneza CifuentesCopyright:

Available Formats

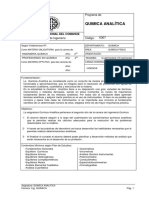

UNIVERSIDAD PEDAGGICA Y TECNOLOGICA DE COLOMBIA FACULTAD DE INGENIERIA ELECTRONICA 2015

Amplificador Multietapa. (Septiembre 2016)

Suly V. Cifuentes B., Estudiante VIII semestre Facultad de Ingeniera Electrnica

suly.cifuentes@uptc.edu.co vcifuentes9@gmail.com

Juan G. Robles P., Estudiante VII semestre Facultad de Ingeniera Electrnica

juan.robles01@uptc.edu.co

I.

RESUMEN

Esta prctica de laboratorio se procedi a desarrollar un

amplificador multi-etapa como recordatorio de lo aprendido en

el curso de electrnica II. Para el desarrollo de esta prctica se

requera hallar los respectivos parmetros y la caracterizacin

de cada transistor, para as poder llevar un buen desarrollo de

la prctica.

Ya teniendo los respectivos parmetros de cada transistor se

procede a hallar el valor de cada una de las resistencias de

cada etapa para as poder simular este esquema en el

simulador Orcad. Una vez verificado el ptimo

funcionamiento en la parte terica se procede a

implementacin en fsico de este amplificador multi-etapa,

probando el funcionamiento de cada una de las etapas por

separado, para luego poder acoplarlas por medio de

capacitores.

Abstract- This lab proceeded to develop a multi-stage

amplifier as a reminder of what has been learned in the

course of electronics II. For the development of this

practice was required to find the respective parameters

and the characterization of each transistor, in order to

bring a good development practice.

Already having the respective parameters of each

transistor proceeds to find the value of each of the

resistors of each stage in order to simulate this scheme in

Orcad simulator. Once verified optimum performance in

the theoretical part we proceed to physical implementation

of this multi-stage amplifier, testing the operation of each

stage separately, and then to couple them through

capacitors.

II.

INTRODUCCIN

Es muy fcil imaginarse que es un amplificador multi-etapa. A

primera impresin se observa que es un circuito que recibe una

seal y devuelve una seal idntica pero de diferente amplitud

(menor o mayor). Y que tiene ms de una etapa en la que realiza

dicha operacin. Ahora si bien es fcil ver de qu se habla, el

estudio es un poco ms complejo. Los 2 factores ms importantes en

un amplificador multi-etapa son: Las etapas amplificadoras y los

modos de acoplamiento. Las etapas amplificadoras ms conocidas

y usadas son: Transistorizadas con emisor comn, seguidor emisor

(colector comn), base comn, diferencial, y amplificacin con

operacionales. Los modos de acoplamiento Ms usuales son:

Acoplamiento directo, Capacitivo, y por transformador. Estas

configuraciones tienen sus ventajas y desventajas. Ya que por

ejemplo se recibe una mayor amplificacin y podemos reducir los

problemas por impedancias. Pero se tiene la desventaja de agregar

ms componentes y perder ancho de banda de trabajo. Conociendo

estas distintas etapas, ventajas, y desventajas se puede realizar

circuitos amplificadores para diferentes utilidades. Etapas

amplificadoras. Emisor comn: La seal se aplica a la base del

transistor y se extrae por el colector. El emisor se conecta a las

masas tanto de la seal de entrada como a la de salida. En esta

configuracin se tiene ganancia tanto de tensin como de corriente y

alta impedancia de entrada. Base comn: La seal se aplica al

emisor del transistor y se extrae por el colector. La base se conecta a

las masas tanto de la seal de entrada como a la de salida. En esta

configuracin se tiene ganancia slo de tensin. La impedancia de

entrada es baja, la de salida media alta y la ganancia de corriente

algo menor que uno, debido a que parte de la corriente de emisor

sale por la base. El desarrollo de un circuito de este tipo se

encontrar en el presente informe, en el apartado III correspondiente

al desarrollo y anlisis de resultados de la prctica, se encontrar el

desarrollo detallado de cada etapa y el respectivo anlisis del

resultado final de la onda.

III.

DESARROLLO, ANALISIS Y RESULTADOS

DE LA PRACTICA

3.1. Desarrollo terico Amplificador Multietapa: Para el

diseo del amplificador multi-etapa se requiri de una

RL=28Ohms una potencia de salida Pout=19W, un voltaje de

entrada Vinpp=100mV y una Impedancia de entrda mayor a

Zin>50KOhms. Teniendo en cuenta los datos mencionados

anteriormente se procede a despejar el voltaje de salida pico a

pico

con

la

ecuacin

1:

UNIVERSIDAD PEDAGGICA Y TECNOLOGICA DE COLOMBIA FACULTAD DE INGENIERIA ELECTRONICA 2015

V opp = 8 * RL * P out = 20.63v

(1)

Y conociendo Vopp y Vinpp hallamos la ganancia de voltaje

de todo el circuito que corresponde a:

V opp

Av = V inpp = 206.3

La que se dividir en dos etapas de emisor comn, en la

primer etapa se tendr una ganancia de Av=20,63 y en la

segunda una ganancia de Av=10. Para el diseo total se har

uso de cuatro etapas, dos de colector comn y dos de emisor

comn.

Fig. Etapa 1: Colector Comn

3.1.1. Etapa I: Colector comn: Para la primer etapa de

colector comn se tiene una ganancia de voltaje ideal de

Av=1, una RL= 28Ohms y se asume un Voltaje de

polarizacin de Vcc=24v, Como esta corresponde a la etapa de

potencia se hace uso de un transistor Tip 122 que se

caracteriza con un VCE=12Vy una corriente de colector de

552,59mA, Los parmetros correspondieron a un Beta=7527.6

y un VBE=1.325, ya que corresponde a un Transistor

Darlington. Los Clculos de los dems elementos del circuito

se plasmaron en la TABLA I, y su comprobacin terica se

encuentra en el Anexo 1.

3.1.2. Etapa II: Emisor Comn: Para la primer etapa de

emisor comn comn se tiene una ganancia de voltaje ideal de

Av=26.03, una RL= 14kOhms y se asume un Voltaje de

polarizacin de Vcc=24v.Para las etapas de amplificacin del

circuito que son las dos etapas de emisor comn se har uso

del transistor de propsito general 2N2222 que se caracteriza

con un VCE=8Vy una corriente de colector de 10mA, Los

parmetros correspondieron a un Beta=191 y un VBE=0.704v.

Los Clculos de los dems elementos del circuito se

plasmaron en la TABLA II, y su comprobacin terica se

encuentra en el Anexo 2.

TABLA I. ETAPA 1 COLECTOR COMN

Transistor: Tip 122 ( B=7527,6, Vbe=1,325 )

Ic = 10mA

Ib=52,35uA

Ie=10,052m

A

Vce=8

PRE=6,63w

t

VRE=8v

Vre=8v

Re=795,86

PRE=4mW

PR1=3,4m

w

R2=40k

RC=800

PRC=12m

W

R =496,6

Ptrt=80m

W

Av=0,9969

Zin=14k

Avmax=30

7

RB=15k

Vbb=9,48 V

R1=38K

PR1=5mW

PR2=4mW

RE1=36

RE2=760

Zin=5k

Vinpp=1v

Cre =1mF

Vce=12v

Vre=12v

Ic=552mA

Ib=73,4uA

Ie=552,66m

A

Ptst=6,63w

RE=21,71

Vbb=14,49v

R1=27k

PR2=5,2mw

R =355

TABLA II. ETAPA EMISOR COMUN (Av=26.03)

Transistor: Q2N2222( B=191 Vbe=0,704 )

Con los parmetros y clculos plasmados en la TABLA I se

procede a implementar en ORCAD la primer etapa del

circuito como se observa en la Figura 1.

CZin=1mF

Con los parmetros y clculos plasmados en la TABLA II se

procede a implementar en ORCAD la primer etapa del

circuito

como

se

observa

en

la

Figura

2.

UNIVERSIDAD PEDAGGICA Y TECNOLOGICA DE COLOMBIA FACULTAD DE INGENIERIA ELECTRONICA 2015

Fig. 2 Etapa Emisor comn Av= 26.03.

Fig.3 Etapa Emisor comn Av=10

3.1.3. Etapa III: Emisor Comn: Para la segunda etapa de

emisor comn se tiene una ganancia de voltaje ideal de

Av=10, una RL= 5kOhms y se asume un Voltaje de

polarizacin de Vcc=24v. Para las etapas de amplificacin del

circuito que son las dos etapas de emisor comn se har uso

del transistor de propsito general 2N2222 que se caracteriza

con un VCE=8Vy una corriente de colector de 10mA, Los

parmetros correspondieron a un Beta=191 y un VBE=0.704v.

Los Clculos de los dems elementos del circuito se

plasmaron en la TABLA III, y su comprobacin terica se

encuentra en el Anexo 3.

3.1.4. Etapa IV: Colector comn: Para la primer etapa de

colector comn se tiene una ganancia de voltaje ideal de

Av=1, una RL= 7.6kOhms y se asume un Voltaje de

polarizacin de Vcc=24v, En esta etapa se hace uso de un

transistor Tip 122 que se caracteriza con un VCE=12Vy una

corriente de colector de 10.79mA, Los parmetros

correspondieron a un Beta=2204.8 y un VBE=1.401, ya que

corresponde a un Transistor Darlington. Los Clculos de los

dems elementos del circuito se plasmaron en la TABLA IV, y

su comprobacin terica se encuentra en el Anexo 4.

TABLA IV. ETAPA FINAL COLECTOR COMUN

TABLA III. ETAPA EMISOR COMN (Av=10)

Transistor: Tip 122 ( B=2204,8 , Vbe=1,161v )

Transistor: Q2N2222 ( B=191 Vbe=0,704 )

Vce=12v

Vre=12v

Ic=10,77mA

Ib=4,85uA

Ic = 10mA

Ib=52,35uA

Ie=10,052mA

Vce=8v

Ie=10,774mA

Ptst=129mw

Re=1113

Pre=3,2mw

Vre=8v

VRE=8v

RE=795,86

Pre=12mW

Vbb=14,35v

R1=54k

Pr1=3,3mw

R2=77k

Rc=800

PRC=7mW

R =496,6

Ptrt=80m

W

Pr2=2,2mw

R =5322

Av=0,9975

Zin=220k

Avmax=30

7

RB=15k

Vbb=9,48 V

R1=38K

PR1=5mW

PR2=4mW

RE1=77

RE2=760

Zin=7,6k

Vinpp=100,28mv

CRE =1mF

CZin=1mF

Con los parmetros y clculos plasmados en la TABLA III se

procede a implementar en ORCAD la primer etapa del

circuito como se observa en la Figura 3.

Con los parmetros y clculos plasmados en la TABLA IV se

procede a implementar en ORCAD la primer etapa del

circuito

como

se

observa

en

la

Figura

4.

UNIVERSIDAD PEDAGGICA Y TECNOLOGICA DE COLOMBIA FACULTAD DE INGENIERIA ELECTRONICA 2015

Fig.4 Etapa Final Colector Comn.

Una de las principales razones por las que se present la falla

en el circuito es el mal acople de impedancias que existe entre

etapas y eso genera inestabilidad en el circuito. Tambin se

debe tener en cuenta que al ser elementos discretos tienden a

ser inestables y a cambiar sus caractersticas al paso del

tiempo y a condiciones no favorables. En este caso las

condiciones no favorables hacen referencia a la disipacin de

calor en los elementos. Tambin cabe resaltar que el no

encontrarse los elementos con los valores exactos no se logra

el resultado exacto ni esperado por el diseador.

Al finalizar el diseo de todas las etapas se procede a unirlas

por medio de capacitores de acople como se muestra en la

Figura 5 que corresponde al circuito amplificador multietapa

con ganancia Av=206.3.

IV.

Fig. 5 Amplificador Multietapa Completo

Y en la figura 6 se puede observar el resultado de la

simulacin en ORCAD. Cabe resaltar que en la

simulacin se observa que la amplificacin no

cumplio con los parametros deseados, ya que

debera amplificar un total de 20.6vpp y logra solo

una amplitud de 16.5vpp.

1.

Es necesario tener en cuenta que hay distintos factores que

pueden afectar el ptimo funcionamiento de un amplificador

multi-etapa, como los son la temperatura, la humedad, etc.

2.

En el momento de la implementacin es necesario utilizar

capacitor igual o mayor al voltaje entregado por la fuente, ya

que en el momento de visualizar la forma de onda en el

osciloscopio esta puede cambiar su forma y verse un poco

alterada, lo cual dificulta su interpretacin.

3.

La inestabilidad en este tipo de circuitos tiende a ser inmensa

cuando se implementan con elementos discretos como son los

transistores. Se logro observar a lo largo del desarrollo de la

practica la poca practicidad y eficiencia de este tipo de

circuitos y tambin el consumo excesivo de espacio, por lo

tanto se hace muy poco practica su implementacin

V.

Fig.6 Simulacin en el tiempo ORCAD.

Al realizar la implementacin fsica del circuito no se logr el

resultado esperado ya que la amplitud que se logro fue de

l

i

l

1Vpp como se observa en la Fig. 7 . y a gananc a de

amplificador se redujo de manera notable

Fig.7 Resultado prctico sobre Osciloscopio.

CONCLUSIONES

REFERENCIAS

[1].BOYLESTAD, Robert L. Electrnica: Teora de

Circuitos. Editorial Prentice Hall, 1995.

[2].GUTIRREZ, Humberto. Electrnica anloga: teora y

laboratorio. Ed. Humberto Gutirrez. 1996

[3]MALVINO, Albert Paul. Principios de electrnica.

Editorial McGraw-Hill, 1991.

[4]MILLMAN, Jacob. Electrnica integrada. Editorial

Hispano

Americano, 1986.

UNIVERSIDAD PEDAGGICA Y TECNOLOGICA DE COLOMBIA FACULTAD DE INGENIERIA ELECTRONICA 2015

ANEXO 1

ANEXO 2

UNIVERSIDAD PEDAGGICA Y TECNOLOGICA DE COLOMBIA FACULTAD DE INGENIERIA ELECTRONICA 2015

ANEXO 3

ANEXO 4

You might also like

- Informe 2 MaqDocument2 pagesInforme 2 MaqVanneza CifuentesNo ratings yet

- BluetoothDocument10 pagesBluetoothVanneza CifuentesNo ratings yet

- Algoritmos MPPT Aplicados A Un Conversor SEPIC en Sistemas FotovoltaicosDocument13 pagesAlgoritmos MPPT Aplicados A Un Conversor SEPIC en Sistemas FotovoltaicosVanneza CifuentesNo ratings yet

- 7 Funcion de Transferencia Primer OrdenDocument13 pages7 Funcion de Transferencia Primer OrdenAna MelendezNo ratings yet

- Informe MultietapaDocument11 pagesInforme MultietapaVanneza CifuentesNo ratings yet

- Teoría Del ColorDocument17 pagesTeoría Del ColorCarlos Javier Alba LopezNo ratings yet

- Programa QA 2016Document6 pagesPrograma QA 2016Lilen CaniuqueoNo ratings yet

- Guia Tecnica de Analisis EspacialDocument85 pagesGuia Tecnica de Analisis Espacialcanelonesc4654100% (7)

- Presentación Trabajo Flotación Cu-Pb-Ag-Zn Ver 2.0Document57 pagesPresentación Trabajo Flotación Cu-Pb-Ag-Zn Ver 2.0evizcardo4617No ratings yet

- Informe FisicaDocument10 pagesInforme FisicaRandyNo ratings yet

- Variable ArtificialDocument11 pagesVariable ArtificialWilly Mendez SilvestreNo ratings yet

- COM Tema VI Transporte LongitudinalDocument54 pagesCOM Tema VI Transporte Longitudinalblass saenzNo ratings yet

- Practica 1probaDocument3 pagesPractica 1probaJuan Manuel LópezNo ratings yet

- MDA4 To Grado 3 Er Trimestre MEXDocument115 pagesMDA4 To Grado 3 Er Trimestre MEXRocioNoemiNo ratings yet

- Problemario V. Física Básica II. Abril Del 2020. La Naturaleza de La Luz y Las Leyes de La Geometría Optica.Document5 pagesProblemario V. Física Básica II. Abril Del 2020. La Naturaleza de La Luz y Las Leyes de La Geometría Optica.Sandra NvaNo ratings yet

- 0348-ESP-AEE-000C-000-0007 KKS Codificación de KKS de Equipos y Componentes PDFDocument87 pages0348-ESP-AEE-000C-000-0007 KKS Codificación de KKS de Equipos y Componentes PDFObedJiménez100% (1)

- PTAP 05 - Mezcla RapidaDocument2 pagesPTAP 05 - Mezcla RapidaCarlos NuñezNo ratings yet

- Monografia Pavimentos RígidosDocument20 pagesMonografia Pavimentos RígidosShamirRivera100% (1)

- Informe Lab Organica Punto de Fusión y SublimaciónDocument5 pagesInforme Lab Organica Punto de Fusión y SublimaciónMartin Elias100% (1)

- Ejercicio 1Document8 pagesEjercicio 1Daniel LautaroNo ratings yet

- Acero Al CrMoDocument21 pagesAcero Al CrMoHugo EnriqueNo ratings yet

- Previo 2 LemDocument7 pagesPrevio 2 LemSandro ReyesNo ratings yet

- Bobinados ConcéntricosDocument4 pagesBobinados Concéntricosjonathansata100% (1)

- Trabajo de Física Calor y OndasDocument7 pagesTrabajo de Física Calor y Ondassantiago hernandezNo ratings yet

- PNN Modificado Abri - CorlDocument26 pagesPNN Modificado Abri - CorlJoseAngelVillarViñolesNo ratings yet

- 10 AlternaDocument1 page10 AlternaRafael Nazareno RivadeneiraNo ratings yet

- Cinemática I y IIDocument5 pagesCinemática I y IIBericht Frexs Vasquez Onzueta0% (2)

- Espectro Del SonidoDocument7 pagesEspectro Del SonidoCristian Michelli Rodriguez LunaNo ratings yet

- GAM 100 InstrDocument48 pagesGAM 100 Instrgpocobos100% (1)

- Especificaciones Tecnicas Estructuras - CraiDocument67 pagesEspecificaciones Tecnicas Estructuras - Craiwilmer100% (1)

- LAB. 8 Generador DCDocument10 pagesLAB. 8 Generador DCJhorvin Santiago SalirrosasNo ratings yet

- Rejillas PDFDocument18 pagesRejillas PDFHeysen Payahuanca ChavezNo ratings yet

- SPC 3 Ppa7 Trimestre 2Document15 pagesSPC 3 Ppa7 Trimestre 2Confezor CoderoNo ratings yet

- Robótica 102 Guía para El Docente SPDocument59 pagesRobótica 102 Guía para El Docente SPLuis CabralNo ratings yet