Professional Documents

Culture Documents

Lec19 PDF

Uploaded by

Mustafa Rashik HasnainOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lec19 PDF

Uploaded by

Mustafa Rashik HasnainCopyright:

Available Formats

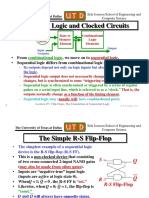

The University of Texas at Dallas

Erik Jonsson School of Engineering and

Computer Science

The CPU Control Unit

We now have a fairly good picture of the logic circuits

in the CPU.

Having designed the ALU or datapath so that it can

perform the necessary instructions, we now have to do

the same thing for the control unit, which decodes

instructions and provides direction to the CPU.

The MIPS control unit decodes the six bits on either

end of the 32-bit instruction word, that is, the op code

and function code* fields, to determine each instruction

sequence.

* On R-R instructions.

1

Lecture # 19: Control Unit Design and Multicycle Implementation

N. B. Dodge 9/15

The University of Texas at Dallas

Erik Jonsson School of Engineering and

Computer Science

The Central Processor Unit (CPU)

ALU

Registers

Control Unit

Instruction Fetch/Decode

In lecture 19, we covered processing elements (blue),

including the registers, ALU, and data buses.

We now address the control unit circuitry (red).

Instruction decoding.

Control signals to ALU and other control elements.

2

Lecture # 19: Control Unit Design and Multicycle Implementation

N. B. Dodge 9/15

Erik Jonsson School of Engineering and

Computer Science

The University of Texas at Dallas

Functionality of Control Unit

00 0000

Op. code

Bit 31

0 1000

0 1001

0 1010

$t0

$t1

$t2

0 0000

10 0000

Shift amt. Fn. code

Bit 0

The control unit determines ALU functions in each

instruction and selects operands for the ALU.

The operation code (the left six bits of the instruction)

determines the type of operation and in some cases (such

as jump instructions) the actual instruction itself.

In the case of register-register instructions, the function

code determines the instruction (for example, in the R/R

instruction above, the function code 0x 20 means add).

3

Lecture # 19: Control Unit Design and Multicycle Implementation

N. B. Dodge 9/15

Erik Jonsson School of Engineering and

Computer Science

The University of Texas at Dallas

10 0000

0 0000

To shift amount decoder

01010

Bit 31

To function code

decoder

To dest. reg. decoder

0 1001

Bit 0

To source 2 reg. decoder

0 1000

As mentioned before,

the control unit is a

collection of decoders

and multiplexers.

The decoded

instruction fields tell

(1) the ALU what

function to perform,

(2) what operands to

use.

To source 1 reg. decoder

00 0000

Functionality of Control Unit (2)

To operation code

decoder

Lecture # 19: Control Unit Design and Multicycle Implementation

N. B. Dodge 9/15

The University of Texas at Dallas

Erik Jonsson School of Engineering and

Computer Science

Current Architecture

The ALU control uses instruction bits 0-5 to obtain

information about the ALU operation in register-toregister instructions.

Note in the following diagram that some of the

decoding is done in the register block, which has the

decoding mechanism (as discussed in lecture 8, slides 8

and 9) that identifies source and destination registers in

load/store and register/register operations.

The ALU control also has input control lines from the

operation code decoder which decodes bits 26-31, and

which will be shown later.

5

Lecture # 19: Control Unit Design and Multicycle Implementation

N. B. Dodge 9/15

Erik Jonsson School of Engineering and

Computer Science

The University of Texas at Dallas

ALU Design with ALU Control Block Shown

32

32

+4

ADD

Inst.

0-31

Instruction bits 0-31

Instruction

Address

Instruction

Memory

M

32

U

X

ADD

Left

shift

2

P

C

32

32

5

5

32

Rs

Rt

M 5

U

Rd

X

Write

Data

32

Read

Data 2

32

Reg. Block

16 (Bits 0-15)

Lecture # 19: Control

Read

Data 1

Sign 32

Extend

ALU

M

32

U

X

ALU

6 (Bits 0-5) Control

32

Data

Address

Write

Data

Read 32

Data

32

M 32

U

X

Data

Memory

ALU Control Block (function code/

op code decoder)

After David A. Patterson and John L. Hennessy, Computer Organization and Design, 2nd Edition

N. B. Dodge 9/15

Unit Design and Multicycle Implementation

The University of Texas at Dallas

Erik Jonsson School of Engineering and

Computer Science

ALU Control Block

ALU operation

bits from op code

control unit

3-bit ALU

control bus

Function code

(instruction

bits 0-5)

ALU Control

Block Detail

Lecture # 19: Control Unit Design and Multicycle Implementation

N. B. Dodge 9/15

Erik Jonsson School of Engineering and

Computer Science

The University of Texas at Dallas

Single-Cycle ALU Design with Full Control Blocks

Reg. Dest.

32

32

ADD

+4

Instruction

Address

Instruction bits 0-31

P

C

6 (Bits 26-31)

Inst.

0-31

Instruction

Memory

5

5

Control

Branch

Mem. Read

Mem. To Reg.

ALU Op.

Mem. Write

ALU Srce.

Reg. Write

M

32

U

X

32

ADD

Left

shift

2

32

Rs

Read

Data 1

Rt

M 5

U

Rd

X

Write

Data

Read

Data 2

Write

ALU

32

Reg. Block

16 (Bits 0-15)

Lecture # 19: Control

32

Sign 32

Extend

M

32

U

X

32

Data

Address

Write

Data

Read

Mem./Reg.

Select

Read 32

Data

32

M 32

U

X

Data

Memory

ALU

6 (Bits 0-5) Control

After David A. Patterson and John L. Hennessy, Computer Organization and Design, 2nd Edition

N. B. Dodge 9/15

Unit Design and Multicycle Implementation

The University of Texas at Dallas

Erik Jonsson School of Engineering and

Computer Science

Op Code Control Block Signal Identifier

RegDst Register destination control (MUX input)

Branch Activates branch address change function

MemRead Signals read cycle to data memory circuits

Op code

decode/

control

block

MemtoReg Selects ALU or memory write to register

ALUOp (2 lines) Used with function code in ALU control

MemWrite Signals write cycle to data memory circuits

ALUSrc Selects register and immediate ALU operand

RegWrite Activates write function to register block

Lecture # 19: Control Unit Design and Multicycle Implementation

N. B. Dodge 9/15

The University of Texas at Dallas

Erik Jonsson School of Engineering and

Computer Science

Function of Op Code Control Signals

Signal Name

10

When Signal = 1

When Signal = 0

RegDst

Write reg. = $rd (bits 1115)

Write reg. = $rt (bits 16-20)

Branch

ALU branch compare activated

No branch activated

MemRead

Memory data write register

No data read from memory

MemtoReg

Memory data write register

ALU results write register

ALUOp

NA; lines go to ALU control block

NA; lines go to ALU control block

MemWrite

ALU or register data memory

No data written to memory

ALUSrc

2nd ALU operand is immediate

(sign-extended instr. bits 0-15)

2nd ALU operand is from $rt

(instruction bits 16-20)

RegWrite

Memory/ALU data write reg.

No input to register block

Lecture # 19: Control Unit Design and Multicycle Implementation

N. B. Dodge 9/15

Erik Jonsson School of Engineering and

Computer Science

The University of Texas at Dallas

Op Code Control Block Circuitry

Instruction

bits 26-31

0

23

2a 04

TO ALU

control block

11

Lecture # 19:

After David A. Patterson and John L. Hennessy, Computer Organization and Design, 2nd Edition

N. B. Dodge 9/15

Control Unit Design and Multicycle Implementation

The University of Texas at Dallas

Erik Jonsson School of Engineering and

Computer Science

Register Block

To shift amount decoder (ALU)

Registers

To $rt source register decoder

$rt

decode

To $rs source register decoder

$rs

decode

TO Operation Code Control Block

01010

To $rd destination register decoder

$rd

decode

0 1001

12

TO ALU Control Block

0 1000

Bit 31

ALU

Control

Block

00 0000

0 0000

Bit 0

10 0000

Instruction Disposition Showing Destination Units

Lecture # 19: Control Unit Design and Multicycle Implementation

Op

Code

Control

Block

N. B. Dodge 9/15

The University of Texas at Dallas

Erik Jonsson School of Engineering and

Computer Science

Data/control Signal Flow Examples

The following diagrams illustrate the flow of control signals and

data in some example MIPS instructions in the single cycle

implementation.

The single cycle implementation is just a stepping stone to the

final MIPS design, but this simpler example has all the features of

the more complex final design in terms of data routing and the

way in which the control signals determine the specific operation

for each given instruction.

Note the data flow in these instructions, and pay special attention

to the way some of the combinational devices we studied, such as

the decoder and multiplexer, are utilized extensively.

13

Lecture # 19: Control Unit Design and Multicycle Implementation

N. B. Dodge 9/15

Erik Jonsson School of Engineering and

Computer Science

The University of Texas at Dallas

Start of R-Type Instruction

Reg. Dest.

32

32

ADD

+4

Instruction

is fetched

P

C

Instruction

Address

Inst.

0-31

Instruction

Memory

14

Instruction bits 0-31

6 (Bits 26-31)

5

5

Control

Branch

Mem. Read

Mem. To Reg.

ALU Op.

Mem. Write

ALU Srce.

Reg. Write

M

32

U

X

32

ADD

Left

shift

2

32

Rs

Read

Data 1

Rt

M 5

U

Rd

X

Write

Data

Read

Data 2

Write

ALU

32

Reg. Block

16 (Bits 0-15)

Lecture # 19: Control

32

Sign 32

Extend

M

32

U

X

32

Data

Address

Write

Data

Read

Mem./Reg.

Select

Read 32

Data

32

M 32

U

X

Data

Memory

ALU

Control

6 (Bits 0-5)

After David A. Patterson and John L. Hennessy, Computer Organization and Design, 2nd Edition

N. B. Dodge 9/15

Unit Design and Multicycle Implementation

Erik Jonsson School of Engineering and

Computer Science

The University of Texas at Dallas

Next Step of R-Type Instruction

Reg. Dest.

32

32

ADD

+4

Instruction

Address

Instruction bits 0-31

P

C

6 (Bits 26-31)

Inst.

0-31

Instruction

Memory

5

5

Control

Branch

Mem. Read

Mem. To Reg.

ALU Op.

Mem. Write

ALU Srce.

Reg. Write

M

32

U

X

32

ADD

Left

shift

2

32

Rs

Read

Data 1

Rt

M 5

U

Rd

X

Write

Data

Read

Data 2

32

ALU

32

Reg. Block

16 (Bits 0-15)

Write

Sign 32

Extend

M

32

U

X

32

Data

Address

Write

Data

Read

Mem./Reg.

Select

Read 32

Data

32

M 32

U

X

Data

Memory

ALU

Registers are identified and

Control

6 (Bits 0-5)

needed operands are routed to

the ALU and the PC update

circuit.

After David A. Patterson and John L. Hennessy, Computer Organization and Design, 2nd Edition

N. B. Dodge 9/15

Lecture # 19: Control Unit Design and Multicycle Implementation

15

Erik Jonsson School of Engineering and

Computer Science

The University of Texas at Dallas

Third Step of R-Type Instruction

Reg. Dest.

32

32

ADD

+4

Instruction

Address

Instruction bits 0-31

P

C

6 (Bits 26-31)

5

5

Inst.

0-31

Instruction

Memory

Control

M

32

U

X

32

ADD

Left

shift

2

32

Rs

Read

Data 1

Rt

M 5

U

Rd

X

Write

Data

Read

Data 2

32

16 (Bits 0-15)

Lecture # 19: Control

Write

ALU

32

Reg. Block

ALU operation is selected

and performed.

16

Branch

Mem. Read

Mem. To Reg.

ALU Op.

Mem. Write

ALU Srce.

Reg. Write

The ALU output is

routed to write

select MUX.

Sign 32

Extend

M

32

U

X

32

Data

Address

Write

Data

Read

Mem./Reg.

Select

Read 32

Data

32

M 32

U

X

Data

Memory

ALU

Control

6 (Bits 0-5)

After David A. Patterson and John L. Hennessy, Computer Organization and Design, 2nd Edition

N. B. Dodge 9/15

Unit Design and Multicycle Implementation

Erik Jonsson School of Engineering and

Computer Science

The University of Texas at Dallas

Completion of R-Type Instruction

Reg. Dest.

32

32

ADD

+4

Instruction

Address

Instruction bits 0-31

P

C

6 (Bits 26-31)

5

5

Inst.

0-31

Instruction

Memory

Control

M

32

U

X

32

ADD

Left

shift

2

32

Rs

Read

Data 1

Rt

M 5

U

Rd

X

Write

Data

Read

Data 2

Lecture # 19: Control

32

Write

ALU

32

Reg. Block

16 (Bits 0-15)

With the write register line

active, data is written back

to the destination register.

17

Branch

Mem. Read

Mem. To Reg.

ALU Op.

Mem. Write

ALU Srce.

Reg. Write

Sign 32

Extend

M

32

U

X

32

Data

Address

Write

Data

Read

Mem./Reg.

Select

Read 32

Data

32

M 32

U

X

Data

Memory

ALU

6 (Bits 0-5) Control

After David A. Patterson and John L. Hennessy, Computer Organization and Design, 2nd Edition

N. B. Dodge 9/15

Unit Design and Multicycle Implementation

Erik Jonsson School of Engineering and

Computer Science

The University of Texas at Dallas

Load Instruction

Reg. Dest.

32

32

ADD

+4

6 (Bits 26-31)

Control

Instr. lines

Instruction bits 0-31

Data store path

Address data

Read address

Immediate

P

C

Instruction

Address

Inst.

0-31

Read

Data 1

Rt

M 5

U

Rd

X

Instruction

Memory

Write

Data

Read

Data 2

ADD

Left

shift

2

32

32

16 (Bits 0-15)

Lecture # 19: Control

Write

ALU

32

Reg. Block

The load instruction identifies the

register containing the address, the

immediate, and the write register

18

M

32

U

X

32

Rs

Branch

Mem. Read

Mem. To Reg.

ALU Op.

Mem. Write

ALU Srce.

Reg. Write

The word addressed in

memory is written back

to the identified write

register

Sign 32

Extend

M

32

U

X

32

Data

Address

Write

Data

Read

Mem./Reg.

Select

Read 32

Data

32

M 32

U

X

Data

Memory

ALU

6 (Bits 0-5) Control

After David A. Patterson and John L. Hennessy, Computer Organization and Design, 2nd Edition

N. B. Dodge 9/15

Unit Design and Multicycle Implementation

Erik Jonsson School of Engineering and

Computer Science

The University of Texas at Dallas

Branch Instruction

Reg. Dest.

32

32

ADD

+4

PC+4

Addr.

Immediate

New PC address

Instruction

lines

P

C

Instruction

Address

Inst.

0-31

Instruction

Memory

Instruction bits 0-31

6 (Bits 26-31)

5

5

Control

M

32

U

X

32

ADD

Left

shift

2

32

Rs

Read

Data 1

Rt

M 5

U

Rd

X

Write

Data

Read

Data 2

Lecture # 19: Control

32

Write

ALU

32

Reg. Block

16 (Bits 0-15)

Active

control lines

Register data

19

Branch

Mem. Read

Mem. To Reg.

ALU Op.

Mem. Write

ALU Srce.

Reg. Write

Sign 32

Extend

M

32

U

X

32

Data

Address

Write

Data

Read

Mem./Reg.

Select

Read 32

Data

32

M 32

U

X

Data

Memory

ALU

6 (Bits 0-5) Control

After David A. Patterson and John L. Hennessy, Computer Organization and Design, 2nd Edition

N. B. Dodge 9/15

Unit Design and Multicycle Implementation

Erik Jonsson School of Engineering and

Computer Science

The University of Texas at Dallas

Jump Instruction Circuitry Added

Instruction Bits 0-25 Left

shift

2

PC+4 (Bits 28-31)

32

Jump

Reg. Dest.

+4

ADD

Instruction

Address

Instruction bits 0-31

6 (Bits 26-31)

P

C

Inst.

0-31

Instruction

Memory

5

5

Control

Branch

Mem. Read

Mem. To Reg.

ALU Op.

Mem. Write

ALU Srce.

Reg. Write

M

32

U

X

32

32

ADD

Left

shift

2

32

Rs

Read

Data 1

Rt

M 5

U

Rd

X

Write

Data

Read

Data 2

32

Write

32

M

32

U

X

Reg. Block

16 (Bits 0-15)

Sign 32

Extend

6 (Bits 0-5)

20

M

U

X

32

ALU

ALU

Control

32

Data

Address

Write

Data

Read

Mem./Reg.

Select

Read 32

Data

32

M 32

U

X

Data

Memory

After David A. Patterson and John L. Hennessy,

Computer Organization and Design, 2nd Edition

Lecture # 19: Control Unit Design and Multicycle Implementation

N. B. Dodge 9/15

Erik Jonsson School of Engineering and

Computer Science

The University of Texas at Dallas

Jump Instruction Flow

Instruction Bits 0-25 Left

shift

2

PC+4 (Bits 28-31)

32

32

Jump

Reg. Dest.

+4

ADD

6 (Bits 26-31)

Control

Instruction bits 0-31

PC+4 data

PC jump data

PC update

Jump control

P

C

Instruction

Address

Inst.

0-31

Instruction

Memory

5

5

Branch

Mem. Read

Mem. To Reg.

ALU Op.

Mem. Write

ALU Srce.

Reg. Write

32

ADD

Left

shift

2

32

Rs

Read

Data 1

Rt

M 5

U

Rd

X

Write

Data

Read

Data 2

32

Write

32

M

32

U

X

Reg. Block

16 (Bits 0-15)

Sign 32

Extend

6 (Bits 0-5)

21

M

32

U

X

32

M

U

X

ALU

ALU

Control

32

Data

Address

Write

Data

Read

Mem./Reg.

Select

Read 32

Data

32

M 32

U

X

Data

Memory

After David A. Patterson and John L. Hennessy,

Computer Organization and Design, 2nd Edition

Lecture # 19: Control Unit Design and Multicycle Implementation

N. B. Dodge 9/15

The University of Texas at Dallas

Erik Jonsson School of Engineering and

Computer Science

Exercise 1

On the next slide is a diagram of the complete

single-cycle preliminary MIPS architecture.

On a copy of that diagram:

1. Circle every element that contains a decoder.

2. Highlight the line that controls the content of the

data written back to the destination register.

3. Circle the device that allows a 16-bit number to be

successfully added to a 32-bit number.

22

Lecture # 19: Control Unit Design and Multicycle Implementation

N. B. Dodge 9/15

Instruction Bits 0-25 Left

shift

2

PC+4 (Bits 28-31)

32

Jump

Reg. Dest.

+4

ADD

Instruction

Address

Instruction bits 0-31

6 (Bits 26-31)

P

C

M

U

X

32

Inst.

0-31

Instruction

Memory

5

5

Control

Branch

Mem. Read

Mem. To Reg.

ALU Op.

Mem. Write

ALU Srce.

Reg. Write

M

32

U

X

32

32

ADD

Left

shift

2

32

Rs

Read

Data 1

Rt

M 5

U

Rd

X

Write

Data

Read

Data 2

32

Write

32

M

32

U

X

Reg. Block

16 (Bits 0-15)

Sign 32

Extend

6 (Bits 0-5)

ALU

ALU

Control

32

Data

Address

Write

Data

Read

Mem./Reg.

Select

Read 32

Data

32

M 32

U

X

Data

Memory

After David A. Patterson and John L. Hennessy,

Computer Organization and Design, 2nd Edition

Print out a copy of this diagram and bring to class.

Lecture # 19: Control Unit Design and Multicycle Implementation

The University of Texas at Dallas

Erik Jonsson School of Engineering and

Computer Science

Making the ALU More Efficient

We have now completed design of the basic MIPS R-2000 CPU.

Although a good basic design, it has a serious drawback:

Our processor is designed so that all instructions complete in one

clock cycle.

While this assures that there is sufficient time to complete any

instruction, it also means that one clock period must be long enough

to accommodate the longest and most complicated instruction.

Thus, ALL instructions take as long as the longest instruction.

Since many (most!) instructions in the MIPS architecture take less

time to execute than the longest instructions (which are usually the

lw memory reference instructions), this means that we are slowing

execution of our CPU a large part of the time to accommodate

instructions that occur substantially less frequently.

25

Lecture # 19: Control Unit Design and Multicycle Implementation

N. B. Dodge 9/15

Erik Jonsson School of Engineering and

Computer Science

The University of Texas at Dallas

Comparative Instruction Timing

One clock cycle (= one instruction cycle)

PC update time

Instructions accessed and inputs to register and op decoders stable

Op and function codes decoded and stable

Register outputs (operands) stable

ALU processing complete

Memory accessed and data storage or read complete

Data written to write (destination) register if necessary

Jumps and branches completed about here

Register-register instructions done about here

26

Lecture # 19: Control Unit Design and Multicycle Implementation

N. B. Dodge 9/15

The University of Texas at Dallas

Erik Jonsson School of Engineering and

Computer Science

Multicycle Implementation

A solution to the single-cycle problem is stated as

follows:

Each instruction has several phases, such as fetch/decode,

register selection, ALU processing, etc.

Instead of using a single clock cycle for the whole instruction,

run the clock much faster, and have a single clock cycle for

each of the elements or phases of the instruction process.

Many instructions take fewer phases (for example, jump,

branch [the fewest phases], register-register or store

instructions), so these instructions execute much faster.

As most instructions execute faster than the longest

instructions (such as lw), the average instruction time will be

reduced substantially.

27

Lecture # 19: Control Unit Design and Multicycle Implementation

N. B. Dodge 9/15

The University of Texas at Dallas

Erik Jonsson School of Engineering and

Computer Science

MIPS Multicycle Concept

Split the processing into five processing segments.

Run the clock much faster (essentially 5X faster!).

Do one instruction segment per clock cycle.

PC updates, branches and jumps take 3 processing

segments since they are simpler; they run much faster.

Register-register instructions do not require memory

access. They take four instruction segments and finish

in about 30% more time than jumps and branches.

Only load memory-access instructions take a full five

processing segments (store takes only four), but do not

slow down the other instructions to their speed.

28

Lecture # 19: Control Unit Design and Multicycle Implementation

N. B. Dodge 9/15

Erik Jonsson School of Engineering and

Computer Science

The University of Texas at Dallas

Multicycle Implementation

P

C

Instruction

Fetch

Instruction

Decode/

Register

Fetch

Instruction

Memory

Register

Block

ALU

Execution

ALU

Memory

Access

(if

required)

Data

Memory

Data

Writeback

Register

Block

Skipped for jump and

branch instructions

Op/Fn

1 clock

cycle

29

Skipped for

reg.-reg. inst.

1 clock

1 clock

1 clock

cycle

cycle

cycle

All five segments (five clock cycles) required only for load instructions

Lecture # 19: Control Unit Design and Multicycle Implementation

Skipped for

store inst.

1 clock

cycle

N. B. Dodge 9/15

Erik Jonsson School of Engineering and

Computer Science

The University of Texas at Dallas

Instruction Cycle Times

Instruction

Step

30

RType

Memory

Reference

Branches

Jumps

Instruction

Fetch

Fetch instruction at address [PC]

[PC][PC+4]

Instruction

Decode /Register

Fetch

Register operands fetched; Instruction decoded and control units activate

appropriate ALU components

Instruction

Execution

ALU output = result

of operation on

register operand(s)

ALU output is

mem. address for

load/store

If condition met,

[PC]address

output of ALU

PC address is instr.

[0-25] (shifted 2

places) + [PC 28-31]

Memory Access or

ALU Data

Writeback

Logical/shift/math

operation result

written to dest. reg.

Reg. data stored or

data accessed for

load to dest. reg.

---

---

Memory Data

Writeback

---

Data written to

destination register

---

---

Lecture # 19: Control Unit Design and Multicycle Implementation

N. B. Dodge 9/15

The University of Texas at Dallas

Erik Jonsson School of Engineering and

Computer Science

Multicycle Advantages

For most instructions, we save 20-40% in clock cycles

and our processor is much faster, as mentioned earlier.

Since different parts of the circuit are active only for

one cycle at a time, we can use less circuitry because

parts of the computer can be reused in different cycles.

The CPU now needs only one ALU, since it can do the PC

update functions prior to the ALU processing.

Since we access memory for data and instructions in different

clock cycles, we only need one path to memory.

31

Lecture # 19: Control Unit Design and Multicycle Implementation

N. B. Dodge 9/15

The University of Texas at Dallas

Erik Jonsson School of Engineering and

Computer Science

Major Impediment to Multicycle Implementation

Our multicycle processor takes up to 5 clock cycles to

complete an instruction.

Each time the clock ticks, part of the instruction is

completed, not all of it.

That means that at the end of each clock cycle, we have

partial instruction results, but no place to store them!

A first concern is therefore a way to store intermediate

data as the instruction winds its way through the

various segments of processing.

32

Lecture # 19: Control Unit Design and Multicycle Implementation

N. B. Dodge 9/15

Erik Jonsson School of Engineering and

Computer Science

The University of Texas at Dallas

Intermediate Results Storage Requirements

Reg. Dest.

32

32

ADD

+4

Instruction

Address

Instruction bits 0-31

P

C

6 (Bits 26-31)

Inst.

0-31

Instruction

Memory

Need instruction

storage here

33

5

5

Control

Branch

Mem. Read

Mem. To Reg.

ALU Op.

Mem. Write

ALU Srce.

Reg. Write

M

32

U

X

32

ADD

Left

shift

2

Need

read

data

storage

here

32

Rs

Read

Data 1

Rt

M 5

U

Rd

X

Write

Data

Read

Data 2

32

Write

ALU

32

M

32

U

X

Reg. Block

16 (Bits 0-15)

Sign 32

Extend

ALU

6 (Bits 0-5) Control

Need operand storage here

Lecture # 19: Control

32

Data

Address

Write

Data

Read

Mem./Reg.

Select

Read 32

Data

32

M 32

U

X

Data

Memory

Need ALU out storage here

After David A. Patterson and John L. Hennessy, Computer Organization and Design, 2nd Edition

N. B. Dodge 9/15

Unit Design and Multicycle Implementation

Erik Jonsson School of Engineering and

Computer Science

The University of Texas at Dallas

Memory

Out

Write

Data

Memory

Memory

Data

Register

Instr.

21-25

Instr.

16-20

Instruction 0-31

Memory

Address

Instruction Register

First-Pass Register Placement

Rs

Rt

Inst.

11-15

Rd

Read

Data 1

Read

Data 2

ALU

ALU

Out

Write Data

Reg. Block

Instr. 0-15

After David A. Patterson and John L. Hennessy, Computer Organization and Design, 2nd Edition

34

Lecture # 19: Control Unit Design and Multicycle Implementation

N. B. Dodge 9/15

Erik Jonsson School of Engineering and

Computer Science

The University of Texas at Dallas

Memory

Out

Write

Data

Memory

Note memory

data path

simplified

Memory

Data

Register

Instr.

21-25

Instr.

16-20

Instruction 0-31

Memory

Address

Instruction Register

Preliminary Multicycle Design Without Control

Ins.

1115

M

U

X

Rs

Rt

Rd

Read

Data 1

Read

Data 2

B

4

Write Data

M

U

X

Reg. Block

Sign

Extend

Instr. 0-15

ALU

Left

shift

2

M

U

X

ALU

Out

ALU now serves

jump/branch

PC update function

Instr. 0-5

After David A. Patterson and John L. Hennessy, Computer Organization and Design, 2nd Edition

Our preliminary multicycle processing design is more compact.

35

Lecture # 19: Control Unit Design and Multicycle Implementation

N. B. Dodge 9/15

Erik Jonsson School of Engineering and

Computer Science

The University of Texas at Dallas

Multicycle Design with ALU Control and PC

M

U

X

Memory

Address

Memory

Out

Write

Data

Memory

Memory

Data

Register

Instr.

21-25

Instr.

16-20

Instruction 0-31

P

C

Instruction Register

PC 0-31

Ins.

1115

M

U

X

M

U

X

Rs

Rt

Rd

Read

Data 1

Read

Data 2

B

4

Write Data

M

U

X

ALU

M

U

X

Reg. Block

Sign

Instr. 0-15 Extend

ALU

Out

ALU

Control

Left

shift

2

Instr. 0-5

After David A. Patterson and John L. Hennessy, Computer Organization and Design, 2nd Edition

36

Lecture # 19: Control Unit Design and Multicycle Implementation

N. B. Dodge 9/15

Erik Jonsson School of Engineering and

Computer Science

The University of Texas at Dallas

Completed Multicycle Design

PC Source

PC Write Cond.

PC Write

ALU Op.

Inst. / Data

Mem. Read

ALU Srce. B

Mem. Write

Mem. To. Reg.

Control

Reg. Write

Inst. Reg. Write

Memory

Out

Write

Data

Memory

PC 0-31

Instruction 0-31

Memory

Address

Instruction Register

M

U

X

Instr. 0-25

Reg. Dest.

Instr. 26-31

P

C

PC 28-31

ALU Srce. A

Instr.

21-25

Instr.

16-20

Ins.

1115

Memory

Data

Register

M

U

X

M

U

X

Rs

Rt

Rd

Read

Data 1

Read

Data 2

Reg. Block

Sign

Instr. 0-15 Extend

ALU

4

Write Data

M

U

X

Left

shift

2

M

U

X

M

U

X

ALU

Out

ALU

Control

Left

shift

2

Instr. 0-5

37

Lecture # 19: Control Unit

After David A. Patterson and John L. Hennessy, Computer Organization and Design, 2nd Edition

N. B. Dodge 9/15

Design and Multicycle Implementation

Erik Jonsson School of Engineering and

Computer Science

The University of Texas at Dallas

Multicycle Summary

Cont.

P

C

Reg.

Memory

ALU

B

ALU

Op.

We have redesigned the MIPS CPU to accommodate a 5-segment

instruction partition with each segment taking one clock cycle.

In doing so, instruction execution time was decreased ~ 30-40%

and greater efficiency was obtained by reducing the circuitry.

In the next lecture, we will take the final step in the MIPS design

and complete the R2000 architecture.

38

Lecture # 19: Control Unit Design and Multicycle Implementation

N. B. Dodge 9/15

The University of Texas at Dallas

Erik Jonsson School of Engineering and

Computer Science

Exercise 2

On the Complete Multicycle Design Diagram

on the next page, do the following:

1. Summarize the inputs into the lower MUX to the

ALU.

2. Why is the 16-bit sign-extender input directly to the

ALU in one case and left-shifted two places in the

other?

3. Why is the output of the ALU sent directly to the

MUX that inputs an instruction address into the

PC?

39

Lecture # 19: Control Unit Design and Multicycle Implementation

N. B. Dodge 9/15

Print out a copy of this diagram and bring to class.

PC Source

PC Write Cond.

PC Write

ALU Op.

Inst. / Data

Mem. Read

ALU Srce. B

Mem. Write

Mem. To. Reg.

Control

Reg. Write

Inst. Reg. Write

Memory

Out

Write

Data

Memory

Memory

Data

Register

PC 0-31

Instruction 0-31

Memory

Address

Instruction Register

M

U

X

Instr. 0-25

Reg. Dest.

Instr. 26-31

P

C

PC 28-31

ALU Srce. A

Instr.

21-25

Instr.

16-20

Ins.

1115

M

U

X

M

U

X

Rs

Rt

Rd

Read

Data 1

Read

Data 2

Reg. Block

Sign

Instr. 0-15 Extend

ALU

4

Write Data

M

U

X

Left

shift

2

M

U

X

ALU

Control

Left

shift

2

Instr. 0-5

Lecture # 19: Control Unit Design and Multicycle Implementation

M

U

X

ALU

Out

You might also like

- Unit 1 Processor Datapath Design: o o o oDocument30 pagesUnit 1 Processor Datapath Design: o o o oanonimoNo ratings yet

- Basic Computer Organization and Design: - Computer Registers - Instruction CycleDocument21 pagesBasic Computer Organization and Design: - Computer Registers - Instruction CycleShashank PandeyNo ratings yet

- Computer Architecture MIPS Processor DescriptionDocument41 pagesComputer Architecture MIPS Processor DescriptionAsif HussainNo ratings yet

- CPS 104 Computer Organization and Programming Lecture-19: Busses, Registers, Building A DatapathDocument29 pagesCPS 104 Computer Organization and Programming Lecture-19: Busses, Registers, Building A DatapathprachesNo ratings yet

- Unit1 Addressing Modes and GPRDocument70 pagesUnit1 Addressing Modes and GPRsaumya2213215No ratings yet

- Lec18 PDFDocument31 pagesLec18 PDFMustafa Rashik HasnainNo ratings yet

- Processor Design: How To Implement MIPS Simplicity Favors RegularityDocument7 pagesProcessor Design: How To Implement MIPS Simplicity Favors RegularityNarender KumarNo ratings yet

- CpuDocument51 pagesCpujunaidalighouriNo ratings yet

- w3 2004-09-29 Blackfin - Architecture v1Document56 pagesw3 2004-09-29 Blackfin - Architecture v1bhanu455No ratings yet

- VHDL Come Strumento Di Progettazione Per Circuiti Digitali VLSIDocument23 pagesVHDL Come Strumento Di Progettazione Per Circuiti Digitali VLSIunibfeNo ratings yet

- 2-Instruction Set ArchitectureDocument31 pages2-Instruction Set ArchitectureHasanLatifNo ratings yet

- Mips DatapathDocument23 pagesMips DatapathKaran KampaniNo ratings yet

- 8 Bit Risc Processor PresentationDocument36 pages8 Bit Risc Processor PresentationSantanu KumarNo ratings yet

- Introduction To MicrocontrollersDocument52 pagesIntroduction To MicrocontrollersSanjayaRangaLSenavirathnaNo ratings yet

- CENG 331 Course Slides Chapter 5Document73 pagesCENG 331 Course Slides Chapter 5Odunayo KusoroNo ratings yet

- Advanced Digital DesignDocument11 pagesAdvanced Digital DesignAli AhmadNo ratings yet

- Topic01B Introdiuction To Microprocessor and MicroControllers Part 2Document63 pagesTopic01B Introdiuction To Microprocessor and MicroControllers Part 2Brett WildermothNo ratings yet

- EE313 PPT Sem1 2015Document192 pagesEE313 PPT Sem1 2015Anonymous oajJpyfmlNo ratings yet

- Lec 11Document42 pagesLec 11gusgifNo ratings yet

- CPU DesignDocument66 pagesCPU DesignAnonymous 0u4X6mgWPNo ratings yet

- CPS 104 Computer Organization and Programming Lecture-18: Memory Elements, Busses, RegistersDocument26 pagesCPS 104 Computer Organization and Programming Lecture-18: Memory Elements, Busses, RegistersprachesNo ratings yet

- CSA CompleteDocument196 pagesCSA CompleteNishant SehgalNo ratings yet

- Basic Performance EquationDocument42 pagesBasic Performance EquationVishal BasugadeNo ratings yet

- Controlling A Pipelined DatapathDocument17 pagesControlling A Pipelined DatapathAlexander TaylorNo ratings yet

- MP8085 Lab ManualDocument179 pagesMP8085 Lab ManualEvan3333No ratings yet

- Multicycle Datapath PDFDocument22 pagesMulticycle Datapath PDFShivam KhandelwalNo ratings yet

- The Pipelined RiSC-16 ComputerDocument9 pagesThe Pipelined RiSC-16 Computerkb_lu232No ratings yet

- ECE 485 Computer Organization and Design: D I Mips CPU M DDocument32 pagesECE 485 Computer Organization and Design: D I Mips CPU M DAkhila kommireddyNo ratings yet

- Chap5 Processor Part-IIDocument21 pagesChap5 Processor Part-IIIsra NazeerNo ratings yet

- Microprocessor ApplicationsDocument100 pagesMicroprocessor Applicationsjai prakashNo ratings yet

- Basic Computer Organization and DesignDocument35 pagesBasic Computer Organization and DesignVinay KumarNo ratings yet

- Cpu Design 2Document16 pagesCpu Design 2Parth ChauhanNo ratings yet

- CS M151B / EE M116C: Computer Systems ArchitectureDocument34 pagesCS M151B / EE M116C: Computer Systems ArchitecturetinhtrilacNo ratings yet

- Creating IPCore Loi 11may2013Document20 pagesCreating IPCore Loi 11may2013LinkyNo ratings yet

- DatapathDocument34 pagesDatapathRoger LikesNo ratings yet

- Sap 1Document54 pagesSap 1ICANSAP0% (3)

- Today - Finish Single-Cycle Datapath/control Path - Look at Its Performance and How To Improve ItDocument28 pagesToday - Finish Single-Cycle Datapath/control Path - Look at Its Performance and How To Improve Itsalloum18No ratings yet

- EC 8791 ERTS 2 MarksDocument24 pagesEC 8791 ERTS 2 Marksdeenandhini b100% (2)

- Basic Computer OrganizationDocument23 pagesBasic Computer OrganizationKibrom HaftuNo ratings yet

- COA Unit 3Document52 pagesCOA Unit 3guptakrishns23No ratings yet

- Computer Architecture Instruction Set GuideDocument65 pagesComputer Architecture Instruction Set GuideHexy ManucianNo ratings yet

- Design and Performance Analysis of 8-Bit RISC Processor Using Xilinx & Microwind ToolDocument10 pagesDesign and Performance Analysis of 8-Bit RISC Processor Using Xilinx & Microwind ToolRakeshconclaveNo ratings yet

- Basic Computer Organization and DesignDocument35 pagesBasic Computer Organization and Designabhisrit2008No ratings yet

- Basic SAP-1 Computer Architecture ExplainedDocument9 pagesBasic SAP-1 Computer Architecture ExplainedAshna100% (1)

- Instruction CodesDocument35 pagesInstruction Codesanilk_patiNo ratings yet

- COA Module 2 NotesDocument46 pagesCOA Module 2 NotesAssini HussainNo ratings yet

- MIPS Datapath IF DecoderDocument14 pagesMIPS Datapath IF DecoderMartin Fuentes AcostaNo ratings yet

- C For PICDocument10 pagesC For PICkapadapaNo ratings yet

- Unitronics V130, V350, V570 DF 1 Communication "How It Is Made" 1 CommonDocument8 pagesUnitronics V130, V350, V570 DF 1 Communication "How It Is Made" 1 CommonEdwin Vitovis TorresNo ratings yet

- PLMU Computer Studies Dept SAP-1 modificationDocument17 pagesPLMU Computer Studies Dept SAP-1 modificationJaysen GeronimoNo ratings yet

- Dire Dawa University Institute of TechnologyDocument28 pagesDire Dawa University Institute of TechnologyAsed ZakirNo ratings yet

- Lec13 PDFDocument24 pagesLec13 PDFMustafa Rashik HasnainNo ratings yet

- 4 Types of Microoperations in RegistersDocument79 pages4 Types of Microoperations in RegistersSriram MurthyNo ratings yet

- 8085 Processor Unit I: Mr. S. VinodDocument52 pages8085 Processor Unit I: Mr. S. VinodVinod SrinivasanNo ratings yet

- BME 438 Digital Logic Design and Computer Architecture LabDocument73 pagesBME 438 Digital Logic Design and Computer Architecture LabHafiz Muhammad Ahmad RazaNo ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- Lec21 PDFDocument68 pagesLec21 PDFMustafa Rashik HasnainNo ratings yet

- Lec20 PDFDocument49 pagesLec20 PDFMustafa Rashik HasnainNo ratings yet

- Lec18 PDFDocument31 pagesLec18 PDFMustafa Rashik HasnainNo ratings yet

- Lec15 PDFDocument26 pagesLec15 PDFMustafa Rashik HasnainNo ratings yet

- Lec12 PDFDocument30 pagesLec12 PDFMustafa Rashik HasnainNo ratings yet

- Developing A Program in SPIM: - by Now, If You Have Been Doing All The Homework andDocument37 pagesDeveloping A Program in SPIM: - by Now, If You Have Been Doing All The Homework andMustafa Rashik HasnainNo ratings yet

- Shift and Rotate Instructions Facilitate Manipulations ofDocument32 pagesShift and Rotate Instructions Facilitate Manipulations ofMustafa Rashik HasnainNo ratings yet

- EE 2310 Is A Required Course, Prerequisite For EE 3320/3120Document52 pagesEE 2310 Is A Required Course, Prerequisite For EE 3320/3120Mustafa Rashik HasnainNo ratings yet

- Lec11 PDFDocument45 pagesLec11 PDFMustafa Rashik HasnainNo ratings yet

- Lec9 PDFDocument46 pagesLec9 PDFMustafa Rashik HasnainNo ratings yet

- Lec13 PDFDocument24 pagesLec13 PDFMustafa Rashik HasnainNo ratings yet

- Exclusive OR/Exclusive NOR (XOR/XNOR) : XOR/XNOR Truth Table Xor B A Xnor B 0 0 0 1 0 1 1 0 1 0 1 0 1 1 0 1Document30 pagesExclusive OR/Exclusive NOR (XOR/XNOR) : XOR/XNOR Truth Table Xor B A Xnor B 0 0 0 1 0 1 1 0 1 0 1 0 1 1 0 1Mustafa Rashik Hasnain100% (1)

- Lec10 PDFDocument26 pagesLec10 PDFMustafa Rashik HasnainNo ratings yet

- Lec8 PDFDocument45 pagesLec8 PDFMustafa Rashik HasnainNo ratings yet

- Lec 3Document25 pagesLec 3Bryant SiegfriedNo ratings yet

- Lec7 PDFDocument37 pagesLec7 PDFMustafa Rashik HasnainNo ratings yet

- Lec4 Digital LogicDocument40 pagesLec4 Digital Logicalphabennydelta4468No ratings yet

- K-Map LessonsDocument32 pagesK-Map LessonsmikkoNo ratings yet

- Lec2 PDFDocument36 pagesLec2 PDFMustafa Rashik HasnainNo ratings yet

- Steca TR 0603 Specification enDocument2 pagesSteca TR 0603 Specification enForrester de Beer0% (1)

- Sany Crane-Brochure STC800T5-083545Document26 pagesSany Crane-Brochure STC800T5-083545Romario OliveiraNo ratings yet

- Industrial Gigabit Ethernet PHY Reference DesignDocument19 pagesIndustrial Gigabit Ethernet PHY Reference DesignNguyễn Hữu TàiNo ratings yet

- h6 Brochure WebDocument9 pagesh6 Brochure WebMadanagopal ManiNo ratings yet

- CV Carb Part 2 WebDocument4 pagesCV Carb Part 2 WebkanwarNo ratings yet

- SM MultiV IV Air Outdoor Units 4 15 - 20150414080917Document150 pagesSM MultiV IV Air Outdoor Units 4 15 - 20150414080917Gino Waximinguirijillo Santana100% (3)

- Manual Servico Sony HCD Gpx5Document68 pagesManual Servico Sony HCD Gpx5Realmember FoxNo ratings yet

- Memory Built-In Self-Repair Using Redundant WordsDocument7 pagesMemory Built-In Self-Repair Using Redundant Wordsaditya_pundirNo ratings yet

- All About Op Amplifier-CollectionDocument105 pagesAll About Op Amplifier-CollectionAnonymous DjWqKpZ1No ratings yet

- RCF ART705AS-Base Amp SubDocument3 pagesRCF ART705AS-Base Amp SubHaroldo CosmeNo ratings yet

- 2290 Breakdown Leakage App NoteDocument4 pages2290 Breakdown Leakage App NoteIng del PeleNo ratings yet

- If Installing A New Clutch Go To Step 19. 2. Install The Special Tool in A ViseDocument18 pagesIf Installing A New Clutch Go To Step 19. 2. Install The Special Tool in A Viserolly abantoNo ratings yet

- Method Statement of HV TestDocument4 pagesMethod Statement of HV TestRavi Kumar80% (5)

- Current Differential Relay ManualDocument4 pagesCurrent Differential Relay Manualppraveenkumar79No ratings yet

- 1009-S1-EL-EAR-4001 - 0 - SV1 - Electrical Outdoor Earthing LayoutDocument1 page1009-S1-EL-EAR-4001 - 0 - SV1 - Electrical Outdoor Earthing LayoutRashmi Ranjan MohantyNo ratings yet

- Heating SystemsDocument30 pagesHeating SystemsEmmanuel BuhwaNo ratings yet

- Rock dowel installation requirementsDocument4 pagesRock dowel installation requirementsMohamed SafrasNo ratings yet

- User Manual: EV1000 Series General Purpose Variable Speed DriveDocument159 pagesUser Manual: EV1000 Series General Purpose Variable Speed DriveEngenharia SematexNo ratings yet

- Database-Mm2100 Company Name ListDocument15 pagesDatabase-Mm2100 Company Name ListRina RachmanNo ratings yet

- Siłowniki UMB, Power-PackDocument6 pagesSiłowniki UMB, Power-PackLitsaNo ratings yet

- Rectifier Diodes BYW29 Series Ultrafast: General Description Quick Reference DataDocument6 pagesRectifier Diodes BYW29 Series Ultrafast: General Description Quick Reference DataEddy Santiago Neira SisaNo ratings yet

- SONY LCD TV Bravia KLV-S26A10Document80 pagesSONY LCD TV Bravia KLV-S26A10Ricardo Chaman ChavezNo ratings yet

- Geared VS Gearless Drive Solutions For Grinding MillsDocument15 pagesGeared VS Gearless Drive Solutions For Grinding MillsLuis B100% (1)

- Peki Adzokoe J.H.S Information and Comunication Technology Form 1, Test IiDocument2 pagesPeki Adzokoe J.H.S Information and Comunication Technology Form 1, Test IiPelsin VisualsNo ratings yet

- First Summative Test in CSS 1Document3 pagesFirst Summative Test in CSS 1Ricky Rom MonteNo ratings yet

- Delta 36-812 Manual and SchematicDocument38 pagesDelta 36-812 Manual and SchematiclukeleohunterNo ratings yet

- Maintenance-Free Valve Regulated Lead-Acid BatteriesDocument4 pagesMaintenance-Free Valve Regulated Lead-Acid BatteriesJayson EnrileNo ratings yet

- tm1606 TXTX178649Document10 pagestm1606 TXTX178649Ber HonzaNo ratings yet

- Simple CPU DesignDocument31 pagesSimple CPU Designanshulchauhan007No ratings yet

- Monatari Gearless-Mgv25mDocument16 pagesMonatari Gearless-Mgv25mminhasranaNo ratings yet