Professional Documents

Culture Documents

Creación de Programa Por Componentes

Uploaded by

Brandon ArevaloOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Creación de Programa Por Componentes

Uploaded by

Brandon ArevaloCopyright:

Available Formats

Creacin del programa con

Componentes o

subcircuitos

VHDL - Xilinx ISE Software

Danilo A. Garca-Hansen

Subcircuitos o componentes

Una entidad de VHDL en un archivo

de cdigo fuente puede usarse como

un subcircuito.

Subcircuito = Componente

La idea es no usar esquemticos

Ejemplo: Sumador Completo 4 bits

La entidad en el archivo es como

tal un componente

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity FULLADD is

Port ( cin, A, B : in STD_LOGIC;

s, cout : out STD_LOGIC);

end FULLADD;

architecture logica of FULLADD is

begin

s<=A xor B xor cin;

cout<= ( A and B) or (cin and A) or (cin and B);

end logica;

Utilizacin de los componentes

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity SUMADOR4 is

Port ( CIN : in STD_LOGIC;

A ,B : in STD_LOGIC_VECTOR(3 DOWNTO 0);

S : out STD_LOGIC_VECTOR(3 DOWNTO 0);

COUT : out STD_LOGIC);

end SUMADOR4;

architecture ESTRUCTURA of SUMADOR4 is

SIGNAL C: STD_LOGIC_VECTOR( 3 DOWNTO 1);

COMPONENT FULLADD

PORT (CIN,A,B: IN STD_LOGIC;

S,COUT: OUT STD_LOGIC);

END COMPONENT;

BEGIN

ETAPA0: FULLADD

ETAPA1: FULLADD

ETAPA2: FULLADD

ETAPA3: FULLADD

end ESTRUCTURA;

PORT MAP (CIN,A(0),B(0),S(0),C(1));

PORT MAP (C(1),A(1),B(1),S(1),C(2));

PORT MAP (C(2),A(2),B(2),S(2),C(3));

PORT MAP (C(3),A(3),B(3),S(3),COUT);

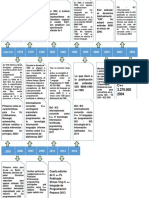

Aspecto del proyecto con los

subcircuitos o componentes

instanciados

Si las seales no estn en el

mismo orden en que fueron

declaradas

ETAPA3: FULLADD PORT MAP (

A=>A(3), B=>B(3), CIN=>C(3), S=>S(3), COUT=>COUT);

Ejemplo 2: Contador Dcadas

Componente 1:Divisor de 50000.000

Componente 2: Contador dcadas (0-9)

Principal: Ensamble del circuito

Archivo de pines (.ucf)

## Clock pin for Nexys 2 Board:

NET "CLKIN"

LOC = "B8";

## Leds

NET "SALIDA<0>"

NET "SALIDA<1>"

NET "SALIDA<2>"

NET "SALIDA<3>"

LOC

LOC

LOC

LOC

=

=

=

=

"J14";

"J15";

"K15";

"K14";

Aspecto del proyecto con los subcircuitos

o componentes instanciados

Ejemplo 3: Uso de bloques

combinacionales y secuenciales.

--------------------------------------------------- Creado por Danilo A. Garcia-Hansen

-- Escuela Colombiana de Ingeniera

--------------------------------------------------library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

Este es el listado del

programa principal.

Contiene dos componentes,

un contador y un

multiplexor

entity CIRCUITO is

Port ( CLK_PPAL : in STD_LOGIC;

PORT_IN : in STD_LOGIC_VECTOR (3 downto 0);

S0 : in STD_LOGIC;

S1 : in STD_LOGIC;

PORT_OUT : out STD_LOGIC_VECTOR (3 downto 0));

end CIRCUITO;

architecture ARQ_CTO of CIRCUITO is

SIGNAL DIVISOR: STD_LOGIC_VECTOR(23 DOWNTO 0);

SIGNAL

SIG1, SIG2, SIG3: STD_LOGIC_VECTOR(3 DOWNTO 0);

COMPONENT CONT_4BITS

Port ( CLK: in STD_LOGIC;

Q : INOUT STD_LOGIC_VECTOR (3 downto 0));

end COMPONENT;

--contina

Continuacin del listado principal

--continuacin

COMPONENT MUX4CH is

Port ( A : in STD_LOGIC_VECTOR (3 downto 0);

B : in STD_LOGIC_VECTOR (3 downto 0);

S : in STD_LOGIC;

Y : OUT STD_LOGIC_VECTOR (3 downto 0));

end COMPONENT;

begin

PROCESS(CLK_PPAL) -- DIVISOR DE FRECUENCIA

BEGIN

IF (CLK_PPAL' EVENT AND CLK_PPAL='1) THEN

DIVISOR<=DIVISOR+1;

END IF;

END PROCESS;

CONTADOR1: CONT_4BITS PORT MAP (DIVISOR(23),SIG1);

CONTADOR2: CONT_4BITS PORT MAP (DIVISOR(20),SIG2);

MUX1: MUX4CH PORT MAP (SIG1, SIG2, S0, SIG3);

MUX2: MUX4CH PORT MAP (SIG3, PORT_IN, S1, PORT_OUT);

end ARQ_CTO;

Componente 1: Contador de 4 bits

--------------------------------------------------- Creado por Danilo A. Garcia-Hansen

-- Escuela Colombiana de Ingeniera

--------------------------------------------------library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity CONT_4BITS is

Port ( CLK: in STD_LOGIC;

Q : INOUT STD_LOGIC_VECTOR (3 downto 0));

end CONT_4BITS;

architecture ARQ_CONTADOR of CONT_4BITS is

begin

process (CLK)

begin

if (CLK='1' and CLK'event) then

Q<=Q + 1;

end if;

end process;

end ARQ_CONTADOR;

Componente 2: Multiplexor cudruple de 2 canales

--------------------------------------------------- Creado por Danilo A. Garcia-Hansen

-- Escuela Colombiana de Ingeniera

--------------------------------------------------library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity MUX4CH is

Port ( A : in STD_LOGIC_VECTOR (3 downto 0);

B : in STD_LOGIC_VECTOR (3 downto 0);

S : in STD_LOGIC;

Y : OUT STD_LOGIC_VECTOR (3 downto 0));

end MUX4CH;

architecture ARQ_MUX of MUX4CH is

begin

process (S,A,B)

begin

case S is

when '0' => Y <= A;

when others => Y <= B;

end case;

end process;

end ARQ_MUX;

You might also like

- Programacion BlackberryDocument17 pagesProgramacion BlackberrydestradarNo ratings yet

- 771 Introduccion Programacion Computacion 2 D LabDocument5 pages771 Introduccion Programacion Computacion 2 D LabGerardo ChayNo ratings yet

- Entregable 1Document1 pageEntregable 1gumontesNo ratings yet

- 8086Document9 pages8086China ArNo ratings yet

- POO - Programación Orientada A Objetos: Unidad Que Imparte: Curso: Unidad ResponsableDocument8 pagesPOO - Programación Orientada A Objetos: Unidad Que Imparte: Curso: Unidad ResponsableOmar Sulca CorreaNo ratings yet

- Resumen Yo RobotDocument8 pagesResumen Yo RobotAlejandro MedinaNo ratings yet

- SW 2Document13 pagesSW 2Israel PaviaNo ratings yet

- Crear Tu Primer Script PHPDocument2 pagesCrear Tu Primer Script PHPBladymir Capcha ChavezNo ratings yet

- El Algebra Lineal La Podemos Ocupar en Diferentes Ámbitos de La IngenieríaDocument3 pagesEl Algebra Lineal La Podemos Ocupar en Diferentes Ámbitos de La IngenieríaMariana Diaz100% (1)

- Linea TiempoDocument2 pagesLinea TiempoAlba Pedregón67% (3)

- Introducción A Stata2 PDFDocument21 pagesIntroducción A Stata2 PDFJuan David Cárdenas AponteNo ratings yet

- Control de Nivel de Líquidos Con TIA PORTAL - FACTORY I/ODocument11 pagesControl de Nivel de Líquidos Con TIA PORTAL - FACTORY I/OPedro CorderoNo ratings yet

- Manual de Usuario Módulo de Programación Multianual 2018 - 2020Document188 pagesManual de Usuario Módulo de Programación Multianual 2018 - 2020UlisesBorchaniNo ratings yet

- Curso de Mantenimiento y Ensamblaje de ComputadorasDocument2 pagesCurso de Mantenimiento y Ensamblaje de ComputadorasgruzuetNo ratings yet

- BlasterDocument5 pagesBlasterElsword DarkNo ratings yet

- Formulario Integracion Numerica Mayo 2014Document2 pagesFormulario Integracion Numerica Mayo 2014Ziry Yamily GarciaNo ratings yet

- Seguridad Simple y Sencilla para DummiesDocument39 pagesSeguridad Simple y Sencilla para DummiesJaimeNo ratings yet

- Diseño de Base de Datos Clase 5Document3 pagesDiseño de Base de Datos Clase 5Cristian Soto ParionaNo ratings yet

- Manual de Oracle Xe 11gDocument14 pagesManual de Oracle Xe 11gdani9410_No ratings yet

- Curso de Mantenimiento de PCDocument19 pagesCurso de Mantenimiento de PCsenacaqueza100% (6)

- 01 Formulacion Programacion Lineal 1Document33 pages01 Formulacion Programacion Lineal 1Saul CamargoNo ratings yet

- Apuntes de Clase de AlgoritmosDocument216 pagesApuntes de Clase de AlgoritmosNelson F Beltrán F100% (9)

- CCNA 4 V6 Capitulo 7Document5 pagesCCNA 4 V6 Capitulo 7Catherine ScarletNo ratings yet

- Puertos de Entrada/SalidaDocument5 pagesPuertos de Entrada/SalidaAlán Montes De Oca ArcosNo ratings yet

- E. 8Document5 pagesE. 8Salome AlvarezNo ratings yet

- Signos Convencionales Final PDFDocument11 pagesSignos Convencionales Final PDFRaul Machaca PumalequeNo ratings yet

- Resumen Temario UOC Asignatura SRC/SXCDocument43 pagesResumen Temario UOC Asignatura SRC/SXCAlfonso Carlos Alvarez ReyesNo ratings yet

- 8086Document6 pages8086pmfornerisNo ratings yet

- Informatica Prerifericos de Entrada y SalidaDocument15 pagesInformatica Prerifericos de Entrada y SalidaAlberto Polanco CasaresNo ratings yet

- Lab Sistemas MIcroprocesados Practica2 2017A PDFDocument5 pagesLab Sistemas MIcroprocesados Practica2 2017A PDFbryansolorzanoNo ratings yet