Professional Documents

Culture Documents

Microcontroladores 2 Exercicios Macro e Microarquitetura v2

Uploaded by

Marcelo LimaOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Microcontroladores 2 Exercicios Macro e Microarquitetura v2

Uploaded by

Marcelo LimaCopyright:

Available Formats

UFPI - UNIVERSIDADE FEDERAL DO PIAU

CENTRO DE TECNOLOGIA

CURSO DE ENGENHARIA ELTRICA

MICROCONTROLADORES

Prof. MARCOS ZURITA

Abril / 2012

MICROARQUITETURA & MACROARQUITETURA EXERCCIOS

(Adaptao do livro Organizao Estruturada de Computadores, A.S. Tanenbaum, 4 Ed., Cap. 4)

Decodificador

4

16

(Read, Write, Fetch)

MAR

MPC

000000001

MDR

PC

Memria de Controle

MBR

8

SP

MIR - MicroInstruction Register

LV

NEXT

ADDRESS

CPP

TOS

J J J

MA A

P MM

CNZ

W F

SS

I

R

EE I

OTC

M M R E BarraLRFF

N

LSP

E

NN N HPOP

DA I

T mento

LA0 1

V

VPC

A

AB C CSP

RR T C

B

8 1

A

D

E H

000000000 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0000

OPC

H

C

Bit de

mais alta

ordem

ULA

ADDR[8]

2

Flip-flops

(1 bit cada)

(Read,

Write,

Fetch)

Deslocador

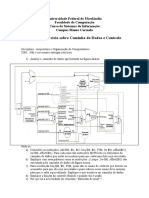

Fig. 1: Diagrama de blocos do MIC-1

1) A Tabela 1 mostra uma maneira de fazer com que A

aparea na sada da ULA. Sabendo que cada um

dos 32 bit slices da ULA implementado conforme

a Fig. 2, determine outra combinao binria que

desempenhe a mesma funo. 011101

F0 F1 ENA ENB INVA INC FUNO

0 1

1

0

0

0

A

0

0

1

1

0

1

1

0

0

1

0

0

B

A

1

1

0

1

1

1

1

1

0

0

0

0

B

A+B

1

1

1

1

1

1

1

0

0

0

1

1

A+B+1

A+1

1

1

1

1

0

1

1

1

0

1

1

1

B+1

B -A

1

1

1

1

0

1

1

0

1

1

0

1

B-1

-A

0

0

0

1

1

1

1

1

0

0

0

0

A AND B

A OR B

0

0

1

1

0

0

0

0

0

0

0

1

0

1

-1

Tabela 1: Funes teis da ULA

Fig. 2: Bit slice da ULA

2) Com base no diagrama da Fig. 2, demonstre qual

funo a ULA deve desempenhar quando:

F0 F1 ENA ENB INC INVA

1 1

0

1

1

1

3) Aps implementar o MIC-1 em laboratrio (Fig. 1),

voc mede os tempos de propagao do circuito e

avergua que o mesmo gasta 1ns para carregar o

MIR, 1ns para habilitar um registrador para que

este coloque seu contedo no barramento B, 3ns

aguardando a operao da ULA e do deslocador, e

1ns para que os resultados se propaguem de volta

aos registradores. Se o intervalo alto do clock no

pode ser inferior a 2ns para que o sequenciador

funcione corretamente, determine a mxima

frequncia de clock com que seu microprocessador

ser capaz de operar (despreze os tempos de

transio de borda). Justifique sua resposta

atravs de um diagrama de tempo indicando cada

intervalo da temporizao.

4) Na Fig. 1 o campo da microinstruo que controla o

acesso ao barramento B est codificado em 4 bits.

mas o campo do barramento C controlado por um

mapa de bits (cada sinal de controle

representado por um bit da microinstruo).

Explique por qu.

5) Na Fig. 1 existe uma caixa identificada como Bit de

mais alta ordem. Mostre como seria o circuito

eletrnico para a implementao dessa funo

lgica.

6) Quando o campo JMPC de uma microinstruo

habilitado. o contedo do MBR passa pela funo

OR (caixa com um crculo) junto com o campo

NEXT_ADDRESS. para formar o endereo da

prxima instruo. Existe alguma circunstncia na

qual faz sentido o campo NEXT_ADDRESS ser igual

a 0x1FF e usar JMPC?

7) Determine o cdigo em linguagem de montagem

resultante da compilao do cdigo Java abaixo.

Assuma que que o compilador utilizado otimiza o

cdigo gerado.

IADD

ISTORE i

10) Ao traduzir o comando MAL

if (Z) goto L1; else goto L2

seria possvel L1 estar, no endereo 0x40 e L2 em

0x140? Justifique sua resposta.

11) No microprograma para o MIC-1, na microinstruo

if_icmpeq3, o contedo do MDR copiado para o

registrador H e na linha seguinte o contedo de

TOS subtrado desse valor. Certamente seria

melhor ter um nico comando como

if_cmpeq3:

Por que isso no feito?

12) Quanto

tempo

demora

para

que

uma

implementao do MIC-1 rodando a 200 MHz

execute o seguinte comando Java:

i = j + k; ?

13)

14)

15)

i = j + k;

if (i==3)

i = 0;

k = 0;

else

j = j 1;

8) Considere o seguinte Comando Java:

i = j + k + 4;

encontre duas tradues diferentes desse

comando para a linguagem de montagem do IJVM.

9) Encontre o comando Java que produziu o seguinte

cdigo lJVM:

ILOAD j

ILOAD k

ISUB

BIPUSH 6

ISUB

DUP

Z = MDR TOS; rd

16)

A resposta deve ser dada em nanossegundos.

Repita o exerccio anterior considerando uma

implementao do MIC-2 que rode a 200 MHz.

Com base nesse clculo. Descubra quanto tempo

um programa que roda em 100ns no MIC-1 vai

gastar rodando no MIC-2.

Na mquina JVM completa. existem cdigos de

operao especiais de 1 byte para carregar as

variveis locais de 0 a 3 na pilha, que substituem a

instruo ILOAD. Qual modificao deve ser feita

na IJVM para aproveitar essas instrues da

melhor maneira possvel?

A instruo ISHR (deslocamento aritmtico

direita de um valor inteiro) existe na JVM mas no

na IJVM. Ela usa as duas palavras do topo da

pilha, substituindo ambas por um nico valor, o

resultado. A segunda palavra do topo da pilha o

operando a ser deslocado. Seu contedo

deslocado direita de um valor entre 0 e 31,

inclusive ambos, dependendo do valor dos 5 bits

menos significativos da palavra do topo da pilha

(os outros 27 bits da palavra do topo da pilha so

ignorados). O bit de sinal replicado para a direita

tantas vezes quantas forem especificadas pelo

parmetro da instruo de deslocamento. O cdigo

de operao para ISHR 122 (0x7A).

a. Qual a operao aritmtica equivalente ao

deslocamento direita com um parmetro igual a

2?

b. Estenda o microcdigo para incluir essa

instruo na IJVM.

A instruo ISHL (deslocamento esquerda de um

valor inteiro) existe na JVM mas no na IJVM. Ela

utiliza as duas palavras do topo da pilha,

17)

18)

19)

20)

substituindo ambas por um nico valor, o resultado.

A segunda palavra do topo da pilha o operando a

ser deslocado. Seu contedo deslocado

esquerda de um valor entre 0 e 31, inclusive

ambos, dependendo do valor dos 5 bits menos

significativos da palavra do topo da pilha (os outros

27 bits da palavra do topo da pilha so ignorados).

Zeros sero deslocados esquerda tantas vezes

quantas forem especificadas pelo parmetro da

instruo de deslocamento. O cdigo de operao

para ISHL 120 (0x78).

a. Qual a operao aritmtica equivalente ao

deslocamento esquerda com parmetro 2?

b. Estenda o microcdigo para incluir essa

instruo na lJVM.

A instruo INVOKEVIRTUAL da JVM precisa

saber o nmero de parmetros de que ela dispe.

Por qu?

Escreva o microcdigo do MIC-1 para implementar

a instruo POPTWO. Essa instruo remove duas

palavras do topo da pilha.

Implemente a instruo JVM DLOAD no MIC-2.

Essa instruo tem um ndice de 1 byte e coloca

na pilha a varivel local nessa posio da pilha.

Em seguida ela coloca na pilha a prxima palavra

de mais alta ordem.

A capacidade mxima do registrador de

deslocamento da Fig. 3 de 6 bytes. Seria

possvel construir uma verso mais barata da IFU

usando um registrador de deslocamento de 5

bytes? E um registrador de 4 bytes?

23)

24)

25)

26)

27)

28)

Fig. 3: Unidade de busca de instruo (IFU)

21) Tendo examinado IFUs mais baratas no exerccio

anterior, vamos agora examinar unidades mais

caras. H vantagem em se utilizar nessa unidade

um registrador de deslocamento de 12 bytes? Por

que sim, ou por que no?

22) No microprograma para o MIC-2. o cdigo para

if_cmpeq6 desvia para T se Z for igual a 1. No

entanto, o cdigo em T o mesmo que em goto1.

Seria possvel ir diretamente para goto1? Isso

melhora a velocidade da mquina?

No MIC-4. a unidade de decodificao mapeia o

cdigo de operao da instruo IJVM no ndice de

um

ROM

onde

as

micro-operaes

correspondentes esto armazenadas. Poderia

parecer mais simples omitir o estgio de

decodificao e entregar o cdigo de operao

IJVM direto na fila. O cdigo de operao da

instruo IJVM poderia ser usado como um ndice

para a ROM, da mesma maneira que no MIC-1. O

que h de errado com esse esquema?

Um computador tem uma cache em dois nveis.

Suponha que 80% das referncias memria

sejam satisfeitas pela cache de nvel 1, 15% o

sejam pela cache de nvel 2 e 5% produzam uma

falta. Os tempos de acesso so 5ns, 15ns e 60ns,

respectivamente, e os tempos de acesso cache

de nvel 2 e memria comeam a contar no

momento em que fica determinada a necessidade

de acesso a cada uma delas (por exemplo, um

acesso cache de nvel 2 no comea at que

ocorra a falta na cache de nvel 1). Qual o tempo

mdio de acesso a esse sistema de memria?

Dentre as tcnicas de atualizao de caches

parcialmente associativas, a tcnica write

allocation s melhor que as outras se ocorrerem

muitos acessos mesma linha da cache. O que

acontece no caso de uma escrita seguida de

muitas leituras?

Um processador com um pipeline de cinco

estgios trata os desvios condicionais parando

pelos trs ciclos seguintes depois de encontrar

uma dessas instrues. Quanto essas paradas

afetam a performance, se 20% de todas as

instrues so desvios condicionais? Despreze

todas as demais causas de parada.

Normalmente as dependncias causam problemas

aos processadores pipeline. Existe algum tipo de

otimizao que possa ser feita nas dependncias

WAW que resulte em algum benefcio?

A temporizao de cada ciclo de execuo do MIC1 representada na figura abaixo.

w

Sete intervalos so especialmente notveis: 1Intervalo de descida do clock; 2-Subciclo w; 3Subciclo x; 4-Subciclo y; 5-Subciclo z; 6Intervalo de subida do clock e; 7-Intervalo de alto

do clock. Descreva passo a passo, o que ocorre

em cada um desses intervalos durante a execuo

da microinstruo MAL

PC = OPC + 1; fetch; goto(MBR)

citando os registradores afetados e seu contedo,

o valor contido nos barramentos e o valor de cada

um dos bits do MIR no momento em que ele

carregado com a microinstruo. Admita que esta

microinstruo est armazenada no endereo

hexadecimal 0x025 da memria de controle.

29) Descreva o processo de inicializao do MIC-1,

ciclo a ciclo, admitindo que aps o reset todos os

registradores so zerados. Proponha uma maneira

de evitar que a instruo NOP seja executada duas

vezes antes de iniciar a execuo do programa

principal.

30) O que difere o papel realizado pelo compilador

Java do papel realizado pelo montador IJVM? Qual

dos dois mais complexo?

31) Determine para cada linha o cdigo IJVM abaixo o

estado da pilha (variveis locais + operandos) e o

valor dos registradores LV, SP e TOS. Admita que a

pilha de variveis locais tenha incio no endereo

0xAF00, sendo suas 2 primeiras posies

ocupadas pelas cpias dos valores anteriores de

LV e SP, e que as posies seguintes sejam

ocupadas pelas variveis

i, j

e k,

respectivamente:

L1:

L2:

L3:

L4:

L5:

L6:

L7:

L8:

ILOAD j

ILOAD k

ISUB

BIPUSH 6

ISUB

DUP

IADD

ISTORE i

You might also like

- Linguagem de ProgramaçãoDocument217 pagesLinguagem de ProgramaçãoMarcia Latorre MatsumotoNo ratings yet

- Algoritmos e Logica de ProgramacaoDocument111 pagesAlgoritmos e Logica de ProgramacaoAlberto Luiz Maciel Uchôa100% (1)

- Apostila Treinamentotreinamento CNC FanucDocument22 pagesApostila Treinamentotreinamento CNC FanucGeraldo Maurício73% (11)

- Funções da UCP e componentes de uma CPUDocument4 pagesFunções da UCP e componentes de uma CPUNatalFonseca0% (2)

- Simulado MicroprocessadoresDocument3 pagesSimulado MicroprocessadoresandkavalheiroNo ratings yet

- Assembly para PCDocument25 pagesAssembly para PCcpcarreiroNo ratings yet

- Manual ANAREDE V09 PDFDocument326 pagesManual ANAREDE V09 PDFMarcelo Lima100% (1)

- Programação Assembly PICDocument7 pagesProgramação Assembly PICrcimplastNo ratings yet

- Unisul Programacao Orientada A ObjetosDocument306 pagesUnisul Programacao Orientada A ObjetosgleicianonunesNo ratings yet

- Respostas Exercicios Redes p2Document7 pagesRespostas Exercicios Redes p2Alessandra Barata0% (1)

- UNIP Compiladores e ComputabilidadeDocument6 pagesUNIP Compiladores e ComputabilidadeLudmila Silva Ueira100% (1)

- Lista de exercícios introdutória sobre história e conceitos básicos de informáticaDocument7 pagesLista de exercícios introdutória sobre história e conceitos básicos de informáticaDulcicleia LiraNo ratings yet

- Apostila de PLC AC500 Módulo IDocument38 pagesApostila de PLC AC500 Módulo IdepimentaNo ratings yet

- Sistema Memória PaginadaDocument8 pagesSistema Memória PaginadaautomacaosemneuroseNo ratings yet

- Cobol MainframeBrasilDocument52 pagesCobol MainframeBrasilDavid Ribeiro de SouzaNo ratings yet

- Lista 2Document5 pagesLista 2FrânsciVieiraNo ratings yet

- Explicando Suas EscolhasDocument2 pagesExplicando Suas EscolhasLeandro da Cruz Farias MatosNo ratings yet

- 2 ExercíciosACIIIDocument5 pages2 ExercíciosACIIIMarlon Bento AzevedoNo ratings yet

- Exercícios de Arquitetura de ComputadoresDocument5 pagesExercícios de Arquitetura de ComputadoresDuarlem RobertoNo ratings yet

- Microcontroladores e Microprocessadores: Lista de Exercícios sobre 8051Document8 pagesMicrocontroladores e Microprocessadores: Lista de Exercícios sobre 8051slytheriNo ratings yet

- Arquitetura de computadores - QuestõesDocument13 pagesArquitetura de computadores - QuestõesSergio de Oliveira0% (2)

- Atividade 3 - Microprocessadores e Microcontroladores - 51-2024Document5 pagesAtividade 3 - Microprocessadores e Microcontroladores - 51-2024admcavaliniassessoriaNo ratings yet

- Lista1 de Exercícios - TeoriaDocument3 pagesLista1 de Exercícios - Teoriaalllandasilvasilva118No ratings yet

- AP1 - 2013-2 - Gabarito - Organização de ComputadoresDocument4 pagesAP1 - 2013-2 - Gabarito - Organização de ComputadoresJoeme AlvesNo ratings yet

- SD Lista1 Vinicius OliveiraDocument6 pagesSD Lista1 Vinicius OliveiraVinícius CésarNo ratings yet

- Capítulo 06Document6 pagesCapítulo 06Samuel LeonhardtNo ratings yet

- Lista de Exercícios ADocument4 pagesLista de Exercícios AbrunoNo ratings yet

- Sistemas MicroprocessadosDocument14 pagesSistemas MicroprocessadosGuilherme FernandesNo ratings yet

- Lista de Exercícios de Arquitetura - Modos de Endereçamento e Chamadas ao SODocument10 pagesLista de Exercícios de Arquitetura - Modos de Endereçamento e Chamadas ao SOGracyeli GuarientiNo ratings yet

- Unidade de controle e organização de sistemasDocument4 pagesUnidade de controle e organização de sistemasdaniel alvesNo ratings yet

- AOC - Lista de Exercícios 1b - RESPOSTASDocument4 pagesAOC - Lista de Exercícios 1b - RESPOSTASJonatas OliveiraNo ratings yet

- Lista01Document10 pagesLista01João SilvaNo ratings yet

- 2 Lista Pipeline RespostaDocument4 pages2 Lista Pipeline RespostaRairon FernandesNo ratings yet

- Arquitetura Computadores QuestionárioDocument5 pagesArquitetura Computadores QuestionárioMarcus RamosNo ratings yet

- Atividade 2 - Microprocessadores e Microcontroladores - 51-2024Document6 pagesAtividade 2 - Microprocessadores e Microcontroladores - 51-2024admcavaliniassessoriaNo ratings yet

- Apostila - Microcontrolador PIC16F84 PDFDocument116 pagesApostila - Microcontrolador PIC16F84 PDFDaniel HenriqueNo ratings yet

- Microcontroladores PIC18FDocument3 pagesMicrocontroladores PIC18FGielly Campos100% (1)

- Teste FormativoDocument10 pagesTeste Formativovaldimiro.gaspar16No ratings yet

- LT1 SO 1 2019 Versao Preliminar 100219Document33 pagesLT1 SO 1 2019 Versao Preliminar 100219Davi JorgeNo ratings yet

- Assembly 0001Document9 pagesAssembly 0001Pablo PinheiroNo ratings yet

- Arquitetura Computadores Lista ExercíciosDocument1 pageArquitetura Computadores Lista ExercíciosThiagoRodriguesAlvesNo ratings yet

- Ap1 - QuestionárioDocument5 pagesAp1 - QuestionárioThiago Francisco Paes AlvesNo ratings yet

- Exercícios AOC II Parte 1Document5 pagesExercícios AOC II Parte 1msancorNo ratings yet

- So Lista2Document7 pagesSo Lista2schulz10No ratings yet

- Arquitetura de Computadores - Questões sobre representação numérica, formatos de ponto fixo e flutuanteDocument3 pagesArquitetura de Computadores - Questões sobre representação numérica, formatos de ponto fixo e flutuanteLucas ViveirosNo ratings yet

- GABARITO ARQ COMP As 2018 2 Questionário 9 Sobre TEMA 9 Videos 24-25-26 Processadores Parte 1Document7 pagesGABARITO ARQ COMP As 2018 2 Questionário 9 Sobre TEMA 9 Videos 24-25-26 Processadores Parte 1Yoshino sempaiNo ratings yet

- ListaExercíciosIADocument4 pagesListaExercíciosIAbrunoNo ratings yet

- Introdução À Prática Laboratorial Com o z80Document13 pagesIntrodução À Prática Laboratorial Com o z80Alfredo Meurer JuniorNo ratings yet

- Arquitetura de Computadores - QuestionárioDocument5 pagesArquitetura de Computadores - QuestionárioMarcus RamosNo ratings yet

- ARQ V3 (1) GvsDocument6 pagesARQ V3 (1) GvsGabriel VicenteNo ratings yet

- Atividade Arquitetura de Computadores - João Victor - 202102104602Document7 pagesAtividade Arquitetura de Computadores - João Victor - 202102104602João Víctor da Silva Barbosa0% (2)

- Microcontrolador PIC 16F628A em WordDocument5 pagesMicrocontrolador PIC 16F628A em WordNandoNo ratings yet

- ARQUITETURA DE COMPUTADORES (UNIDADE I) (2a VEZDocument19 pagesARQUITETURA DE COMPUTADORES (UNIDADE I) (2a VEZvictor cccNo ratings yet

- LISTA 2c - OC 2023 Unip ADSDocument6 pagesLISTA 2c - OC 2023 Unip ADSMarcus Regis Novetti BarrosNo ratings yet

- Microcontrolador ATMega328Document7 pagesMicrocontrolador ATMega328Jorge Luiz A. MorgadoNo ratings yet

- Lista Exercicio Caminho Dados ControleDocument4 pagesLista Exercicio Caminho Dados ControleJonathan BorgesNo ratings yet

- Lista CavalaroDocument4 pagesLista CavalaroThierry RodriguesNo ratings yet

- Implementação da ISA Java Virtual Machine em uma microarquitetura de exemploDocument10 pagesImplementação da ISA Java Virtual Machine em uma microarquitetura de exemploJoão Paulo MoreiraNo ratings yet

- Formação Específica - TEC - Testes Adicionais - Parte I - 1 A 25Document60 pagesFormação Específica - TEC - Testes Adicionais - Parte I - 1 A 25Fabio SilveiraNo ratings yet

- Lista de Exercícios - P1 - MicrocontroladoresDocument10 pagesLista de Exercícios - P1 - Microcontroladoresnaamacorrea44No ratings yet

- Aula 4 - Modbus Slides PDFDocument20 pagesAula 4 - Modbus Slides PDFEduardo FariaNo ratings yet

- Arquitetura ComputadoresDocument1 pageArquitetura Computadorescarolina MidoryNo ratings yet

- MGL 123Document12 pagesMGL 123Thiago VelosoNo ratings yet

- MGL 123Document12 pagesMGL 123Thiago VelosoNo ratings yet

- TransitoriosDocument17 pagesTransitoriosMarcelo LimaNo ratings yet

- Oscilador Massa-MolaDocument3 pagesOscilador Massa-MolaMarcelo LimaNo ratings yet

- Lab 2 TheveninDocument1 pageLab 2 TheveninMarcelo LimaNo ratings yet

- Res AV4Document6 pagesRes AV4Marcelo LimaNo ratings yet

- Circuitos ResistivosDocument3 pagesCircuitos ResistivosMarcelo LimaNo ratings yet

- UFPI Circuitos Digitais IIDocument1 pageUFPI Circuitos Digitais IIItalo TavaresNo ratings yet

- Prática #05Document2 pagesPrática #05Marcelo LimaNo ratings yet

- 2 - 00 - LAB 2 TheveninDocument1 page2 - 00 - LAB 2 TheveninMarcelo LimaNo ratings yet

- Q 1 2Document5 pagesQ 1 2Marcelo LimaNo ratings yet

- Lau Do de VistoriaDocument5 pagesLau Do de VistoriaMarcelo LimaNo ratings yet

- Transdutores 1Document21 pagesTransdutores 1Rafael NunesNo ratings yet

- Relatório Exercício 1 - PEF5762 - ColorDocument6 pagesRelatório Exercício 1 - PEF5762 - Colormarcelo.lima_5809No ratings yet

- Estrutura Diretórios APDocument9 pagesEstrutura Diretórios APDjalma Luiz De Barros JuniorNo ratings yet

- A evolução da tecnologia desde os primórdiosDocument19 pagesA evolução da tecnologia desde os primórdiosecsk50% (2)

- Slides de Aula - Unidade IDocument43 pagesSlides de Aula - Unidade IAntonio Carlos Da SilvaNo ratings yet

- Implementando Um Primeiro Agente - Wumpus-Seção1-6Document2 pagesImplementando Um Primeiro Agente - Wumpus-Seção1-6Antônio Ely Pinho VenâncioNo ratings yet

- Avaliação 1 CompiladoresDocument5 pagesAvaliação 1 Compiladorestecnico de informaticaNo ratings yet

- OO Java WebDocument18 pagesOO Java WebNatashaSophieNo ratings yet

- GROMACS Tutorial (Portuguese BR) v.1.6Document26 pagesGROMACS Tutorial (Portuguese BR) v.1.6fernandojardim12No ratings yet

- Sistemas de Computador - A Perspectiva de Um ProgramadorDocument226 pagesSistemas de Computador - A Perspectiva de Um ProgramadorJenner Patrick Lopes BrasilNo ratings yet

- Av2 OacDocument4 pagesAv2 Oaccluiz00No ratings yet

- Projeto ArquiteturaDocument43 pagesProjeto ArquiteturaFernando PereiraNo ratings yet

- Tutorial01 - JDK Eclipse MooshakDocument15 pagesTutorial01 - JDK Eclipse MooshakLeandro CostaNo ratings yet

- Java introdução linguagem programaçãoDocument62 pagesJava introdução linguagem programaçãoZemario OliveiraNo ratings yet

- BPLs No DelphiDocument22 pagesBPLs No DelphiClradioAlmeidaNo ratings yet

- Multipic4 16f628 Assembly ApostilaDocument43 pagesMultipic4 16f628 Assembly ApostilaOirã Vinícius Moreira de OliveiraNo ratings yet

- LEX e YACCDocument9 pagesLEX e YACCGleiserpbNo ratings yet

- Introdução à BioinformáticaDocument7 pagesIntrodução à Bioinformáticafamp_carrijoNo ratings yet

- Evolução das Principais Linguagens de ProgramaçãoDocument67 pagesEvolução das Principais Linguagens de ProgramaçãoNatália GonçalvesNo ratings yet

- Quiz 01 - Algoritimo e Programação IDocument13 pagesQuiz 01 - Algoritimo e Programação IJosé Carlos Silva SantosNo ratings yet

- Apostila de Programação II - Linguagem de Programação C - FIT - Faculdade de Informática de Taquara Curso de Sistemas de InformaçãoDocument33 pagesApostila de Programação II - Linguagem de Programação C - FIT - Faculdade de Informática de Taquara Curso de Sistemas de InformaçãopriscillaraquelNo ratings yet

- Programação Básica em CDocument64 pagesProgramação Básica em CPatriciaCarlaRodriguesBarrosNo ratings yet

- Linguagem de Programação - Wikipédia, A Enciclopédia LivreDocument7 pagesLinguagem de Programação - Wikipédia, A Enciclopédia LivreDivaldoDanielNo ratings yet

- Programação para Engenharia: Aula Prática #1Document9 pagesProgramação para Engenharia: Aula Prática #1Celson Victória VenturaNo ratings yet