Professional Documents

Culture Documents

10 1016@j Vlsi 2016 11 001

Uploaded by

Technos_IncOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

10 1016@j Vlsi 2016 11 001

Uploaded by

Technos_IncCopyright:

Available Formats

INTEGRATION the VLSI journal 57 (2017) 1119

Contents lists available at ScienceDirect

INTEGRATION, the VLSI journal

journal homepage: www.elsevier.com/locate/vlsi

Hybrid TFET-MOSFET circuit: A solution to design soft-error resilient

ultra-low power digital circuit

crossmark

Maede Hemmata, Mehdi Kamala, Ali Afzali-Kushaa, , Massoud Pedramb

a

b

School of Electrical and Computer Engineering, University of Tehran, Iran

Department of Electrical Engineering, University of Southern California, USA

A R T I C L E I N F O

A BS T RAC T

Keywords:

Tunnel FET

Reliability issues

Low power design

Hybrid TFET-MOSFET designs

Soft error

In this work, to increase the reliability of low power digital circuits in the presence of soft errors, the use of both

III-V TFET- and III-V MOSFET-based gates is proposed. The hybridization exploits the facts that the transient

currents generated by particle hits in TFET devices are smaller compared to those of the MOSFET-based devices

while MOSFET-based gates are superior in terms of electrical masking of soft errors. In this approach, the

circuit is basically implemented using InAs TFET devices to reduce the power and energy consumption while

gates that can propagate generated soft errors are implemented using InAs MOSFET devices. The decision

about replacing a subset of TFET-based gates by their corresponding MOSFET-based gates is made through a

heuristic algorithm. Furthermore, by exploiting advantages of TFETs and MOSFETs, a hybrid TFET-MOSFET

soft-error resilient and low power master-slave ip-op is introduced. To assess the ecacy of the proposed

approach, the proposed hybridization algorithm is applied to some sequential circuits of ISCAS89 benchmark

package. Simulation results show that the soft error rate of the TFET-MOSFET-based circuits due to particle

hits are up to 90% smaller than that of the purely TFET-based circuits. Furthermore, energy and leakage power

consumptions of the proposed hybrid circuits are up to 79% and 70%, respectively, smaller than those of the

MOSFET-only designs.

1. Introduction

Todays, almost all of digital circuits are based on the MOSFET

transistors. However, owing to the increase in the usage of portable

devices, the power consumption of digital circuits has become a main

design constrain. As the feature sizes of transistors scales down, draininduced barrier lowering becomes more dominant. This causes an

exponential increase in leakage current between the source and drain

when the gate voltage is zero, enlarging the static power consumption

even. Also, the scaling should be accompanied with the reduction in the

threshold voltage due to the supply voltage lowering required for

smaller sizes. The reduction is translated to higher leakage current.

This originates from the fundamental limitation of 60 mV per decade

for the minimum subthreshold swing in the case of conventional

MOSFETs [1]. Finally, the increase in the surface scattering in the

channel is another negative consequence of the scaling of conventional

MOSFETs. Since the increase is due to the vertical electric eld

enlargement which lowers the surface mobility (and ON-current) which

is eld dependent. All of these, limit the application of highly scaled

conventional MOS transistors in low-power applications.

Tunnel Field Eect Transistors (TFETs), known as steep switching

devices, are considered as proper replacements for conventional bulk

MOSFETs in low power applications [1]. TFETs are P-i-N gated diodes,

operating under reverse bias condition, with a gate over the intrinsic

region. They are good candidates to operate at very low supply voltages

(VDD < 0.3 V) with ultra-low leakage power. The current generation

mechanism in TFETs is band to band tunneling of carriers across a

reversed-biased PN junction [1]. Nowadays, III-V TFETs with small

and direct band gap produce acceptable on-current [2]. Therefore,

unlike MOSFET transistors which fail to produce a large enough on- to

o-current at very low supply voltage levels, TFET transistors perform

very well at these voltage regimes. The performance and power

consumption of TFET-based circuits have been investigated in several

works [1,3,4]. For instance, in [3], TFET-based ip-op designs were

studied, and dynamic power, static power, hold-up times, and setup

times for dierent topologies of ip-ops were reported and compared

to those of the MOSFETs. The study showed that low voltage ip-ops

provided signicant advantages in power and energy consumptions as

well as performance compared to those of higher voltage MOSFET

designs.

Corresponding author.

E-mail addresses: m.hemmat@ut.ac.ir (M. Hemmat), mehdikamal@ut.ac.ir (M. Kamal), afzali@ut.ac.ir (A. Afzali-Kusha), pedram@usc.edu (M. Pedram).

http://dx.doi.org/10.1016/j.vlsi.2016.11.001

Received 6 June 2016; Received in revised form 25 September 2016; Accepted 3 November 2016

Available online 10 November 2016

0167-9260/ 2016 Elsevier B.V. All rights reserved.

INTEGRATION the VLSI journal 57 (2017) 1119

M. Hemmat et al.

To safely take advantage of TFETs, their reliability issues should

also be considered and investigated. Radiation tolerance is one of the

important characteristics in designing reliable circuits [5]. As the

feature size of transistors scale down in the deep sub-nano ranges,

circuits are becoming increasingly more susceptible to radiationinduced single-event upsets (SEU). Precisely, alpha-particle and neutron hits lead to injection or removal of charge from capacitive nodes in

the circuit, thereby giving rise to generation of soft errors in the

circuits. Furthermore, due to technology scaling, satisfying soft error

requirements is becoming increasingly challenging for high performance nanometer circuit applications [6]. Technology scaling roughly

leads to decrease in supply voltage and node capacitance in every

generation.[6]. These reductions lead to an 8% increase in soft error

rate (SER) per logic state bit for each technology generation [7]. One

more point is that low band gap materials, such as III-V materials,

generally have low ionization energy which makes them more sensitive

to neutron radiation and consequently generation of soft errors,

compared to silicon [7].

Although protecting CMOS circuits from soft errors has been

studied in many works (see, e.g., [5,6]), there are a couple of reports

on the behavior of the TFET-based circuits in the presence of the soft

errors (i.e., generation and propagation of soft faults). The mechanism

of soft error generation in TFETs has been investigated in [9] where

results showed that TFETs exhibit a dierent behavior compared to

MOSFETs in terms of the generation of soft errors caused by particles

hit. Furthermore, the SRAM SER has been calculated for TFETs and

FinFETs in [7]. Results showed 5 times reduction in the SER of TFETbased circuits compared to that of FinFET-based one.

In this work, rst, by selecting a III-V TFET device model, the

operation of the TFET device when a particle hits it, is investigated, and

the prole of the generated transient current due to the hit is extracted.

This process is also performed for the III-V MOSFET device to compare

the behaviors for these two device types. Next, an approach for

designing soft-error resilient (low SER) ultra-low power hybrid

TFET-MOSFET circuits is introduced and a heuristic algorithm for

the hybridization of TFET- and MOSFET-based gates in the circuit is

suggested. In addition, in this work, by simultaneously exploiting

advantages of TFETs and MOSFETs, a hybrid master-slave soft

error-resilient low power ip-op is presented. The proposed ip-op

is utilized in the hybrid circuits to increase reliability in the presence of

soft-errors.

It should be noted that the overall fabrication processes for TFETs

are compatible with the MOSFET process [10,11]. Hence, it is possible

to have hybrid circuits as stated in [1113]. However, the fabrication of

TFET is more costly and complicated [12]. Also, the proposed

hybridization approach is ecient for the range of supply voltages

(i.e., low supply voltage levels) where the performances of both TFET

and MOSFET devices are almost similar.

The rest of paper is organized as follows. Section II describes the

device model of the TFET considered in this work and compares its

operation with a similar MOSFET device. Section III investigates the

generation and propagation of soft errors in TFET- and MOSFETbased circuits and introduces the idea of hybrid TFET-MOSFET circuit

designs. In Section IV a hybrid TFET-MOSFET master-slave ip-op is

proposed. The proposed heuristic hybridization algorithm is provided

in Section V while its ecacy is discussed in Section VI. Finally the

paper is concluded in Section VII.

Table 1

Nominal physical parameters of TFET device considered in this work.

Parameter

Nominal value

Relative Gate Dielectric Permittivity

Body Thickness

Gate Oxide Thickness

Source Doping

Drain Doping

Gate Work Function

Channel length

Channel width

21

5 nm

2.5 nm

41019/cm3

41017/cm3

4.8 eV

22 nm

22 nm

a)

HfO2 Oxide

N+

Drain

Intrinsic

channel

P++

Source

HfO2 Oxide

b)

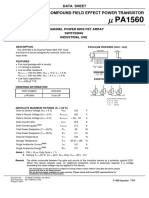

Fig. 1. a) TFET structure and b) Energy band diagram of TFET.

characteristics of an ultra-thin 22 nm double-gate InAs Homojunction

TFET is also obtained using TCAD simulation [3]. Nominal parameters

of the device model are adopted from [14] and are summarized in

Table 1. The structure and band diagram of the device are shown in

Fig. 1. All simulations for this section have been performed at device

level, using Silvaco ATLAS. The activated physical models were nonlocal band to band tunneling, band gap narrowing, Shockley-Read-Hall

model, and mobility model. The output characteristic of the

Homojunction TFET (Id-Vds) is depicted in Fig. 2. It should be noted

2. Comparison of TFET and MOSFET

2.1. TFET and MOSFET device model

Since compact models have not been fully developed for TFETs yet

[3], the circuit simulation is performed by utilizing Verilog-A look-up

tables. Hence, transfer characteristics of the TFET are obtained

through device simulations across a range of voltages. In this work,

Fig. 2. Output characteristics of InAs TFET device for Vgs =0.3 V, 0.4 V, and 0.5 V.

12

INTEGRATION the VLSI journal 57 (2017) 1119

M. Hemmat et al.

Fig. 3. a) Verilog-A small signal model. b) Transient response of TFET 2-input AND

gate.

that, unlike MOSFETs, TFETs are uni-directional devices because of

the structural asymmetry between the source and the drain [3]. The oncurrent of 123A at Vds = Vgs =0.5 V, leakage current of 32pA, and

Ion/Io =3.8106 are obtained for the TFET device.

After obtaining device characteristics of the Homojunction TFET,

these characteristics can be used in circuit-level simulations using a

Verilog-A table. The,Ids (Vgs, Vds ), Cgd (Vgs, Vds ) and Cgs (Vgs, Vds ), characteristics are captured in a two-dimensional look-up table. The Verilog-A

small signal model that uses the look-up table for circuit simulations is

shown in Fig. 3(a). As an example, the transient output characteristics

of InAs TFET 2-input AND gate obtained by exploiting the model is

shown in Fig. 3(b), which is used as an example to demonstrate the

validity of the look-up table based model. Voltage spikes of the 2-input

AND gate output are related to enhanced on-state Miller capacitance.

The structure of the InAs MOSFET used in this work is based on an

ultra-thin 22 nm double gate. To perform an acceptable comparison

and hybridization, the nominal physical parameters of the MOSFET are

similar to those of the TFET. It, however, should be noted that, for

MOSFETs, a high drain doping as high as source doping is

necessary. The high doping level of the drain (and source) is required

for reducing the short channel eects such as drain induced barrier

lowering (DIBL). This helps controlling the subthreshold leakage

current. In addition, it reduce the drain parasitic resistance while

increasing the parasitic capacitance. The high drain doping level also

may increase hot carrier eect at the drain side of the channel.

Fig. 4. Comparison of the drain- source current (leakage current at low gate-source

voltage and on-current at high gate-source voltage) for a) VDD =0.3 V, b) VDD =0.7 V.

2.2. Comparision of TFET and MOSFET operations

In this subsection, the results of a comparative study of the leakage

current, drive current, and dynamic power consumption of both III-V

MOSFET and TFET devices are reported. As mentioned before, for low

power designs, TFETs are a promising alternative to the MOSFETs

because of possibility of achieving sub-60 mv/decade sub-threshold

slope. This leads to less leakage power consumption. Fig. 4 compares

the leakage current and on-current of TFETs and MOSFETs in low and

high supply voltages. As Fig. 4(a) shows, TFETs are able to achieve

lower leakage current and higher on-current at very low voltages. On

the other hand, as Fig. 4(b) shows, in spite of low leakage current of

TFET at relatively high supply voltages, the MOSFET device has a

higher on-current, and hence, better performance at this supply

voltage.

Fig. 5. Comparison of capacitance behavior of TFET and MOSFET devices under

dierent supply voltages.

A comparison between TFET and MOSFET capacitances is depicted

in Fig. 5 which reveals the gate capacitance of TFET is smaller than that

of the MOSFET. Also, it shows that by increasing the gate voltage, the

dierence between the two increases. Hence, in III-V TFETs, the

overall gate capacitance which includes gate-source capacitance and

gate-drain capacitance (Cgg) is lower than that of III-V MOSFETs due

13

INTEGRATION the VLSI journal 57 (2017) 1119

M. Hemmat et al.

to lighter drain doping of TFETs [3]. It should be noted that the smaller

capacitance of the TFET leads to smaller dynamic power consumptions

for TFET-based circuits. Finally, note that in MOSFETs, the dominant

capacitance is gate-source capacitance (Cgs) while in TFETs, the drain

capacitance (Cgd) is the dominant one [3]. Therefore, the enhanced onstate Miller capacitance may lead to induce a voltage spike during

switching in the TFET-based circuits and impact the total dynamic

power consumption.

Based on the above discussion about the on-current and the

capacitance of TFETs and MOSFETs, the voltage range in which the

overall performance of TFET and MOSFET is close to each other, is

about 0.45 V < VDD < 0.55 V.

Fig. 6. Band diagrams of TFET and MOSFET devices before and after ion strike [9].

3. TFET and MOSFET soft error characteristics

generated holes, however, can be collected at the source side at the

same time, instead of being stored in the body. This charge collection

leads to a signicant hole storage reduction in TFETs. It consequently

leads to a considerable reduction in the bipolar gain eect and

generated transient current. Fig. 6 shows the band diagrams of

TFETs and MOSFETs before and after the particle hit. The energy

band diagrams of the transistors, reveal the hole storage induced

source barrier lowering eect [9].

Considering the impact of the bipolar gain eect on the generation

of the transient current, we adopt the TCAD heavy ion model to

simulate the generated carriers after the ion strike. Transient current

proles for InAs MOSFET and InAs TFET devices are plotted in Fig. 7

assuming a particle hit inducing a charge density of 50 fC/m [9]

strikes.

As the gure demonstrates, the duration and amplitude of the

transient current of the TFET are about 80% and 70% smaller than

those of the MOSFET. It shows that TFET devices are more immune to

the soft error generation. Here, as an example, Fig. 8 shows the output

voltage spike of a MOSFET- and TFET-based FO4 inverter when a

particle with a charge density of 50 fC/m strikes to the input of the

inverter. The output voltage spike of the MOSFET-based inverter is up

to 310 mV while the voltage change for TFET-based inverter is about

140 mv. Therefore, the generated voltage spikes in the case of the

particles hit in TFET-based gates are smaller compared to those of the

MOSFET-based gates. Note that, both duration and amplitude of

propagated error pulse through TFET-based gate is increased due to

weak drive ability of TFET-based gates.

The radiation induced single-event upset (SEU), also known as soft

error, has become a key challenge as the transistor packing density is

increasing with physical scaling, which in turn leads to more internal

nodes in the circuits given the same die area (of course this also means

that more functions are integrated on the same chip). Use of low bandgap materials, scaling down of the supply voltages, and reduction of

capacitances of internal nodes make the design of soft-error resilient

circuits ever more challenging [9]. Energetic particles, such as cosmic

ray neutrons and alpha particles, are sources of soft errors [1517].

These particles strike sensitive nodes and travel through the bulk of the

transistor. The creation of minority carriers during the travel of the

particles and the collection of them by the source/drain diusion, may

change the voltage value of the victim node. More specically, soft error

occurs when the collected charge at a specic node is greater than a

critical charge (i.e., Qcritical), of the node. The critical charge is the

minimum charge, needed to be deposited at a sensitive node, to change

the value of the node. This charge is widely used as a metric for

measuring the SER and is proportional to the node capacitance and

supply voltage [18]. The particle hit and the change in the value of the

node may be modeled by a transient current pulse as proposed in [8].

In the following subsections, rst, the transient current generation

due to particles hit in III-V TFETs and III-V MOSFETs are investigated

and compared using TCAD device simulations. Next, electrical masking

in TFET- and MOSFET-based gates (circuits) will be discussed. Finally,

the idea of hybridization is proposed.

3.1. Transient current generation

3.2. Soft error propagation

In this part, to analyze the behavior of the transistor after the ion

strike, we perform the radiation-induced transient current evaluation.

As mentioned before, the considered TFET and MOSFET device

models are based on the ultra-thin 22 nm double-gate InAs. Also, the

heavy ion model [9] is utilized to simulate the electron hole pairs

generation along the ion track and perform radiation-induced transient

current analysis. The generated charges due to the particle hit, result in

a transient current when the device is in the o-state (i.e., Vgd = VDD,

Vgs =0).

First, it should be mentioned that the characteristic of the generated

transient current and the amount of charge collection in fully depleted

channel devices such as MOSFETs, FinFETs, and TFETs are signicantly inuenced by the bipolar gain eect [9]. In n-channel MOSFETs,

generated electrons are collected at the drain node because of the

source-drain bias. On the other hand, due to the source-channel

barrier, generated holes are stored in the body. The hole storage

increases the channel potential and subsequently reduces the source

barrier. The reduction of the barrier leads to the ow of additional

electrons into the channel and an increase in the transient current. This

phenomena is known as the bipolar gain eect.

In TFETs, the hole storage is dierent from that of MOSFETs due to

the asymmetric source and drain doping. The collection of induced

electrons at the drain node is similar to the case of MOSFETs. The

The generated transient current due to the particle strike induces a

Fig. 7. Generated transient current prole for InAs TFET and InAs MOSFET devices.

14

INTEGRATION the VLSI journal 57 (2017) 1119

M. Hemmat et al.

Based on discussions in this section, TFETs exhibit a better

characteristic in terms of the generation of the transient current due

to the particle hit. In contrast MOSFETs exhibit a better characteristic

in terms of the electrical masking of the transient current due to the

particle hit.

3.3. Soft error generation and propagation in Hybrid TFET-MOSFET

circuit

To take advantages of both TFETs and MOSFETs, some hybrid

designs have been proposed. For example, in [11], a mixed TFETMOSFET 8 T SRAM is proposed to provide signicant improvements in

the SRAM performance and the minimum operation voltage.

Furthermore, in [12], a hybrid TFET-CMOS based power gating

technique is proposed to reduce the sleep mode leakage current.

Considering characteristics of TFETs and MOSFETs, implementing

the circuit using both TFET and MOSFET gates may lead to a more

soft-error resilient design compared to pure TFET or pure MOSFETbased design. It originates from the fact that TFET-based gates are

superior to MOSFET-based ones in terms of the error generation, while

the latter mask the error more eciently. Hence, to have a soft-error

resilient design, one should have the TFET-based gates in the generation path of the transient (error) current and the MOSFET-based ones

in the propagation path of the transient (error) voltage. Here, as a

motivational example, we hybridized the inverter chain which was

studied in the previous subsection using two dierent approaches. It

should be stressed that although for this simple example, it is assumed

that a (particle hit) soft fault SEU occurs at the input of the inverter, for

all other circuits considered in the rest of this paper, there is not such a

assumption. In the former approach, the rst and last inverter gates

have been implemented by TFET devices while the second gate has

been implemented by MOSFET devices. In the latter one, the rst

inverter gate is based on TFETs while the other gates are MOSFETbased ones. The output voltage spike due to the particle hit in the input

of the chains are depicted in Fig. 10. As the results show the amplitude

of the output voltage in the second case (Fig. 10(b)) is smaller. Also,

comparing the chains of Fig. 9(b) and Fig. 10(b) suggest that

hybridizing is an eective solution for decreasing the amplitude of

the voltage spike.

Fig. 8. Output voltage spikes of MOSFET- and TFET-based FO4 inverters.

voltage pulse, known as a glitch, which may propagate through logic

paths in the circuit. The voltage pulse may be electrically masked due to

the delay of logic gates. Hence, in this case an error happens when the

generated voltage pulse either is latched by a ip op or reaches a

primary output node of the circuit. Therefore, to conduct a complete

investigation of the soft error rates in TFET- and MOSFET-based

circuits, the propagation of glitches (due to the particle hits) in each

type of the circuits should be studied [6]. The propagation of the

voltage pulse strongly depends on the characteristics of propagating

gates. It is obvious that slower gates mask the voltage pulse better than

fast ones [6]. Furthermore, if the input voltage spike is not large

enough to cause the gate output to change, the error is masked [6].

Our studies show that TFETs propagate glitches more easily

compared to MOSFETs, leading to lower electrical masking for

TFETs. This observation originates from the fact that the overall

capacitance in TFETs is smaller than that of MOSFETs as was

discussed in Subsection II.B (see Fig. 5). Hence, circuit nodes in

TFET-based circuits are more sensitive to the glitch. In addition, at low

voltage levels (VDD < 0.3 V), TFETs have more on-currents compared

to those of the MOSFETs giving rise to higher error propagations.

Hence, the probability of the electrical masking in MOSFET-based

gates is higher than that of TFET-based gates. Here, as an example,

Fig. 9 shows the voltage spike at the output of two chains of three

inverter gates when a particle with a charge density of 50 fC/m hits at

the inputs of the chains. One of these chains has been implemented by

TFET-based inverter gates while the other one has been implemented

by MOSFET-based inverter gates. As the gures reveal, the amplitude

of the voltage spike at the output of the chain in the case of MOSFETbased implementation is smaller than that of the TFET-based implementation showing a better masking.

4. Hybrid TFET-MOSFET ip-op

In addition to aecting the combinational logic, the soft error also

aects memory and sequential elements. To detect and correct any soft

errors in SRAMs, Error Correction Code (ECC) methods have been

proposed [19]. However, protecting latches and ip-ops from soft

errors is more complicated. To protect ip-ops from soft errors,

Fig. 9. Output voltage of chains of three a) TFET-based and b) MOSFET-based inverters after particles hit in the input of chains.

15

INTEGRATION the VLSI journal 57 (2017) 1119

M. Hemmat et al.

Fig. 10. Output voltage of a hybrid inverter in a) TFET-MOSFET-TFET implementation, b) TFET-MOSFET-MOSFET implementation after particles hit in the input of the chains.

this case, if a particle hit happens in the input node of the ip-op, the

generated transient current is smaller and shorter. Furthermore, the

error can be masked more easily by the MOSFET-based inverter (I1).

Conclusively, in the proposed hybrid TFET-MOSFET master slave ipop, the inverters I1, I2, I3, I4 are MOSFET-based gates while the

other gates are implemented by TFET devices.

several redundant ip-op structures have been proposed. TMR (Triple

Modular Redundancy) [20], DICE (Dual Interlocked storage cell) [21],

BISER (Built-in Soft Error resilient) [22], and RHBD-MSFF (Radiation

Hardening By Design Master-Slave Flip-op) [22] are several examples

of the proposed ip-ops. In this section, we propose a low power softerror resilient hybrid TFET-MOSFET master-slave ip- op.

First, note that the capacitance of the internal nodes is an important

factor in the soft error rate of designs. It is obvious that the node with

smaller capacitance is more susceptible to soft errors, and hence,

should be protected. Given this fact, one should determine this node in

the master-slave ip-op. Then, a TFET-based gate should be used

after the selected node in order to generate a smaller and shorter

transient current. Finally, it is benecial to use MOSFET-based gates in

the propagation path of the error to increase the probability of error

masking. In this work, we focus on the master-slave ip-op whose

internal structure is depicted in Fig. 11. Due to the symmetric circuits

of both master and slave, the capacitance measurement was performed

only for the master circuit.

To measure the capacitance of a node, one may use an appropriate

current pulse at the node and measure the time in which the output

voltage of the node changes a particular amount. Using the measured

time and voltage changes (and, respectively), the capacitance of the

node may be calculated from

I =C

dv (t )

dt

5. Proposed heuristic hybridization algorithm

In this part, a heuristic algorithm is proposed for designing softerror resilient hybrid TFET-MOSFET circuits. The ow of the proposed

hybridization algorithm is depicted in Fig. 12. In step 1 of this

algorithm, in order to avoid degradation of the performance of the

circuits after hybridization, the operating supply voltage level which

leads to almost the same delays for both the TFET- and MOSFET-based

implementations of the input design is determined. Note that delays of

both circuits should be smaller than a predened delay (i.e., Dconst).

This process is performed by using HSPICE simulations under dierent

supply voltage levels. This process is an iterative approach which is

started by considering the parameter Vstart as the initial operating

voltage level and continues by increasing the voltage by Vstep at the

end of each iteration. In each iteration, delays of both TFET- and

MOSFET-based circuits are compared. If delays are close to each other

and smaller than Dconst, this process is terminated. Otherwise, the

process is repeated by increasing the supply voltage level. It should be

noted that the dierence of delays for MOSFET-based and TFET-based

circuits should be less than 10% of the delay of MOSFET-based circuit

to choose the corresponding voltage. It should be noted that the

motivation behind accepting a 10% performance dierence with that

of MOSFET-based circuit (considered as the reference implementation)

is to lower the eort for nding the supply voltage which could provide

the same performances for all the implementations.

Based on the reported on-current in Section II, in this work, we

consider 0.4 V as the Vstart, and our study shows that the selected

supply voltage level for this process turns out to be smaller than 0.55 V.

It should be noted that if a small Dconst is considered, this process may

not reach an operating supply voltage level, and hence, in this case,

Dconst should be increased. It should be noted that since lowering the

power consumption of the circuit is desired, we start from a lower

supply voltage.

For performing the hybridization, in the second step of algorithm,

we propose to start from TFET-based implementation of the design

while all the ip-ops are implemented by the proposed hybrid ones.

Hence, after determining the supply voltage level, the capacitances of

the internal nodes are extracted and a collection of sensitive internal

nodes are chosen (i.e., SSIN). The sensitive nodes are nodes with small

capacitances. For these nodes, the probability of generating the voltage

(1)

The measurement of the capacitance for the internal nodes of the

master-slave ip-op show that node 3 has the smallest capacitance

and hence is the most sensitive node to the particle hits. Therefore, in

order to achieve a soft-error resilient ip-op, we propose to exploit a

TFET-based transmission gate between nodes 3 and 1 (i.e., the

transmission gate T2). Also, to mask the generated error, the inverters

I1 and I2 are implemented by MOSFET devices. Also, we suggest to

implement the transmission gate T1 by employing TFET devices. In

Fig. 11. The internal structure of master-slave ip-op.

16

INTEGRATION the VLSI journal 57 (2017) 1119

M. Hemmat et al.

1

5

2

Fig. 12. Flowchart of the proposed hybridization algorithm.

of these paths are extracted. Now, if the capacitance of a node which

belongs to the sensitive list increases to a value higher than the

considered threshold, this node is removed from the sensitive nodes

list. Also, because it is possible that a gate is shared among some paths,

if in the hybridization process of a path, this gate is considered to be

implemented by MOSFETs, we consider this gate to be also MOSFETbased gate for the other paths.

As mentioned before, in step 5, for each hybrid path, its immunity

to the soft error is determined by extracting the soft error rate. The

extraction is performed by injecting some errors (voltage pulses) in the

chosen sensitive internal node and propagate it through the gates of the

path. This process is performed by using HSPICE simulation. It is clear

that an error will happen if the error voltage is latched by a ip-op in

the path or reaches to the output of the circuit.

spike due to the particles hit is high. Hence in this work, we consider a

node as the sensitive node when its capacitance is less than or equal to

1.2 times of the smallest internal node capacitance of the circuit.

In step 3, to decrease the soft error rate of the circuit, the sensitive

internal nodes are chosen one by one. Then, in step 4, for each chosen

sensitive node, all paths which are started from this sensitive node are

extracted and for each of them, the hybridization process is performed

by replacing some gates by TFET- and MOSFET-based gates. For each

extracted path, the rst gate of the path is considered to be implemented by TFETs. This leads to generating smaller voltage pulse due to

the particle hit. However, the gates in the second and third levels are

considered to be implemented by MOSFETs to electrically mask the

generated voltage pulse. Our results show that one MOSFET-based

gate is not able to fully mask the generated voltage pulse, while with a

high probability, two consecutive MOSFET-based gates mask the

generated pulse.

After this phase, soft error rates of the path under three dierent

implementations have been extracted where these implementations are

TFET-based, MOSFET-based, and hybrid TFET-MOSFET. If the error

rate of the hybrid TFET-MOSFET implementation is smaller than the

other implementations, the hybridization for this path is terminated.

While, if the error rate of the hybrid TFET-MOSFET path is larger than

that of the other implementations, the rst gate after the last MOSFETbased gate is considered to be implemented by MOSFET devices. This

process is carried out till either the soft error rate of hybrid path

reaches to a value smaller than the soft error rates of the two other

implementations or there are no more gates in the path for the

replacement. When the process of the hybridization for all the

extracted paths of a sensitive node is terminated, the algorithm chooses

another sensitive node and applies the above replacement procedure to

the gates of its paths.

Note that replacing a TFET-gate by a MOSFET-gate may lead to a

capacitance increase of the internal nodes of the circuit connected to

the inputs of this gate. Hence, after nalizing the hybridization of all

the paths of a sensitive node, all the capacitances of the internal nodes

6. Results and disscussion

6.1. Simulation setup

To assess the eciency of the proposed design approach, we applied

it to some sequential circuits of ISCAS89 benchmark packages. All the

simulations were performed by utilizing the HSPICE tool. For this

purpose, rst, all of the considered circuits were synthesized to gatelevel netlists using Synopsys Design Compiler. Note that in this work,

without loss of generality, only Inverter, and 2-input NAND, NOR,

AND, OR, XOR and XNOR gates were considered as the cells of the

technology library. After extracting the gate-level netlist, the HSPICE

netlist of the circuits were generated by using an in-house tool. Also, as

mentioned before, we have used Verilog-A models of 22 nm double

gate InAs TFET and 22 nm InAs MOSFETs during the HSPICE

simulations. In addition, the proposed heuristic hybridization algorithm was implemented using Python language. Finally, each of the

studied circuits was implemented in three forms of MOSFET-based

circuit, TFET-based circuit, and Hybrid TFET-MOSFET-based circuit.

Note that, to keep the overall performance of the circuit almost

17

INTEGRATION the VLSI journal 57 (2017) 1119

M. Hemmat et al.

Table 2

The ranges of the values used for generating error injection voltage pulse.

Parameter

Range of values

Rise time

Fall time

Arrival time compared to edge of the clock

Duration

Amplitude

10100 ps

10100 ps

100 ps to +100 ps

10300 ps

Verror 0. 05Verror

Table 3

Leakage power and energy consumption of the different implantations of master-slave

flip-flop..

Leakage power

Energy consumption

TFET-based

design

CMOS-based

design

Hybrid design

0.09

0.53

1

1

0.57

0.7

Fig. 13. Soft error rates of the dierent implementations of master-slave ip-op.

Fig. 14. a) Normalized leakage power, b) normalized energy, and c) normalized soft

error rate of some benchmark circuits of ISCAS'89 benchmark package.

Table 4

The supply voltages used for different implementations of the benchmarks.

Benchmark

Vdd (V)

S27

S344

S444

S526

S713

S838

S953

S1238

0.43

0.47

0.44

0.45

0.44

0.46

0.49

0.48

Fig. 15. Comparison of soft error rates of hybrid design and TFET-based design at equal

and higher supply voltages.

constant after the hybridization, the operation voltage was determined

by the algorithm such that both TFET-based gates and MOSFET-based

gates had about the same delays.

The particle hit in each critical node was modeled by injecting

voltage pulses. The injected voltage pulses, which were totally 60, were

dierent in rise time, fall time, arrival time compared to edge of the

clock, duration, and amplitude. The ranges of these parameters utilized

in this work are given in Table 2. Note that Verror is the amplitude of

the voltage spike at the output of the gate when a particle with a charge

density of 50 fC/m hits the gate. These voltages, which are dierent

for dierent gates, have been extracted for each implementation by

simulation.

In the rest of this section, rst, discuss the performance of the

hybrid ip-op and then the results for the hybrid design circuits are

examined.

dynamic power, and soft error rate for each of the implemented ipfops were extracted. Table 3 summarizes the leakage power and energy

consumptions of the dierent implementations of the master-slave ipop. The values are normalized to the leakage power and energy

consumption of the MOSFET-based design. As the results reveal, the

leakage power and energy consumption of the hybrid approach are

about 43% and 30%, respectively, smaller than those of the MOSFETbased design. Also, the same parameters are about 6 times and 32%,

respectively, larger than those of the TFET-based design.

To extract the soft error rates of the ip-ops, rst, the input and

internal nodes of the ip-ops were exposed to the particles hit. Then,

the ability of the ip-ops to mask the errors was measured. The

particle hit in each node was modeled by injecting voltage pulses. The

injected voltage pulses were dierent in rise time, fall time, arrival time

compared to edge of the clock, and duration. For each node, we

injected, totally, 60 voltage pulses. Fig. 13 reports the SER values for

the three implementations of the master-slave ip-op. Note that, the

SER percentage used in the Y-axis of Fig. 13 is the ratio of the

amplitude of the generated error voltage pulse at the output to that of

the injected voltage pulse at the input of the circuit. As the results

demonstrate, by the hybridization technique, the soft error rate is

reduced by about 59% and 51% compared to those of the TFET-based

6.2. Hybrid ip-op

To make sure that the overall performance of the circuit is not

changed after the hybridization, the operating voltage was chosen such

that both TFET-based and MOSFET-based ip-ops had about the

same delays. The simulation indicated the operating voltage level of

0.45 V for the circuits. Based on this voltage, the leakage power,

18

INTEGRATION the VLSI journal 57 (2017) 1119

M. Hemmat et al.

investigate soft error generation and propagation due to particle hits.

Then, considering the characteristics of both TFET and MOSFET

devices, a hybrid master-slave ip-op was proposed. The proposed

ip-op showed a smaller rate of soft error, compared to both TFETand MOSFET-based ones. Furthermore, a heuristic algorithm for the

circuit hybridization using TFET and MOSFET devices with the

objective of reducing the soft error rate was proposed. The proposed

algorithm was applied to some sequential circuits of ISCAS89 benchmark packages. The results showed that the soft error rate of the hybrid

TFET-MOSFET-based circuits, on average, was about 80% lower

compared to that of the TFET-based circuits. Also, the leakage power

and energy consumptions of the hybrid circuits, on average, were about

67% and 52%, lower compared to the pure MOSFET-based ones.

and MOSFET-based implementations, respectively.

6.3. Hybrid design circuits

In this section, the ecacy of the proposed hybridization algorithm

is evaluated. As mentioned in part V, the supply voltage of benchmarks

are chosen through an iterative process to avoid degradation in

performance. The supply voltages used for dierent benchmarks in

this work are given in Table 4. As may be observed from this table, the

voltages are not very dierent, and hence, having the same supply

voltages for all of them is not expected to lead to very dierent results

for the delays and energies compared to those which we obtained for

the voltages given in Table 4. However, selecting these slightly dierent

supply voltages for dierent benchmarks leads to the same performances for the circuits regardless of their implementations. This way

we can assure performing a fair comparison in terms of the performance.

The normalized leakage power and energy consumptions as well as

the soft error rates of the three implementations of the benchmark

circuits are shown in Fig. 14. In the case of the leakage power and

energy consumptions, the values are normalized to those of the

MOSFET-based implementation while the reported SER values are

normalized to that of the TFET-based implementation. Also, for the

results presented in this gure, we have used uniform random inputs to

determine the power and energy consumption.

The results indicate that the leakage power and energy consumptions of the hybrid circuits were smaller than those of the MOSFETbased designs. Also, in the best case, the hybrid design had a leakage

power (energy) consumption of about 79% (70%) smaller than that of

the MOSFET-based design which belonged to the case of S713 (S713)

benchmark circuit. Also, on average, the hybrid approach led to the

67% and 52% smaller leakage power and energy consumptions

compared to those of the MOSFET-based design. Also, as we expected,

the leakage power and energy consumptions of the TFET-base designs

were smaller than those of the hybrid designs where the increases were,

on average, about 10% and 9%, respectively.

Finally, the proposed hybridization approach led to higher soft

error immunity. As Fig. 14(c) shows, for all the benchmark circuits, the

proposed approach resulted in lower SER values. The best case

belonged to the S27 benchmark circuit with a rate about 90% and

85% lower than those of the TFET-based and MOSFET-base circuits,

respectively. Also, the SER values of the hybrid TFET-MOSFET-based

designs, on average, was about 79% and 60% smaller than those of

TFET and MOSFET-based designs, respectively.

It is known that the SER value decreases as the supply voltage

increases, and hence, to further evaluate the eciency of the proposed

algorithm, the eect of the supply voltage increase on the SER of the

TFET-based circuits was studied. For this study, we also obtained the

SER results for the TFET-based circuit at a higher supply voltage. To

amount of increase in the supply voltage was determined based on

having the same energy consumptions for both the hybrid circuit and

TFET-based circuits (less than 20% increase in the supply voltage).

Apparently, the energy consumption of the hybrid circuit is more than

TFET-based one when the same supply voltage is utilized. The results

of this study are depicted in Fig. 15 which indicates that the superiority

of the hybrid design in masking soft errors when compared to the pure

TFET-based design with higher supply voltage.

References

[1] R. Mukundrajan, M. Cotter, V. Saripalli, M. Irwin, S. Datta, V. Narayanan, Ultra low

power circuit design using Tunnel FETs, in: Proceedings of IEEE Computer Society

Annual Symposium on VLSI (ISVLSI), 2012, pp. 153158.

[2] M. S. Kim, H. Liu, K. Swaminathan, X. Li, S. Datta, V. Narayanan, Enabling PowerEcient Designs with III-V Tunnel FETs, in: Proceedings of IEEE Compound

Semiconductor Integrated Circuit Symposium (CSICs), 2014, pp. 14.

[3] M. Cotter, H. Liu, S. Datta, V. Narayanan, Evaluation of tunnel FET-based ip-op

designs for low power, high performance applications, in: Proceedings of the 14th

international symposium on Quality electronic design (ISQED), , 2013, pp. 430

437.

[4] J.Singh, K.Ramakrishnan, S.Mookerjea, S.Datta, N.Vijaykrishnan, D.Pradhan, A

novel si-tunnel FET based SRAM design for ultra low-power 0.3 VV DD applications, in: Proceedings of Asia and South Pacic Design Automation

Conference(ASP-DAC),pp. 181186, 2010.

[5] N. Miskov-Zivanov, D. Marculescu, Modeling and optimization for soft-error

reliability of sequential circuits, IEEE Trans. Comput.-Aided Des. Integr. Circuits

Syst., 27 (2008) 803816.

[6] Y. S. Dhillon, A. U. Diril, A. Chatterjee, Soft-error tolerance analysis and

optimization of nanometer circuits, in: Proceedings of the Design, Automation, and

Test in Europe, 2008, pp. 389400.

[7] H. Liu, M. Cotter, S. Datta, V. Narayanan, Technology assessment of Si and III-V

FinFETs and III-V tunnel FETs from soft error rate perspective, in: Proceedings of

teh IEEE International Electron Devices Meeting (IEDM), 2012, pp. 25.5. 125.5.

4.

[8] S.Lin, Y.-B.Kim, F.Lombardi, Soft-error hardening designs of nanoscale CMOS

latches in: Proceedings of the 27th IEEE Symposium on VLSI Test,pp. 4146, 2009.

[9] S. Datta, H. Liu, V. Narayanan, Tunnel FET technology:a reliability perspective,

Microelectron. Reliab., 54 (2014) 861874.

[10] A. Tura, Novel Vertical Tunnel Transistors for Continued Voltage Scaling, (Ph.D.

dissertation), Univ. of California, Los Angeles, 2010.

[11] Y.-N. Chen, M.-L. Fan, V.-H. Hu, P. Su, C.-T. Chuang, Evaluation of Stability,

Performance of Ultra-Low Voltage MOSFET, TFET, and Mixed TFET-MOSFET

SRAM Cell With Write-Assist Circuits, IEEE J. Emerg. Sel. Top. Circuits Syst. 4

(2014) 389399.

[12] A. Mishra, K.K. Jha, M. Pattanaik, Parameter variation aware hybrid TFET-CMOS

based power gating technique with a temperature variation tolerant sleep mode,

Microelectron. J. 45 (2014) 15151521.

[13] V.Saripalli, A.Mishra, S.Datta, V.Narayanan, An energy-ecient heterogeneous

CMP based on hybrid TFET-CMOS cores, in: Proceedings of the 48th Design

Automation Conference(DAC)pp. 729734, 2011.

[14] H. Liu, S. Datta, III-V Tunnel FET model manual,, the Pennsylvania State

University, 2015.

[15] M.Ebrahimi, M.Tahoori, Cross-layer Approaches for Soft Error Modeling and

Mitigation, in: Proceedings of the 53rd Annual Design Automation Conference

(DAC)Article No. 32, 2016.

[16] B. Narasimham, et al., Bias Dependence of Single-Event Upsets in 16 nm FinFET

D-Flip-Flops, (Dec)IEEE Trans. Nucl. Sci. 62 (6) (2015) (Dec).

[17] Y.P. Frang, A.S. Qates, Muon-Induced Soft Errors in SRAM Circuits in the

Terrestrial Environment, IEEE Trans. Device Mater. Reliab. 15 (1) (2015)

115122.

[18] R.Ramanarayanan, V.Degalahal, N.Vijaykrishnan, M.Irwin, D.Duarte, Analysis of

soft error rate in ip-ops and scannable latches, in: Proceedings of the IEEE

International Systems On Chips( SOC) Conference,pp. 231234, 2003.

[19] A.Goel, S.Bhunia, H.Mahmoodi, K.Roy, Low-overhead design of soft-error-tolerant

scan ip-ops with enhanced-scan capability, in: Proceedings of Conference on

Design Automation. Asia and South Pacic, 6 pp. 2006.

[20] M. Nicolaidis, Design for soft error mitigation, IEEE Trans. Device Mater. Reliab.

(2005) 405418.

[21] L.Sheng, Y.Kim, F.Lombardi, Soft-error hardening designs of nanoscale CMOS

latches, in: Proceedings of the 27th Symposium on VLSI Testpp. 4146, 2009.

[22] N.Seifert, B.Gill, V.Zia, M.Zhang, V.Ambrose, On the scalability of redundancy

based SER mitigation schemes, in: Proceedings of the IEEE International

Conference on Integrated Circuit Design and Technology(ICICDT), 2007, pp. 19

7. Conclusion

In this paper, a hybrid TFET-MOSFET design approach for

decreasing the soft error rate of digital circuits was proposed. The

hybridization method was inspired by the fact that the transient

current, generated by particle hits, was shorter and smaller for

TFETs and MOSFET-based gates had better electrical masking characteristics. First, a III-V TFET model was selected which was used to

19

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5795)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- An Efficient E2E Verifiable E-Voting System Without Setup AssumptionsDocument9 pagesAn Efficient E2E Verifiable E-Voting System Without Setup AssumptionsTechnos_IncNo ratings yet

- An Smartphone-Based Door LockingDocument4 pagesAn Smartphone-Based Door LockingTechnos_IncNo ratings yet

- Robot LiteratureDocument58 pagesRobot LiteratureTechnos_IncNo ratings yet

- Android Best Titles 2018Document2 pagesAndroid Best Titles 2018Technos_IncNo ratings yet

- Online Review ModulesDocument2 pagesOnline Review ModulesTechnos_IncNo ratings yet

- Android Theft Tracking ReportDocument56 pagesAndroid Theft Tracking ReportTechnos_IncNo ratings yet

- Image Fusion ReportDocument79 pagesImage Fusion ReportTechnos_IncNo ratings yet

- Banking Robot MissingDocument18 pagesBanking Robot MissingTechnos_IncNo ratings yet

- Thermal and Structural Analysis of Vented and Normal Disc Brake RotorsDocument9 pagesThermal and Structural Analysis of Vented and Normal Disc Brake RotorsTechnos_IncNo ratings yet

- A Human Hand Gesture Based TV Fan Control System Using Open CVDocument99 pagesA Human Hand Gesture Based TV Fan Control System Using Open CVTechnos_IncNo ratings yet

- VT Scope 3 Scope 2: Discrete, Ts 5e-005 SDocument1 pageVT Scope 3 Scope 2: Discrete, Ts 5e-005 STechnos_IncNo ratings yet

- Fabrication of A Drone: A Major Project Report OnDocument30 pagesFabrication of A Drone: A Major Project Report OnTechnos_Inc100% (1)

- IoT WiFi Based Data Logger With Device ControlDocument3 pagesIoT WiFi Based Data Logger With Device ControlTechnos_IncNo ratings yet

- CanonicalDocument7 pagesCanonicalTechnos_IncNo ratings yet

- Dam Monitoring PPT 1Document19 pagesDam Monitoring PPT 1Technos_IncNo ratings yet

- (##) Pneumatic High Speed Hacksaw MachineDocument79 pages(##) Pneumatic High Speed Hacksaw MachineTechnos_Inc0% (2)

- Cuck ConverterDocument14 pagesCuck ConverterTechnos_IncNo ratings yet

- VT Scope 3 Scope 2: Discrete, Ts 5e-005 SDocument1 pageVT Scope 3 Scope 2: Discrete, Ts 5e-005 STechnos_IncNo ratings yet

- Licence PlateDocument40 pagesLicence PlateTechnos_Inc50% (2)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1091)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- NS Analog Signal Path Design Seminar 2006Document442 pagesNS Analog Signal Path Design Seminar 2006Id Vágó MiklósNo ratings yet

- Triac and DiacDocument10 pagesTriac and DiacUmair HassanNo ratings yet

- N Channel MOSFET Level 1Document5 pagesN Channel MOSFET Level 1Kyusang ParkNo ratings yet

- Buk 553100 BDocument7 pagesBuk 553100 BMario FloresNo ratings yet

- ATC321 PTV Training ManualDocument44 pagesATC321 PTV Training ManualThetechmanNo ratings yet

- Mosfet I RF 6602Document9 pagesMosfet I RF 6602BioxxxsmartbrainNo ratings yet

- KL 620 PDFDocument151 pagesKL 620 PDFFidaa JaafrahNo ratings yet

- Introduction To Nanoelectronics FinalDocument18 pagesIntroduction To Nanoelectronics Finalparmis1212No ratings yet

- FDP3651UDocument7 pagesFDP3651UPramote RodbonNo ratings yet

- R 2008 M.E. Applied Electronics SyllabusDocument31 pagesR 2008 M.E. Applied Electronics SyllabusisasenthilNo ratings yet

- Irf 540 NsDocument11 pagesIrf 540 NsLucas PascualNo ratings yet

- Ec 1Document35 pagesEc 1Rekha SharmilyNo ratings yet

- Data SheetaaaDocument6 pagesData SheetaaaАлександар МазињанинNo ratings yet

- Rajiv Gandhi Proudyogiki Vishwavidyalaya, Bhopal: BT301 Mathematics-III 3L-1T-0P 4 CreditsDocument7 pagesRajiv Gandhi Proudyogiki Vishwavidyalaya, Bhopal: BT301 Mathematics-III 3L-1T-0P 4 CreditsRachit JainNo ratings yet

- IGBTDocument17 pagesIGBTJuank Ñ LduNo ratings yet

- Test Igbt-1Document2 pagesTest Igbt-1Amanda Carroll100% (1)

- Compound Field Effect Power Transistor: N-Channel Power Mos Fet Array Switching Industrial UseDocument4 pagesCompound Field Effect Power Transistor: N-Channel Power Mos Fet Array Switching Industrial Usekatty cumbeNo ratings yet

- The Development of Flexible Integrated Circuits Based On Thin-Film TransistorsDocument10 pagesThe Development of Flexible Integrated Circuits Based On Thin-Film TransistorsJOAM MANUEL RINCÓN ZULUAGANo ratings yet

- CSE IYearAutonomoussyllabusDocument52 pagesCSE IYearAutonomoussyllabusRazha GarrixNo ratings yet

- Design and Performance Analysis of Low Power DigitalDocument16 pagesDesign and Performance Analysis of Low Power DigitalPooja VermaNo ratings yet

- Cascode Connection (Group 4)Document4 pagesCascode Connection (Group 4)Mark justine davidNo ratings yet

- DIC QuestionsDocument2 pagesDIC QuestionsAshish KrNo ratings yet

- N WellDocument21 pagesN WellSanthanu SurendranNo ratings yet

- High Voltage Power Pulse CircuitDocument1 pageHigh Voltage Power Pulse CircuittaiyawutNo ratings yet

- Discrete MOSFET AmplifiersDocument43 pagesDiscrete MOSFET Amplifiersmaddineni vagdeviNo ratings yet

- Microwave & Optical Engineering Question BankDocument47 pagesMicrowave & Optical Engineering Question BankThiagu RajivNo ratings yet

- PAM Multiplexers ReportingDocument20 pagesPAM Multiplexers ReportingJaed Caraig100% (1)

- Datasheet k3325Document8 pagesDatasheet k3325Heriberto Flores AmpieNo ratings yet

- S.Y. B.SC - PDF - VNSGU 2006-07Document8 pagesS.Y. B.SC - PDF - VNSGU 2006-07drharshalpatel1986No ratings yet

- VLSIDocument22 pagesVLSIMoulana YasinNo ratings yet