Professional Documents

Culture Documents

A Low Cascode Amplifier: Noise

Uploaded by

dcastrelos2000Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

A Low Cascode Amplifier: Noise

Uploaded by

dcastrelos2000Copyright:

Available Formats

Volume 92, Number 6, November-December 1987

Journal of Research of the National Bureau of Standards

A Low Noise Cascode Amplifier

Volume 92

Steven R. Jefferts

Joint Institute for Laboratory

Astrophysics

University of Colorado and

National Bureau of Standards

Boulder, CO 80309

and

Number 6

November-December 1987

We describe the design, schematics, and

performance of a very low noise FET

cascode input amplifier. This amplitier has noise performance of less than

1.2 n V / 6 and 0.25 f A d % over the

500 Hz to 50 kHz frequency range. The

amplifier is presently being used in conjunction with a Penning ion trap but is

applicable to a wide variety of uses

requiring low noise gain in the 1 Hz to

30 MHz frequency range,

Key words: cascode amplifier; low bias

current amplifier; low noise FET amplitier; noise analysis; noise current; noise

voltage.

F. L. Walls

National Bureau of Standards

Boulder, CO 80303

Accepted June 8, 1987

Introduction

This paper discusses some general design criteria

for cascode amplifiers and draws some conclusions

concerning the optimum choice of FETs for such

amplifiers. A particular design having the noise

performance described above is presented and analyzed. Variations of the design which either have

much larger bandwidth, 30MHz, or draw extremely low input bias current, less than 0.01 PA,

are briefly discussed.

A low noise amplifier has been designed using a

2SK117 N channel J-FET as the input device in

a cascode [11 configuration. Noise measurements

on this amplifier y g d a low frequency noise current of 0.25 fA@Hz and a voltage noise of less

than 1.2 nV/dHz in the 500 Hz to 50 kHz region.

Bloyet et al. [2] suggest a figure of merit of the

product of the noise voltage and current as being

appropriate for amplifiers of this type. This amplifier has a figure of merit of -3 X lopz5W/Hz,

which is almost two orders of magnitude smaller

than other amplifiers reported elsewhere. [2]

The amplifier described here is presently being

used in conjunction with a Penning trap to detect

small image currents (-0.01 PA) induced by ion

motion in the trap. [3] This amplifier also appears

to be well suited for use in noise thermometry experiments. [4]

Equivalent Circuit for Noise Analysis

The schematic of the amplifier is shown in

figure 1. The biasing scheme used for 4 2 , the common base portion of the cascode, is attractive for its

simplicity and inherent low noise. However, to

work properly it requires that Idss [5] of 4 2 be

larger than Idss of Q1.

383

Volume 92, Number 6, November-December 1987

Journal of Research of the National Bureau of Standards

500R 500R V +

(12-30V)

I MR

A OP- 2 7 IBoPF

UTPUT

I OpF

I MR

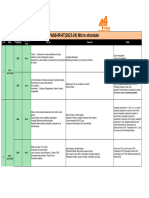

Figure 1. Schematic diagram of the low noise preamplifier. NOTE: 1) All resistors 1% metal film.

2) All capacitors are tantalum. 3) V + must be well filtered. 4) The OP-27 power supply leads should

be bypassed with 10 fl and 0.1 pF close to the OP-AMP.

The gain of the cascode input stage is large,

about 50. Hence, the noise in this stage is the dominant noise mechanism in the amplifier, and we will

therefore confine our analysis to the cascode input

stage and the associated biasing circuitry. The signal frequency equivalent circuit of the input stage

is illustrated in figure 2. From figure 2 we can proceed to draw the noise equivalent circuit as shown

in figure 3. Using this model, we can write the

equivalent input noise, Eni,as [6]

bootstrapping c g d of Q1 for lowest input capacitance and gain in Q1 suppressing voltage noise in

4 2 relative to Q1. This suggests that the choice of

identical FETs for Q1 and 4 2 may not be optimum. For this amplifier, we chose 4 2 to be a

2N4416, yielding gml/gm2

4,which suppresses

the voltage noise of 4 2 well below that of Q1 and

still provides a reduction of input capacitance from

-44 to -11 pF.

Noise Measurements

The amplifier noise was determined by first measuring the transfer function of the amplifier on a

spectrum analyzer (see fig. 4). The input capacitance was then obtained by using a known value of

the capacitor in series with the input of the amplifier and measuring the change in apparent amplifier

gain as a function of capacitance. In order to measure the input current noise, the gate bias$resistor,

R,, was increased to 7 X 10" R so that the term

ItQlZ,' would dominate in eq (1). A measurement

of the noise from 1.5 to 10Hz coupled with the

known input capacitance, C,, allows one to write

where K , = gmlRd and KQ1 = -gml/gm2 is the

gain of the common source component of the cascode. Z , is the impedance presented to the gate of

Q1 formed by the parallel combination of C,, the

gate capacitance, and R,, the gate bias resistor.

The choice of 4 2 is governed by a tradeoff between

where Eni(f)is the equivalent noise at frequency f

at the input of Q1. Using a linear regression analysis to find the slope, m , of the l/Eni vs f line, we

can then write

OUTPUT

2TC

InQI

(3)

This analysis holds, assuming that the thermal noise

current of R, does not swamp the noise current of

Q1 and that the perturbation of l/f noise is small.

The first assumption is easily checked as our

Figure 2. Signal frequency equivalent circuit of the cascode

input stage.

3 84

Volume 92, Number 6, November-December 1987

Journal of Research of the National Bureau of Standards

17

Rd=3K

qm2"GS2

OUTPUT

INPUT a

ENIOLI

Figure 3. The noise equivalent circuit of the cascode input state

If the noise associated with 42, gml/gm2, and the

output noise are measured, one can infer the noise

associated with Q 1.

7 x 10" R resistor used for R, generates only

0.15 fA/dHz noise current which is of the same

order of magnitude as the noise current associated

with Q1. The l/f contribution of current noise in

both the input FET and R , was measured to be less

than

A / d H z at 1.5 Hz.

Results

Measurements using three different 2SK117

FETs for Q1 and a variety of different 2N4116

FETs for 4 2 give the following results for the

amplifier

Eni1: 1. 1 nV/d/Hz

IO

I

10

IO2

io3

io4

Ini== 0.25 fA/d&

(5)

Figure 5 shows the measured voltage noise as a

function of frequency for the amplifier. Independent measurements with 2N4416 FETs show that

the noise voltageassociated with them is approximately 3 nV/dHz. Using this value and eq ( 5 ) we

can infer a noise voltage for the 2SK117 of about

0.8 nV/v/Hz. It is interesting to compare this to

the theoretical result derived by van der Ziel: [7]

lo5

FREQUENCY ( H z )

Figure 4. Measured transfer function of the amplifiers.

E,,,,, the -voltage noise associated with Q1, was

measured by replacing the 7X 10" R resistor used

for R, with a 10 R resistor. This makes the I&, Z,'

term in eq (1) insignificant and the equation can

then be rewritten to yield:

enQl=

(; Z)I2

--

Using gml = - the transconductance of the

60 R '

385

Volume 92, Number 6, November-December 1987

Journal of Research of the National Bureau of Standards

Conclusion

2SK117 at 3 mA drain current, we obtain

enQl= 0.82 n V / m which is in agreement (possiWe have discussed the design and test of a FET

cascode input amplifier with extremely low

voltage noise, less than 1.2 nV/dHA and extremely low current noise, 0.25 fA/dHz.

This amplifier also has a low input capacitance

of 11 pF. Thus it can be used to provide useful low

noise gain from 1 Hz to more than 30 MHz. Another significant attribute is the very low bias current drawn by the amplifier, less than 0.3 PA; a

modified version of this amplifier draws even less

input bias current. A short discussion of design

criteria and noise mechanisms in cascode amplifiers

is also provided.

bly fortuitous) with the measured result.

100,

'

v)

z

W

W

a

I-

>

102

103

io4

FREQUENCY ( H z )

Figure 5.

Measured input voltage noise.

Acknowledgments

If one measures the gate current of the input

FET in a version of this amplifier in which 42, the

common gate portion of the cascode, is shorted,

making the input of the amplifier a common source

stage, an interesting effect occurs. The gate current, as measured by the voltage drop across R,,

decreases and finally changes sign with increasing

drain current. A measurement of the noise current

in this region suggests that in fact two (at least)

competing currents are responsible, as the noise

current is monotonically increasing in the region of

apparently zero gate bias current. This is as would

be expected for the noise from two competing processes. Thus, this effect is potentially useful in an

application in which the amplifier must draw a

minimal bias current through the gate. However, a

drawback to this circuit is that the input capacitance is 50 pF as opposed to 11 pF for the cascode configuration. The cascode amplifier also

exhibits very low input bias current, typically less

than 0.3 pA for drain currents in the 3 mA range,

but it does not exhibit an apparent vanishing of this

bias current as does the common source configuration. It should be noted that this effect prevents us

from inferring that the noise current in'Q1 is due to

shot noise in the measured gate current of Q1, since

the true gate current is not a well determined quantity in the presence of these competing currents.

The bandwidth of the amplifier as shown in

figure 1 is limited to about 500kHz. This bandwidth limitation is, however, due to the limited

bandwidth of the op-amp used for the output stage.

If additional bandwidth is required, R, and Rd

should be reduced and a video amplifier should be

used as the output stage.

The authors are grateful to John Hall and David

Howe for their many useful comments and suggestions. Steven R. Jefferts would also like to thank

Gordon Dunn for his support and encouragement

on this project.

About the Authors: Steven R. Jefferts is with the Joint

Institute for Laboratory Astrophysics University of

Colorado and the National Bureau of Standards.

F. L. Walls is a physicist with the Time and Frequency Division in the NBS Center for Basic Standards.

References

[ 11 The term cascode amplifier refers, in a historical sense, to a

pair of triode vacuum tubes operated as a grounded

cathode amplification stage followed by a grounded grid

amplification stage. In the case of bipolar transistors it

refers to a common emitter stage followed by a common

base stage and in FETs it is a common source-common

gate pair as used here. Hybrid cascode amplifiers using a

common source FET followed by a common base bipolar

transistor are also common. See, for example, R. Q. Twiss

and Y. Beers, in Vacuum Tube Amplifiers, MIT Radiation

LABS Series edited by G. E. Valley Jr. and M. Wallman

(Boston Technical Lithographers, 1963), Ch. 13.

[2] Bloyet, D., Lepaisant, J., and Varoquaux, E., Rev. Sci. Instrum. 56, 1763 (1985).

[3] Barlow, S. E., Luine, J. A., and Dunn, G. H., Int. J. Mass.

Spectrom. Ion Proc. 74, 97 (1986).

[4] Anderson, P. T., and Pipes, P. B., Rev. Sci. Instrum. 45, 42

(1974).

[5] Zdss is the value of the saturated drain-source current in a

FET operated at zero gate source voltage.

[6] Motchenbacher, C. D., and Fitchen, F. C., in Low Noise

Electrical Design (Wiley, New York, 1973), p. 231.

[7] van der Ziel, A., Proc. IEEE 50, 1808 (1962).

3 86

You might also like

- An Ultra Low Distortion Oscillator With THD Below - 140 DB PDFDocument7 pagesAn Ultra Low Distortion Oscillator With THD Below - 140 DB PDFvali29No ratings yet

- A 1 5V 1 5GHz CMOS LNADocument2 pagesA 1 5V 1 5GHz CMOS LNAZath OnamNo ratings yet

- MT-008 Tutorial: Converting Oscillator Phase Noise To Time JitterDocument10 pagesMT-008 Tutorial: Converting Oscillator Phase Noise To Time JitterAustin ShiNo ratings yet

- Audio IC Circuits Manual: Newnes Circuits Manual SeriesFrom EverandAudio IC Circuits Manual: Newnes Circuits Manual SeriesRating: 5 out of 5 stars5/5 (1)

- Design of Ultra Low Noise AmplifiersDocument10 pagesDesign of Ultra Low Noise AmplifiersRakotomalala Mamy TianaNo ratings yet

- Design of A 2.0 GHZ Low Noise AmplifierDocument4 pagesDesign of A 2.0 GHZ Low Noise AmplifierVaibhav TiwariNo ratings yet

- Design and Simulation of LNA: (Cadence Spectre RF)Document19 pagesDesign and Simulation of LNA: (Cadence Spectre RF)Kushal GajavellyNo ratings yet

- A 2.4-Ghz Low-Flicker-Noise Cmos Sub-Harmonic ReceiverDocument11 pagesA 2.4-Ghz Low-Flicker-Noise Cmos Sub-Harmonic ReceiverdabalejoNo ratings yet

- HFE0605 GrebennikovDocument7 pagesHFE0605 GrebennikovemremiranNo ratings yet

- Natural Radio ReceiverDocument4 pagesNatural Radio ReceiverFJ GLNo ratings yet

- 10MHz - 10GHz Noise SourceDocument8 pages10MHz - 10GHz Noise SourceOksana LotitoNo ratings yet

- A 1.5V 1.5GHz CMOS LNADocument16 pagesA 1.5V 1.5GHz CMOS LNAptt3iNo ratings yet

- LSK489 Application Note Preliminary DraftDocument16 pagesLSK489 Application Note Preliminary DrafttarpinoNo ratings yet

- Active AntennasDocument4 pagesActive AntennasGuillermo Avila Elizondo100% (1)

- LP SiGe-HBT Active DB Mixer For Compact Integrated C-Band WLAN RXsDocument4 pagesLP SiGe-HBT Active DB Mixer For Compact Integrated C-Band WLAN RXssuper_lativoNo ratings yet

- Simultaneous Noise and Impedance MatchingDocument4 pagesSimultaneous Noise and Impedance MatchingDurbha RaviNo ratings yet

- Measuring Inductors at VHF and AboveDocument7 pagesMeasuring Inductors at VHF and Abovedusan.papez9216No ratings yet

- LM1894 Dynamic Noise Reduction System DNR: General DescriptionDocument10 pagesLM1894 Dynamic Noise Reduction System DNR: General DescriptionKoszegi AttilaNo ratings yet

- Influence of RF Oscillators On An Ofdm SignalDocument12 pagesInfluence of RF Oscillators On An Ofdm SignalLi ChunshuNo ratings yet

- A 100MHz To 500MHz Low Noise Feedback Amplifier Using ATF-54143 (AN5057 Avago)Document8 pagesA 100MHz To 500MHz Low Noise Feedback Amplifier Using ATF-54143 (AN5057 Avago)XollloXNo ratings yet

- Tayloe Mixer X3aDocument12 pagesTayloe Mixer X3alu1agpNo ratings yet

- 10 1 1 464 2858Document31 pages10 1 1 464 2858hariprasad123450% (1)

- HF VHF SDR Receiver Part1 YU1LMDocument15 pagesHF VHF SDR Receiver Part1 YU1LMtelkonNo ratings yet

- AMSAT Eagle - 70 CM Receiver Circuit DescriptionDocument9 pagesAMSAT Eagle - 70 CM Receiver Circuit Descriptionettore68No ratings yet

- Amp DesignDocument10 pagesAmp DesignakeedtheNo ratings yet

- Performance Very Low Frequency Filters: Design Considerations For HighDocument4 pagesPerformance Very Low Frequency Filters: Design Considerations For Highmvmuthukumar88No ratings yet

- LinearAudio v0 - A New Low-Noise Circuit Approach For PentodesDocument20 pagesLinearAudio v0 - A New Low-Noise Circuit Approach For PentodeslordoffDOCNo ratings yet

- Noise in LDOs Slyt201Document4 pagesNoise in LDOs Slyt201David DobrinNo ratings yet

- Atf36077 Appl2Document4 pagesAtf36077 Appl2Johnny TienNo ratings yet

- Design of Low Power LNA For GPS Application: Varish Diddi, Kumar Vaibhav Srivastava and Animesh BiswasDocument5 pagesDesign of Low Power LNA For GPS Application: Varish Diddi, Kumar Vaibhav Srivastava and Animesh BiswasSoar HoNo ratings yet

- JLH 2001 DesignDocument4 pagesJLH 2001 DesignDaniel ScardiniNo ratings yet

- Ultra-Wideband Low Noise Amplifier Using A Cascode Feedback TopologyDocument3 pagesUltra-Wideband Low Noise Amplifier Using A Cascode Feedback TopologyAsad AsadiNo ratings yet

- Low Noise Amplifiers For Small and Large Area PhotodiodesDocument2 pagesLow Noise Amplifiers For Small and Large Area Photodiodesramon_orozco_2No ratings yet

- Practical Transistor CircuitsDocument11 pagesPractical Transistor CircuitsFilip Angelovski100% (1)

- A 1v Fully Differential Cmos Lna For 24ghz ApplicationDocument4 pagesA 1v Fully Differential Cmos Lna For 24ghz ApplicationPradipta RayNo ratings yet

- An-779 Low-Distortion 1.6 To 30 MHZ SSB Driver DesignsDocument10 pagesAn-779 Low-Distortion 1.6 To 30 MHZ SSB Driver DesignsEdward YanezNo ratings yet

- Wideband Microwave Amplifier DesignDocument11 pagesWideband Microwave Amplifier DesignbaymanNo ratings yet

- Implementing Voice Controlled Operation of Peripherals (Interactive Voice Response)Document49 pagesImplementing Voice Controlled Operation of Peripherals (Interactive Voice Response)Ramnarayan ShreyasNo ratings yet

- Government College of Engineering Aurangabad: Optical Fiber Communication Assignment On "Receiver Structures"Document58 pagesGovernment College of Engineering Aurangabad: Optical Fiber Communication Assignment On "Receiver Structures"mekalaNo ratings yet

- HP AN1129 Low Noise 2.3GHz Amplifier ATF-36077Document4 pagesHP AN1129 Low Noise 2.3GHz Amplifier ATF-36077Johnny TienNo ratings yet

- Folded Cascode ChopperDocument4 pagesFolded Cascode ChoppergirishknathNo ratings yet

- An106 - Low-Noise Jfets - Spuerior Perform Ace To BipolarsDocument5 pagesAn106 - Low-Noise Jfets - Spuerior Perform Ace To BipolarsDewdeAlmightyNo ratings yet

- Design and Implementation of A Low-Voltage 2.4-Ghz Cmos RF Receiver Front-End For Wireless CommunicationDocument6 pagesDesign and Implementation of A Low-Voltage 2.4-Ghz Cmos RF Receiver Front-End For Wireless CommunicationPaul ShineNo ratings yet

- SiGe RF Front-End PerformanceDocument6 pagesSiGe RF Front-End PerformancekimvirusNo ratings yet

- An Integrated Planar Patch Clamp System For Cell ElectrophysiologyDocument4 pagesAn Integrated Planar Patch Clamp System For Cell ElectrophysiologySantosh PandeyNo ratings yet

- Unleashing The LM386Document3 pagesUnleashing The LM386MR XNo ratings yet

- 4 PDFDocument7 pages4 PDFPramod PuttaNo ratings yet

- Coaxial Cable DelayDocument6 pagesCoaxial Cable DelayFeberly BarituaNo ratings yet

- A Low Frequency Ultra Low Distortion OscillatorDocument2 pagesA Low Frequency Ultra Low Distortion Oscillatorluis lopezNo ratings yet

- LTC6268 Photodiode AmplifierDocument7 pagesLTC6268 Photodiode Amplifierestraj1954No ratings yet

- Chapter13 Transceiver Design ExampleDocument72 pagesChapter13 Transceiver Design ExampleNikunj ShahNo ratings yet

- 12AX7 6V6 Single Ended Class A Tube Amplifier Design and ConstructionDocument11 pages12AX7 6V6 Single Ended Class A Tube Amplifier Design and ConstructionOz Heat86% (7)

- An Area-Efficient Low-Power SC Integrator For Very High Resolution AdcsDocument4 pagesAn Area-Efficient Low-Power SC Integrator For Very High Resolution AdcsmikeNo ratings yet

- Simple Broadband Power AmplifiersDocument6 pagesSimple Broadband Power AmplifiersYoussef FayadNo ratings yet

- RF Power Amplifier FundamentalsDocument36 pagesRF Power Amplifier Fundamentalsi_spyder5388100% (1)

- Benson's BurstsDocument5 pagesBenson's Burstsdcastrelos2000No ratings yet

- Semiconductor Application NoteDocument10 pagesSemiconductor Application NoteFarshad yazdi100% (2)

- Active Loads and Signal Current ControlDocument10 pagesActive Loads and Signal Current ControlyogimgurtNo ratings yet

- ESL DesignDocument13 pagesESL Designdcastrelos20000% (1)

- Servo BiasDocument3 pagesServo Biasdcastrelos2000No ratings yet

- BSC MathCadDocument11 pagesBSC MathCaddcastrelos2000No ratings yet

- Benson's BurstsDocument5 pagesBenson's Burstsdcastrelos2000No ratings yet

- Active Loads and Signal Current ControlDocument10 pagesActive Loads and Signal Current ControlyogimgurtNo ratings yet

- Measuring Junction NoiseDocument7 pagesMeasuring Junction Noisedcastrelos2000No ratings yet

- PI74ALVTC16374: Product Description Product FeaturesDocument9 pagesPI74ALVTC16374: Product Description Product Featuresdcastrelos2000No ratings yet

- Measuring Measuring Mics PDFDocument3 pagesMeasuring Measuring Mics PDFdcastrelos2000No ratings yet

- Honeywell Thermostat CM61NGDocument2 pagesHoneywell Thermostat CM61NGdcastrelos2000No ratings yet

- Servo BiasDocument3 pagesServo Biasdcastrelos2000No ratings yet

- Rodons Angles Bigues PlanxesDocument1 pageRodons Angles Bigues Planxesdcastrelos2000No ratings yet

- Technical Data!Document19 pagesTechnical Data!Emi CurlettoNo ratings yet

- Hattifant TPballs 2 A4.compressed PDFDocument1 pageHattifant TPballs 2 A4.compressed PDFdcastrelos2000No ratings yet

- Physics of Microwave OvenDocument8 pagesPhysics of Microwave Ovenabdel100% (1)

- FLIR Lepton Data BriefDocument50 pagesFLIR Lepton Data BriefcbspfrsNo ratings yet

- Index PDFDocument15 pagesIndex PDFdcastrelos2000No ratings yet

- Taula de Pesos I Mides de Tubs Rectangulars, Rodons I QuadratsDocument1 pageTaula de Pesos I Mides de Tubs Rectangulars, Rodons I Quadratsdcastrelos2000No ratings yet

- ThesisteslaDocument96 pagesThesisteslangelectronic5226No ratings yet

- Chapter 2Document10 pagesChapter 2Amara BhargavNo ratings yet

- Development of Low-Cost Tesla Transformer For High Performance Testing 115 KV Line Post InsulatorDocument5 pagesDevelopment of Low-Cost Tesla Transformer For High Performance Testing 115 KV Line Post Insulatordcastrelos2000No ratings yet

- Toc PDFDocument15 pagesToc PDFdcastrelos2000No ratings yet

- 26 June 2014 Webcast TDocument34 pages26 June 2014 Webcast Tdcastrelos2000No ratings yet

- ReadmeDocument2 pagesReadmewrite2arshad_mNo ratings yet

- Power Topologies Quick Reference Guide: 5 DpnqpxfsupqpmphjftDocument7 pagesPower Topologies Quick Reference Guide: 5 Dpnqpxfsupqpmphjftdcastrelos2000No ratings yet

- Eupl enDocument7 pagesEupl enMing LiNo ratings yet

- 5990 6999en PDFDocument7 pages5990 6999en PDFdcastrelos2000No ratings yet

- Kasp10.0 Rescue Disk enDocument81 pagesKasp10.0 Rescue Disk enHarilal SajanNo ratings yet

- Carel MxproDocument64 pagesCarel MxproPreot Andreana CatalinNo ratings yet

- CSIE Fisa Disciplina - Baze de DateDocument4 pagesCSIE Fisa Disciplina - Baze de DateCostin CheluNo ratings yet

- Module 1 Grade 8 (De Guzman)Document9 pagesModule 1 Grade 8 (De Guzman)Kim De GuzmanNo ratings yet

- T 096Document3 pagesT 096abelNo ratings yet

- Ethoxy 1Document77 pagesEthoxy 1HoshiNo ratings yet

- FI Printing Guide Vinyl-303Document1 pageFI Printing Guide Vinyl-303tomasykNo ratings yet

- Silicon Controlled RectifierDocument38 pagesSilicon Controlled RectifierPaoNo ratings yet

- Sqluser v11r1Document199 pagesSqluser v11r1samnolenNo ratings yet

- GTG - TFA Belt DrivenDocument2 pagesGTG - TFA Belt Drivensuan170No ratings yet

- MoazzamMaqsood Transcript PDFDocument3 pagesMoazzamMaqsood Transcript PDFmoazzam maqsoodNo ratings yet

- LBX 6513DS VTMDocument4 pagesLBX 6513DS VTMsergiocuencascribNo ratings yet

- PDC NitDocument6 pagesPDC NitrpshvjuNo ratings yet

- Air Movements 06-26-2019 - Full ScoreDocument5 pagesAir Movements 06-26-2019 - Full ScoreMichael CrawfordNo ratings yet

- Zener Barrier: 2002 IS CatalogDocument1 pageZener Barrier: 2002 IS CatalogabcNo ratings yet

- Tutoriales Mastercam V8 6-11Document128 pagesTutoriales Mastercam V8 6-11Eduardo Felix Ramirez PalaciosNo ratings yet

- Latihan Matematik DLP Minggu 1Document3 pagesLatihan Matematik DLP Minggu 1Unit Sains Komputer MRSM PendangNo ratings yet

- 1400 CFM TDocument3 pages1400 CFM TmahmadwasiNo ratings yet

- Narayana Xii Pass Ir Iit (2023 24) PDFDocument16 pagesNarayana Xii Pass Ir Iit (2023 24) PDFRaghav ChaudharyNo ratings yet

- Unit Exam 5Document3 pagesUnit Exam 5Rose AstoNo ratings yet

- Magnetism NotesDocument14 pagesMagnetism Notesapi-277818647No ratings yet

- The Roles of ComputerDocument1 pageThe Roles of ComputerDika Triandimas0% (1)

- K20 Engine Control Module X3 (Lt4) Document ID# 4739106Document3 pagesK20 Engine Control Module X3 (Lt4) Document ID# 4739106Data TécnicaNo ratings yet

- X500Document3 pagesX500yu3zaNo ratings yet

- Question IARDocument4 pagesQuestion IARAryan jay vermaNo ratings yet

- Basic Electronics Lab ManualDocument47 pagesBasic Electronics Lab ManualAlpesh ThesiyaNo ratings yet

- TMT Boron CoatingDocument6 pagesTMT Boron Coatingcvolkan1100% (2)

- Chap006 - Process Selection & Facility Layout-1Document48 pagesChap006 - Process Selection & Facility Layout-1Ohud AlanaziNo ratings yet

- Cep MPDocument1 pageCep MPAzmat HabeebNo ratings yet

- P 130881757895329843Document44 pagesP 130881757895329843Vijay MohanNo ratings yet