Professional Documents

Culture Documents

RTL Synthesis: Choice-1: Target Expression-1 Choice-2: Target Expression-2 Choice-N: Target Expression-N

Uploaded by

Harshal Ambatkar0 ratings0% found this document useful (0 votes)

10 views2 pagesRTL Synthesis

Original Title

RTL Synthesis

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentRTL Synthesis

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

10 views2 pagesRTL Synthesis: Choice-1: Target Expression-1 Choice-2: Target Expression-2 Choice-N: Target Expression-N

Uploaded by

Harshal AmbatkarRTL Synthesis

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

You are on page 1of 2

RTL Synthesis

1. To transform Verilog design descriptions expressed at the register-transfer level of abstraction

into implementations at the gate level.

2. We can perform operations on single-bit nets and variables for single-bit signals and vector nets

and variables for multibit signals, such as logical operations (&&, || and !), bit-wise operations

(&, |, ~ etc.), shift operations (<<, >> etc.), the conditional operator (... ?... : ...), concatenation

({..., ...}), bit select and part select. These operations can be implemented by synthesis tools.

3. Synthesis tools typically do not support use of real numeric values and operations, since the

hardware required to implement them is much more complex than that for integer types

4. Consider conditional statements in the always block implementing same logic

Case i: case statement

always @*

case (select-expression)

choice-1: target = expression-1;

choice-2: target = expression-2;

...

choice-n: target = expression-n;

endcase

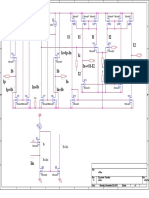

A synthesis tool could infer a multiplexer, provided the choice values were distinct and included all

possible values of the select expression. The select inputs of the multiplexer are connected to the output of

the combinational logic inferred from the select expression.

Each of the assignment expressions would be synthesized to combinational logic connected to the

particular data input of the multiplexer identified by the corresponding choice value. The choice values

are expressions, but they must not involve any inputs. Usually, they are just literal values.

Case i: if statement, containing nested assignments.

always @*

if (condition-1) target = expression-1;

else if (condition-1) target = expression-1;

...

else target = expression-n;

Each of the expressions and conditions implies combinational logic. The outputs of the expression logic

are connected to decision logic driven by the condition logic, such as that shown in Figure C.3. Since the

conditions are tested one by one until a true condition is found, the decision logic is priority based, with

conditions appearing earlier in the conditional assignment having priority over those appearing later. As a

consequence, the propagation delay for the inferred logic may be as long as the sum of propagation delays

of the inferred decision component. Of course, a synthesis tool may optimize the circuit, and may be able

to implement the assignment as a single multiplexer if the conditions are mutually exclusive.

You might also like

- DAA Unit 1Document15 pagesDAA Unit 1mfake0969No ratings yet

- Daa Unit-1Document73 pagesDaa Unit-1Razia BegumNo ratings yet

- Daa Unit 1Document15 pagesDaa Unit 1KARTHIK BANDINo ratings yet

- Unit 1Document72 pagesUnit 1Syed SulaimanNo ratings yet

- Daa Unit-IDocument80 pagesDaa Unit-Iansh_123No ratings yet

- Data Flow Modelling, Mux and Adders: Gate DelaysDocument15 pagesData Flow Modelling, Mux and Adders: Gate DelaysMuhammad Usman RafiqNo ratings yet

- Unit 1Document28 pagesUnit 1Jogappagari VinodkumarNo ratings yet

- INF1511 - Chapter 2 - Getting Wet in PythonDocument3 pagesINF1511 - Chapter 2 - Getting Wet in PythonRofhiwa RamahalaNo ratings yet

- 1 - To - 5 - Lecture NotesDocument41 pages1 - To - 5 - Lecture Notesabizer safdariNo ratings yet

- Design and Analysis of Algorithms ModuleDocument53 pagesDesign and Analysis of Algorithms Moduledawit8030No ratings yet

- Analysis & Design of AlgorithmsDocument14 pagesAnalysis & Design of AlgorithmsHarshit kumar sinhaNo ratings yet

- DSC I UnitDocument77 pagesDSC I UnitSaiprabhakar DevineniNo ratings yet

- Learning Complex Boolean Functions: Algorithms and ApplicationsDocument8 pagesLearning Complex Boolean Functions: Algorithms and ApplicationsMario Betanzos UnamNo ratings yet

- Unit - 3Document14 pagesUnit - 3savatid730No ratings yet

- DS Unit1 Part-1Document65 pagesDS Unit1 Part-1reethu joyceyNo ratings yet

- Aim: Write A R Script To Demonstrate The Use of 1) Decision Making, 2) Loops 3) FunctionsDocument9 pagesAim: Write A R Script To Demonstrate The Use of 1) Decision Making, 2) Loops 3) FunctionsdwrreNo ratings yet

- Unit1 DaaDocument21 pagesUnit1 DaaArunachalam SelvaNo ratings yet

- Week 3 Branch 12425Document19 pagesWeek 3 Branch 12425Sems KrksNo ratings yet

- Unit - IDocument28 pagesUnit - I21131a05g1No ratings yet

- R19 It Iii Year 1 Semester Design and Analysis of Algorithms Unit 1Document39 pagesR19 It Iii Year 1 Semester Design and Analysis of Algorithms Unit 1KaarletNo ratings yet

- Assignment No.1: Title: Study of Object Oriented ProgrammingDocument20 pagesAssignment No.1: Title: Study of Object Oriented ProgrammingSports ClubeNo ratings yet

- Some Applications of The Vector Spaces:: Note1Document2 pagesSome Applications of The Vector Spaces:: Note1Zenonissya GalwanNo ratings yet

- Laboratory For Information and Decision Systems, Massachusetts Institute of Technology, Canibridge, MA 02139, U.S.ADocument14 pagesLaboratory For Information and Decision Systems, Massachusetts Institute of Technology, Canibridge, MA 02139, U.S.Aarun_kejariwalNo ratings yet

- HCS 111 Handout 1Document11 pagesHCS 111 Handout 1Gerald KapinguraNo ratings yet

- Data Structure & Algorithm: Prepared by Ms. Chyril A. Concemino, Mba, MistDocument61 pagesData Structure & Algorithm: Prepared by Ms. Chyril A. Concemino, Mba, MistMaria Canete100% (1)

- The Opensees Command Language ManualDocument34 pagesThe Opensees Command Language ManualNaba Raj ShresthaNo ratings yet

- CRC Analysing and Correcting ErrorsDocument13 pagesCRC Analysing and Correcting ErrorsAdarshNo ratings yet

- Greedy AlgorithmsDocument42 pagesGreedy AlgorithmsreyannNo ratings yet

- Complexity Theory: Space Complexity Probabilistic Complexity Interactive ProofDocument44 pagesComplexity Theory: Space Complexity Probabilistic Complexity Interactive ProofAyella JimmyNo ratings yet

- Chapter 09 PDFDocument16 pagesChapter 09 PDFJohn YangNo ratings yet

- Design & Analysis of Algorithms (DAA) Unit - IDocument18 pagesDesign & Analysis of Algorithms (DAA) Unit - IYogi NambulaNo ratings yet

- Daa Lecture NotesDocument120 pagesDaa Lecture NotesManoharNo ratings yet

- Pages From Digital Design - An Embedded Systems Approach Using VerilogDocument2 pagesPages From Digital Design - An Embedded Systems Approach Using VerilogHarshal AmbatkarNo ratings yet

- Introduction To Concurrent Programming: Operating SystemsDocument18 pagesIntroduction To Concurrent Programming: Operating Systemsonkar khavaleNo ratings yet

- Daa Lecture NotesDocument169 pagesDaa Lecture NotesNeelima MalchiNo ratings yet

- Unit 1 PDFDocument17 pagesUnit 1 PDFABHINAYA RANINo ratings yet

- DAA Unit1 JDocument39 pagesDAA Unit1 JA Raghava Chowdary maddipatiNo ratings yet

- Introduction To AlgorithmsDocument25 pagesIntroduction To Algorithmsanon_514479957No ratings yet

- BSFFTDocument30 pagesBSFFTChoon Peng TohNo ratings yet

- Fuzzy Logic - Wikipedia PDFDocument69 pagesFuzzy Logic - Wikipedia PDFannie joseNo ratings yet

- Data Structure and AlgoritmsDocument86 pagesData Structure and AlgoritmsasratNo ratings yet

- Lecture#02, DAA, Designing Algorithms, Calculating CostsDocument24 pagesLecture#02, DAA, Designing Algorithms, Calculating CostsSaqib AmeerNo ratings yet

- FsadfaDocument10 pagesFsadfaLethal11No ratings yet

- SEM5 - ADA - RMSE - Questions Solution1Document58 pagesSEM5 - ADA - RMSE - Questions Solution1DevanshuNo ratings yet

- C Language KeywordsDocument16 pagesC Language KeywordsSunny MahurNo ratings yet

- DAA Unit 1,2,3-1Document46 pagesDAA Unit 1,2,3-1abdulshahed231No ratings yet

- Bs (It) Al Habib Group of Colleges: Assignment AlgorithmDocument5 pagesBs (It) Al Habib Group of Colleges: Assignment AlgorithmusmanaltafNo ratings yet

- Modeling Long-Run Relationship in FinanceDocument43 pagesModeling Long-Run Relationship in FinanceInge AngeliaNo ratings yet

- Simulation of Compound Hierarchical ModelsDocument9 pagesSimulation of Compound Hierarchical ModelsEdwin Quevedo QuispeNo ratings yet

- DAA 2marks With AnswersDocument11 pagesDAA 2marks With AnswersmiraclesureshNo ratings yet

- DA SlidesDocument349 pagesDA SlidesAvinash RajoriyaNo ratings yet

- DAA - Ch. 1 (Lecture Notes)Document24 pagesDAA - Ch. 1 (Lecture Notes)xihafaf422No ratings yet

- Department of Computer Science: A Genetic Algorithm TutorialDocument41 pagesDepartment of Computer Science: A Genetic Algorithm TutorialPrempal TomarNo ratings yet

- Chapter 1Document18 pagesChapter 1DesyilalNo ratings yet

- Vision 2024 CD Chapter 5 Compiler Code Optimization 731689660928542Document24 pagesVision 2024 CD Chapter 5 Compiler Code Optimization 731689660928542Aman KoliNo ratings yet

- Daa SDocument6 pagesDaa Skolasandeep555No ratings yet

- Some NotesDocument5 pagesSome NotesMarvin AtienzaNo ratings yet

- Cddita - Page10Document1 pageCddita - Page10Harshal AmbatkarNo ratings yet

- Assignment 3Document1 pageAssignment 3Harshal AmbatkarNo ratings yet

- Cddita - Page11Document1 pageCddita - Page11Harshal AmbatkarNo ratings yet

- Pedram 1Document15 pagesPedram 1Harshal AmbatkarNo ratings yet

- FlowCAD An Quick Start PSpice 172 LiteDocument26 pagesFlowCAD An Quick Start PSpice 172 LiteHarshal AmbatkarNo ratings yet

- Comp Arch CH 03 L05 Booth AlgorDocument35 pagesComp Arch CH 03 L05 Booth AlgorLatesh RSNo ratings yet

- Pedram 1Document15 pagesPedram 1Harshal AmbatkarNo ratings yet

- Corrected CodeDocument4 pagesCorrected CodeHarshal AmbatkarNo ratings yet

- Pages From ASIC Flow DiagramDocument1 pagePages From ASIC Flow DiagramHarshal AmbatkarNo ratings yet

- Power Dissipation DerivationDocument11 pagesPower Dissipation DerivationHarshal AmbatkarNo ratings yet

- Ieee Ieee STD - LOGIC - 1164: Library Use ALLDocument2 pagesIeee Ieee STD - LOGIC - 1164: Library Use ALLHarshal AmbatkarNo ratings yet

- Bidirectional BusDocument1 pageBidirectional BusHarshal AmbatkarNo ratings yet

- TSMC 180nmDocument2 pagesTSMC 180nmHarshal Ambatkar100% (1)

- Buffer - How To Find Setup Time and Hol..Document7 pagesBuffer - How To Find Setup Time and Hol..Harshal AmbatkarNo ratings yet

- 8085Document21 pages8085Harshal AmbatkarNo ratings yet

- Scope of Eda ToolsDocument2 pagesScope of Eda ToolsHarshal AmbatkarNo ratings yet

- SyllabusDocument1 pageSyllabusHarshal AmbatkarNo ratings yet

- LibrariesDocument3 pagesLibrariesHarshal Ambatkar100% (1)

- Pages From Digital Design - An Embedded Systems Approach Using VerilogDocument2 pagesPages From Digital Design - An Embedded Systems Approach Using VerilogHarshal AmbatkarNo ratings yet

- Void Main Int I WhileDocument1 pageVoid Main Int I WhileHarshal AmbatkarNo ratings yet

- DFTDocument3 pagesDFTHarshal AmbatkarNo ratings yet

- Microprocessor FileDocument93 pagesMicroprocessor FileHarshal AmbatkarNo ratings yet

- RTL inDocument1 pageRTL inHarshal AmbatkarNo ratings yet

- AFD Assignment (2k15VLS02) Harshal 5Document1 pageAFD Assignment (2k15VLS02) Harshal 5Harshal AmbatkarNo ratings yet

- AFD Assignment (2k15VLS02) Harshal 3Document1 pageAFD Assignment (2k15VLS02) Harshal 3Harshal AmbatkarNo ratings yet

- AFD Assignment (2k15VLS02) Harshal 8Document1 pageAFD Assignment (2k15VLS02) Harshal 8Harshal AmbatkarNo ratings yet

- AFD Assignment (2k15VLS02) Harshal 7Document1 pageAFD Assignment (2k15VLS02) Harshal 7Harshal AmbatkarNo ratings yet

- AFD Assignment (2k15VLS02) Harshal 6Document1 pageAFD Assignment (2k15VLS02) Harshal 6Harshal AmbatkarNo ratings yet

- AFD Assignment (2k15VLS02) Harshal 4Document1 pageAFD Assignment (2k15VLS02) Harshal 4Harshal AmbatkarNo ratings yet

- Grokking Algorithms: An illustrated guide for programmers and other curious peopleFrom EverandGrokking Algorithms: An illustrated guide for programmers and other curious peopleRating: 4 out of 5 stars4/5 (16)

- Dark Data: Why What You Don’t Know MattersFrom EverandDark Data: Why What You Don’t Know MattersRating: 4.5 out of 5 stars4.5/5 (3)

- Fusion Strategy: How Real-Time Data and AI Will Power the Industrial FutureFrom EverandFusion Strategy: How Real-Time Data and AI Will Power the Industrial FutureNo ratings yet

- Blockchain Basics: A Non-Technical Introduction in 25 StepsFrom EverandBlockchain Basics: A Non-Technical Introduction in 25 StepsRating: 4.5 out of 5 stars4.5/5 (24)

- Modelling Business Information: Entity relationship and class modelling for Business AnalystsFrom EverandModelling Business Information: Entity relationship and class modelling for Business AnalystsNo ratings yet

- Starting Database Administration: Oracle DBAFrom EverandStarting Database Administration: Oracle DBARating: 3 out of 5 stars3/5 (2)

- Business Intelligence Strategy and Big Data Analytics: A General Management PerspectiveFrom EverandBusiness Intelligence Strategy and Big Data Analytics: A General Management PerspectiveRating: 5 out of 5 stars5/5 (5)

- THE STEP BY STEP GUIDE FOR SUCCESSFUL IMPLEMENTATION OF DATA LAKE-LAKEHOUSE-DATA WAREHOUSE: "THE STEP BY STEP GUIDE FOR SUCCESSFUL IMPLEMENTATION OF DATA LAKE-LAKEHOUSE-DATA WAREHOUSE"From EverandTHE STEP BY STEP GUIDE FOR SUCCESSFUL IMPLEMENTATION OF DATA LAKE-LAKEHOUSE-DATA WAREHOUSE: "THE STEP BY STEP GUIDE FOR SUCCESSFUL IMPLEMENTATION OF DATA LAKE-LAKEHOUSE-DATA WAREHOUSE"Rating: 3 out of 5 stars3/5 (1)

- Optimizing DAX: Improving DAX performance in Microsoft Power BI and Analysis ServicesFrom EverandOptimizing DAX: Improving DAX performance in Microsoft Power BI and Analysis ServicesNo ratings yet

- The Future of Competitive Strategy: Unleashing the Power of Data and Digital Ecosystems (Management on the Cutting Edge)From EverandThe Future of Competitive Strategy: Unleashing the Power of Data and Digital Ecosystems (Management on the Cutting Edge)Rating: 5 out of 5 stars5/5 (1)

- Joe Celko's SQL for Smarties: Advanced SQL ProgrammingFrom EverandJoe Celko's SQL for Smarties: Advanced SQL ProgrammingRating: 3 out of 5 stars3/5 (1)

- SQL QuickStart Guide: The Simplified Beginner's Guide to Managing, Analyzing, and Manipulating Data With SQLFrom EverandSQL QuickStart Guide: The Simplified Beginner's Guide to Managing, Analyzing, and Manipulating Data With SQLRating: 4.5 out of 5 stars4.5/5 (46)

- Oracle Database 12c Backup and Recovery Survival GuideFrom EverandOracle Database 12c Backup and Recovery Survival GuideRating: 4.5 out of 5 stars4.5/5 (3)

- High-Performance Oracle: Proven Methods for Achieving Optimum Performance and AvailabilityFrom EverandHigh-Performance Oracle: Proven Methods for Achieving Optimum Performance and AvailabilityNo ratings yet