Professional Documents

Culture Documents

Single Phase Inverters: Experiment 9

Uploaded by

AmeerMuaviaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Single Phase Inverters: Experiment 9

Uploaded by

AmeerMuaviaCopyright:

Available Formats

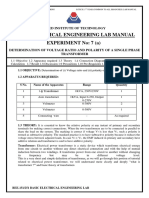

Experiment 9

Single Phase Inverters

Objectives

Understanding the operation and function of a single phase inverter in different configurations.

Pre-Lab Reading

Chapter 6, Power Electronics Circuits, Devices and Applications by M.H Rashid, 3rd

Edition

Lecture Notes for inverter circuits

Equipment

DC supply, oscilloscope, MOSFETs, TLP494, Multi-turn variable resistances, STM board, connecting wires and breadboard. DC supply and oscilloscope will be available in the lab remaining

components should be brought by the students as the part of component box. Please bring required resistances and capacitor as well.

9.1

Half Bridge Inverter

Figure 9.1(a) shows the circuit diagram for a half bridge inverter. A DC supply can be divided

into two equal voltage levels using the capacitors. Use high values of capacitor (100s of F) to

ensure the constant voltage division. Alternatively two separate supplies can be used as shown

in Figure 9.1. Switches S1 and S2 are switched in complimentary form such that S1 + S2 = 1.

The four switching states of the inverter operation are shown in Figure 9.2. Switches S1 and S2

must not be turned on at the same time. If S1 and S2 are switched on at the same time, there

will be a dead short, and destroys IGBTs/MOSFETs. If, on the other hand, both of them are

turned off, the inverter enters a stage called the dead-time.

87

88

EXPERIMENT 9. SINGLE PHASE INVERTERS

(a)

(b)

(c)

Figure 9.1: Half Bridge circuit for DC to AC inversion

During state A), S1 is conducting therefore we have a positive voltage across our load and there

is a current through the load. This current is slowly getting larger, since our load is inertial

(inductive).

During state B), the polarity of the load voltage is flipped (inverted). Therefore, the current

through inductor decreases. Notice that during this state, the current of the load is opposing

the voltage as if it was a current source. Note what happens with the load current: it flows

through S2 s diode, flowing against the barrier of potential created by the bottom voltage source.

During state C), the load current has already changed its polarity, so it can safely flow

through S2 . This phase is symmetrical to phase A). State D) is analogous to phase B) the

current cannot find any escape path other than S1 s diode.

This should suffice to explain why are flyback diodes used with inductive loads. Since an

IGBT can conduct current in one direction only, and does not have an intrinsic body diode of

a MOSFET, this is why IGBTs need to have protective freewheeling diodes in parallel.

Using a diode in parallel with a unidirectional device is common practice. Should the device

be subjected to a reverse-polarity voltage, a dangerous situation might occur. If the voltage

is high enough, an electric arc might destroy the device. With a diode, however, applying a

reverse voltage will result in current flowing through the diode. This may only destroy the

diode, which can be easily and inexpensively replaced.

Task

Setup the half bridge circuit circuit as shown in Figure 9.1. Use IR2104/IR2103 Gate

Driver IC for complimentary switching of S1 and S2 . Use RL = 5 10 and an appropriate value of Inductance (in the range 300 H) with a switching frequency of 50 Hz. C1

and C2 should be large value capacitors (100s of uF). Insert a small resistance in range of

9.1. HALF BRIDGE INVERTER

89

Figure 9.2: Four switching states of half bridge inverter.

0.1 in series with load to observe the current waveform in terms of voltage. Set input

voltage equal to 30V and supply current limit to 2 A.

Set a duty cycle of 50%. Observe the load voltage and current waveform ans save for your

report. Also record the RMS voltage VLrms and ILrms. Measure the input current from

the power supplies. Calculate the efficiency of the inverter.

Generate a switching waveform of frequency 10 kHz with variable duty cycle and perform

AND operation with previously generated 50 Hz 50 @ 50% duty cycle. Observe the load

voltage and current waveform ans save for your report. Also record the RMS voltage

VLrms and ILrms. Measure the input current from the power supplies. Calculate the

efficiency of the inverter.

Design the value of series resonance filter capacitor Cf to obtain a resonance frequency

equal to the switching frequency of 10 kHz. This capacitor is to be connected in series

with the inductor L.

Obtain the waveform across the load resistor RL with capacitor Cf connected. Observe

the load voltage and current waveform ans save for your report. Also record the RMS

voltage VLrms and ILrms. Measure the input current from the power supplies. Calculate

the efficiency of the inverter.

90

EXPERIMENT 9. SINGLE PHASE INVERTERS

Vary the duty cycle of PWM waveform (the duty cycle of 50 Hz gate signal is 50 %, do not

change) and measure the RMS load voltage at different duty cycle and sketch the trend.

Vary the switching frequency and observe the effect over spectrum of load current and

voltage waveform.

9.2

Full Bridge Inverter

Circuit diagram of the full bridge inverter circuit is shown in the Figure 9.3. When T1 and T2

are turned ON, the input voltage Vd appears across the load. If T3 and T4 are turned ON, the

voltage across the load is Vd . Table 9.1 shows the main principle of a single phase full bridge

inverter.

Figure 9.3: Single phase full bridge inverter

Figure 9.4: Single phase switching sequences

Tasks

Setup the full bridge circuit circuit as shown in Figure 9.3. Use Two IR2104/IR2103 Gate

Driver IC for complimentary switching of T1 ,T4 and T3 ,T2 . Use RL = 5 10 and an

9.3. SINOSOIDAL PWM FOR SINGLE PHASE INVERTER

91

appropriate value of Inductance (in the range 300 H). Generate gate pulses for square

wave 50 Hz operation. Insert a small resistance in range of 0.1 in series with load to

observe the current waveform in terms of voltage. Set input voltage equal to 30V and

supply current limit to 2 A.

Set a duty cycle of 50%. Observe the load voltage and current waveform ans save for your

report. Also record the RMS voltage VLrms and ILrms. Measure the input current from

the power supplies. Calculate the efficiency of the inverter.

Generate a switching waveform of frequency 10 kHz with variable duty cycle and perform

AND operation with previously generated 50 Hz 50 @ 50% duty cycle waveform. Observe

the load voltage and current waveform ans save for your report. Also record the RMS

voltage VLrms and ILrms. Measure the input current from the power supplies. Calculate

the efficiency of the inverter.

Design the value of series resonance filter capacitor Cf to obtain a resonance frequency

equal to the switching frequency of 10 kHz. This capacitor is to be connected in series

with the inductor L.

Obtain the waveform across the load resistor RL with capacitor Cf connected. Observe

the load voltage and current waveform ans save for your report. Also record the RMS

voltage VLrms and ILrms. Measure the input current from the power supplies. Calculate

the efficiency of the inverter.

Vary the duty cycle of PWM waveform (the duty cycle of 50 Hz gate signal is 50 %, do not

change) and measure the RMS load voltage at different duty cycle and sketch the trend.

Vary the switching frequency and observe the effect over spectrum of load current and

voltage waveform.

9.3

Sinosoidal PWM for single phase inverter

You can get extra/bonus credit if you implement sinusoidal PWM for single phase inverter.

Check the end notes.

Two bonus marks for running all the inverter circuits such that you have 220 Vrms output.

Use a 100 Watt bulb as a load.

This manual is to be completed in two lab sessions before 2nd December 2016

92

EXPERIMENT 9. SINGLE PHASE INVERTERS

9.3. SINOSOIDAL PWM FOR SINGLE PHASE INVERTER

93

94

EXPERIMENT 9. SINGLE PHASE INVERTERS

You might also like

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Lab 8 Single Phase InvertersDocument8 pagesLab 8 Single Phase InvertersM Hassan BashirNo ratings yet

- Lab Manual 8 Inverters PDFDocument8 pagesLab Manual 8 Inverters PDFMuhammad AbubakarNo ratings yet

- Question BankDocument11 pagesQuestion BankRohini MukunthanNo ratings yet

- EES612 Lab2Document19 pagesEES612 Lab2kombat13_708353334No ratings yet

- بور الكترونيكDocument20 pagesبور الكترونيكawabNo ratings yet

- PE AssignmentsDocument11 pagesPE AssignmentsVinayaniv YanivNo ratings yet

- DC-DC Converter: Four Switches V V 2, Capacitive Turn-Off Snubbing, ZV Turn-OnDocument10 pagesDC-DC Converter: Four Switches V V 2, Capacitive Turn-Off Snubbing, ZV Turn-OnRomitan AlexandraNo ratings yet

- Comparison and Simulation of Full Bridge and LCL-T Buck DC-DC Converter SystemsDocument5 pagesComparison and Simulation of Full Bridge and LCL-T Buck DC-DC Converter SystemsKrishnaveni Subramani SNo ratings yet

- Ee6701 Hve Eee Viist Au Unit IIIDocument13 pagesEe6701 Hve Eee Viist Au Unit IIIsyailendraNo ratings yet

- Pe Unit 5 PDFDocument8 pagesPe Unit 5 PDFmjrsudhakarNo ratings yet

- DC-DC Converters Lab ManualDocument32 pagesDC-DC Converters Lab ManualShah SahadNo ratings yet

- Power Electronics 102409025108 1Document7 pagesPower Electronics 102409025108 1sushil4056No ratings yet

- ZvsDocument29 pagesZvsSandy RonaldoNo ratings yet

- Phase-Controlled Converters: Unit IiDocument29 pagesPhase-Controlled Converters: Unit IiChinnaGurappaNo ratings yet

- Theory of Switched Mode Power SupplyDocument21 pagesTheory of Switched Mode Power Supplyseahate100% (1)

- Full-Wave Rectifier PDFDocument3 pagesFull-Wave Rectifier PDFRitik kumarNo ratings yet

- UNIT 3&4 DC - AC Switched Mode Inverters: ApplicationsDocument37 pagesUNIT 3&4 DC - AC Switched Mode Inverters: Applicationsdivya k sNo ratings yet

- Zero Voltage Switching Resonant Power Devices by Bill AndrecakDocument28 pagesZero Voltage Switching Resonant Power Devices by Bill AndrecakRekhamtrNo ratings yet

- Basic Switching CircuitsDocument19 pagesBasic Switching Circuitsash1968No ratings yet

- UNIT-II Transformers & Alternator-2marksDocument5 pagesUNIT-II Transformers & Alternator-2marksashwen30No ratings yet

- Dire Dawa University: Institute of TechnologyDocument49 pagesDire Dawa University: Institute of TechnologyAsed ZakirNo ratings yet

- IE Mod 01 PowerSupplyDocument25 pagesIE Mod 01 PowerSupplyRy AnNo ratings yet

- Qpaper 2019Document4 pagesQpaper 2019OmkarNo ratings yet

- ZVSDocument28 pagesZVS12BACAUNo ratings yet

- ELEC3105 Lab4Document10 pagesELEC3105 Lab4James AllenNo ratings yet

- Voltage-Source Active Power Filter Based On Multilevel Converter and Ultracapacitor DC LinkDocument9 pagesVoltage-Source Active Power Filter Based On Multilevel Converter and Ultracapacitor DC LinkhdinhhienNo ratings yet

- Comparison Between FLC and MMC IECON2009 1 PDFDocument6 pagesComparison Between FLC and MMC IECON2009 1 PDFAamir YousufNo ratings yet

- AC DC ConvertersDocument11 pagesAC DC ConvertersMoon BorahNo ratings yet

- Ece Vii Power Electronics (10ec73) AssignmentDocument6 pagesEce Vii Power Electronics (10ec73) AssignmentThomas PriceNo ratings yet

- CUK ConverterDocument4 pagesCUK Converterranjitheee1292No ratings yet

- Resonant DC Link InvertersDocument6 pagesResonant DC Link InvertersSanchit AgarwalNo ratings yet

- EEE Lab ManualDocument26 pagesEEE Lab ManualPrabin RoyNo ratings yet

- Pe Course File 9 198Document190 pagesPe Course File 9 198Dr ADITYA VORANo ratings yet

- Conv DC-DC Paper ENglishDocument5 pagesConv DC-DC Paper ENglishpepe890305No ratings yet

- ECT 246 Week 1 IlabDocument17 pagesECT 246 Week 1 IlabKrystle HaleyNo ratings yet

- Exercises On Transformer (Chapter-3)Document3 pagesExercises On Transformer (Chapter-3)koxabey137No ratings yet

- Pe 2019Document2 pagesPe 2019Aniruddh AndeNo ratings yet

- PWM Inverters With Common DC-DC Converter Supply: Stepped Wave Synthesis From Pre-ProgrammedDocument7 pagesPWM Inverters With Common DC-DC Converter Supply: Stepped Wave Synthesis From Pre-ProgrammedSumit HarwaniNo ratings yet

- Chapter Two: Ac-Dc Conversion: Uncontroled RectificationsDocument53 pagesChapter Two: Ac-Dc Conversion: Uncontroled Rectificationsfor life100% (3)

- Lab #2 CNET219: ObjectivesDocument7 pagesLab #2 CNET219: Objectivesliam butlerNo ratings yet

- 9 Basic DC To DC Converter CircuitsDocument40 pages9 Basic DC To DC Converter Circuitsuser123phc100% (1)

- Power Electronics - 102409025108 - 1Document7 pagesPower Electronics - 102409025108 - 1Herbert DeepakNo ratings yet

- Experiment 1.: Aim: Determination of Transformer Equivalent Circuit From Open Circuit TheoryDocument7 pagesExperiment 1.: Aim: Determination of Transformer Equivalent Circuit From Open Circuit TheorySur ShriNo ratings yet

- DC DC ConverterDocument2 pagesDC DC ConverterMahmoud A. AboulhasanNo ratings yet

- Basic DC To DCDocument36 pagesBasic DC To DCstrelectronicsNo ratings yet

- CyclocovertersDocument4 pagesCyclocovertersAlfredNo ratings yet

- Bhwna Unit 5Document9 pagesBhwna Unit 5Pradeep KumarNo ratings yet

- HW 1 SolutionsDocument6 pagesHW 1 Solutionsmitrax1pNo ratings yet

- Implementation of Single Stage Three Level Power Factor Correction AC-DC Converter With Phase Shift ModulationDocument6 pagesImplementation of Single Stage Three Level Power Factor Correction AC-DC Converter With Phase Shift ModulationseventhsensegroupNo ratings yet

- International Journal of Engineering Research and DevelopmentDocument7 pagesInternational Journal of Engineering Research and DevelopmentIJERDNo ratings yet

- AssignmentDocument1 pageAssignmentrupamandalNo ratings yet

- With and Without Var CompensationDocument6 pagesWith and Without Var CompensationAdeniji OlusegunNo ratings yet

- One-Quadrant Switched-Mode Power Converters: R. PetrocelliDocument26 pagesOne-Quadrant Switched-Mode Power Converters: R. PetrocelliClaudiu UdrescuNo ratings yet

- Modelling and Control of A Flying-Capacitor Inverter: AbstractDocument9 pagesModelling and Control of A Flying-Capacitor Inverter: AbstractMariem KammounNo ratings yet

- A Is (Facts) (SVG) ,: AbstractDocument9 pagesA Is (Facts) (SVG) ,: AbstractSherif M. DabourNo ratings yet

- Transformer - NT PDFDocument108 pagesTransformer - NT PDFReshab Sahoo100% (1)

- PEC Lecture Slide Inverter TurkceDocument43 pagesPEC Lecture Slide Inverter Turkcemdur67No ratings yet

- Physics Lab - Rectification and Smoothing of An A.C. VoltageDocument8 pagesPhysics Lab - Rectification and Smoothing of An A.C. Voltageaben100% (1)

- Pendulum Periods and Gravitational AccelerationDocument11 pagesPendulum Periods and Gravitational AccelerationAmeerMuaviaNo ratings yet

- Chapter One 1.1 Background of The StudyDocument43 pagesChapter One 1.1 Background of The StudyAmeerMuaviaNo ratings yet

- Pendulum Periods and Gravitational AccelerationDocument10 pagesPendulum Periods and Gravitational AccelerationAmeerMuaviaNo ratings yet

- I Ntervi Ewquesti Ons (Techni Cal)Document7 pagesI Ntervi Ewquesti Ons (Techni Cal)AmeerMuaviaNo ratings yet

- Noise Factor of Active and Passive Networks: Student NameDocument28 pagesNoise Factor of Active and Passive Networks: Student NameAmeerMuaviaNo ratings yet

- Output PDFDocument2 pagesOutput PDFAmeerMuaviaNo ratings yet

- Velocity Time Graph For Second WeightDocument2 pagesVelocity Time Graph For Second WeightAmeerMuaviaNo ratings yet

- Beckman Coulter Ac.T DiffDocument1 pageBeckman Coulter Ac.T DiffBasharatNo ratings yet

- Communications II Lecture 4: E Ffects of Noise On AMDocument36 pagesCommunications II Lecture 4: E Ffects of Noise On AMAmeerMuaviaNo ratings yet

- Material Selection Assignment: Learning Outcomes To Be AssessedDocument3 pagesMaterial Selection Assignment: Learning Outcomes To Be AssessedAmeerMuavia100% (1)

- Roots of Quadratic Equation: MATLAB Script FileDocument3 pagesRoots of Quadratic Equation: MATLAB Script FileAmeerMuaviaNo ratings yet

- BJT Differential Amplifier: Circuit SensorDocument9 pagesBJT Differential Amplifier: Circuit SensorAmeerMuaviaNo ratings yet

- Constructing Program in MATLAB: 1.1. MATLAB As A CalculatorDocument12 pagesConstructing Program in MATLAB: 1.1. MATLAB As A CalculatorAmeerMuaviaNo ratings yet

- Part (A)Document15 pagesPart (A)AmeerMuaviaNo ratings yet

- PLL FM DemodulationDocument2 pagesPLL FM DemodulationAmeerMuaviaNo ratings yet

- Iterative Algorithm: 5.1. For A 2Document2 pagesIterative Algorithm: 5.1. For A 2AmeerMuaviaNo ratings yet

- Application & Challan FormDocument5 pagesApplication & Challan FormAmeerMuaviaNo ratings yet

- PES Technical Report Template Jan 2016Document2 pagesPES Technical Report Template Jan 2016AmeerMuaviaNo ratings yet

- Arduino, Gyroscope and ProcessingDocument12 pagesArduino, Gyroscope and Processingmihret henokNo ratings yet

- Electronics - Q3 - Week4-5 - Inductors - Answer SheetDocument2 pagesElectronics - Q3 - Week4-5 - Inductors - Answer SheetMelissa Gagujas0% (1)

- Kalkulimi Për NXDocument6 pagesKalkulimi Për NXGazmend NixhaNo ratings yet

- 11kv Voltage RegulatorDocument4 pages11kv Voltage RegulatorEkhlas SayeedNo ratings yet

- 1MRK505188-BEN B en BuyerAs Guide Line Differential Protection IED RED 670 Pre-Config 1.1Document56 pages1MRK505188-BEN B en BuyerAs Guide Line Differential Protection IED RED 670 Pre-Config 1.1Anonymous BBX2E87aHNo ratings yet

- 88-02 Cummins Exhaust BrakeDocument24 pages88-02 Cummins Exhaust Brakemark_dayNo ratings yet

- 1SBC100208C0203 - Catalogue AF Safety ContactorsDocument46 pages1SBC100208C0203 - Catalogue AF Safety ContactorsDulce Martinez TolentinoNo ratings yet

- SuprA Company Profile (2019)Document28 pagesSuprA Company Profile (2019)dedison_rNo ratings yet

- Pasha Hawaii Guide - Preparing Your Vehicle ShipmentDocument3 pagesPasha Hawaii Guide - Preparing Your Vehicle ShipmentUmrbek NazarovNo ratings yet

- Dell E152Fpb LCD Monitor RepairDocument3 pagesDell E152Fpb LCD Monitor RepairMicheal speedNo ratings yet

- Fabrication of Plant Irrigation Water Sprinkler PDFDocument10 pagesFabrication of Plant Irrigation Water Sprinkler PDFSanjayNo ratings yet

- P1.3.R02 LBG Linear Bar Grille.A4Document6 pagesP1.3.R02 LBG Linear Bar Grille.A4ekahNo ratings yet

- CRITICAL PARTS LIST OF GENERATING SET 80KVA CATERPILLARDocument3 pagesCRITICAL PARTS LIST OF GENERATING SET 80KVA CATERPILLARamonNo ratings yet

- Kamn40 Series: Model ListDocument4 pagesKamn40 Series: Model ListkasiiiiiNo ratings yet

- Manual Caterpillar d6t Track Type Tractor Operation Cab Monitoring System Engine Power Train Implement HydraulicsDocument178 pagesManual Caterpillar d6t Track Type Tractor Operation Cab Monitoring System Engine Power Train Implement HydraulicsRoussel Florez Zuloaga100% (11)

- Government of Uttar PradeshDocument1 pageGovernment of Uttar PradeshAkhand SinghNo ratings yet

- MCQs - EAM - Unit 5Document10 pagesMCQs - EAM - Unit 5Sayee DeshpandeNo ratings yet

- Inverter Buying GuideDocument9 pagesInverter Buying GuideGanesh BabuNo ratings yet

- 09 - Car Seat Design (Ver.1)Document55 pages09 - Car Seat Design (Ver.1)deliNo ratings yet

- Pt. Rahmi Ida Nusantara: Sumbagut-2 Peaker Power Plant (Electrical)Document20 pagesPt. Rahmi Ida Nusantara: Sumbagut-2 Peaker Power Plant (Electrical)Andri WahyudiNo ratings yet

- NuMicro Nano100 (B) Series Product Brief en V1.00Document72 pagesNuMicro Nano100 (B) Series Product Brief en V1.00HanhoaiNguyenNo ratings yet

- From 1660 To 5100 kVA: Medium Voltage Inverter Station, Customized Up To 5.1 MvaDocument4 pagesFrom 1660 To 5100 kVA: Medium Voltage Inverter Station, Customized Up To 5.1 MvaPhelipe LealNo ratings yet

- Experiment 7Document4 pagesExperiment 7Swaroop MallickNo ratings yet

- Material - Tech - High Impedance Differential Protection - 757208 - ENaDocument22 pagesMaterial - Tech - High Impedance Differential Protection - 757208 - ENaThet ThetNo ratings yet

- Instruction Manual: Turbo Instrument Controller (TIC)Document64 pagesInstruction Manual: Turbo Instrument Controller (TIC)E.LenaNo ratings yet

- 394 Seminar Mai 2004GBDocument154 pages394 Seminar Mai 2004GBMartinez Andryj100% (1)

- Experiment 07Document3 pagesExperiment 07Harsh KalamNo ratings yet

- DR-UPS40: 40A DC UPS ModuleDocument3 pagesDR-UPS40: 40A DC UPS ModuleadrianioantomaNo ratings yet

- MC-10164446-0001 LineartronicDocument6 pagesMC-10164446-0001 LineartronicossoskiNo ratings yet

- U33 ThermaV - Split (R410A - 50Hz) (April.2020)Document87 pagesU33 ThermaV - Split (R410A - 50Hz) (April.2020)Vent system СервисNo ratings yet