Professional Documents

Culture Documents

Ssi Book Images PDF

Uploaded by

Shruthi Ravishankar0 ratings0% found this document useful (0 votes)

46 views538 pagesOriginal Title

ssi book images.pdf

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

46 views538 pagesSsi Book Images PDF

Uploaded by

Shruthi RavishankarCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 538

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

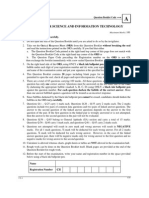

494 Chapter ¥

Bae eo tect cases tobe ued nc, ndix A

with the test driver you outlines ae ae ONE O Source tng Ape! 7

9. Wit 3 te Acvess_symtab to'be used in the top-dawn testing of S| XE Instruction

he modular structure in Figs, 8.10 and 8.11, mee i

10. Write a stub for P_read_source to be used in the top-down tes Set and Addressing

the modular structure in Figs. 8.10 and 6.11 ee

1. Write stubs for the methods of the object Opeode table (see Figs. 614 Modes

and 8.15) he

. Write stubs for the methods of

and 8.15).

the object Source line (see Figs. § 14

instruction Set

"inthe following descriptions,

) Bia sn indicates a memory: ae

| (qand rl and r2 represent ey

| ihecontents of a register or memory loc

ee of the memory locations

+2 (A) specifies that the contents

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

Appendix A SIC Inst

Mnemonic

ADD m

ADDF m

ADDR r1,r2

AND m

CLEAR ri

COMP m

COMPF m

COMPR 11,12

DIV m

DIVF m

DIVR rlr2

Format

3/4

3/4

3/4

nm

Opcade

18

58

90

2225

(Beeeeeenezacat2s

Effect

Ae (A) +

FE & (F) + (m.m+5) ee

2 & (12) + (rl) A

A 1A) & (m..m42)

reo ¢

(A): (m.m42) c

(F): (m..m+5) xre

(rl): (2) ae

Ae (A) / (m.m42)

Fe (F) / (m.m45) XE

re (r2) / (rl) NG

A<(F) [convertto integer] «XE

F<(A) [convert tofloating] — XF

Halt 1/O channel number (A) TX

rPcem

PC <— mif CC setto=

PC — mif CC set to>

PC e mif CC setlo<

Le (ro; Poem

Ae (m.m+2)

Be (m.m2)

A Erigtonet byte) (9

Fe (m.mt5)

Le (mm)

Opcode

60

9B

ca

44

DB

AC

4c

Ad

Effect

-® +5)

2. (12) * (rl) x

F< (F) [normalized] XF

A& (A) | (m2)

Alrightmost byte] dala P

roar ae specified by (m)

2 (rl)

PC (L)

rl < (rl); left circular shift

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

= AGATE, ee

ates column have the following meanings:

Mnemonic

Format Opcode —_ Effect patersin ine

SUBR 11,12 2 94 n “te a

SVE n 4 2+ (12)~(1) x Format 4 TE

B Ger ee

0 ae ie SVC interrupt, {in x = Direct-addressing: instruction,

fe. ie ns ted instruction, r1 =n] ‘assembler selects either program-counter relative or base-relative

= ED Test device specified byim) pg B ipod chine,

1 FB Test 1/Ochannel number (A) px i Compatible with instruction format for standard SIC machi

et) oh es ae é s erand value can be between Qand 32,767 (see Section 1.3.2 for

TIXR 1 z Be X— O41; OO: (A) xc a

WD m 3/4 pe Device specified by (m) — (A) P eguge ofl

ETE Gye| ssing Flag bits language of target

oe nixbpe notation address TA

Instruction Formats pane Pee aes

110001 +op™

ti0010 «opm — (PC) + disp

110100 opm (8) +disp

111000 op X

111001 top mX

111010 op mX

1i1ioo

p00. - -

po1---

00000

Format 1 (1 byte):

&

Format 2 (2 bytes):

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

Po

am

SSSRSe |B

gesese

EIX

BOT

ENQ

ACK

BEL

BS.

Hr

att

VT

FF

cR

50

bai

DCE

BS

Bee SRRERERSESEREES

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

a

appeNndIx i;

gic/XE Referen

waterial s

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

Appendix SIC/XE Re

Format

SVC Codes cponmel command

Contents

Code Mnemonic _ Register parameter pupae

tu Command code (see below)

ae 4

0 WAIT (A) = address of ESB for event * Device code:

is 1 SIGNAL (A) = address of ESB for event a Number of bytes to transfer

ai

lo ned

Memory address for start of data tra

a = address of FSB for 1/Q operation

REQUEST (1) = address of resource name

RELEASE (7) = address of resource name

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

ion supervisor. Talso want to Contents

Pat Brown, Julie Dunn, and |

A Lith

in her role as PTO

enany others, inclucting,

argya, Bill Morris, Ron

Sind reference material

Ashford, John Carroll, Sushant G

th Sean teal puevious versions of Chapter? Background ;

ted to the ;

sided many valuable suggestion LLB 11 Introduction 1

San Diego, California 1,2 System Software and Machine Architecture 3

1.3 The Simplified Instructional Computer (SIC) 4

13.1 SIC Machine Architecture 5

1.3.2 SIC/XE Machine Architecture 7

13.3 SIC Programming Examples 12

1.4 Traditional (CISC) Machines 21

14.1 VAX Architecture 21

14.2 Pentium Pro Architecture 25

1.5 RISC Machines 29

1.5.1 UltraSPARC Architecture 29

1.5.2 PowerPC Architecture 33.

1.5.3 Cray T3E Architecture 37

Exercises 40

Chapter2 Assemblers

2.1 Basic Assembler Functions 44

. 211 ASimpleSIC Assembler 46

2.1.2

a2

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

253 AIX Assembler 108

Exercises 111

3 Loaders and Linkers

Basic Loader Functions 124

341 Design ofan Absolute Loader 124

31.2 ASimple Bootstrap Loader 127

‘Machine-Dependent Loader Features 129

Relocation 130

Program Linking 134 ae

‘Algorithon and Data Structures fora Linking Loader 141

i Independent Loader Features 147

‘Automatic Library Search 147

Loader Options 149

175

181

ELENA Macro Processor 213

Chapter5 Compilers seg

5.1

5.2

54

He

61

Exercises 318

Chapter 6 _ Operating Systems

Basic Compiler Functions 225

51.1 Grammars 227

5.1.2 Lexical Analysis 231

5.1.3 Syntactic Analysis 242

514 CodeGeneration 260

Machined Dependent Compiler Features 272

Intermediate Form ofthe Program 272

Machine-Dependent Code Optimization 274

Ffschineindependel Compiler Features 278

5.3.1 Structured Variables 279

5.32 Machine-Independent Code Optimization 284

5.4.3 Storage Allocation 289

534 Block-Structured Languages 294

Compiler Design Options 299

54.1 Division into Passes 299

542 Interpreters 301

54.3 P-Code Compilers 302

544 Compiler-Compilers 304

Implementation Examples 305

5.5.1 SunOSC Compiler 305

55.2 GNU NYU Ada Translator 308

5.5.3 Cray MPP FORTRAN Compiler a0

554 JavaCompilerand Environment 313

55.5 The YACC Compiler-Compil

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

tof Virtual Memory 361

625 Managemen! ‘vals of System Specifications 453

i tem Features 372

‘Machine-Independent Operating Sys Types of Specifications 454 4

63.1 File Processing ee g ror Conditions 458 4

63.2 ee at eation = 83 m Design 459

i eaten oe Data Flow Diagrams 459

3. ee eae Ae General Principles of Modular Design 465

erating System Design Op! at Partitioning the Data Flow Diagram 466

es : Module Interfaces 470

Machines i

rtual N 2 84 Object-Oriented System Design 474

i fems 392 sales i

1 eee He 84.1 — Principles of Object-Oriented Programming 475

pectic eS ee Systems 298 8.4.2 Object-Oriented Design ofan Assembler 478

Iperating. 85 System Testing Strategies 485

8.5.1 Levels of Testing 485

8.5.2 Bottom-Up Testing 486

85.3 Top-Down Testing 489 :

Exercises 490)

Appendix B ASCII Character Codes

Appendix € SIC/XE Reference Material

References

Index

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

Leland L. Beck

eben eels

5

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

— ———————————————

System Software

An Introduction to

Systems Programming

Third Edition

Leland L. Beck

San Diego State University

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

To Marla and Kendra

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

Preface

suis text is an introduction to the design and implementation of various types Of sf

tem software. A central theme of the book is the relationship between machine architec-

te ind system softvvare. For exemple, the design of an assembler or an operaling

two is greatly influenced by the architecture of the machine on whieh ft runs These

qinuences are emphasized and demonstrated theough the discussion of actual pleces of

ystem software for a variety of real machines

* ‘However, there are also similarities between software for different systems, For ex-

ample, the basic structure and design of an assembler js essentially the same for most

Samplers, These fundamental machine-independent asperts of software design are

Clearly identified and separated from machine-specific details

This third edition includes all new examples of machine architecture and solvers:

‘The principal computer architectures used as examples ar Pentium Pra (x86),

UitraSPARC, PowerPC, and Cray T3E, The text discusses assemblers, loaders, conpil-

crs, and operating systems for these machines, focusing on the relationship between

ere pine architecture and software dasign. There are also discussions of mUlipis= st

ia distributed opceating systems, and systems structured according 10 the client

server model,

This edition also includes an introduction to the principles of object-oriented pro

gramming and design. These concepts are i lustrated by considering an

design for an assenibler. There are also examples of object-oriented operatiny

and brief discussions of the Java language, compiler, and rurvtime environment,

‘Anumber of other new topics have been added in the third edition. Far ex

the introductory chapter contains @ brief discussion of RISC architectures, T

‘on compilers includes new material on finite automata and shift-reduce

revisions and clarifications have been made throughout the test, and |

than 40 new exercises.

“This book is intended primarily for use as a tex!

Jevel course in system software or systems

reference or for independent study: The reader is

sembler language for at least one machine and ¥) the

instructions and data within a computer (for ex:

and I's and. 2's complement representation ol i

the reader is |

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

and characteristics should remain css

teaching: ‘pasic assembler functions a Beh

Bese reeeraliss ‘of what machine is being used. This gives the stu

Gear een tobegin the desion of an assembler for a ew or unfamtia

“Sachin Section 9.2 discusses machine-dependent extensions to the basic stru

in Sectio r emphasize the relationship between machine ar-

fed in Section 2 tis (oe*e* 4 implementation, Section 23 introduces a number

and Section 2.4 discusses some important

ves the assembler. These features and alternatives

Brey Ete cetrons they are choices made by the software di

‘such ateas, Here is no one “right” way of downs things: a software design

ie aware of the available options in order to make intelligent decisions bi

Finally, Section 2.5 discusses examples of actual assemblers for a variety

€ This provides an illustration of both machine-dependent ancl ma-

nt vatiations that reinforces the points made in previous sections of

re and assembler design and implem

chine-independent assembler features,

J approach is followed in discussing loaders and linkers (Chapter

ors (Chapter 4), compilers (Chapter 5). and operating systems

; basic features of each type of software are described first, followed by

endent and machine-independent extensions to the basic

are then discussed and examples of actual pieces of solt-

varies considerably fram one chapter to another. Chapters

ete discussions of assemblers, linkers and loaders, and macro

details, such as algorithms and data structures, are also in-

‘be able to write a working assembler, loader, or macro

upplied by the text. (Istrongly recommend that such a pro-

‘on this book.)

r hand, deal with the much larger subjects of compil-

‘of these topics has, by itself, been the subject of many

to fully discuss either one in a single chapter.

‘brief-but-not-superficial overview of compilers

rand fundamental concepts of these types of

with examples. More advanced topics are men-

r the reader who wishes to explore these areas fur-

: ation details have been omitted. A

discusses database management sys-

re engineering concepts and tech-

the full scope of software engineering

t useful in designing and

assembler. Both procedural and

‘chapter is to provide the stu-

| ise in a software project based

iE endent of the rest of

er the introduction to assemblers in

a

of the questions are open:

Many of the exercises require

the text, extending: them to new situ

n problems that have no one “right answen!!

to apply concepts that have been covered in

ons. This ensures that the reader fully under=

stands the principles involved and is able to put them into actual practice: have pur-

posely riot included answers to the exercises because I believe that a set of answers

would have the effect of stifling thought and creativity rather than stimulating it.

This book contains more material than can usually be covered in a one-semester

course. This allows the instructor to place a varying degree of emphasis on different

topics to suit the needs of a specific curriculum. For example, if students will later take

a course that deals solely with operating systems, the instructor may wish to omit

Chap 6 remaining chapters include enough material for a typical one-semester

course, Other instructors may prefer to caver al a iminati

some of the more advanced acts see

One issue that deserves comment is the use of a hypothetical

structional purposes. I have used the hypotheti 1 aetin pacinilp Suet

the problem of dealing with the irrelevant compleaities and “quirks” found on most

real computers. It also clearly separates the fundamental concepts of a Piece of software

from implementation details associated with a particular computer. Ifa real machine is

used in teaching, students are often unsure about which software characteristics are

le fundamental and which are simply consequences of the particular machine used

in the text.

A secondary benefit to using a hypothetical machine is that i

equal footing. No student is at an inte disadvantage because ns ' ene

unfamiliar with the hardware and software system on which the text is ae Thave

found this to be particularly important in my: courses, which tend to attract students

mnatare had experience ona variety of computers.

‘nally, it should be noted that some of the original reviewers of this text we

tially skeptical about SIC, bi ir opini seeing, raed

et Be a ut changed their opinion after how it could be used

OF course, students in a course of this type need to b i

grams for the machine being studied. A SIC eauise ea i Se aG Geen

available for this purpose. This software enables students to develop and run progra

as though they actually had access to a SIC machine, Itis Rot necessary to use an

Heular real computer—the simulator and assembler can be run on almost any

ing system that supports Pascal, The SIC support software is available by i

oe rohan sdstnedu, in the file faculty /beck /SystemSoftware.tar.

ome fieeie given their time and energy to help make this a

a Pt for this third edition was reviewed by Donald Gus

Unigene oral E. Merusi, The Hartford Graduate Center, Jo

essee at Chattanooga, Thomas W. ‘Ohi

in finding errors and other problems in the

Errors whi i

Which remain are, of caurse, entirely my. serene

“fone 4 t2.ihy fester for pointing out such errors, lease sen

ti aatteat beck. ed,

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

‘8259-Q00N3A

ost 1430

ME SYEHLHOS HUSAS-TUUL

e yoae-HOHINY

quo1syoo8 SNAKVI-NO YNOA 1 p/22/1

Aussopmor mE mmany-dny

coils 42M 2PM PHO m0 wo syoog Aa]saq,-UosIppy moqe UOTEULIOJUT ISA] I SsoDay

-Aaysam-UosIppy Woy ang] papiny Y *[9sd JO

rope ayy osye St 9799q Id “Suueautdua aremyos pue ‘suiaisds Suneiado “Aqun3as Jaynduros

apnput sjsarayur yoreasal STE] -Aisraatup ISIpoUpa|W WsyINOS Wo a2ue—s saynduio2 pue

Sunzaaursua suraysAs UT “Ud PUe ’S'IAL ST PU ‘AsranTap) any Woy sashyd /soyeurayyeUt

ur-y'g sty peaezal pag Id ‘Aystaatup) ayers o8aiq ues 12 urerZ01d aoueps rayndurea

ayy Jo 1OJeUTPIOOD ay) Pure SadUaDs [EITEUISTAEUT JO aossajoid e st pag “] puepey

JoyynY ayy Noqy

‘aAo9 0} yueM TOA yeyQ saMyDayTYDIe.

pure aremyjos ayy UO ayeTUSIUOD OF nok Surmorye “GTIqEey se yjem se jzoddns

Sumpeay Surptaoad ‘sasiosaxa pur sojdurexa Jo uonsa]as apiM & SUTETUOD «

surays(s Jansas /quaTp pure ‘pamnqiystp ‘1osseoorxdyjnur se yons ‘sordoy suraysAs

Suyesado juarmo Surpnput Aq Aysmput yy paads-oj-dn yooq aug ssuLig «

“suiaysAs Suyesado pue

‘szapiduio3 ‘sa8enSury] payuaro-jalqo yo sajdurexa YL sydanuo2 asay} sayeqsnyy

pue ‘uStsap pue SurumuesSoid payuatio-alqo oj uoyINpoaUT ue SapnPUuy «

‘qe Aeip pue ‘Oyvds uns ‘Ddiemog Wal “Caja ‘og “wmuag) Ayrurey

ggx Jaquy at Surpnput ‘sajdurexa aremyjos pur ainyoaytypre payepdn saplao1d «

sainjyea.y MON,

‘aremyos utaysAs [env Jo saydurexa saat’ pur “s}daauoo s1seq ayy 0} suoTsUayxe Juapuadapul

-2uypew pur juapuadap-aurypeum yjoq sassnosip ayy ap] ‘AeM quepuedapur-aunypeut

2 ur aremyos jo ad4q Upea Jo uSISap o1seq pue s}dazu0 [eyUeWepuNy ay sJuasard ysxy

ypag ‘Hoddns 0) pauZisap st} auTyDeUT ayy Jo aINyayTYyDIe ay pue aremyos wiaysds waaM\jaq,

drysuoyeyjar ayy Suissayjs ‘aremqos waysis jo sad‘q snouea jo uopeyuauaydun pue usisap

au 0} UOQINpoyut ayapdurod ve sapraomd yoeq pues] ‘ayy Jsse[d sty Jo UOQTpa pang snp uy

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

references

man, Jeffrey D., Compilers: Principles, Techniques, aid Toots,

Reading, Mass, 1988.

Processor System

fri, Ravi andl UT

Architecture (2nd edition), Addisons

ey Pubeshun CO. ‘

a Hens CTE James, The fava Programing Lamgien ‘Addison-Wesley Publishing Co.

Mai 1988:

vANerd Assent

chile, NI. 192.

Nabaiyotl.

jeuiaropolis, 1992.

Serre Elena ned Pelacant Gianluca, “A Software Development Syste

Mscruprocessan.” Suffice: Practice and Experwnce 14 519-531, June 1964. t

IGP. rani Ata 95, Adlon Wesley Publis 8

“que BL, “Software EngineesiNze Iiformation Processing 72, North-Hlland

x

97

rie George Mortis, Mary ©. $. ame Slattery, Kathy Ser fn

"Sungoft Press, Mountain View, Ca 1993-

‘Grady Object-Oriented Analysis nnd Desig wilt APPIN

tig Cx, Redwood City, Ca, 1994.

ck, The Mythicnd Mantel: Essays cm Fi

Poblishing Co. Reading, Mass 1995) Piel

“Macro Processors wind Teclmiques for Poriable:

ingunge Programming 2a eiion), Pretce Hal ne Englewood

he Write Grou soft Macro Assembler Bible (2nd edition), HWS

=e

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

-

TBM Corporation, “AL

a ‘AIX Assembler Languags , f 9 -

= anguage Reference fe sete GNAT Project’ A GNU-Ada 9% Compiler”

oe Ste 10112-1950, Standard Glessory of Softnne Pree “i

J peering Th 157 iiey 8

Intel Co: ” f neited DOS edition), Addison-Wesley Publishing Cou Reading.

| papeentee ‘A Tour of the Pentium(R) Pro Process ae ae

; /com//procs,/ p6/péwhite, 1995, 7 | Addison-Wesley Publishing Co, Reading,

Jensen, Kathleen and Wirth, Niklaus, PASCAL Use, ns of Pr

; : 1974, Jateractive Debug, Requirements," Proceedings of the ACH

eriner, Richard, “Integrating GNAT into GCC," Tri-Adla 94 Proceed rearing Sumnposiur ot Hig-Letel Cebu ge Mar 193 a

b LAN Notices, August 1983, pp. 9-22

[ath edition), H. W. Sams, Indianapolis, 1991

‘Advanced Concepts in Operating Systerss, MeGraw=

Kernighan, Brian W., and Ritchie, Dennis M., The € Programmi

Englewood Cliffs, N, J, 1975 ee

King, Adrian, Insiile Windows 95, Microsoft Press, Redmond, Wash, 1904

Knuth, Donald E., The Art of Computer Programming, Vol. 3: Sorting an Swarching, Ada

Publishing Co., Reading, Mass, 1973. pee)

er ‘A, Software Engineering: Plonning for Chmnge, Prentice-Hall, Englewood Clit, Xi}

Language, Prenticetyy

« Manual, Digital Press, Burlington, Missi, 1892.

PC 601 and Alpha 21064: A Tale of Twe RISCE

al,” 1984.

‘Landwehr, Carl E., Bull, Alan R., McDermott, John P, and Choi, William 8, “A Taxonony a gpARC Assembly Language Reference Mant

‘Computer Program Security Flaws,” ACM Corrputing Suirecys 26; 211-254, Sepiember 75 oo ase 1994b.

‘Lazzerini, Beatrice, Program i : r i wstemns, “C3.0.1 User's Guide, pre

ee Sealer, "The UllraSPARC Psocessor & Technology White Papen’

eye San ca: 0 sparc/ whitepapers /UltraSPARCtechnology 19253.

Si Microsystems, "The Java(im) Language Environment: A White Pay

Jjjvasincom hitePaper/javacwhitepaper-L em 3S:

“fer Mextsystems, "Sun Reference Mant 1995.

“Bok, Daniel, Afoenred Microprocessirs {2nd edition), MeGraw-Hill, Inc]

‘ ; i Wesley Pablisking ©,

Roe Virteat Machine, Addison Wesley Falling sys, Andrew $. Mistern Operating Systems, Prentice-Hall

Bee ee 2 in Ereyclopati of Sohort r ‘Andrew 5, van Renesse, Robbert, van Staveren, Hans, 5B

J), "Software Engineering, A Histories! Boretirer Sipe}, Jansen, Jack, and van Rossnm, Guido, “Experiences W

ting System,” Commirnientions of the ACM 33 5

ley é& Sons, Inc., New York, 1994. -

yan Dam, Andries, "Interactive Editing 5YS167= art LACH

Fara neil, rnterastive Eating Se" 1

16, September 1982.

yam Laboratories, LINEN Sustent W Relive 4: big

rt 17 Aci esers, Prentice-Ftall, Englewood Cliffs, NJ. 1992.

Prognrmeminng Language Processors: Conpiter

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

res

Gla Raceerelative ntdressinng, Direct muddressinlg,

alte testing, Jicenes advessing, In irecl adidress=

Dingren-cuuater relatioe addressing

p11

21,25, 34.35, 38

T3E

Assembler directives, 13, 44,48, 49,60

‘Assignment statement ES

code goneratian, 26-268

parsing 247, 259

syntax, 229-230, 247

Associative memory, 370

Asynchronaus, 133- .

Authorization, 385,465

Authorization lis, 333

Automatic allocation,

Automatic call, See At

Baseclass

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

Bootstrap loader, 127-129, 158-159

and control sections, 91-592

Bootstrapping of compiler, 303 =

in assembler language, 7577, 92

F ee Parsing, 243, 247, 260, 317 5 ss al 5 relative, See Relative expression

fom-up testing, 486-498, 490 she “5 See alsa aritlimetie expression

ce eaee See alignmestt intel EXTDEF, 65, 88

Bounds registers, 358 : ended i

F s ane: Extended instruction format (SIC)

> Breakpoint, 441, 444 es Uy, if 68, 8, 142 =i and linking 55

Buffer, 374, 375, 376 : ' ater ef definition of, 9

‘Buffering, 374 3 inl i use of, 56, 57, 59)

Button device, 433 Ci . hy 3, 3 Extended machine; 330, 331, 388,

BYTE, 13, 44, 48 External reference

and expressions, 91-92

Bytecode compiler, 302, 313 assembly of, 85-89 pares ‘noma reir 1

definition Pe te pais

C language, 203, 209-213, 293, 305-905 PEG aaa 5 poune iaeag ene

Bee eee a5, one linking ane Vading 84,5, 8, 905,119 sage B67 no cuahy inking of, 106, 135-140, 149, 155

Capability, 399, 412 : 1 Se interuphinibted suse of, 85 4

ity, 3 tse of, 83, 85. ied interrupt. See Intereupl ternal BS. See alsa |

Capability list, 385 Coupling, 465, 467-468, 470 Oe aa? ae ae Wed Ak

Catalog, 373-374, See also Directory CPU management. Se es He Sen ee

pence att Be Eee spt, HEA EXTRER, 85,88

‘Channel 5 ray. See fy ultzpmecess0%, i ‘

rose ia ; 5s sche “i

“in virtual machine, 392 (Cross-reference listing, 151 kesh Se Pes F Fectoe isolation, 468

‘SIG, 12 (CSECT, 85, See also Control section 19, Field 26

nici 57-9 Lali Gee ae oa ‘

. : structured language), 297+ aoe

Data abstraction, 468, 475 ‘spay {in bloc) “Fike manager, 373

Data dependence, 420, 421-422 tribated memory, 399 |

Data deterpticn, 424-127 JBttboted operating system, 328, 330, 395-397, 39%, 411- Fike pr

‘Data description 427 a

pees eeaee ns TW Soe Dole mvp elation langunge

Data eneryption, 397

Data flow diagram: ‘Themenintioe, 451, 452, 454, 464, 474

definition of, 452-460 Tepe vector, 283

partitioning ef, 466-470 Doile buffering, 376

refining of, 461-454 1 eon tion, 362, 364-266, 368, 372

Data independence, 422424 array

Data manipulation language, 428,429 Tyrac Heer 6 es

‘Data capping descnption, 422, 424, 427 ee 641

‘Data model, 425 fet, 3

Data redundancy, 419, 420421 ge allocation

Daa security 427. See aio Pla

165, 310,

Pantie, elusive cir) of 378350 38

ee ee se

Datab; 421

Prtabace aderinasrator $24,427 at

“Database management system. 41!

eeeryption, Preictate

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

‘Has-a relationship, 476

Hash table, 51,70

Header record, 48, 142

‘Heap, 294

Hierarchical structure, 288-389

1/0 channel, 344, 351-354. See also Chy

1/O configuration, 344

“L/O error, 330, 349-350

A/O request, 344-349, 351-351

A/O supervision, 329-330, 344-354

‘Ad. Soe Hientifier

lysis, 231, 239

Interpreter, 299, 301.

Interrupt, 331, 332-339

classe 4, 503

1/0, 334, coal

in virtual machine, 391

inhibited, 338, 339, 368

masked, 338-33

nested, 339

page fault. See Page fault

pending, 338

Priority of, 338-359

‘processing nf, 332-333, 934-397,

program, 333, 337, 365, S04

SVC, 333, 337

timer, 333-334

Interrupt handler. Sec Interrupl-processing wutine

Interrupt work area, 334-337

Interrupt-processing routine

concept of, 332-333, 34-337

1/0, 49-351, 4

fault, 368, 370

it af, 389

SVC, 351

timer, S41

Interval timer, 333, 334, 40, ML

[nvariant. See Loop invariant

stionship, 476

atte design far 465575

java, 304, 313-315

Fave ual Machine, 13314

Macro processor

stgorithe, 161-186, 193-194, 196, 201-20

data structures; 181-183

rors, 207

general-purpose, 202-208, 218-217

integrated, Z1H-206

tive by-line, 204-208, 206

pre-processor, 204-205, 209,211

Macro-time conditional, 189-184

Macro-time loop, 14-196:

Maero-time variable, 195; rpsn06. 218

Masked interri

MASM, 103-108, 208-207

Massively parallel p

‘Master-slave tulip

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

dynamic linking of, 156, 163164

invoking methods an, 398, 399, 412,

Object diagram, 480

‘Object manager, 399

Object program.

and control sections, 89

binary, 126

for one-pass assembler, 96-417

format of, 48-49

Joading of, 125

‘MASM, 105

MS-DOS, 160-161

_ SPARC, 106, 162

Object-oriented design, 398-399, 450, 474-485, 487, 458

. "identification of objects, 479-480

system, 395-399, 411-413

rogramming, 156, 308, 313, 314, 315, 398,

Performanc

Personal computer. 3

Mic Seay

Fipelining, 32,

PMT. See Page mu

Polymorphism, 478

Portability, 302, 313, 314

Positional parameter, 196, 197

POSEX, 406, 407, 409

PowerPC, 33-37

ackdressing modes, 35-26

assembler, 108-111

data formats, 34-35

input and output, 35-37

instruction formals, 33

instruction set, 36

memory, 33-4

ers, 34

Precedence, 231, 24-24

Precedence matrix, 244-246, 250

Precedence relation, 214-245, 246

ling, 344,351

342, 343, 344, 377, 408-405 407-48

Privileged instructions, 331,337,388, 387, 391

Procedural design, 459-474, $86,485

module interfaces, 470-474

ciples of, 465

sing data flow diagram, $6547)

Process, 339-100, 4b, 408, See also Theat

7,402. sora? secaiily

‘ing 104

ats Hock

nclire

re

a chine. Se F

ae Pg satis curd

es, 272-274

acca, 858

ws

9p,7, 119-30

READ AEM ia

fle ganeranon, 261

seen 127 7am, 252, 254-259

829

need fi

SunOS

with bit mask, 132-14

eith Medification record, 4,91, 194

Relocation bits, v2

Relocation register, 361, 302

Remote procedure call 399,412

Request (resource, 304-395

Requiroments aaljsis, M3450, 451

RESB, 13, 4,48

Reserved word) 237

Resource allocation: ‘See Resource

Resporce manage ae

Resource string, 995,235)

Response Tirhe, 328, 3783979)

RESW, 13, 41,45

RISC, 21, 29.31.32

ROM, Sec Reai-an

Rownd-robin

Row-major ord

Rule, 228-230

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

SIGNAL, 342, 343-344, 34

Silver bullet, 474

pee eresine. 0

yzle-job system, 327, 332, 339

S10, 12

SLR, 251

rene

vcrisis, 448

Software development. See Software engineering, Softusire

‘cycle, 449-452, See also Imptanentation,

5 is nnalysis, Sustem design, Sustem

Systeni testing

1-32.

and progam bloc

in assembler. 50, 51,57, 5

in compiler, 235, 253, 295,

in interprete

in ome-pass assembler, 9-96

Symmetric multiprocessing, 394-395, 405, 410

SYMTAB. See Syinbol tnbte

Syntactic analysis, 226, 202-240

Syntax, 235, 227

Syntax, tree. See Parse tree

System design, 450, 451, 433-454, 456

object-oriented, 450, 474-485

procedural, 450), 459-474

System software, 12,3

System spocification, 450,451, 452-459

‘and error conditions, 459-459

examples, 454-156, 457

gonls of, 53-451

types of, 44-457

System testing, 451, 454, 485-490

ottom-p, 456-498, 490

Jevels of, 485-485

registers, 22 seen

Virtual addeess space, 21-22,

virtual machine, 330, ‘390-392, 103-404

ive monitor, 390-592, AH

Virtual memory, 21-22: 25, 26, 30,34, 30

408

‘virtual resource, 361 ‘

a p-real mapping, 350 72 See

peslation +

ven See Viral mac mia

Voice-input devices’

wart 30,

wine

eee

‘WD, 7,19, 46

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

Chapter 1

Background

‘This chapter contains a variety of information that serves as background for

= the material presented later. Section 1.1 gives a brief introduction to system

software and an overview of the structure of this book, Section 1,2 begins a

discussion of the relationships between system software and machine architec-

ture, which continues throughout the text. Section 1.4 describes the Simplified

Instructional Computer (SIC) that is used to present fundamental software

concepts. Sections 1.4 and 1.5 provide an introduction to the architecture of

several computers that are used as examples throughout the text. Further in

formation on most of the machine architecture topics discussed can be fou

in Tabak (1995) and Patterson and Hennessy (1996).

Most of the material in this chapter is presented at a summary

many details omitted. The level of detail given here is suffi

for the remainder of the text. You should not attempt to men

in this chapter, or be overly concerned with minor points. Ins

mended that you read through this material, and then use’

needed in later chapters. References are provided thro

readers who want further information. :

1.1 INTRODUCTION

This text is an introduction to the design and

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

sbably wrote programs in assembler languas

ae co uetrectors in these programs to read

a other higher-level functions. You used an assembler, whic

luded a iacro processor, to translate these programs into machine lan,

translated programs were prepared for execution by the loader or

‘and may have been tested using the debugger.

controlled all of these processes by interacting with the ope 1g sus

suter. IF you were using a system like UNIX or DOS, you proba-

n ata keyboard, If you were using 4 system like MacOS or

bably specified commands with menus and a point-and-

er case, the operating system took care of all the ma-

for Your computer may have been connected to a

ve been shared by other users. It may have had many dit-

vices, and several ways of performing input and out-

[not need to be concerned with these issues. You could

‘you wanted to do, without worrying about how it was

will learn about several important types of sys-

understand the processes that were going on

the computer in previous courses. By under-

, you will gain a deeper understanding of how

book are assemblers, loaders and linkers,

| operating systems; each of Chapters 2

subjects. We also consider implementa-

| several real machines. One central theme of

fem software and machine architec-

ig System, ete, is influenced by the ar-

‘fo run. Some of these influences are

examples appear throughout the

it types of system soft-

d interactive debugging,

itis obviously impossible ta provide a full

single chapter of any reasonable size. Instead,

to the most important concepts and issues related)

8 systems, stressing the relationships between soft-

rchitecture. Other subtopics are discussed as Space

provided for readers who wish to explore these areas

further. Our goal is to provide a good overview of these subjeets that can also

serve as background for students who will later take more advanced software

courses. This same approach is also applied to the other topics surveyed in

Chapter 7.

many con

cove!

we provide

to compilers and opera

ware des

permits, with reference

4.2 SYSTEM SOFTWARE AND

MACHINE ARCHITECTURE

One characteristic in which most system software differs from application soft-

ware is machine dependency. An application program is primarily concerned:

with the solution of some problem, using the computer as a tool. The focus is

on the application, not on the computing system. System programs, on the

other hand, are intended to support the operation and use of the computer it-

self, rather than any particular application. For this reason, they are usually re-

Jated to the architecture of the machine on which they are to run. For example,

assemblers translate mnemonic instructions into machine code; the instruction

formats, addressing modes, etc., are of direct concern in as Ik Sleslens ti

Similarly, compilers must generate machine language code, takin

count such hardware characteristics as the number and type

the machine instructions available. Operating systems are

with the management of nearly all of the resource

Many other examples of such machine dependencies may:

out this book,

On the other hand, there are some aspects of

directly depend upon the type of computing:

example, the general design and logic of

most computers, Some of the code optimizal

are independent of the target machine (al

dependent optimizations). Likewise, the

dently assembled subprograms does not 1

being used. We will also see

features in the chapters that follow.

Because most system software i

‘machines and real pieces

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

ult to distinguish between those features of the software that are truly

fundamental and those that depend solely on the idiosyncrasies of a particular

machine. To avoid this problem, we present the fundamental functions of each

of software through discussion of a Simplified Instructional Computer

SIC is a hypothetical computer that has been carefully designed to in-

the hardware features mast often found on real machines, while avoid-

unusual or irrelevant complexities. In this way, the central concepts of a

of system software can be clearly separated from the implementation de-

ith a particular machine. This approach provides the reader

point from which to begin the design of system software for a

computer.

pter in this text first introduces the basic functions of

software being discussed. We then consider machine-

ine-independent extensions to these functions, and exam-

on actual machines. Specifically, the major chapters

and character are closely related to the

» commonly found in implementations of this

2 relatively machine-independent.

for structuring a particular piece of software—

s multi-pass processing.

on actual machines, stressing unusual

that are related to machine characteristics.

‘illustrate the most com

most

‘ of out Simplified Instructional

Like many other products, SIC comes in two versions: the standard model

and an XE version (XE stands for “extra equipment,” or perhaps “extra expen-

sive”). The two versions have been designed to be upnard compatible—that 15,

an object program for the standard SIC machine will also execute properly on

a SIC/XE system. (Such upward compatibility is often found on real comput-

ers that are closely related to one another.) Section 1.3.1 summarizes the stan-

dard features of SIC. Section 13.2 describes the additional features that are

included in SIC/XE. Section 1.3.3 presents simple examples of SIC and.

SIC /XE programming, These examples are intended to help you become more

familiar with the SIC and SIC/XE instruction sets and assembler language.

Practice exercises in SIC and SIC/XE programming can be found at the end of

this chapter

4.3.1 SIC Machine Architecture

Memory

Memory consists of 8-bit bytes: any 3 consecutive bytes form a word (24 bits),

‘All addresses on SIC are byte addresses; words are addressed by the location —

of their lowest numbered byte. There are a total of 32,768 (215) bytes in the

computer memory.

Registers

There are five registers, all of which have special uses. Each register is 241

in length. The following table indicates the numbers, mnemonics, and use:

these registers. (The numbering scheme has been chosen for comp:

with the XE version of SIC.)

Mnemonic Number Special use

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

45 24-bit binary numbers; 2's complement representation is

tive values. Characters are stored using their 8-bit ASCII code,

8). There is no floating-point hardware on the standard version

lable, indicated by the setting of the x bit

‘describes how the farget address is calcu-

provided nkage, [SUB jumps to the subroutine, placing the

return address in register L; RSUB returns by jumping to the address con-

tained in register |

Appendix A gives a complete list of all SIC (and SIC/ XE) instructions, with

their operation codes and a specification of the function performed by each.

input and Output

On the standard version of SIC, input and output are performed by transfer

ring 1 byte ata time to or from the rightmost 8 bits of register A_ Each device is

assigned a unique S-bit code. There are three I/O instructions, each of which

specifies the device code as an operand.

The Test Device (TD) instruction tests whether the addressed device is

ready to send or receive a byte of data. The condition code is set to indicate the

result of this test. (A setting of < means the device is ready to send or receive,

and = means the device is not ready.) A program needing to transfer data must

wait until the device is ready, then execute a Read Data (RD) or Write Data

(WD), This sequence must be repeated for each byte of data to be read or writ:

ten. The program shown in Fig, 2.1 (Chapter 2) illustrates this ‘aun

performing 1/0.

4.3.2 SIC/XE Machine Architecture

Memory

‘The memory structure for SIC/XE is the same as that

SIC. However, the maximum memory available.

1 megabyte (220 bytes). This increase leads to a

and addressing modes.

Registers

‘The following additional registers are,

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

formats as the standard version. In addition,

provides the same data

ta type with the following format

ig a 48-bit floating-point dat

preted asa value between 0 and 1; that is, the assumed bi-

ly before the high-order bit. For normalized floating-

high-order bit of the fraction must be | The exponent is

signed binary number between 0 and 2047. If the exponent

has value f, the absolute value of the number rep-

fe pte-1024)_

-number is indicated by the value of s (0 =

jue of zero is represented by setting, all bits

fraction) to 0.

means that an address will (in gen-

struction format used on the

te two possible aptions—

address field to 20

A Wei eeey

1b enepiar

41 oex

Format 3 (3 bytes) bb! Gase

Pe Pe

6 y444d4 12 ; :

Suvaniy’ © 2 etenpep

(ovate [ell elec

Format 4 (4 bytes):

6 y1aiiiti 20 io

(== ERE

Addressing Modes I

Two new relative addressing modes are available for use with

assembled using Format 3, These are described in the fallow: 1

Mode Indication Target addre

Base relative b=1,p=0 TA=(B)+ disp

Program-counter b=0,p=1

relative

For bse relative addressing, the

tion is interpreted as a 12-bit

dressing, this field is interpre!

values represented in 2's comp

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

Chapter 1 Beckgrownt

Bile anda in Formats 3nd 4are used to specify how the target address is

Wised: If bit ¢= Land m= 0, the target address itself is used as the

Waluse; ho memory reference is performed. This is called jvm

Tebiti = 0 and # = 1, the word at the location given by the targ:

fetched; the glue contained in this word is then taken as the address of the

operand value. This is called indirect addressing. If bits ¢ and 2 are both 0 or

both 1, the target address is taken as the location of the operand; we will refer

‘to this as simple addressing. Indexing cannot be used with immediate or indi-

rect addressing modes

| Many authors use the term efectioe address to denote what we have called

‘the farget address for an instruction. However, there is disagreement concern-

"ing the meaning of effective address when referring to an instruction that uses

ect addressing, To avoid confusion, we use the term target address

rand

addressing

XE instructions that specify neither immediate nor indirect addressing.

with bits n and fboth set to 1. Assemblers for the standard vi

swill, however, set the bits in both of these positions to 0. (This is be

binary codes for all of the SIC instructions end in 00.) All

=: have a special hardware feature designed to provide the up-

ty mentioned earlier. If bits n and i are both 0, then bits b, )»,

to be part of the address field of the instruction (rather

addressing modes). This makes Instruction Format 3

sed on the standard version of SIC, providing the de-

es of the different addressing modes available on

the contents of registers B, PC, and X, and of se-

_{All values are given in hexadecimal.) Figure 1.1(b)

a series of LDA instructions. The target address

i the value that is loaded into register A, are

lly examine these examples, being sure you un

odes illustrated,

/XE instruction formats and addressing

ions that are available on the standard

tions to load and store the new registers

arithmetic operations (ADDF,

e303 | 003030

(a)

Hex

32600,

eacs00

or2030

‘910030

‘oa3600

03100303.

onoaae

060000

oppo0

oooo0o

ooga09

oonadg

puter (SIC)

(a) = 098000

(Pc) = o0a000

[xj = popa80

Machine instruction

Binary s

pe

1 2 0 9 3 © 9110 e000 oono

1 1 1 1 @ 06 o@it oppo 9900

1 0 a 0 3 © 0090 o01u odeo

o 1 @ © 6 © 000g 01a Oooo

o 0 8 0 4 4 Olio caoo the

1 1 6 5 © 21 ooo 1100 bon

ta) ;

Figure 1.1 Examples of SIGIXE instructions and addressi

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

Chapter 1 Bavkgenert

here are also instructions that take the

ei arithme ic operations (ADL 3K, SUBR, MUL

alt instruction (SVC) is provided. Executing t!

erates an interrupt thatcan Pe used for communication with the

“gystem, (Supervisor calls rd interrupts are discussed in Chapter 6,

© There arealeo several other new qnstructions. Appendix A gives @ complete

“gist of all SIC/XF instructions, with their op

the function performed by each.

codes ancia specification of

“Input and Output

instructions we discussed for SIC are also Hable on SIC/ XE. In ad-

there are 1/O channels that can be used to perform input and output

the CPU is executing other instructions. This allows overlap of comput

ra 1/0) resulting in more efficent system operalion, The instructions

and HIG are used to start, test, and halt the operation of 1/0 chan-

concepts are discussed in detail in Chapter 6.

Programming Examples

ts simple examples of SIC and SIC/XE assembler language

‘examples are intended to help you become more familiar

{nstruction sets and assembler language. It is as-

“alteady familiar with the assembler language of at

the basic ideas involved in assembly-level pro-

‘book is systems programming, not assembler

owing chapters contain discussions of various

‘some cases SIC programs are used to illus:

his ection contains material that may help you

ily. However, it does not contain any

programming. Thus, this section

t operations for SIC and

Wve instructions; thus, all data

2(a) shins two examples of

Toading it into register

g the rightmost &bit byte of

ted.

ys of defining storage for data

assembler directives até discussed,

1.) The statement WORD reserves one word of stor

value defined in the operand eld of the state

ment in Fig. 1.2(a) defines a data word labeled

alized to 5, The statement RESW reserves one or

use by the program. For example, the RESW state:

rent in Fig. 1.2(a) defines one word of storage labeled ALFHA, which will be

eed to hold a value generated by the program.

The statements BYTE and RESB perform similar storage-definition func:

tions for data items that are characters instead of words. Thus in Fig. 1.2la)

CHARZ is a L-byte data item whose value is initialized to the character ee

and C1 isa L-byte variable with no initial value

more words of ste

TOA FIVE

Sth ALPHA

EncH = -CHARZ

LOAD CORISTANT 5 INTO REGISTER A

STORE IN ALEHA

LOAD CHASACTER ‘2! INTO RESISTER A

Sica cl STORE IN CHABACTER VARIABLE O1

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

ET ao

also work

adwanc

‘Chapter 2 Backgrownst

not have to be fetched

ue i ched fray

uted. Immediate addressing is used ie

ister X to 0,

aTie instructions shawn in Fig: 1.2(a) would

‘ever, they would no take advantage of the more

available. Figure 1.2(b) shows the same two data-m¢

“they might be written for GIC/XE. In this example, the v

“register A using immediate addressing. The operand field for this in

‘contains the flag # (which specifies immediate addressing) and the cai

Similarly, the character 47" jg placed into register A by uw

addressing to.foad the value 90, which the decimal valu

[onde that is used internally to represent the character "#

sure 1a) shows examples of arithmetic instructions for SIC. All arith.

are performed using: register A, with the result being left in

this sequence of instructions stores the value (ALPHA + INCR

ithe value (GAMMA + INCR~ 1) in DELTA.

viluctates how the same calculations could be performed on

INCR is loaded into register S initially, and the registes

an ADDR is used to add this value to register Awhen itis

g to fetch INCR from memory each time it is used in

Wy make the program more elficient Immediate ad-

t Lin the subtraction eperations.

ations are illustrated in Fig. Figure 1.4(a)

ii-byte character string to another, The index

zero before the loop begins. Thus, during

et address for the LDCH instruction will

yemet

ER A

REG

OF THCR

STORE TN DELTA

cue is ONE-WORD CONSTANT

ONE-WORD VARTABLES

nck -RESW

n code is

if the condition

; to the beginning of the loop

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

T2E 1

RACTER FRC

App 1 70 INDEX, CU

mop tf INDEX IS LE

GinRgT STRING’ © 11-BYTE STRING CONSTANT

1-8YTE VARIABLE

ONE-WORD CONSTANTS

(3)

ITIALIZE REGISTER T TO 11

THITIALTZE INDEX REGISTER TO 0

LOAD CHARACTER FROM STR1 INTO REG A

STORE CHARACTER INTO STRE

App 1 TO INDEX, COMPARE RESULT TO 11

LOOP IF INDEX TS LESS THAN 11

_-1-BYTE STRING CONSTANT

4L1-BYTE VARIABLE

oh VALUE ‘1-0,

ALE INTO REGISTER

ALPHA INTO REGISTER A

COMPARE NEW INDEX VALUE TO 300

LOOP If INDEX IS LESS THAN 300

ONE-WORD VARIABLE FOR INDES VAUIE

ARRAY VARIABLES=-100 WORDS EACH

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

Chapter 1 Barckgrmund

In Fig. 15a), we define 4 variable INDEX that holds the +

for indexing for each iteration of the Joop. Thus, INDEX sh:

first iteration, 3 for the second, and so on. INDEX is initialize

Start of the loop. The first instruction in the body of th

value of INDEX into register X so that it can be

Hon, The next three instructions in the loop load ALPHA

corresponding word from BETA, and store the result in the corre

Montiel GAMMA, The value of INDEX is then loaded into register A, incy

mented by 3, and stored back into INDEX. After ring stored, the new if

INDEX is still present in register A. This valuc is then compared to 300 (the

Jength of the arrays in bytes) to determine whether or not to terminate the

“bop: It the value of INDEX is less than 300, then all bytes of the arrays have

‘Tok yet beea processed. In that case, the JLT instruction causes a jump back to

* beginning of the Joop, where the new value of INDEX is loaded inte epi

Patticular loop is cumbersome on SIC, because register A must be

"adding the array elements together and also for incrementing the fn

c loop can be written much more efficiently for SIC/XE, as

(b), In this example, the index value is kept permanently in

mount by which to increment the index value (3) is kept in

rorregister ADDR instruction is used to add this in-

Similarly; the value 300 is kept in register T, and the in-

ed to compare registers X and T in order to decide

Iple of input and output on SIC; the same

ME. (The more advaneed input and out-

eh as 1/O channels and interrupts, are

| fragment reads 1 byte of data from de-

put a

acter-oriented (for ex-

‘the ASCII code for the

LOOP UNTIL DEVICE Is REA

LOAD DATA BYTE INTO ABGISTER A

WRITE ONE BYTE 9 OUTPUT Device

RIFL’ INPUP DEVICE WUMBER

ane OUTPUT DEVICE NUMBER

NTE

Be ech ONE-BYTE VARIABLE

DATA 5

Figure 1.6 Sample input and output operations for SIC.

he TD instruction and then check th

tes, the progeiin must execute t p and the

Pisa code by using a conditional jump. If the condition code is

[device not ready}, the program jumps back to the TD ins

instruction loop will continue until the device becomes ready;

ted.

ee is performed in the same way. First the }

whether the output device is ready to receive a byte

be written is loaded into the rightmost byte

Data) instruction is used to transmit it to the device. —

Figure 17 shows how these instr

record from an input device into memory, Th

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

SUBROUTINE

INDTYALIZE IN

TEST INPUT 0

Wor IF PAVICE TS Ft

RO RES

STORE DATA BYTE Uf

ADD 1 TO INDEX AND cot

LOOP IF INDEX I5 LESS

EXIT FROM SUBROUTINE

INPUT DEVICE NUMBER.

100-BYTE BUFFER FUR INPUT RECORD

ONE-HORD CONSTANTS

-SUBROURINE TQ READ 100-BYTE RECORD

Traditional (CASC} Machines

(CISC) MACHINES

ines that will be

AX architecture,

intel x86 family of proces:

The mach tion are classified as Complex Instruc-

ISC machines ally have a relatively large

coms tru q ferent instruction formats and

ssing modes, Thus the implementation of

Sia hardware tends to be complex

You may want to compare the examples in this section with the Reduced

Instruction Set Computer (RISC) examples in Section 1.5, Further discussion of

CISC versus RISC designs can be found in Tabak (1995),

1.4.1 VAX Architecture

‘The VAX family of computers was introduced by Digital Equipment

Corporation (DEC) in 1978. The VAX architecture was designed for compatre

bility with the earlier PDP-11 machines. A compatibility mode was p

the hardware level so that many PDP-11 programs could run un

the VAX, It was even possible for PDP-11. programs and’ VAX 4

share the same machine ina multi-user environment.

“This section summarizes some of the main charact

tecture. For further information, see Baase (1992),

‘Memory

The VAX memory consists of 8-bit bytes. All

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

Chapter 1 Backgrownit

f the proces tains

is defined separately for each program. A pa

stacks that are available to the program. Sp

tions aid in the use of these stacks:

registers and m a

Registers

There are 16 general

Ris. Some of these registers, however, have

ral registers are 32 buts in length. Register R15

called PC. It is updated during instruction execute

struction byte to be fetched. R14 is the stack pomrter SP, w!

rent top of the stack in the program's process Space. Although it is pos:

‘use other registers for this purpose, hardware instructions that implicitly use

the stack always use SP. R13 is the franre pointer FP. VAX procedure call con-

ventions build a data structure called a stack frame and place its address in

FP. Rizis the argiinent pointer AP. The procedure call convention uses AD’ to

‘pass a list ofarguments associated with the call

Registers RG through R11 have no special functions, and are available for

al use by the program, Registers RO through RS are likewise available for

ral uses however, these registers are also used by some machine instruc-

urpose registers on th

‘In addition to the general registers, there is a processor status longwort

fh contains state variables and flags associated with a process. The

among many other items of information, a condition code and a

whether PDP-11 comp: y mode is being used by a

also a number of control registers that are used to support

system functions.

joint data

are compatible with those found on the

. The other two are available

s Tepresentec! as a fraction that is to

ta format. In this format, each

GR ay

s with one

sit per byte, In this format, the

2 separate byte preceding the first

and leading separate mis

wath bit strings. Data structures

@, be implemented on any machine; however, VAX,

support for them. There are single machine instruc-

provides «

tions th tries in queues, and perform a variety of opera

tions ¢ existence of such powerful machine instructions and

complex is one of the more unusual features af the VAX

Instruction Formats

VAX machine instructions use a variable-length instruction format, Each in-

struction consists of an operation code (1 or 2 bytes) followed by up to six

operand specifiers, depending, on the type of instruction. Each operand specifier

clesignates one of the VAX addressing modes and gives any additional infor-

mation necessary to locate the operand, (See the description of addressing

modes in the following section for further information}

Addressing Modes

VAX provides a large number of addressing, modes, With few exceptions, any

of these addressing modes may be used with any instruction. The operand it=

self may be in a register (register mode), or its address may be specified by a

register (register deferred mode). If the operand address is ina register, the regy

ister contents may be automatically incremented or decremented by the

‘operand length (autoincrement and autodecrement modes). There are several

‘pase relative addressing modes, with displacement elds of different Y

when used with register PC, these become program-counter relatly

‘All of these addressing modes may also include an index register,

them are available in a form that specifies indirect re

modes on VAX). In addition, there are immediate operands

cial-purpose addressing modes, For further details, see Baase|

Instruction Set

One of the goals of the VAX designers was to pr

symmetric with respect to data type. Many |

y combining the following, elements:

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

‘Chapter 1 Backgroverel

1. a prefix that specifies the type of operation

>, a suffix that specifies the data type of the operands,

3. a modifier (on some instructions) that gives the 1

involved.

For example, the instruction ADDW2 is an add operation with two operands,

each a word in length. Likewise, MULL3 is a multiply operation with throp

Yongiwond operands, and CVTWL specifies a conversion from Word to lon

word. (In the latter case, 4 fwo-operand instruction is assumed } F.

Gretuction, eperands may be located in registers, in memory, or in the instruc.

tion itself (immediate addressing). The same machine instruction code is used

-regardless of operand locations, i

VAX provides all of the usual types of instructions for computation, data

at and conversion, comparison, branching, ete In addition, there area

Foperations that are much mare complex than the machine instruc.

‘on most computers, These operations are, for the most part, hard.

ations of frequently occurring sequences of code. They are

single instructions for efficiency and speed, For example, VAX

is ts load and store multiple registers, and to manipulate

leength bit fields. There are also powerful instructions for

ming from procedures. A single instruction saves a designated

asses a list of arguments to the procedure, maintains the

iment pointers, and sets a mask to enable error traps for

or further information on all of the VAX instructions,

4 typical

ccomplished by T/O device controllers.

/status and data registers, which are as-

‘space The portion of the address

sl re mapped is called 1/0 space,

‘to access registers in 1/O space. An

the controller by storing values

were physical memory loca-

these registers to obtain status in-

[/O space with a physical register

14 Traditional (CISC) Machines

4.42 Pentium Pro Architecture

The Pentium Pre essor, introd!

near the end of 1995, is the lafest

jn the Intel x

‘Other recent microprocessors in this family are the

504g6 and Pentium. sors of the xh family are presently used ina major

ity of personal compu 4 there is a vast amount of software for these

F eeseors. It is expected that additional generations of the x86 family will be

Fieveloped in the future.

The various xB6 processors. differ in implementation details and operating

peed. However, they share the same basic architechure, Each succeeding gen-

soa has been designed to be compatible with the earlier verstons, This set

fey contains an overview of the x86 archileetite which will serve as

fackground for the examples to be discussed later in the book. Further infor-

mation about the x86 family can be found in Intel (1995), Anderson and

ghanley (1995), and Tabak (1995).

Memory

Memory in the x86 architecture can be described in at Jeast two different ways.

‘At the physical level, memory consists of B-bit bytes, All addiesses ‘used are

byte addresses. Two consecutive bytes form a word; four, bytes form a double~

joord (also called a dword). Some operations are more efficient when operands

are aligned in. # particular way—for example; a doubleword operand that be

gins at a byte address that isa multiple of 4. 7 ‘

However, programmers usually view the x86 memory as a collection of

segneits. From this point of view, an address consists of bvo pe a oe .

Number and an offset that points to a byte within the segment: 9S6P

be of different sizes, and are often used for different purposes For

some segments may contain executable instructions and other 5

be used to store data. Some data segments may be treates

‘used to save register contents, pass parameters [0 sub)

cal memory. In some cases, @ Se

the pages of a segment may be

stored on disk. When an x!

erating system make sure nes

physical memory. The segment offset

wutomatically translated into a phy:

JPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

IPG To PDF - Unregistered

If you want to remove this text, Please register

JPG To PDF - Unregistered

If you want to remove this text, Please register

Chapter 1 Background

Management Unit (MMU). Chapter 6 contains a brief discussi

af methods

thatean be used in this kind of address translation

Registers

There are eight general-purpose registers, which are named EAX, EBX, ECx,

EDX, ESI, EDI, EBP, and ESP Each general-purpose register is 2 bits long (he

one doubleword). Registers EAX, EBX, ECX, and EDX are generally used for

data manipulation; it is possible to access individual words or bytes from

- these registers. The other four registers can also be used for data, but are more

ly used to hold addresses. The general-purpose register set is identi.

for all members of the x86 family beginning, with the 80386, This set is also

mpatible with the more limited register sets found in earlier members of the

e are also several different types of special-purpose registers in the x86

IP is a 32-bit register that contains a pointer to the next instruc.

FLAGS is a 32-bit register that contains many different bit

flags indicate the status of the processor; others are used

of comparisons and arithmetic operations. There are also

isters that are used to locate segments in memory

the address of the currently executing code seq-

idress of the current stack segment. The other seg-

and GS) are used to indicate the addresses of data

are performed using a special floating-point

eight 80-bit data registers and several other con-

[so far are available to application programs

jat are used only by system programs

La Traditional (CISC) Machines

sfute-enatian byte cause the “little end” of the value comes first in

or

memes?) can also be stored in binary coded decal (BCD). In the unpacked

BCD format, ch byte represents one decimal digit, The value of this digit is

Be te (in binary) in the low-order 4 bits of the byte the high-order bis are

eresnally zero. Inthe packed HCD format, each byte represents seo decimal

ante 4 bits of the byte.

There are three different floating:point data formats. The single-precision

format is 32 bits long, It stores 24 significant bits of the floating-point value;

ety allows for a 7-bit exponent (power of 2). (The remaining, bit is used to

tore the sign af the floating-point value.) The double-precision formal is 64

bits long, It stores 53. significant bits, and allows for a 10-bit exponent. The

extended-precision format is BO bits long, 1t stores 64 significant bits, and

allows for a 15-bit exponent

‘Characters are stored one per byte, using their S-bit ASCII codes. Strings

may consist of bits, bytes, words, or doublewords; special instructions are

provided to handle each type of string,

Instruction Formats

All of the x86 machine instructions use variations of the same basic for

‘This format begins with optional prefixes containing flags that modify th