Professional Documents

Culture Documents

Ananth Resume

Uploaded by

Krishna ShettyCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Ananth Resume

Uploaded by

Krishna ShettyCopyright:

Available Formats

ANANTH SHETTY K R

Email: ananthsetty05@gmail.com

Mobile No: 8105010222

Objective

To become a more challenging full custom layout design engineer proficient in effective floor plan and optimized

layout designs in future technologies.

Core Competencies

Worked on Custom layout design of 180nm, 90nm & 28nm technologies

Knowledge of complete ASIC flow, Full custom flow and sub-flows

Knowledge of Layout development and Verification (DRC,LVS& Parasitic Extraction)

Played an important role in designing the layouts for standard cells and analog blocks such as OPAMP

Played an important role in designing the layout for SRAM Memory Compiler using 28nm

Good understanding of LVS errors, shorts, opens, real and false errors

Knowledge of analog layout concepts like Matching, symmetry

Knowledge of EDA tools such as Cadence, Mentor Graphics and Synopsys

Good exposure to technology by undergoing additional training in VLSI

Good understanding of fundamentals of Transistors and CMOS device operation

Good knowledge of Digital Design Concepts

Working Knowledge of Linux

Good knowledge on parasitics and their effects on performance

Education Profile

M.Tech - Industrial Electronics from SJCE, Mysore, Affiliated to VTU, 2015, with 8.48 CGPA (77.3%)

B.E Electronics and Communication Engineering (under VTU) from KLEIT, Hubli, 2012, with aggregate

of 70.12%

Senior Secondary Class 12 (PUC II), Fatima Composite PU College, Hubli, 2008, with aggregate of 78%

Class 10 (SSLC), Saint Andrews English Medium High School, Hubli, 2006, with aggregate of 82.24%

Experience

Trainee at RV-VLSI Design Center:

As a trainee in RV-VLSI Design Center, I physically verified layouts for various standard cells in 180nm, 90nm

and 28nm technology nodes of TSMC and Jazz semiconductor foundries respectively. Worked on 28nm 32x32

SRAM Memory Layout compiler where I was designing layouts of leaf cells.

Projects

1) 90nm 9track Standard Cell Library Design

Designing Standard Cells Library for Combinational Circuits such as:

INVERTER: INVx1, NOR: NOR2x1, NAND: NAND2X1, HALF ADDER: HADDx2, MUX: MUX21x2

Sequential Circuits such as: D- Flip Flop: DFFX1, DFFX2

Tools Used:

IC studio: Mentor Graphics

Pyxis: Schematic and Layout editor

Calibre RVE: DRC & LVS check

Deliverable/Challenges Faced:

1. Fitting the complete layout within the PR-Boundary including n-tap and p-tap maintaining all DRC rules

2. Making the layout as optimized as possible by Source & Drain sharing

3. Reducing the parasitic by making use of metal over poly

4. Placing as many contacts for connecting the metals for the reduction of parasitic

5. Placing metal pins on grid by maintaining proper distance among them to satisfy compatibility of the design

2) Two Stage Differential Amplifier Layout Design in 180nm Technology

Tools Used:

IC studio: Mentor Graphics.

Pyxis: Schematic and Layout editor.

Calibre RVE: DRC & LVS check.

Deliverable/Challenges Faced:

1. Making common centroid

2. Device matching

3. Maintaining of metal width such that in order to come across cross talk

4. To overcome Latch-up & Electro Migration problem

5. DRC is error free but to make error free LVS filter is needed because dummies are to be neglected

3) Design of Leaf Cell for SRAM Memory in 28nm Technology

Designing Standard Cells Library for Combinational Circuits such as:

INVERTER: INVx1, INVx2, NAND: NAND2x1, NAND2x2, NAND2x4, NOR: NOR3x1, NOR3x2, NOR3x4,

AND: AND2x1, AND3x1, OR: OR3x1, OR3x2, OR3x4

Tools Used:

IC studio: Mentor Graphics

Pyxis: Schematic and Layout editor

Calibre RVE: DRC & LVS check

Deliverable/Challenges Faced:

1. Placing contacts and polys on grid

2. There are no pin placement rules

3. Reducing the parasitic by making use of metal over poly

You might also like

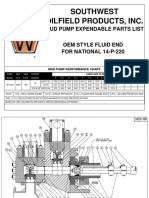

- Oem National 14-P-220 7500psiDocument9 pagesOem National 14-P-220 7500psiandrew0% (1)

- Ananth Resume 1Document3 pagesAnanth Resume 1Krishna ShettyNo ratings yet

- AL Radhakrishna 2+Document3 pagesAL Radhakrishna 2+shubhadNo ratings yet

- Vijay Kumar Physical Design EngineerDocument3 pagesVijay Kumar Physical Design EngineerKarthik VarmaNo ratings yet

- Resume KumarVishalDocument4 pagesResume KumarVishalkumarvishalsingh3No ratings yet

- Prudhvi SaiDocument3 pagesPrudhvi SaishubhadNo ratings yet

- Role Title: Research Engineer (Ece) Key AccountabilitiesDocument2 pagesRole Title: Research Engineer (Ece) Key AccountabilitiesAbhay KumarNo ratings yet

- Siva Kumar Raju - Analog - Layout - ResumeDocument5 pagesSiva Kumar Raju - Analog - Layout - ResumeSiva Kumar Raju ChamarthiNo ratings yet

- What To LearnDocument2 pagesWhat To LearnJeethendra PathakNo ratings yet

- L&T EmbDocument6 pagesL&T Embmanjeet.singh837824No ratings yet

- Resume LayoutDocument10 pagesResume LayoutvijaykannamallaNo ratings yet

- Ashwini ResumeDocument5 pagesAshwini ResumekalyanNo ratings yet

- Resume Arvind ShrivastavaDocument2 pagesResume Arvind ShrivastavaArvind ShrivastavaNo ratings yet

- PD Profile 6 PBDocument2 pagesPD Profile 6 PBRA NDYNo ratings yet

- CAD & Design Flow: Motivation: Microelectronics Design EfficiencyDocument18 pagesCAD & Design Flow: Motivation: Microelectronics Design EfficiencyJubin JainNo ratings yet

- SMTS II / PE Circuit Design Engineering Areas of ResponsibilitiesDocument1 pageSMTS II / PE Circuit Design Engineering Areas of ResponsibilitiessairaghubabuNo ratings yet

- PD 2.1 Years Adithyan JDocument4 pagesPD 2.1 Years Adithyan JAdithyan JNo ratings yet

- ResumeDocument2 pagesResumeArnab DuttaNo ratings yet

- Vinod PD 2.5 Years Tessolve SemiconductorsDocument2 pagesVinod PD 2.5 Years Tessolve SemiconductorstejanossamNo ratings yet

- Resume Srinivasa GadigatlaDocument3 pagesResume Srinivasa GadigatlasgadigatNo ratings yet

- Akash Kumar IITMandiDocument1 pageAkash Kumar IITMandib21215No ratings yet

- Career Objective: Projets and ExperienceDocument6 pagesCareer Objective: Projets and ExperiencesnehaNo ratings yet

- Bilal Resume 2023Document2 pagesBilal Resume 2023Rizwan AliNo ratings yet

- Infotech Electronic Design Services OverviewDocument15 pagesInfotech Electronic Design Services OverviewVirath KaurNo ratings yet

- VLSI - Job - Title - Skills - SummaryDocument12 pagesVLSI - Job - Title - Skills - SummaryBhargavi PatilNo ratings yet

- Shubham.p ResumeDocument4 pagesShubham.p ResumeShubham PatilNo ratings yet

- Feroz Choudhary: Profile SummaryDocument5 pagesFeroz Choudhary: Profile SummaryFeroz AhmedNo ratings yet

- Analog Design Methodology Jnotor r3Document17 pagesAnalog Design Methodology Jnotor r3Manjunath ReddyNo ratings yet

- Me SyllabusDocument3 pagesMe SyllabusPrabhu SubramaniamNo ratings yet

- Tick The Circle Which Is Interested: Cradle CFDDocument6 pagesTick The Circle Which Is Interested: Cradle CFDMithun RajuNo ratings yet

- NyklDocument3 pagesNyklBunti KumarNo ratings yet

- Pavan - PD Updated ResumeDocument3 pagesPavan - PD Updated ResumeRA NDYNo ratings yet

- Course Code: Course Title: Pre-Requisite: Course ContentDocument2 pagesCourse Code: Course Title: Pre-Requisite: Course ContentFaisal HossainNo ratings yet

- Lead RFIC EngineerDocument3 pagesLead RFIC EngineerKini FamilyNo ratings yet

- Vlsi ch1Document64 pagesVlsi ch1Nihar ranjan AditNo ratings yet

- Application of Mentorgraphics Tools: Eldo PlatformDocument5 pagesApplication of Mentorgraphics Tools: Eldo Platformvijendra_415174385No ratings yet

- DCCT SyllabusDocument11 pagesDCCT SyllabusmkmaithalNo ratings yet

- Sem1 EmbbededDocument9 pagesSem1 Embbededvishwanath cNo ratings yet

- Rishikesh Suresh TambulkarDocument3 pagesRishikesh Suresh TambulkarHariharan SNo ratings yet

- Electronic Services PCB Design Services: Library DevelopmentDocument6 pagesElectronic Services PCB Design Services: Library DevelopmentRamanan MNo ratings yet

- Aca Lecuternotes 1-4unitsDocument91 pagesAca Lecuternotes 1-4unitsvamsi.imgNo ratings yet

- Vlsi NotesDocument5 pagesVlsi NotesDiwakar TiwaryNo ratings yet

- CpE321L Lesson 1 - Introduction To IC Design and HDLDocument38 pagesCpE321L Lesson 1 - Introduction To IC Design and HDLSebastian KarlNo ratings yet

- Srivats Iyer ResumeDocument2 pagesSrivats Iyer ResumeSrivats IyerNo ratings yet

- DS CR 5000 Board Designer en v2Document2 pagesDS CR 5000 Board Designer en v2mryalamrbNo ratings yet

- Advanced Computer Architecture: Tran Ngoc Thinh HCMC University of TechnologyDocument46 pagesAdvanced Computer Architecture: Tran Ngoc Thinh HCMC University of TechnologyAnkit GuptaNo ratings yet

- Al Nevespenn State 2019Document55 pagesAl Nevespenn State 2019FreesomNo ratings yet

- 138 DraftDocument36 pages138 DraftPhola PatulinNo ratings yet

- DE CourseResume ENGDocument2 pagesDE CourseResume ENG潘卫平No ratings yet

- For ReferenceDocument9 pagesFor ReferenceashfaqsarafNo ratings yet

- RF MmWave IC Design Engineer - CambridgeDocument4 pagesRF MmWave IC Design Engineer - CambridgeRamnath KiniNo ratings yet

- VLSI Design Methodology: TopicsDocument12 pagesVLSI Design Methodology: Topicskrishy19sNo ratings yet

- Abhishek Chakraborty ResumeDocument2 pagesAbhishek Chakraborty Resumeabhi2006fiemNo ratings yet

- 0 - Resume - Pradeep KumarDocument6 pages0 - Resume - Pradeep KumarShiva PrasadNo ratings yet

- Resume - Gandhi (Full Time)Document1 pageResume - Gandhi (Full Time)Prit GalaNo ratings yet

- SAURABH KORANGLEKAR, B-41, C2C Day1 Assignment: Company Name Job Title Job QualificationDocument7 pagesSAURABH KORANGLEKAR, B-41, C2C Day1 Assignment: Company Name Job Title Job QualificationSaurabh KoranglekarNo ratings yet

- Elective-Iv Digital Vlsi DesignDocument4 pagesElective-Iv Digital Vlsi Designnayna bhosaleNo ratings yet

- Vlsi Ecad Lab Manual 2nd Cycle Exp 2019Document25 pagesVlsi Ecad Lab Manual 2nd Cycle Exp 2019Nilasha NilaNo ratings yet

- 2 - RSD - VLSI Design FlowDocument11 pages2 - RSD - VLSI Design FlowRashmi SinghNo ratings yet

- Vit Ece 5th Year SyllabusDocument16 pagesVit Ece 5th Year Syllabuspranavateja12399No ratings yet

- Time and WorkDocument4 pagesTime and WorkKrishna ShettyNo ratings yet

- Shock: Sandesh S Melagiri 57Document5 pagesShock: Sandesh S Melagiri 57Krishna ShettyNo ratings yet

- CSP - Final PPT 1.1Document50 pagesCSP - Final PPT 1.1Krishna ShettyNo ratings yet

- Final Report EEDocument12 pagesFinal Report EEKrishna Shetty100% (1)

- CSP - Final PPT 1.1Document50 pagesCSP - Final PPT 1.1Krishna ShettyNo ratings yet

- Pavement Engg NotesDocument25 pagesPavement Engg NotesKrishna ShettyNo ratings yet

- Building and Other Construction Workers Act 1996Document151 pagesBuilding and Other Construction Workers Act 1996Rajesh KodavatiNo ratings yet

- Ce - 332 Ee Lab ManualDocument105 pagesCe - 332 Ee Lab ManualShanihaKKNo ratings yet

- Material Testing Open Ended Experiment: Effect On Strength and Slump of The Concrete Due To Different Types of WaterDocument11 pagesMaterial Testing Open Ended Experiment: Effect On Strength and Slump of The Concrete Due To Different Types of WaterKrishna ShettyNo ratings yet

- Material Testing Open Ended Experiment: Effect On Strength and Slump of The Concrete Due To Different Types of WaterDocument11 pagesMaterial Testing Open Ended Experiment: Effect On Strength and Slump of The Concrete Due To Different Types of WaterKrishna ShettyNo ratings yet

- AggregatesDocument15 pagesAggregatesKrishna ShettyNo ratings yet

- Building Permission HDMCDocument36 pagesBuilding Permission HDMCPavan ReddyNo ratings yet

- Ananth Setty ResumeDocument2 pagesAnanth Setty ResumeKrishna ShettyNo ratings yet

- Ananth Setty ResumeDocument2 pagesAnanth Setty ResumeKrishna ShettyNo ratings yet

- Text DetectionDocument17 pagesText DetectionKrishna ShettyNo ratings yet

- Ananth Setty ResumeDocument2 pagesAnanth Setty ResumeAnanth SettyNo ratings yet

- Learn To Play Bansuri - Alankars (1-15)Document7 pagesLearn To Play Bansuri - Alankars (1-15)Krishna ShettyNo ratings yet

- Ananth Shetty K R Mobile No: 8105010222 ObjectiveDocument1 pageAnanth Shetty K R Mobile No: 8105010222 ObjectiveKrishna ShettyNo ratings yet

- Ananth Setty ResumeDocument2 pagesAnanth Setty ResumeAnanth SettyNo ratings yet

- Official SBI Specialist Officers Eligibility & Recruitment Notification 2016Document6 pagesOfficial SBI Specialist Officers Eligibility & Recruitment Notification 2016Testbook BlogNo ratings yet

- Ananth Setty ResumeDocument2 pagesAnanth Setty ResumeAnanth SettyNo ratings yet

- Setty Resume 2Document3 pagesSetty Resume 2Krishna ShettyNo ratings yet

- Ananth Setty ResumeDocument2 pagesAnanth Setty ResumeAnanth SettyNo ratings yet

- Ananth Setty ResumeDocument2 pagesAnanth Setty ResumeAnanth SettyNo ratings yet

- OBIEE Developer - Amit U KDocument4 pagesOBIEE Developer - Amit U KAnanth SettyNo ratings yet

- ZCZXCDocument14 pagesZCZXCramaNo ratings yet

- Naruto - NagareboshiDocument2 pagesNaruto - NagareboshiOle HansenNo ratings yet

- BE Enus DP3441DP3441e DP3661e Series Portable Radios Quick Reference GuideDocument6 pagesBE Enus DP3441DP3441e DP3661e Series Portable Radios Quick Reference GuideEduardoNo ratings yet

- StarbucksDocument19 pagesStarbucksNimah SaeedNo ratings yet

- Lexium Motion Control 200401Document130 pagesLexium Motion Control 200401Mohamed Elsayed HasanNo ratings yet

- Doppler NavigationDocument21 pagesDoppler NavigationRe-ownRe-ve100% (3)

- Pre-Disciplinary and Post-Disciplinary Perspectives: Bob Jessop & Ngai-Ling SumDocument13 pagesPre-Disciplinary and Post-Disciplinary Perspectives: Bob Jessop & Ngai-Ling SumMc_RivNo ratings yet

- FConvert Free YouTube Converter Downloader Convert To MP3, MP4Document2 pagesFConvert Free YouTube Converter Downloader Convert To MP3, MP4FConvert Free YouTube ConverterNo ratings yet

- Spare Parts List: Hand-Held Gas Saw DS HS80-14"Document20 pagesSpare Parts List: Hand-Held Gas Saw DS HS80-14"mayoo1986No ratings yet

- Unit 2Document3 pagesUnit 2lewlking123No ratings yet

- Patch Apply Instructions 19852360.HTMLDocument60 pagesPatch Apply Instructions 19852360.HTMLdineshNo ratings yet

- Market Intelligence Case Study Sales & MarketingDocument20 pagesMarket Intelligence Case Study Sales & MarketingBrian ShannyNo ratings yet

- Đề luyện tập 5Document5 pagesĐề luyện tập 5Nguyễn Duy TânNo ratings yet

- Argumentative EssayDocument20 pagesArgumentative EssayLuthfi MaullanaNo ratings yet

- Digital Market Space in BeautyDocument48 pagesDigital Market Space in BeautyInaNo ratings yet

- Glastic Utr Angles ChannelsDocument2 pagesGlastic Utr Angles Channelsdanielliram993No ratings yet

- Citroen Xsara I - Wiring DiagramDocument20 pagesCitroen Xsara I - Wiring DiagramDavid VasNo ratings yet

- 3UG46251CW30 Datasheet enDocument5 pages3UG46251CW30 Datasheet enDante AlvesNo ratings yet

- 20140630-A2384 ALTRONIXDocument30 pages20140630-A2384 ALTRONIXRicardo MercadoNo ratings yet

- PA Hidden FiguresDocument12 pagesPA Hidden FiguresJoya Jimenea GenzolaNo ratings yet

- 9591-102-102-PVM-U-009-02A Nox CalculationsDocument16 pages9591-102-102-PVM-U-009-02A Nox CalculationsVijay PalNo ratings yet

- Utilisation of Electrical Energy May 2008Document8 pagesUtilisation of Electrical Energy May 2008rajaniramNo ratings yet

- Android Chapter13 Multi ThreadingDocument42 pagesAndroid Chapter13 Multi ThreadingPrasad G. Kulkarni50% (2)

- Chapter 7 - Design FocusDocument2 pagesChapter 7 - Design FocusMegan Camaya100% (1)

- PDFDocument16 pagesPDFmayankNo ratings yet

- Bteq Fexp Fload MloadDocument59 pagesBteq Fexp Fload MloadShijuJohnNo ratings yet

- American Standard fl7tg Installation SheetDocument2 pagesAmerican Standard fl7tg Installation SheetJonn Denver NuggetsNo ratings yet

- Assessment PlanDocument2 pagesAssessment Planapi-282348214No ratings yet

- OxyGEN Router User's GuideDocument83 pagesOxyGEN Router User's Guidemakro100% (1)