Professional Documents

Culture Documents

Ramp Generators PDF

Uploaded by

PunithRossi0 ratings0% found this document useful (0 votes)

6 views22 pagesOriginal Title

RAMP GENERATORS.pdf

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

6 views22 pagesRamp Generators PDF

Uploaded by

PunithRossiCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 22

CHAPTER 7

Ramp

Generators

and Integrators

INTRODUCTION

A simple ramp generator circuit can be constructed using @ capacitor

charged via o resistonce, in conjunction with a discharge rensistor. To

improve the romp output linearity, @ transistor constant current circuit con

bbe employed. When the discharge is replaced by @ unijunction transistor,

the circuit becomes a relaxation oscillator. The bootstrap ramp generator,

which produces a closely linear romp, con be constructed using hansistor

for an IC operational amplifier. An IC operational amplifier con alvo be

‘employed in a Miller integrator.

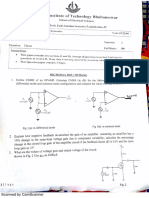

7-1 CR RAMP GENERATOR

‘The simplest ramp generator circuit is @ capacitor charged via a series

resistance. A transistor must be comnected in parallel with the eapacitor to

provide a discharge path, as shown in the citeuit of Figure 7-1(@). Capac

r fovtre

ouput £

Sm

Pry

Input

(©) Vottge waveforms

{or CR ramp geerston

Output

Yawn

4 aie

FIOURE 7.1. CRromp generator cist ond vohoge waveforms

166 ‘Chop. 7 RAMP GENERATORS AND INTEGRATORS

tor C; is charged [rom Voc via Ry. Q, is biased on via R, so the capacitor

is normally in a discharged state, When a negative-going input pulse is

‘coupled by C; to Q, base, the transistor switches off. Then, C, begins to

charge; this provides an approximate ramp output ntl the input pulse

fends [see Figure 7-1(b)). At this point, Q, switches on again, and rapidly

discharges the capacitor.

‘The output from a simple CR circuit is exponential rather than linear,

For voltages very much less than the supply voliage, however, the output is

‘approximately linear. When the transistor is on, the capacitor is discharged

0 Vertag: Hence, Veriag is the starting level of the output ramp. Output

amplitude control can be provided by making the charging resistance (R,)

adjustable.

Capacitor Cy, which couples the input pulse to the transistor base,

should be selected as small as possible, both for minimum cost and

smallest possible physical size. The minimum suitable size can be de-

termined by allowing the base voltage of Qj; to rise during the input pulse

time, as shown in Figure 7-1(b). The base Voltage starts approximately at

0.7 V when Q, is on. Then, Vp3 is pulled negative by the input pulse, but

starts to rise again as C, is charged through Ry. To ensure that Q, is still

off a the end of the pulse time, Vy should not rise above —0.5 V. This

approach to coupling capacitor selection is outlined in See. 5-2.

EXAMPLE 7-1

Design a simple CR ramp generator to give an output that peaks at 5 V.

The supply voltage is 15 V, and the load to be connected at the output is

100 k@. The ramp is to be triggered by a negative-going pulse with an

amplitude of 3 V, PW=1 ms, and the time interval between pulses is 0.1

ims. Take the transistor hpgiaiy 8850.

solution

‘This circuit is shown in Figure 7-1(a). The maximum output current is

Select the minimum capacitor charging current I,>>Tigmag- At peak output

vr

voltage, let

Ly 100% I,

=100x50pA=5 mA

Veo=Vp

er

Isv—sv

SFR T2R@ (use 2.2 kO standard value)

‘The voltages for capacitor C, are

Initial voltage= 2,0

Final voltage=e,=5 V

(Charging voltage E= Voc 15 V

E-(E-E, Je [Equation (2-2)]

‘The discharge time for C is 0.1 ms, which is one-tenth of the charging

time. For Q, to discharge Cin the specified time,

210% (C; charging current)

I5V-0.7V

T mA,

3k@ (use 128 standard value)

v8 ‘Chop. 7 RAMP GENERATORS AND INTEGRATORS,

For Q, to remain biased off at the end of the input pulse, let Vy=

-05V.

AV=V;-Vae~Va [See Figure 7-1(b)]

=3V-0.7V—05V=18V

‘The charging current for C, is equal to the current through Ry when Q, is

ff:

_ 1SV-(-3)

ET

From Equation (2-7):

LS mAX1 ms

TaV

0.83 4F (use 1 pF standard value)

7-2, CONSTANT CURRENT RAMP GENERATORS

7-2.1 Bipolar Transistor Constant Current Circuits

‘The major disadvantage of the single CR ramp generator is its nonlinear-

. To produce a linear ramp, the capacitor charging current must be held

constant. This can be achieved by replacing the charging resistance with a

constant current circuit

AA basic transistor constant current circuit is shown in Figure 7-2(a).

‘The potential divider (Rand R,) provides a fixed voltage Vat the base

of pp transistor Q,. The voltage across the emitler resistor Ry retuains

constant at (¥,—Vyg). Thus, the emitter current is also constant: Zy=(V

=Vag)/Ra. Since Tey, the collector current remains constant. Figure

7-205) shows an arrangement that allows the level of constant current 10 be

adjusted. R, provides adjustment of Vy. Since Vy=(Vq—Vap), ¥5 als is

adjustable by Rg, and Ip can be set to any desized level over & range

‘dependent upon Re.

Figure 7.2(@) shows a ramp generator that employs the constant

current creut, Note that because Ze of is «constant charging current

‘Sec. 7-2. CONSTANT CURRENT RAMP GENERATORS, 169

(4) Constant curent circuit (©) Adjstabt constant cure scale

FHOURE 7.2. Trontitor Raed end adjunabeconson caret cre,

for C4; the capacitor voltage Vo grows linearly. The simpler capacitor-

charging equation, Equation (2-, may now be used for C, ealeulations,

‘The circuit of Figure 73a) functions like the simple CR ramp generator,

‘with R, replaced by the constant current circuit,

‘The output voltage from the constant current ramp generator remain

linear only if a sufficient voltage is maintained across Q, for it to operate

in the active region of its characteristics. If Qy teaches saturation, the

‘output stops at a constant level. Therefore, Ver2 should not fall below

about 3 V. Because of this and the constant vollage V, acrose resistor Re,

the maximum ramp output voltage obtainable from the cireuit of Figure

73 is approximately Vo= Vcc ¥y~3 V.

In the circuit of Figure 7-3(6) the input pulse is directly connected to

the base of transistor Q,. When the input is at ground level, 0, is off and

capacitor Cy charges vin 3. When a positive input is applied, Q, is

switched on and C; is rapidly discharged. Q, remains on during the positive

input pulse; thus C, is held in a discharged condition, and the ramp

Senerator output voltage remains at the Veryay Of Oy

EXAMPLE 7-2 a

Using a constant current circuit, modify the ramp generator designed in

Example 7-1 to produce a liness ramp output.

(2) Constant cument ramp generator with capaitorcouped input

-— fee

Ry &

2

(6) Constant current ramp generator wth acct coupled np

FIGURE7-3. Conon caren! rmp generators

Sec. 7-2 CONSTANT CURRENT RAMP GENERATORS, m

solution

Refer to the circuit of Figure 7-34.

Vocmany=5 V

V+ Ves=Voc-5 V=10V

Let

Vers™3 V, minimum

then

W=10V-3V=7V

To maintain a constant level of Ty (and J), the voltage across Ry should

‘be several times larger than the base emitter voltage V5. This ensures that

changes in Vz, do not significantly affect 1,

a

w

For Cy=1 xF, V=5 V, and =i ms,

tot xs Vas mA

4k (use 1.2 kA standard value)

mAXI.2KQ

=6v

Vim Vat Veg V40.7 V

=67V

¥; must be a stable bias voltage unaffected by J_,. Make J,=tg=5 mA.

R=

61

3mA

= 1340 (use 1.2.k0 standard value)

Redesign the circuit of Example 7-2 to make the ramp amplitude adjuste-

ble from 3 V to 5 V.

‘The circuit modification is shown in Figure 7-2(b). The charging current,

with AV=3 V, is

For AV=5V,

For I=3 mA, Ip~3 mA and

Vom fpxRy=} MAXI IED

sv

WinVitVs,

=43v

6Y+0.7

(At this point, the moving contact on the potentiometer is at the upper

end)

Sec.7-2_ CONSTANT CURRENT RAMP GENERATORS, vw

For R)=12 ko,

For J=3 mA,

VymSmAX12k0

v

and

v6.7

(At this point the potentiometer moving contact is at the lower end.)

Wye VitVe

V6.1 V-3.6V3.1¥

and

Voom Va- Ma

=15V-43 V-3.6V

env

(use 2.2 kM standard value)

m4 ‘Chop. 7 RAMP GENERATORS AND INTEGRATORS,

7-22 FET Constant Current Circuits

A field effect transistor with a single source resistance can function as a

constant current circuit. A p-channel FET is shown in Figure 7-4(a) with «

resistor connected between the source terminal and Voc. With the gate

terminal also connected to Vac, the gate-source voltage is the voltage drop,

across Rs, Which is [ys oF Ip Rg. Referring to the FET transconductance

characteristics in Figure 7-4(b), the desired drain/source current (/,) ean

be selected and the corresponding gate-source voltage (V5) determined as

illustrated. Then,

Yas

Ts

cy

This approach is saistactory only when the transconductance char=

acteristic forthe particular FET has been plotted. For any given FET type,

there are two possible extreme characteristics as shown in Figure 7A),

‘These occur because of the spread in values of dhain-source saturation

current Upssimuy 224 Fosse h 4 pinchoffcoltage ray 204 Fray)

In this case tis necessary To draw a Bas fine for each posible valve of

source resistance, This is done simply by using Equation (7-1) to determine

two convenient corresponding valuer of Ip and Voq:

When Ves

h

Vgs/Rg=0

Plot point A on Figure 7-4(¢) at Vos:

‘When V,5=6 V and R,=3.3 KO,

Ip=6V/33k0=18 mA

and Jp:

Plot point # on Figure 7-4(c) at Vgg=6 V and [p= 1.8 mA.

Draw the bias line through points a and B. The maximum and minimum

source current levels that can flow are now shown at the intersections of

the bias lines and the characteristics, When it is desired to set Ig to a

precise level Rg must be made adjustable.

‘One important caution that must be observed when using a FET

‘constant current circuit is that the drain-source voltage Ving must not be

allowed to fall below the maximum value of pinch-off voltage Vejaay Just

as a bipolar transistor cannot be expected to function linearly if its

collector-base voltage approaches the saturation level, so too a FET will

not function correctly in a Hinear circuit if ite drain-source voltage falls

below the pinch-off level.

a rr et

a] jt ‘|?

ro]

(2) FET constant coment cet

covewa=ai °

lao Tas

(©) PET tansconductane characteristics

(¢) FET meximum and minimum

leansoondctancecharctsntcs

OURE7-4, FET contont eurant eit nd Womconcitene coro.

1% ‘Chop. 7 RAMP GENERATORS AND INTEGRATORS,

A constant current diode (ot field effect diode) is essentially a FET and a

resistor connected as illustrated in Figure 7-4(a), and contained in a single

package. These devices can be purchased with various constant current

levels

7-3, UST RELAXATION OSCILLATORS

7-3.1 The Unijunction Transistor

‘The basic construction of a unijunction transistor (UFT) and its equivalent

circuit are shown in Figure 7-5. The device can be thought of asa bar of

lightly doped mtype silicon with a small piece of heavily doped p-type

Joined to one side [sce Figure 7-5(a)]. The p-type is named the emitter,

while the two end terminals of the bar are designated bases 1 and 2 (B,

and B,), as shown. In the equivalent circuit of Figure 7-5(b), the silicon

bar is represented as two resistors, rg and rp, while the pr junction formed

by the emitter and the bar is represented by-a diode.

(0) Equivalent citait

FIOUREY.3. Roi constuction and equivalent el a unoncion enor,

Sec. 7-9 UIT RELAXATION OSGLLATORS 7

The ratio, ru/(rm-rq) is termed the intrinsic standoff ratio of the

UT, and is desigaatedm. Thus the voltage cross ry lt ven by

"=" —

Fn

Yao (7)

‘The pn junction becomes forward-biased ata peak volage, Ve Vz

=¥+ Vy, When this peak is reached, the flow of charg carios irae

aus its resistance to fall Thus, a capacitor connected across E and

1s rapidly dstharged, The flow of current into the emitter teminal

continues uni Vy falls to the enter sotwation eoltage Venger, at hich

time the device switches of.

“Two more important parameters for the UST are peak point curren Ip

and the valley point current ly. The peak point curtent is the inizimurs

emitter current that most flow for the UIT to switch on or fre. This

furrentoocurs when Vis atthe fring vollage, that i, at peak poiat Pr

‘The valley point current isthe emitter current that flows when Vir at te

emitter saturation voltae, Fzziay

7-32 UST Relaxation Oscillator

‘A unijunction transistor can be used in conjunction with a capacitor and a

charging circuit, to construct an oscillator with an approximate rammp-type

‘output, Figure 7-6(a) shows the simplest form of such a circuit, which is

called @ UIT relaxation oscitator. The UST remains off until is emiter

voltage Vea: approaches the firing voltage V for the particular deviee. At

this point, the UIT switches on and a large emitter current J, flows. This

‘causes capacitor C, to discharge rapidly. When the capacitor voltage falls

to the emilter saturation level, the UST switches off, allowing C; to begin

to charge again,

The frequency of a relaxation oscillator can be made variable by

switched selection of capacitors and/or by adjustment of the charging

resistance [see Figure 7-6(b)}. The resistance 2, in series with UIT

ferminal 2, allows synchronizing input pulses to be applied. When an

input pulse pulls &, negative, Vg, is increased to the level at which the

‘UIT fires. Once the UIT fies it will not switch off again until the capacitor

is discharged.

(Chap. 7 RAMP GENERATORS AND INTEGRATORS,

LM

Fesivuny T -

Syachronisng

pubes

(0) Vasile requeney UIT el

FIOURE 7-6. tose UIT relaxation oxlitar and vorabl equency cc,

In the design of « UIT relaxation oscillator, the charging resistance R

‘aust be selected between certain upper and lower limits, Resistance Ri

‘aust not be so large that the emitter current is less than the peal roint

current when Vzq; is at the firing voltage: otherwise, the device may not

switch on. If R, is very small, then when Vzpy is at the emitter saturation

fevel, a current greater than the valley point current

See.7-9 UIT RELAXATION OSCLLATORS 7

‘emitter terminal. In this ease, the UIT may not switeh off. Thus, for

correct UST operation, Ry must be selected between two limits that allow

the emitter current to be a minimum of fp and a maximum of I,,

The UIT oscillator circuits shown ‘in Figures 7-6) and’ (b) will

produce exponential output waveforms because the capacitors are charged.

by resistances. Constant current circuits could be used here to generic

linear ramp output waveforms

ANU 76)

‘The circuit of Figure 7-6(a) is to use a 2N3980 UFT. The supply voltage

Vay is 20 V, and output frequency is to be 5 kHz. Design a suitable circlt,

and caleulate the output amplitude.

sotlon

Capacitor Cy charges from Vegan to the fring voliage, Vp—V-+nVqy.

The data sheet for the 2N3986" (Appendix I-12) gives the follow

specifications:

Veaey=3V maximum, T=2pA, 1,

and

90.68 10 0.82

0.75 average.

¥,=0.7+(0.75%20V)

<5

Supply voltage=Vg=20 V

E,= Initial charge= Ven

Now, to select R,

_20V-15.1

TRA

180 (Chop. 7 RAMP GENERATORS AND INTEGRATORS.

Tima

‘So R; must be in the range 17 k@ to 2.15 MQ. If R, is very large, C, must

be a very small capacitor. Let R, have a value of 22k!

then fom

atsion 22)

phe

You might also like

- Large and Fast: Exploiting Memory HierarchyDocument75 pagesLarge and Fast: Exploiting Memory HierarchyPunithRossiNo ratings yet

- Larry EllyDocument9 pagesLarry EllyPunithRossiNo ratings yet

- 5.risk and ReturnDocument18 pages5.risk and ReturnPunithRossiNo ratings yet

- Chapter 2 Accounting Review: Income Statements and Balance SheetsDocument50 pagesChapter 2 Accounting Review: Income Statements and Balance SheetsnajmulNo ratings yet

- Eurozone CrisisDocument29 pagesEurozone CrisisPunithRossiNo ratings yet

- Greening GrowthDocument79 pagesGreening Growthvanhung2809No ratings yet

- VEHICLE SCHEDULE W.E.F. 23.07.2018: Traveler Schedule On Working Days Bus Schedule On Working DaysDocument1 pageVEHICLE SCHEDULE W.E.F. 23.07.2018: Traveler Schedule On Working Days Bus Schedule On Working DaysPunithRossiNo ratings yet

- Large and Fast: Exploiting Memory HierarchyDocument75 pagesLarge and Fast: Exploiting Memory HierarchyPunithRossiNo ratings yet

- Chapter 2 Accounting Review: Income Statements and Balance SheetsDocument50 pagesChapter 2 Accounting Review: Income Statements and Balance SheetsnajmulNo ratings yet

- Mitacs Globalink Reference Letter Instructions June2016 PDFDocument1 pageMitacs Globalink Reference Letter Instructions June2016 PDFpreeteshNo ratings yet

- EPIndexreport of Yaleunvereisty2012Document50 pagesEPIndexreport of Yaleunvereisty2012PunithRossiNo ratings yet

- Business Planning ProcessDocument29 pagesBusiness Planning ProcessPunithRossiNo ratings yet

- VEHICLE SCHEDULE W.E.F. 23.07.2018: Traveler Schedule On Working Days Bus Schedule On Working DaysDocument1 pageVEHICLE SCHEDULE W.E.F. 23.07.2018: Traveler Schedule On Working Days Bus Schedule On Working DaysPunithRossiNo ratings yet

- Sustainable Development in India: Perspectives by - Sunderlal BahugunaDocument10 pagesSustainable Development in India: Perspectives by - Sunderlal BahugunajeevandohifodeNo ratings yet

- CamScanner Scans PDFs from PhotosDocument5 pagesCamScanner Scans PDFs from PhotosPunithRossiNo ratings yet

- Resume IITBomayDocument1 pageResume IITBomayPunithRossiNo ratings yet

- Classtest Solutions TSMDocument4 pagesClasstest Solutions TSMPunithRossiNo ratings yet

- FLAT CurriculumDocument1 pageFLAT CurriculumPunithRossiNo ratings yet

- Theory of Computing: MAS 714 Hartmut KlauckDocument27 pagesTheory of Computing: MAS 714 Hartmut KlauckPunithRossiNo ratings yet

- Assignment 2Document6 pagesAssignment 2PunithRossiNo ratings yet

- Mannipaya LyricsDocument3 pagesMannipaya LyricsPunithRossiNo ratings yet

- Station IslandDocument246 pagesStation Islandpiej1209No ratings yet

- Transducer, Sensors and Measurement (EE2L002) Assignment 3Document2 pagesTransducer, Sensors and Measurement (EE2L002) Assignment 3PunithRossi0% (1)

- RAM StatementsDocument11 pagesRAM StatementsPunithRossiNo ratings yet

- CamScanner Scans PDF DocsDocument6 pagesCamScanner Scans PDF DocsPunithRossiNo ratings yet

- Notes 326 Set8Document16 pagesNotes 326 Set8Bakshi AmitNo ratings yet

- Signals and Systems - Assignment 01 - Signal RepresentationsDocument7 pagesSignals and Systems - Assignment 01 - Signal RepresentationsVIVEK100% (1)

- Digital CountersDocument6 pagesDigital CountersPunithRossiNo ratings yet

- WienbrDocument5 pagesWienbrahimpliNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)