Professional Documents

Culture Documents

Analysis and Characterization of Various Current Mirror Topologies in 90 NM Technology

Uploaded by

Gurinder Pal SinghOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Analysis and Characterization of Various Current Mirror Topologies in 90 NM Technology

Uploaded by

Gurinder Pal SinghCopyright:

Available Formats

International Journal of Emerging Technology and Advanced Engineering

Website: www.ijetae.com (ISSN 2250-2459, ISO 9001:2008 Certified Journal, Volume 2, Issue 12, December 2012)

Analysis and Characterization of Various Current Mirror

Topologies in 90 nm Technology

Jaydeep Chikani1, Parag Chaudhari2, Prof. Vijay Savani3

1,2

B.Tech. Student, Institute of Technology, Nirma University, Gujarat, India

Asst. Professor, EC Department, Institute of Technology, Nirma University, Gujarat, India

Abstract Although large electronic systems can be

constructed almost entirely with digital techniques, many

systems still have analog components and current mirror is

the core structure for almost all analog and mixed mode

circuits. It determines the performance of analog structures,

which largely depends on their characteristics. In this paper,

we have analyzed various topologies of current mirror using

90 nm technology in Mentor Graphics and compared them

based on different parameters like power dissipation,

minimum output voltage, bandwidth, transfer characteristics

etc.

Fig. 1 Current Mirror Symbols (a) NMOS Current Mirror (b) PMOS

Current Mirror

Current mirrors mimic the performance of an ideal

current source. Therefore their designs must fulfill the

following requirements. [3]

Input impedance should be zero.

Output impedance should be infinite.

Output current should be constant over wide swing of

voltage

Accurate copy of input current.

The paper is organized as follows: Various current

mirror topologies are described in section II. The

simulation results are discussed in section III. The paper is

concluded in section IV.

Keywords Current Mirror, Excess gate voltage,

Minimum output voltage, MOSFET, Output impedance,

Power dissipation, Transfer characteristics

I. INTRODUCTION

A two terminal circuit whose output current is

independent of the output terminal voltage and depends

only on the input current is called current mirror.

Generally, it is used to generate a replica of given reference

current. If necessary, it can also amplify or attenuate the

reference current. A current mirror can be thought as a

current controlled current source. Ideally, the output

impedance of a current source/sink should be infinite and

capable of generating or drawing a constant current over a

wide range of voltages. However, finite value of output

resistance and a limited output voltage required to keep

device in saturation will ultimately limit the performance of

the current mirror. Current mirror is used for biasing,

loading, current amplification etc. Current mirrors are

employed in many applications such as operational

amplifiers, analog to digital and digital to analog

converters.

Fig. 1 shows the symbols of current mirror circuits in

which arrow is used to designate the direction of the

current flow on the input side. The ratio 1: K represents the

current gain of the mirror circuit. [4]

II. TOPOLOGIES OF CURRENT MIRROR

A. Basic Current Mirror

Fig. 2 shows the basic current mirror. A current flows

through M1 corresponding to VGS1. Since VGS1 = VGS2,

ideally the same current, or a multiple of the current in M1,

flows through M2. If the MOSFETs are of the same size,

the same drain current flows in each MOSFET, provided

M2 stays in the saturation region[1]. The current through

M1 can be given by,

I D1

1

(VGS1 VTHN )2

2

The output current, assuming M2 in saturation is given

by

I D 2 IO

151

2

(VGS 2 VTHN )2

2

International Journal of Emerging Technology and Advanced Engineering

Website: www.ijetae.com (ISSN 2250-2459, ISO 9001:2008 Certified Journal, Volume 2, Issue 12, December 2012)

Fig. 2 Basic Current Mirror

Fig. 3 Double Cascode Current Mirror

Since VGS1=VGS2, the ratio of the drain currents is

ID2

I D1

Fig. 4 shows the small signal model for double cascode

current mirror. The output resistance of the double cascode

current source is given by

W2

L

2 2

1 W1

L1

Ro ro4 (1 gm4ro2 ) ro2 gm4ro2

The desired output current can be obtained by adjusting

W/L ratios of two devices.[1]

Here it is required that M2 remains in saturation.

Therefore the minimum output voltage across the current

mirror is given by Vmin=VDS(SAT)=VGS-VTHN. The output

resistance of current mirror is equal to output resistance of

M2.

ro

1

I o

The simulation results are shown in fig. 8a and 8b. Fig.

8a shows AC analysis. Transfer characteristic is shown in

fig. 8b. Transfer characteristic is not exactly linear. It is of

curved shape because of small scale effects. Output

resistance of basic current mirror is very low. But it

possesses larger bandwidth compared to other topologies.

Fig. 4 Small-signal model of Double Cascode Current Mirror

C. Triple Cascode Current Mirror

Output impedance can be further increased by adding

one more stage to double cascode configuration.[1] Triple

cascode configuration is shown in fig. 5.

B. Double Cascode Current Mirror

Double cascode configuration is used to increase the

output resistance of a current source or sink. Fig. 3 shows

schematic diagram for this configuration. If we define V

as excess gate-source voltage, the gate voltage of M4 is

2(V+VTHN) and source voltage is V+VTHN. The

minimum voltage across the current sink is limited by the

requirement that M4 remains in the saturation region.

VDS4 VGS4 -VTHN or VD4 2V+VTHN [1]. This minimum

voltage across the cascode current mirror is significantly

larger than the minimum voltage across the basic current

mirror.

Fig. 5 Triple Cascode Current Mirror

152

International Journal of Emerging Technology and Advanced Engineering

Website: www.ijetae.com (ISSN 2250-2459, ISO 9001:2008 Certified Journal, Volume 2, Issue 12, December 2012)

The minimum output voltage for triple cascode

configuration is given by 3V+2VTHN.[2] Output

impedance can be found by applying small signal model at

output side and is given by,

The minimum output voltage for regulated cascade is

given by VDS3(sat). The small-signal model is shown in fig.

7. The output impedance can be given by,

Rout g m 2 g m 4 (ro1 ro 2 )ro 3ro 4

Ro gm6 g r

3

m4 o

Where gm4 and gm6 is trans-conductance of M4 and M6

respectively and ro is output impedance of each MOSFET.

g m2 ro3

2

Where gm is trans-conductance for particular MOSFET

and ro is output impedance.

D. Regulated Cascode Current Mirror

This configuration uses negative feedback concept to

stabilizes the output current Io. This configuration is shown

in fig. 6.

III. SIMULATIONS RESULTS

All the above proposed topologies were simulated using

90 nm technology. Simulation results were taken with the

help of Pyxis Schematic tool provided by Mentor

graphics.

For analog design it is extremely important to keep

output resistance as high as possible. It is also important to

reduce the effect of channel length and mobility

modulation. These effects are reduced by increasing the

channel length of devices. We have taken the channel

length equals to 100 nm for all the MOSFETs used in each

topology due to above reasons. Their widths may vary

according to need and topology.

For our simulation values of different parameters are as

follows: VTHN = 0.228 V, VTHP = -0.2038 V, VGS = 0.35 V,

VDD = 0.9 V, VSS = -0.9 V, I0 = 10 A, = 0.84 V-1.

A. Basic Current Mirror

This topology does not provide high output impedance.

But it provides very high bandwidth as shown in fig. 8a. It

is also seen that output current is not perfectly following

the input current form fig. 8b. Transfer characteristic is

nonlinear in nature.

Fig. 6 Regulated Cascode Current Mirror

MOSFETs M2 and M4 provides negative feedback

while, M1 and M3 form current mirror.[1]Here, the

voltages VBias1 and VBias2 are applied in such a way that

only constant current can pass through M1 and M3

respectively. If output current increases due to some

reason, voltage at node-A rises since only constant current

can pass through M3. So it increases current through M2,

but because of VBias1, current cannot increase for M1. This

results in decrease in voltage at node-B. Thus, excess

current from M4 is absorbed by M2 and it balances the

output current Io.

Fig. 8a AC Characteristic of Basic Current Mirror

Fig. 7 Small-signal model for Regulated Cascode Current Mirror

153

International Journal of Emerging Technology and Advanced Engineering

Website: www.ijetae.com (ISSN 2250-2459, ISO 9001:2008 Certified Journal, Volume 2, Issue 12, December 2012)

Fig. 9b Transfer characteristic of Double Cascode Current Mirror

Fig. 8b Transfer characteristic of Basic Current Mirror

B. Double Cascode Current Mirror

This topology provides high output resistance than basic

configuration but it requires comparably high minimum

output voltage. It provides less bandwidth than basic

configuration as shown in fig. 9a. Output current is

effectively following the input current which can be seen

from fig. 9b. Still transfer characteristic is quite non-linear.

Fig. 10a AC Characteristics of Triple Cascode Current Mirror

Fig. 9a AC Characteristics of Double Cascode Current Mirror

C. Triple Cascode Current Mirror

This topology provides same results as double cascade.

The minimum output voltage required to keep output

device in saturation is higher than double cascade current

mirror. Bandwidth is increased by some amount as shown

in fig. 10a. Transfer characteristic is shown in fig. 10b.

Fig. 10b Transfer characteristic of Triple Cascode Current Mirror

154

International Journal of Emerging Technology and Advanced Engineering

Website: www.ijetae.com (ISSN 2250-2459, ISO 9001:2008 Certified Journal, Volume 2, Issue 12, December 2012)

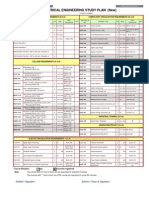

TABLE I

COMPARISON AMONG VARIOUS PARAMETERS

Topology

Minimum output

Voltage

Bandwidth

Power Dissipation

Output Resistance

Basic Current Mirror

0.122 V

5.89 GHz

34.84 W

119 K

Double Cascode Current

Mirror

0.472 V

2.59 GHz

32.84 W

2.32 M

Triple Cascode Current

Mirror

0.822 V

2.95 GHz

31.70 W

45.26 M

Regulated Cascode

Current Mirror

0.122 V

659 MHz

102.68 W

22.63 M

D. Regulated Cascode Current Mirror

Negative feedback provides optimization between output

resistance and minimum output voltage. It provides less

bandwidth compared to double and triple cascade

configurations and is shown in fig. 11a. The transfer

characteristics is linear for small input current, but for

larger value of current it becomes non-linear as shown in

fig. 11b.

Fig. 11b Transfer characteristic of Triple Cascode Current Mirror

Different current mirror topologies have their own

advantages and disadvantages. Minimum output voltage

and output impedance are the two most important

parameters for any current mirror topology. Output

impedance can be increased by stacking more and more

number of stages in basic current mirror. The consequence

is the increase in minimum output voltage. Hence there is a

trade-off between output impedance and minimum output

voltage required.

From table 1 it is clear that basic current mirror provides

very high bandwidth and possesses lowest minimum output

voltage, but has very low output impedance. Double

cascode and triple cascode current mirror possess very high

output impedance, but they require higher minimum output

voltage compared to basic current mirror topology.

Fig. 11a AC Characteristics of Regulated Cascode Current Mirror

IV. CONCLUSION

The design of current mirrors is one of the most

challenging aspects in the analog and mixed signal design.

In this paper we have analysed various current mirror

parameters like minimum output voltage, output

impedance, bandwidth etc. for different topologies in 90

nm technology.

155

International Journal of Emerging Technology and Advanced Engineering

Website: www.ijetae.com (ISSN 2250-2459, ISO 9001:2008 Certified Journal, Volume 2, Issue 12, December 2012)

Regulated cascode current mirror topology comprises

negative feedback technique to provide stable output

current. It possesses optimum values for almost all

parameters compared to other topologies.

In 90 nm technology, due to small-scale effects found in

MOSFETs, current mirrors behave non-linearly. This nonlinearity decreases from basic current mirror topology to

higher topologies. Operating bandwidth of current mirror is

very high for 90 nm technology.

REFERENCES

[1]

[2]

[3]

[4]

156

R. Jacob Baker, Harry W. Li, and David E. Boyce, CMOS Circuit

Design, Layout and Simulation, 2005.

P. E. Allen and D. R. Holberg, CMOS Analog Circuit Design,

Oxford University Press, 2002.

Franco Maloberti, Analog Design for CMOS VLSI systems, Kluwer

Academic/Plenum Press, 1998.

Manish Tikyani and Rishikesh Pandey, A New Low-Voltage

Current Mirror With Enhanced Bandwidth, IEEE paper.

You might also like

- V2I300142Document3 pagesV2I300142editor_ijarcsseNo ratings yet

- Analysis of Low Voltage Bulk-Driven High Swing Cascode Current Mirrors For Low Voltage ApplicationsDocument10 pagesAnalysis of Low Voltage Bulk-Driven High Swing Cascode Current Mirrors For Low Voltage ApplicationsIJRASETPublicationsNo ratings yet

- ECC508 Electronics Engineering Lab - II - VLSIDocument40 pagesECC508 Electronics Engineering Lab - II - VLSIRAJA RAMALINGAMNo ratings yet

- Simulation and Analysis of Bulk Driven Circuits For Low Power ApplicationsDocument4 pagesSimulation and Analysis of Bulk Driven Circuits For Low Power ApplicationsAbhishek MatNo ratings yet

- A Low-Voltage Current Conveyor Using Inverter-Based Error Amplifier and Its Oscillator ApplicationDocument7 pagesA Low-Voltage Current Conveyor Using Inverter-Based Error Amplifier and Its Oscillator ApplicationAshin AntonyNo ratings yet

- New CMOS Voltage Divider Based Current Mirror, Compared With The Basic and Cascode Current MirrorsDocument6 pagesNew CMOS Voltage Divider Based Current Mirror, Compared With The Basic and Cascode Current MirrorsvlsijpNo ratings yet

- Analysis of Different Types of Current Mirror in 45nm TechnologyDocument5 pagesAnalysis of Different Types of Current Mirror in 45nm TechnologyesatjournalsNo ratings yet

- Comparative Analysis of Different Current Mirror Using 0.35 M and Its ApplicationDocument5 pagesComparative Analysis of Different Current Mirror Using 0.35 M and Its ApplicationaliNo ratings yet

- Unipolar and Bipolar SPWM Voltage Modula PDFDocument5 pagesUnipolar and Bipolar SPWM Voltage Modula PDFĐorđe ĐurđićNo ratings yet

- DC-DC Boost Converter Design Asmarashid Ponniran 2009Document6 pagesDC-DC Boost Converter Design Asmarashid Ponniran 2009Sigit KurniawanNo ratings yet

- Self Biased Cascode CM PDFDocument7 pagesSelf Biased Cascode CM PDFDhaval ShuklaNo ratings yet

- Design of A Linear and Wide Range Current Starved Voltage Controlled Oscillator For PLLDocument8 pagesDesign of A Linear and Wide Range Current Starved Voltage Controlled Oscillator For PLLJames MorenoNo ratings yet

- High Speed, Low Power Current Comparators With Hysteresis: Neeraj K. ChastaDocument12 pagesHigh Speed, Low Power Current Comparators With Hysteresis: Neeraj K. ChastanengsintanovitaNo ratings yet

- SM7020Document17 pagesSM7020BenoitDeCoomanNo ratings yet

- Single Phase Asymmetrical Cascaded Multilevel Inverter Design For Induction MotorDocument6 pagesSingle Phase Asymmetrical Cascaded Multilevel Inverter Design For Induction Motorfarid kerroucheNo ratings yet

- Lab 4Document5 pagesLab 4Sudhanshu SrivastavaNo ratings yet

- 2002apr08 Icd Amd Pow TacDocument9 pages2002apr08 Icd Amd Pow TacMihaela CaciumarciucNo ratings yet

- Realization of Voltage Mode Universal Filter by Using Single Differential Voltage Current Conveyor Transconductance AmplifierDocument4 pagesRealization of Voltage Mode Universal Filter by Using Single Differential Voltage Current Conveyor Transconductance AmplifierijsretNo ratings yet

- Performance Analysis of PWM Based Full Wave Bridge InverterDocument9 pagesPerformance Analysis of PWM Based Full Wave Bridge InverterIJRASETPublicationsNo ratings yet

- DC-to-DC Power Converter by Rodney Yeu and Sudip Kundu ECE 345 Section H TA: Jon Wheeler 4/26/02 Project #34Document22 pagesDC-to-DC Power Converter by Rodney Yeu and Sudip Kundu ECE 345 Section H TA: Jon Wheeler 4/26/02 Project #34Harkishen SinghNo ratings yet

- Comparison of Current Mirror Circuits Using Pspice Simulation ToolDocument4 pagesComparison of Current Mirror Circuits Using Pspice Simulation Toolsuyash_4376No ratings yet

- Solar Powered Simplified Multilevel InverterDocument8 pagesSolar Powered Simplified Multilevel InverterAnney RevathiNo ratings yet

- Second Generation Current ConveyorDocument4 pagesSecond Generation Current Conveyormuhammad_andinovaNo ratings yet

- CMOS Implemented VDTA Based Colpitt OscillatorDocument4 pagesCMOS Implemented VDTA Based Colpitt OscillatorijsretNo ratings yet

- Variable Power SupplyDocument27 pagesVariable Power SupplyDharang ShahNo ratings yet

- The International Conference On Renewable Energies: "ICRE-2010"Document30 pagesThe International Conference On Renewable Energies: "ICRE-2010"M VetriselviNo ratings yet

- Diffrential Amplifier 2Document5 pagesDiffrential Amplifier 2jaigodaraNo ratings yet

- Regulated Power SupplyDocument19 pagesRegulated Power SupplyRonn Albert GabucayNo ratings yet

- 300 Level Alternativev To PracticalDocument6 pages300 Level Alternativev To PracticalDjNo ratings yet

- International Journal of Computational Engineering Research (IJCER)Document7 pagesInternational Journal of Computational Engineering Research (IJCER)International Journal of computational Engineering research (IJCER)No ratings yet

- An0002 Efm32 Hardware Design ConsiderationsDocument16 pagesAn0002 Efm32 Hardware Design ConsiderationsRam SakthiNo ratings yet

- Ch. No Chapter Name Page NoDocument27 pagesCh. No Chapter Name Page NoSruthi ReddyNo ratings yet

- Underground Fault LocatorDocument12 pagesUnderground Fault LocatorMadan PragadaNo ratings yet

- Sowparnika 8Document8 pagesSowparnika 8ulaganathanNo ratings yet

- Design and Construction of A Low DC Voltage Power Supply UnitDocument28 pagesDesign and Construction of A Low DC Voltage Power Supply UnitRasaq Eneji Jimoh100% (1)

- AN521 Intoduction To IGBTDocument10 pagesAN521 Intoduction To IGBTBuelnitaNo ratings yet

- Multilevel Inverter With Reduced Number of Switches: Arun - Thorat@ritindia - EduDocument5 pagesMultilevel Inverter With Reduced Number of Switches: Arun - Thorat@ritindia - EduagastinNo ratings yet

- 1Document30 pages1sreevatsakurudiNo ratings yet

- Modular Multilevel Converter Control Strategy With Fault ToleranceDocument6 pagesModular Multilevel Converter Control Strategy With Fault TolerancesatyacvaNo ratings yet

- Statcp, XdsadsadsadasasdsadsadsadsadsadsadsadDocument6 pagesStatcp, Xdsadsadsadasasdsadsadsadsadsadsadsadrathorsumit2006No ratings yet

- Iceict2015i020315001 PDFDocument6 pagesIceict2015i020315001 PDFmadihaNo ratings yet

- Performance Analysis of Multi-Level Inverter For Dynamic Voltage RestorerDocument6 pagesPerformance Analysis of Multi-Level Inverter For Dynamic Voltage Restorersup9No ratings yet

- Design and Simulation of RF Energy Extracting Circuits and SystemDocument28 pagesDesign and Simulation of RF Energy Extracting Circuits and SystemHaresh SinghNo ratings yet

- Viper22a Equivalent PDFDocument16 pagesViper22a Equivalent PDFXande Nane Silveira0% (1)

- Microchip CLC DescriptionDocument12 pagesMicrochip CLC DescriptionKamlesh YadavNo ratings yet

- A Modified Seven Level Cascaded H Bridge InverterDocument6 pagesA Modified Seven Level Cascaded H Bridge InverterMary NdhlovuNo ratings yet

- Design of A Low-Dropout Linear RegulatorDocument4 pagesDesign of A Low-Dropout Linear RegulatorParindraNo ratings yet

- Accident AlertDocument35 pagesAccident AlertChandra SekarNo ratings yet

- IGCT Technology Baseline and Future Opportunities: Peter Steimer, Oscar Apeldoorn, Eric Carroll, Andreas NagelDocument6 pagesIGCT Technology Baseline and Future Opportunities: Peter Steimer, Oscar Apeldoorn, Eric Carroll, Andreas NagelculwavesNo ratings yet

- Fast Transient Low-Dropout Voltage Regulator With Hybrid Dynamic Biasing Technique For Soc ApplicationDocument6 pagesFast Transient Low-Dropout Voltage Regulator With Hybrid Dynamic Biasing Technique For Soc ApplicationNguyen Van ToanNo ratings yet

- Digital Object Counter Using MicrocontrollerDocument60 pagesDigital Object Counter Using MicrocontrollerKishan Amara82% (22)

- An-9014-Fairchild QFET For Synchronous Rectification DC To DC Converters - ImpDocument16 pagesAn-9014-Fairchild QFET For Synchronous Rectification DC To DC Converters - ImpbmmostefaNo ratings yet

- Electronics 08 01137 v2Document14 pagesElectronics 08 01137 v2sigit kurniawanNo ratings yet

- Design and Implementation of A Novel Multilevel DC-AC InverterDocument7 pagesDesign and Implementation of A Novel Multilevel DC-AC Inverterrock starNo ratings yet

- Sepic Converter Design and Operation: by Gregory SharpDocument21 pagesSepic Converter Design and Operation: by Gregory SharpSingam SridharNo ratings yet

- Analog/Digital Circuit Design in Sige For Space ApplicationsDocument6 pagesAnalog/Digital Circuit Design in Sige For Space ApplicationsNguyễn ThaoNo ratings yet

- Simulation and Analysis of Bulk Driven Circuits For Low Power ApplicationsDocument4 pagesSimulation and Analysis of Bulk Driven Circuits For Low Power ApplicationserpublicationNo ratings yet

- Boost ProjectDocument13 pagesBoost ProjectAbdur RahmanNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- FPGA Selection: LTC2387-18 S.No Pin - Name Pin - No. - ADC Mode PurposeDocument6 pagesFPGA Selection: LTC2387-18 S.No Pin - Name Pin - No. - ADC Mode PurposeGurinder Pal SinghNo ratings yet

- Solutions Assignment No. 2Document4 pagesSolutions Assignment No. 2Gurinder Pal SinghNo ratings yet

- Assgn 3Document1 pageAssgn 3Gurinder Pal SinghNo ratings yet

- Design, Construction and Testing of The Digital Hadron Calorimeter (DHCAL) ElectronicsDocument20 pagesDesign, Construction and Testing of The Digital Hadron Calorimeter (DHCAL) ElectronicsGurinder Pal SinghNo ratings yet

- IC Holders (DIL Sockets) : Removing An IC From Its HolderDocument1 pageIC Holders (DIL Sockets) : Removing An IC From Its HolderGurinder Pal SinghNo ratings yet

- Predictive Model For HCI (Beta Version) : Exp Exp) (+ 2) 2 (Document1 pagePredictive Model For HCI (Beta Version) : Exp Exp) (+ 2) 2 (Gurinder Pal SinghNo ratings yet

- A Novel Robust exclusive-OR Function Implementation in QCA Nanotechnology With Energy Dissipation AnalysisDocument11 pagesA Novel Robust exclusive-OR Function Implementation in QCA Nanotechnology With Energy Dissipation AnalysisGurinder Pal SinghNo ratings yet

- Final CBSE Answer Final 2009 FinalDocument1 pageFinal CBSE Answer Final 2009 FinalGurinder Pal SinghNo ratings yet

- Paper 2 Code 0 SolutionDocument39 pagesPaper 2 Code 0 SolutionGurinder Pal SinghNo ratings yet

- IIT-JEE-2012-Paper-II (Code-0) PDFDocument26 pagesIIT-JEE-2012-Paper-II (Code-0) PDFGurinder Pal SinghNo ratings yet

- 14af45 14af45c SVMDocument50 pages14af45 14af45c SVMLuis MorenoNo ratings yet

- Ecu Omegas Direct 3 0 Di60 4cyl enDocument2 pagesEcu Omegas Direct 3 0 Di60 4cyl enZinou ZizouNo ratings yet

- Exp 1,2Document4 pagesExp 1,2NischayNo ratings yet

- Battery Sizing NicdDocument4 pagesBattery Sizing NicdMandip Pokharel0% (1)

- Xerox XD100-102-104 Service ManualDocument331 pagesXerox XD100-102-104 Service ManualNorton YuNo ratings yet

- Elec Advising Study Plan PDFDocument1 pageElec Advising Study Plan PDFDDDrayNo ratings yet

- 622x Keithely Reference ManualDocument454 pages622x Keithely Reference ManualppopcevicNo ratings yet

- TTA MCC in Withdrawable DesignDocument8 pagesTTA MCC in Withdrawable DesignLaurentiu CatalinNo ratings yet

- Acti9 Ik60 - A9K27210 PDFDocument2 pagesActi9 Ik60 - A9K27210 PDFThanh Luân HuỳnhNo ratings yet

- EMD SyllabusDocument2 pagesEMD Syllabuskkk212No ratings yet

- Huawei Power Systems Acceptance Manual - Update - 20190621Document25 pagesHuawei Power Systems Acceptance Manual - Update - 20190621wawanNo ratings yet

- CMOS VLSI DESIGN NOTES Made by Barun Dhiman From Various Books Like Kamran Neil E WasteDocument226 pagesCMOS VLSI DESIGN NOTES Made by Barun Dhiman From Various Books Like Kamran Neil E WasteBarun DhimanNo ratings yet

- DDR 30Document42 pagesDDR 30FERNANDO CONTRERASNo ratings yet

- Instrumentation and Control SystemDocument7 pagesInstrumentation and Control SystemikhsannurrahmanNo ratings yet

- PT19 1300 SeriesDocument112 pagesPT19 1300 Seriesbejoythomas100% (1)

- CE Utilization For HuaweiDocument4 pagesCE Utilization For HuaweiAnonymous XKMLJK0uNo ratings yet

- Relays PresentationDocument32 pagesRelays PresentationbijoyNo ratings yet

- CA AOC15 DatasheetDocument1 pageCA AOC15 DatasheetSankesh SethiyaNo ratings yet

- Philips TV 7607 Service ManualDocument257 pagesPhilips TV 7607 Service ManualPlayer NumberNo ratings yet

- Street Light Monitor and Control System Synopsis-1Document8 pagesStreet Light Monitor and Control System Synopsis-1muskan sNo ratings yet

- SP6-8K Handy Ultra user manual - КопиеDocument78 pagesSP6-8K Handy Ultra user manual - КопиеYordan StoyanovNo ratings yet

- 05-Fault Code List-WabcoDocument11 pages05-Fault Code List-WabcoRaul GTNo ratings yet

- SEW 5500CB Datasheet PDFDocument2 pagesSEW 5500CB Datasheet PDFSaul Pablo Maita FarfanNo ratings yet

- TFM 94 SeriesDocument2 pagesTFM 94 Seriesluat1983No ratings yet

- Chapter12 150428100942 Conversion Gate01 PDFDocument30 pagesChapter12 150428100942 Conversion Gate01 PDFSnr Berel ShepherdNo ratings yet

- Bee Hive - Woods Bee Apidictor PDFDocument1 pageBee Hive - Woods Bee Apidictor PDFDaniel LourençoNo ratings yet

- Fast Fourier Transform ReportDocument19 pagesFast Fourier Transform ReportKarabo LetsholoNo ratings yet

- Rls 51 Rotary Limit SwitchDocument4 pagesRls 51 Rotary Limit SwitchYasser BadrNo ratings yet

- BateriaDocument17 pagesBateriaGabriel MarzolaNo ratings yet

- High Side Smart Power Solid State Relay: Pentawatt (Vertical) Pentawatt (Horizontal)Document11 pagesHigh Side Smart Power Solid State Relay: Pentawatt (Vertical) Pentawatt (Horizontal)Paulo SilvaNo ratings yet