Professional Documents

Culture Documents

Control Bits

Uploaded by

Sri RamCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Control Bits

Uploaded by

Sri RamCopyright:

Available Formats

Control Bits

Every data transaction in a Processor requires a Data Path to be established by the activation of

selected Control Bits. In the nomenclature adopted by us for the Single-bus Processor, the Control Bits

can be of five different types:

(a)

(b)

(c)

(d)

(e)

Enable Denoted generically by EXY, where XY refers to the Module in question, this category of

Control Bits is used to enable Module XY to place data on the Data Bus, with only one exception

EFL, which enables the selected Flag (FL) to decide the next Instruction Fetch. RD ( EML) is a

special Enable bit used to place on the Data Bus ( Read) the contents of a Memory Location

selected by the Address provided by the Address Selector.

Load Denoted generically by LXY, where XY refers to the Module in question, this category of

Control Bits is used to connect the Data Bus to the Data Input of module XY, so that the data

applied to the Data Bus by the selected Data Source (Module enabled by an appropriate Enable

bit) gets loaded into Module XY at the next Active Edge of the Clock. WR ( LML) is a special

Load bit used to load the data available on the Data Bus ( Write) into the Memory Location

selected by the Address provided by the Address Selector.

Select Denoted generically by SXY, where XY refers to the Module in question, this category of

Control Bits is used to select one out of the multiple data sources. Two selections are built into

the Op Code its least significant 3 bits OC2-0 ( <fl>/<rn>/<pn>) being used the select the

Flag/Register/Port to be used in the Instruction, and its most significant 4 bits OC7-4 ( <af>)

being used to select the ALU Function. SIF is a special Select bit used to initiate the next

Instruction Fetch, either unconditionally if the Control Bit EFL = 0, or subject to the value of the

Flag selected by <fl> if EFL = 1.

Increment Applicable only to PC and SP, this Control Bit is used to decide whether the

contents of PC/SP will be incremented at the next Active Edge of the Clock or not.

Decrement Applicable only to SP, this Control Bit is used to decide whether the contents of SP

will be decremented at the next Active Edge of the Clock or not.

The actions of the last three types of control bits are straightforward, and the module-wise control bits

tabulated on the next page should be sufficient to clarify them. There is scope for some ambiguity in the

actions of the Enable and Load bits on modules that have multiple data paths for Output and Input

respectively. Let us therefore examine the data paths associated with such modules one by one in

order to understand the actions of the control bits pertaining to these modules.

(a) Memory This module has two data paths, one for the Address Bus and the other for the Data

Bus of the Memory module. The Address Bus is permanently connected to the output of the

Address Selector module, so as to keep the desired Memory Location always selected. What

the control bits RD and WR do is to connect the Data Bus of the Processor either to the output or

to the input of the Memory Location so as to set up the data path for the desired operation.

(b) Program Counter (PC) Control bits EPC and LPC control data transactions between PC and any

other module via the Data Bus. The data path connecting the PC to the Address Selector is, on

the other hand, independent of control bits, and so [PC] is ALWAYS available as the source for

(Program) Memory Address. Thus during the Fetch cycle of every instruction, Memory Address =

[PC] during the transfer of the Op Code from (Program) Memory to the Instruction Register and

[PC] [PC] + 1 at the end of that Clock cycle. The EPC bit is NOT applicable to this data

transaction; NOR is it applicable to the transfer of the Operand from (Program) Memory to the

Operand Register during the execution of an Instruction containing an Operand.

(c) Stack Pointer (SP) Like PC, SP also provides an ALWAYS available source for (Stack)

Memory Address to the Address Selector. The value provided through this data path is [SP] 1

if DSP = 1, and [SP] otherwise; the next Active Clock Edge decrements [SP] if DSP = 1, and

increments [SP] if ISP = 1. Thus for the instructions CUD, CCD and PSH, Memory Address = [SP]

1 during the saving of [PC] to (Stack) Memory and [SP] [SP] 1 at the end of that Clock

cycle; while for the instructions RTU, RTC and POP, Memory Address = [SP] during the transfer

(d)

(e)

of the Return Address from (Stack) Memory to PC and [SP] [SP] + 1 at the end of that Clock

cycle. ESP and LSP control transactions between SP and any other module via the Data Bus. They

are NOT applicable to the transactions carried out in the Branch instructions mentioned above.

Operand Register (OR) The value (operand) contained in the Operand Register is ALWAYS

available as the B Input to the ALU, The control bits EOR and LOR are applicable only to data

transactions between OR and any other module via the Data Bus.

Register Array The Registers in this module can receive input either from the ALU Output or

from the Data Bus, the selection being done by the control bit SAL (SAL = 1 selects ALU output).

The output of the Accumulator (R0) is ALWAYS available as the (Data) memory Address input to

the Address Selector. ER0 is applicable only for placing [R0] on the Data Bus.

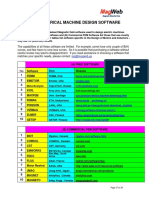

Module-wise Control Bit Action:

Module

Memory

Address

Selector

Program

Counter

Stack

Pointer

Control Bits

implies action at the next Active Edge of the Clock

Action of Control Bits when Active (= 1)

RD

Contents of selected Memory location read out on Data Bus

WR

Data on Data Bus written into the selected Memory Location

SPC SSP = 0 0

[R0] selected to provide the address of the Memory Location

SPC SSP = 0 1

[SP] selected to provide the address of the Memory Location

SPC SSP = 1 0

[PC] selected to provide the address of the Memory Location

EPC

Contents of the Program Counter [PC] read out on Data Bus

LPC

Data on Data Bus written into the Program Counter

IPC

Contents of the Program Counter [PC] incremented

ESP

Contents of the Stack Pointer [SP] read out on Data Bus

LSP

Data on Data Bus written into the Stack Pointer

ISP

Contents of the Stack Pointer [SP] incremented

DSP

Contents of the Stack Pointer [SP] decremented

Instruction

Register

LIR

Data on Data Bus (Op Code) written into the Instruction Register

Input Port

EIP

Contents of the selected Input Port [PN] read out on Data Bus

Output Port

LOP

Data on Data Bus written into the selected Output Port

Operand

Register

EOR

Contents of Operand Register [OR] read out on Data Bus

LOR

Data on Data Bus written into the Operand Register

ER0

Contents of Accumulator [R0] read out on Data Bus

ERN

Contents of selected Register [RN] read out on Data Bus

Register

Array

Control Code

Generator

LR0 LRN = 0 1

Input Data written into the selected Register RN

LR0 LRN = 1 0

Input Data written into the Accumulator R0

LR0 LRN = 1 1

Input Data written in parallel into ALL the Registers R0, R1, R2...R7.

SAL = 0

Data on Data Bus selected as the Input Data for the Register Array

SAL = 1

ALU Output selected as the Input Data for the Register Array

EFL

Conditional Branch Instruction

SIF

Next Instruction Fetch initiated either if EFL= 0 or if FL = 0

You might also like

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Basic Computer OrganizationDocument23 pagesBasic Computer OrganizationKibrom HaftuNo ratings yet

- Chapter 5Document53 pagesChapter 5Yididiya TilahunNo ratings yet

- Chapter 4Document17 pagesChapter 4Manju JangirNo ratings yet

- General Register OrganizationDocument16 pagesGeneral Register OrganizationGovind UpadhyayNo ratings yet

- Cpu Design 2Document16 pagesCpu Design 2Parth ChauhanNo ratings yet

- WISC-99S Computer Architecture Design ProjectDocument10 pagesWISC-99S Computer Architecture Design ProjectzzzzoobbiiaaNo ratings yet

- Computer Organization & ArchitectureDocument82 pagesComputer Organization & ArchitectureDhirendra SinghNo ratings yet

- Computer Organization UNIT-3 Processor and Control Unit: Fundamental ConceptsDocument23 pagesComputer Organization UNIT-3 Processor and Control Unit: Fundamental ConceptsAbhinav BhardwajNo ratings yet

- SAP Report Group 2Document14 pagesSAP Report Group 2Chanel Hooper0% (1)

- معمارية 2Document13 pagesمعمارية 2firasvtNo ratings yet

- 08 CompOrgDocument35 pages08 CompOrgIke Mag-away GaamilNo ratings yet

- SAP-1 (Simple As Possible-1) Computer ArchitectureDocument8 pagesSAP-1 (Simple As Possible-1) Computer ArchitecturesaikotNo ratings yet

- 8086 Architecture and Addressing ModesDocument53 pages8086 Architecture and Addressing ModeskarthiNo ratings yet

- UNIT III: Central Processing Unit: GeneralDocument25 pagesUNIT III: Central Processing Unit: GeneralGagandeep SinghNo ratings yet

- Sap-1 ArchitectureDocument9 pagesSap-1 ArchitectureAshna100% (1)

- Computer Organization Chapter 8 Short NoteDocument31 pagesComputer Organization Chapter 8 Short NoteMeskatul Islam2100% (1)

- Coa 5Document37 pagesCoa 5pahujahimankNo ratings yet

- Timing and Control Instruction Cycle Memory Reference Instructions Input-Output and Interrupt Complete Computer DescriptionDocument38 pagesTiming and Control Instruction Cycle Memory Reference Instructions Input-Output and Interrupt Complete Computer DescriptionGeorgian ChailNo ratings yet

- Chapter 4Document71 pagesChapter 4Yididiya TilahunNo ratings yet

- Execution of InstructionDocument60 pagesExecution of InstructionKr RanjithNo ratings yet

- Operation of DatapathDocument13 pagesOperation of Datapathsas21-d01-s6-cs15No ratings yet

- SCS1315Document98 pagesSCS1315Sai KrishnaNo ratings yet

- Unit IV Cpu OrganizationDocument124 pagesUnit IV Cpu Organizationrajendra.rajuNo ratings yet

- Instruction CodesDocument35 pagesInstruction Codesanilk_patiNo ratings yet

- Unit-I: 8-Bit MicroprocessorsDocument55 pagesUnit-I: 8-Bit MicroprocessorsAASTHA KIETNo ratings yet

- Register FileDocument6 pagesRegister FilejayaprasadkalluriNo ratings yet

- NEC 022 External Paper SolutionDocument13 pagesNEC 022 External Paper SolutionSachin PalNo ratings yet

- The C5x Devices Offer These AdvantagesDocument38 pagesThe C5x Devices Offer These AdvantagesmailtoakhilsNo ratings yet

- Morris ManoDocument29 pagesMorris Manojupillisjohn_9650432100% (4)

- COA Module 5 BEC306CDocument19 pagesCOA Module 5 BEC306Csachinksr007No ratings yet

- Opcodes 80537Document57 pagesOpcodes 80537Sebas EuNo ratings yet

- Labview Serial CommunicationDocument0 pagesLabview Serial Communicationmajidkhan04No ratings yet

- Coa HW2Document6 pagesCoa HW2Mohammed AyadNo ratings yet

- YamahaDx7 9ServiceManualDocument16 pagesYamahaDx7 9ServiceManualTony RoeNo ratings yet

- Cpre 381 Processor Project 1Document20 pagesCpre 381 Processor Project 1api-272773251No ratings yet

- Registri TriDocument4 pagesRegistri TriNenad FemicNo ratings yet

- Draw The Block Diagram of Von Neumann Architecture and Explain About Its Parts in Brief AnswerDocument7 pagesDraw The Block Diagram of Von Neumann Architecture and Explain About Its Parts in Brief AnswerhayerpaNo ratings yet

- Computer OrganizationDocument18 pagesComputer OrganizationBolaji AwokiyesiNo ratings yet

- 8051 Instruction Set Rv01Document81 pages8051 Instruction Set Rv01lizhi0007No ratings yet

- Coa Unit 5Document73 pagesCoa Unit 5Shiv Patel 18-38No ratings yet

- Yamaha DX7 and DX9 ServiceManualDocument16 pagesYamaha DX7 and DX9 ServiceManualx7No ratings yet

- Coa Lecture Unit 2Document82 pagesCoa Lecture Unit 2Sumathy JayaramNo ratings yet

- Processor RegistersDocument6 pagesProcessor Registersirinaasdf12No ratings yet

- Basic Processing Unit:: Fundamental ConceptsDocument35 pagesBasic Processing Unit:: Fundamental ConceptsJoseph JohnNo ratings yet

- 1.1 IntroDocument49 pages1.1 IntroKarl Martin AlduesoNo ratings yet

- MPMC NotesDocument301 pagesMPMC NotesVarinder KumarNo ratings yet

- Sap 2Document35 pagesSap 2Michael Vincent B. Nierva88% (8)

- Computer Registers & Common Bus SystemDocument21 pagesComputer Registers & Common Bus SystemsatNo ratings yet

- Part 2Document41 pagesPart 2ah chongNo ratings yet

- CHAPTER 5, Inside Digital DesignDocument33 pagesCHAPTER 5, Inside Digital DesignSyed Abdullah RizviNo ratings yet

- Microprocessor and Micro ControllerDocument118 pagesMicroprocessor and Micro ControllerShiva ShanNo ratings yet

- Seven Cpu RegistersDocument6 pagesSeven Cpu RegistersPriyanka PuvvalaNo ratings yet

- Chapter 7 MicrocontrollersDocument7 pagesChapter 7 MicrocontrollerspurushresthaNo ratings yet

- Co3 0Document51 pagesCo3 0Gautam ChhabraNo ratings yet

- 8051 Instruction SetDocument79 pages8051 Instruction Setgsathishbsa100% (1)

- Two Basic Components of A ComputerDocument11 pagesTwo Basic Components of A ComputerNiñoChuaNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Lec 31Document27 pagesLec 31Sri RamNo ratings yet

- Lec1 09 PDFDocument21 pagesLec1 09 PDFSri RamNo ratings yet

- Autosar NotesDocument10 pagesAutosar NotesSri RamNo ratings yet

- Abstract Format-2017Document2 pagesAbstract Format-2017Sri RamNo ratings yet

- 3.presentation EVPowerDocument16 pages3.presentation EVPowerSri RamNo ratings yet

- Recommendations (Towards A Predictive Business Aligned Training Ecosystem)Document23 pagesRecommendations (Towards A Predictive Business Aligned Training Ecosystem)Sri RamNo ratings yet

- Shiv Nadar University Lab-3 (Deconvolution) : Department of Electrical Engineering - (Soe)Document1 pageShiv Nadar University Lab-3 (Deconvolution) : Department of Electrical Engineering - (Soe)Sri RamNo ratings yet

- Digital Electronics S: EED 206 Pring Problem Set 1Document1 pageDigital Electronics S: EED 206 Pring Problem Set 1Sri RamNo ratings yet

- Basic Processor Modules: "Floating". To Transfer Data From Module XY To Module PQ, TheDocument3 pagesBasic Processor Modules: "Floating". To Transfer Data From Module XY To Module PQ, TheSri RamNo ratings yet

- Diode and DIAC - CharacterisitcsDocument4 pagesDiode and DIAC - CharacterisitcsSri RamNo ratings yet

- Single-Bus Processor - FinalDocument1 pageSingle-Bus Processor - FinalSri RamNo ratings yet

- TRIAC - CharacteristicsDocument3 pagesTRIAC - CharacteristicsSri RamNo ratings yet

- Ug Course Catalog SPR 2015 1.0 PDFDocument235 pagesUg Course Catalog SPR 2015 1.0 PDFSri RamNo ratings yet

- Syllabus For Nursing & Paramedical PostDocument32 pagesSyllabus For Nursing & Paramedical PostSri RamNo ratings yet

- Sub: Marrs International Spelling Bee - State Level Oral and National Level Orientation 2013-14Document1 pageSub: Marrs International Spelling Bee - State Level Oral and National Level Orientation 2013-14Sri RamNo ratings yet

- Mini Search EngineDocument1 pageMini Search EngineSri RamNo ratings yet

- Ipemarch 2013Document1 pageIpemarch 2013Sri RamNo ratings yet

- Maty ProposalDocument27 pagesMaty Proposalkassahun meseleNo ratings yet

- Installing An Operating SystemDocument83 pagesInstalling An Operating SystemMaricel Fraga Azcarraga100% (1)

- Mindwave MobileDocument46 pagesMindwave MobileRodrigo AlexanderNo ratings yet

- An0046 Efm32 Usb Hardware Design GuidelinesDocument21 pagesAn0046 Efm32 Usb Hardware Design GuidelinesMohammad HBNo ratings yet

- Leggett (2008) - Realism and The Physical WorldDocument6 pagesLeggett (2008) - Realism and The Physical WorldsajadonscribdNo ratings yet

- SKF Endoscopes TKES 10 Series: Instructions For UseDocument24 pagesSKF Endoscopes TKES 10 Series: Instructions For UseRizky MuhammadNo ratings yet

- Bugreport Ysl PKQ1.181203.001 2020 01 04 19 37 44 Dumpstate - Log 20606Document18 pagesBugreport Ysl PKQ1.181203.001 2020 01 04 19 37 44 Dumpstate - Log 20606Sandeep TaleNo ratings yet

- 2CSG257153R4051 Anr96prf 230 Network AnalyserDocument2 pages2CSG257153R4051 Anr96prf 230 Network AnalyserLuis EduardoNo ratings yet

- 06 June 1993Document92 pages06 June 1993MastroghettiNo ratings yet

- SBS FM30 Manual (29-06-06) PDFDocument37 pagesSBS FM30 Manual (29-06-06) PDFK.S. BalasubramaniamNo ratings yet

- Electric Products: Contactors / MPCB / MCCB / ACBDocument29 pagesElectric Products: Contactors / MPCB / MCCB / ACBZAHEER ABBASNo ratings yet

- GSPRMDocument12 pagesGSPRMtrung2iNo ratings yet

- VMEbus Connector Pin Assignment and Signal Descriptions Under VME64xDocument14 pagesVMEbus Connector Pin Assignment and Signal Descriptions Under VME64xgeorgeNo ratings yet

- .Automatic Room Light Controller Using Arduino and PIR SensorDocument4 pages.Automatic Room Light Controller Using Arduino and PIR SensorLÂM PHẠM NHƯ100% (1)

- Lecture Notes For Physics 229: Quantum Information and ComputationDocument321 pagesLecture Notes For Physics 229: Quantum Information and ComputationIvan CheungNo ratings yet

- Fire and Gas Detection Systems Product Catalogue Morley-IAS V2.1Document230 pagesFire and Gas Detection Systems Product Catalogue Morley-IAS V2.1mgkvprNo ratings yet

- TCM1.0E TCM2.0E: May, 2008Document69 pagesTCM1.0E TCM2.0E: May, 2008JejeNo ratings yet

- Mcd388 98 Pss AenDocument3 pagesMcd388 98 Pss AenmallipudyNo ratings yet

- Punit Resume WorkDocument3 pagesPunit Resume Workapi-321948941No ratings yet

- Design Software 1Document2 pagesDesign Software 1anbarasuval84No ratings yet

- Ratio TronicDocument31 pagesRatio TronicTinaManoussi100% (1)

- Chapter 10: Vibration Isolation of The SourceDocument12 pagesChapter 10: Vibration Isolation of The SourceAshokNo ratings yet

- Myth-II-Soulblighter Manual Win enDocument81 pagesMyth-II-Soulblighter Manual Win enlupyen youngNo ratings yet

- Survey & Mitigation: Who We Are & What We DoDocument5 pagesSurvey & Mitigation: Who We Are & What We DorustyNo ratings yet

- Design and FPGA Implementation of Vending Machine: Submitted To: Submitted byDocument39 pagesDesign and FPGA Implementation of Vending Machine: Submitted To: Submitted byManish SarohaNo ratings yet

- A - ATG - PR 2014 0006 GB - HyPower Geko OCT - BR - K1 02 2015 - 150dpi PDFDocument16 pagesA - ATG - PR 2014 0006 GB - HyPower Geko OCT - BR - K1 02 2015 - 150dpi PDFionutenacheNo ratings yet

- K To 12 ICT - Computer Systems Servicing (NC II) Curriculum Guide May 2016 LO - Learning Outcome ofDocument2 pagesK To 12 ICT - Computer Systems Servicing (NC II) Curriculum Guide May 2016 LO - Learning Outcome ofFroz WorksNo ratings yet

- LCD TV: Service ManualDocument14 pagesLCD TV: Service ManualPrabir Kumar SurNo ratings yet

- Genicom 5000 Series Full ManualDocument223 pagesGenicom 5000 Series Full ManualRJNo ratings yet

- ARM7Document36 pagesARM7Yogesh SutharNo ratings yet