Professional Documents

Culture Documents

AdvancedSDRSDRAMController DesignDocumentation

Uploaded by

Hưng Nguyễn ĐìnhOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

AdvancedSDRSDRAMController DesignDocumentation

Uploaded by

Hưng Nguyễn ĐìnhCopyright:

Available Formats

SDR SDRAM Controller

September 2014

Reference Design RD1010

Introduction

Synchronous DRAM (SDRAM) has become a mainstream memory of choice in embedded system memory design

due to its speed, burst access and pipeline features. For high-end applications using processors such as Motorola

MPC 8260 or Intel StrongArm, the interface to the SDRAM is supported by the processors built-in peripheral module. However, for other applications, the system designer must design a controller to provide proper commands for

SDRAM initialization, read/write accesses and memory refresh. In some cases, SDRAM is chosen because the

previous generations of DRAM (FP and EDO) are either end-of-life or not recommended for new designs by the

memory vendors. From the board design point of view, design using earlier generations of DRAM is much easier

and more straightforward than using SDRAM unless the system bus master provides the SDRAM interface module

as mentioned above. This SDRAM controller reference design, located between the SDRAM and the bus master,

reduces the users effort to deal with the SDRAM command interface by providing a simple generic system interface to the bus master. Figure 1 shows the relationship of the controller between the bus master and SDRAM. The

bus master can be either a microprocessor or a users proprietary module interface.

In today's SDRAM market, there are two major types of SDRAM distinguished by their data transfer rates. The

most common single data rate (SDR) SDRAM transfers data on the rising edge of the clock. The other is the double data rate (DDR) SDRAM which transfers data on both the rising and falling edge to double the data transfer

throughput. Other than the data transfer phase, the different power-on initialization and mode register definitions,

these two SDRAMs share the same command set and basic design concepts. This reference design is targeted for

SDR SDRAM, however, due to the similarity of SDR and DDR SDRAM, this design can also be modified for a DDR

SDRAM controller. For illustration purposes, the Micron SDR SDRAM MT48LC32M4A2 (8Meg x 4 x 4 banks) is

chosen for this design. Also, this design has been verified by using Microns simulation model. It is highly recommended to download the simulation model from the SDRAM vendors for timing simulation when any modifications

are made to this design.

Figure 1. SDR SDRAM Controller System

System

Interface

SDRAM

Interface

Control

BUS

Master

Status

Command

SDR

Synchronous

DRAM

SDR

SDRAM

Controller

Address

Address

Data

Data

2014 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand

or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

www.latticesemi.com

rd1010_4.8

SDR SDRAM Controller

Features

Simplifies SDRAM command interface to standard system read/write interface.

Internal state machine built for SDRAM power-on initialization.

Read/write cycle access time optimized automatically according to the SDRAM timing specification and the

mode it is configured to.

Dedicated auto-refresh request input and acknowledge output for SDRAM refresh.

Easily configurable to support different CAS latency and burst length.

By taking advantage of the sysCLOCK PLL feature, a slower system clock can be used. The system

interface clock does not need to be the same as the SDRAM clock.

With the support of the sysIO feature available in all Lattice devices, the system interface can be in any I/O

standards supported by the device.

Pin Descriptions

Pin Name

Type

Pin Description

sys_R_Wn

In

System interface read/write signal. High indicates a read cycle and low indicates a write cycle.

When this pin is high, it indicates to the controller that the bus master is performing a read cycle.

When low, it indicates that its a write cycle.

sys_ADSn

In

Active low system interface address strobe. This pin indicates the start of a bus master cycle.

sys_DLY_100US

In

This active high signal indicates to the controller that the SDRAM has gone through the 100s delay

for power and clock stabilization.

sys_CK

In

System interface clock.

sys_RESET

In

This active high signal resets the controller to the initial state.

sys_REF_REQ

In

Active high SDRAM refresh request.

sys_REF_ACK

Out

sys_A

sys_D

In

Active high SDRAM refresh acknowledge

System interface address bus.

In/Out Bi-directional three-state system interface data bus.

sys_D_VALID

Out

Active high data valid signal. This pin activates only for read cycles and indicates the data currently

present on the system interface data bus sys_D is valid.

sys_CYC_END

Out

This active high signal indicates to the bus master that the system interface read/write cycle is completed. This pin is active after reset. After that, it is negated at the first clock and asserted at the last

clock of the system interface read/write cycle.

sys_INIT_DONE

Out

This active high signal indicates that the SDRAM initialization is completed.

sdr_DQ

In/Out SDRAM data bus

sdr_A

Out

SDRAM address bus

sdr_BA

Out

SDRAM bank address

sdr_CK

Out

SDRAM clock (If PLL is used, this will be the PLL output pin PLL_OUT0 or PLL_OUT1.)

sdr_CKE

Out

SDRAM clock enable

sdr_CSn

Out

SDRAM command inputs CS#

sdr_RASn

Out

SDRAM command inputs RAS#

sdr_CASn

Out

SDRAM command inputs CAS#

sdr_Wen

Out

SDRAM command inputs WE#

sdr_DQM

Out

SDRAM data bus mask

SDR SDRAM Controller

Functional Description

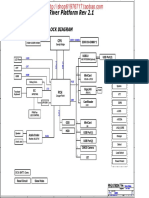

The functional block diagram of the SDRAM controller is shown in Figure 2. It consists of three modules: the main

control module, the signal generation module and the data path module. The main control module, containing two

state machines and a counter, is the primary module of the design which generates proper iState and cState outputs according to the system interface control signals. The signal generation module generates the address and

command signals required for SDRAM based on iState and cState. The data path module performs the data latching and dispatching of the data between the bus master and SDRAM.

If using a PLL, all modules derive internal timing from the PLL clock output. This PLL clock also can be connected to

the SDRAM directly. A separate on-board SDRAM clock may not be required. With the sysIO feature, the bus master

I/O can be LVCMOS 1.8/2.5/3.3, LVTTL, PCI, PCI-X, GTL+ or any of the other standards supported by the device

being used.

When targeting to other Lattice CPLD devices, instead of generating SDRAM clock with the CPLD, the system

needs an on-board clock source such as a clock oscillator to generate the clocks for both the CPLD and the

SDRAM.

Figure 2. Block Diagram

sdr_ctrl.v

sdr_sig.v

Main Control

sys_DLY_100US

INIT_FSM

Signal

Generation

iState

sdr_CK

sdr_CKE

sdr_CSn

sys_INIT_DONE

sdr_RASn

sys_R_Wn

sys_ADSn

sdr_CASn

CMD_FSM

cState

sdr_WEn

sys_REF_REQ

sys_REF_ACK

sdr_BA

MSB

sdr_A

sys_CYC_END

sdr_A

LSB

COUNTER

"High"

sdr_data.v

sys_A

sys_CLK

sdr_DQM

PLL

cState

To All

Modules

Data Path

clkCNT

sys_D

sys_RESET

sdr_DQ

To All

Modules

sys_D_VALID

SDR SDRAM Controller

Benefits of Using PLL

As mentioned in the functional description section above, the SDRAM clock can be generated by the internal PLL

of the devices. For example, if the system is running at 40MHz, a 100MHz SDRAM clock can be obtained through

the dedicated PLL output pin by setting the proper PLL attributes (multiply = 5 and divide = 2).

Also, by using the PLLs variable delay line capability, all the output signals to the SDRAM can be tuned to retard or

advance the normal output timing for timing optimization and system reliability improving.

SDRAM Initialization

Before normal memory accesses can be performed, the SDRAM needs to be initialized by a sequence of commands. The INIT_FSM state machine handles this initialization. Figure 3 shows the state diagram of the INIT_FSM

state machine. During reset, the INIT_FSM is forced to the i_NOP state. After reset, the sys_100s signal will be

sampled at the rising edge of every PLL clock cycle to determine if the 100s power/clock stabilization delay is

completed. After the power/clock stabilization is complete, the SDRAM initialization sequence will begin and the

INIT_FSM will switch from i_NOP to i_PRE state. The initialization starts with the PRECHARGE command, followed by two AUTO REFRESH commands, and then the LOAD MODE REGISTER command to configure SDRAM

to a specific mode of operation. The i_PRE, i_AR1, i_AR2 and i_MRS states are used for issuing these commands.

After each of these commands is issued, a corresponding timing delay needs to be satisfied before any command

other than NOP can be issued. These timing delays are tRP, tRFC and tMRD for command PRECHARGE, AUTO

REFRESH and LOAD MODE REGISTER respectively. After issuing the LOAD MODE REGISTER command and

the tMRD timing delay is satisfied, INIT_FSM goes to i_ready state and remains there for the normal memory

access cycles unless sys_RESET is asserted. Also, signal sys_INIT_DONE is set to high to indicate the SDRAM

initialization is completed.

The LOAD MODE REGISTER command configures the SDRAM by loading data into the mode register through the

address bus. The data present on the address bus during the LOAD MODE REGISTER command is loaded to the

mode register. The mode register contents specify the burst length, burst type, CAS latency, etc. Refer to the

SDRAM vendors data sheet for more detailed information about the mode register field definitions. As long as all

banks of the SDRAM are put into idle state by the PRECHARGE or AUTO PRECHARGE, the mode register can be

reloaded with different values, thereby changing the mode of operation. However, in most applications, the mode

register value will not be changed after the initialization. This design assumes the mode register stays the same

after initialization and a fixed mode register content is implemented in the HDL code. The mode register content in

the HDL code may need to be modified to suit the users needs.

SDR SDRAM Controller

Figure 3. INIT_FSM State Diagram

sys_DLY_100US

i_NOP

i_PRE

i_tRP

endOf_tRP

tR

f_

dO

en

sys_DLY_100US

i_AR1

i_tRFC1

endOf_tRFC

i_tRFC2

endOf_tRFC

i_tMRD

endOf_tMRD

FC

tR

f_

dO

en

i_AR2

FC

tR

f_

dO

en

i_MRS

tM

f_

dO

en

i_ready

As mentioned above, certain timing delays (tRP, tRFC, tMRD) need to be satisfied before another non-NOP command

can be issued. These SDRAM delays vary from speed grade to speed grade and sometimes from vendor to vendor. To accommodate this without sacrificing performance, the designer needs to modify the HDL code for the specific delays and clock period (tCK). According to these timing values, the number of clocks the state machine will

stay at i_tRP, i_tRFC1, i_tRFC2, i_tMRD states will be determined after the code is synthesized. In cases where

tCK is larger than the timing delay, the state machine doesnt need to switch to the timing delay states and can go

directly to the command states. The dashed lines in Figure 3 show the possible state switching paths.

Read/Write Cycle

Figure 4 shows the state diagram of CMD_FSM which handles the read, write and refresh of the SDRAM. The

CMD_FSM state machine is initialized to c_idle during reset. After reset, CMD_FSM stays in c_idle as long as

sys_INIT_DONE is low which indicates the SDRAM initialization sequence is not yet completed. Once the initialization is done, sys_ADSn and sys_REF_REQ will be sampled at the rising edge of every clock cycle. A logic high

sampled on sys_REF_REQ will start a SDRAM refresh cycle. This is described in the following section. If logic low

is sampled on both sys_REF_REQ and sys_ADSn, a system read cycle or system write cycle will begin. These

system cycles are made up of a sequence of SDRAM commands.

SDR SDRAM Controller

Figure 4. CMD_FSM State Diagram

c_AR

ON

_D

IT

_IN

(sys_INIT_DONE * sys_REF_REQ * sys_ADSn) + sys_INIT_DONE

EQ

* sy

_R

EF

_R

sys

endOf_tRFC

en

dO

f

nc

y

ate

_L

as

____________

________

sys_INIT_DONE * sys_REF_REQ * sys_ADSn

endOf_Write_Burst

t

rs

Bu

e_

rit

f_

f_C

c_tDAL

dO

dO

endOf_tDAL

en

en

endOf_tRFC

L

DA

endOf_Cas_Latency

f_t

c_rdata

dO

endOf_Read_Burst

c_tRFC

en

_R

ea

d_

Bu

rst

c_idle

c_cl

c_wdata

c_ACTIVE

sys

Wn

_R_

_R_

sys

_________

endOf_tRCD * sys_R_Wn

endOf_tRCD * sys_R_Wn

c_READA

Wn

c_tRCD

c_WRITEA

endOf_tRCD

Similar to the FP and EDO DRAM, row address and column address are required to pinpoint the memory cell location of the SDRAM access. Since SDRAM is composed of four banks, bank address needs to be provided as well.

The SDRAM can be considered as a four by N array of rows. All rows are in the closed status after the SDRAM

initialization. The rows need to be opened before they can be accessed. However, only one row in the same bank

can be opened at a time. Since there are four banks, there can be at most four rows opened at the same time. If a

row in one bank is currently opened, it must be closed before another row in the same bank can be opened.

ACTIVE command is used to open the rows and PRECHARGE (or the AUTO PRECHARGE hidden in the WRITE

and READ commands, as used in this design) is used to close the rows. When issuing the commands for opening

or closing the rows, both row address and bank address need to be provided.

For sequential access applications and those with page memory management, the proper address assignments

and the use of the SDRAM pipeline feature deliver the highest performance SDRAM controller. However, this type

of controller design is highly associated with the bus master cycle specification and will not fit the general applications. Therefore, this SDRAM controller design does not implement these custom features to achieve the highest

performance through these techniques.

SDR SDRAM Controller

In this design, the ACTIVE command will be issued for each read or write access to open the row. After a tRCD

delay is satisfied, READ or WRITE commands will be issued with a high sdr_A[10] to enable the AUTO REFRESH

for closing the row after access. So, the clocks required for read/write cycle are fixed and the access can be random over the full address range.

Read or write is determined by the sys_R_Wn status sampled at the rising edge of the clock before tRCD delay is

satisfied. If a logic high is sampled, the state machine switches to c_READA. If a logic low is sampled, the state

machine switches to c_WRITEA.

For read cycles, the state machine switches from c_READA to c_cl for CAS latency, then switches to c_rdata for

transferring data from SDRAM to bus master. The number of clocks the state machine stays in c_rdata state is

determined by the burst length. After the data is transferred, it switches back to c_idle.

For write cycles, the state machine switches from c_WRITEA to c_wdata for transferring data from bus master to

SDRAM, then switches to c_tDAL. Similar to read, the number of clocks the state machine stays in c_wdata state is

determined by the burst length. The time delay tDAL is the sum of WRITE recovery time tWR and the AUTO PRECHARGE timing delay tRP. After the clock rising edge of the last data in the burst sequence, no commands other

than NOP can be issued to SDRAM before tDAL is satisfied.

As mentioned in the INIT_FSM section above, the dash lines indicates possible state switching paths when tCK

period is larger than timing delay spec.

Refresh Cycle

Similar to the other DRAMs, memory refresh is required. A SDRAM refresh request is generated by activating

sdr_REF_REQ signal of the controller. The sdr_REF_ACK signal will acknowledge the recognition of

sdr_REF_REQ and will be active throughout the whole refresh cycle. The sdr_REF_REQ signal must be maintained until the sdr_REF_ACK goes active in order to be recognized as a refresh cycle. Note that no system read/

write access cycles are allowed when sdr_REF_ACK is active. All system interface cycles will be ignored during

this period. The sdr_REF_REQ signal assertion needs to be removed upon receipt of sdr_REF_ACK acknowledge,

otherwise another refresh cycle will again be performed.

Upon receipt of sdr_REF_REQ assertion, the state machine CMD_FSM enters the c_AR state to issue an AUTO

REFRESH command to the SDRAM. After tRFC time delay is satisfied, CMD_FSM returns to c_idle.

Data Path

Figure 5 shows the data flow design between the SDRAM and the system interface. The module in this reference

design interfaces between the SDRAM with 4-bit data bus and the bus master with 16-bit data bus. The user

should be able to modify this module to customize to fit his/her system bus requirements.

The size of each bus in Figure 5 is shown by the number under the slash across the bus. The grayed components

are for read cycles and the white components are for write cycles.

SDR SDRAM Controller

Figure 5. Data Path Module

cState

Combinatorial

Logic

clkCNT

sys_CLK

To All

FlipFlops

sys_RESET

CE

CE

CE

CE

sys_D_VALID

sys_D

sdr_DQ

16

16

16

4

4

Timing Diagrams

Figures 6 and 7 are the read cycle and write cycle timing diagrams of the reference design with the two CAS

latency cycles and the burst length of four. The timing diagrams may be different due to the values of the timing

delays tMRD/tRP/tRFC/tRCD/tRCD/tWR, the clock period tCK, the CAS latency and the burst length. The total number of

clocks for read and write cycles are decided by these factors. In the example shown in the figures, the read cycle

takes 10 clocks and the write cycle takes 9 clocks.

The state variable c_State of CMD_FSM is also shown in these figures. Note that the ACTIVE, READ, WRITE commands are asserted one clock after the c_ACTIVE, c_READA, c_WRITEA states respectively.

The values of the region filed with slashes in the system interface input signals of these figures are dont care. For

example, signal sys_R_Wn needs to be valid only at the clock before CMD_FSM switches to the c_READA or

c_WRITEA states. Depending on the values of tRCD and tCK, this means the signal sys_R_Wn needs to be valid at

state c_ACTIVE or the last clock of state c_tRCD.

SDR SDRAM Controller

Figure 6. Read Cycle Timing Diagram

T1

T2

T3

T4

T5

T6

T7

T8

T9

T10

pllCLK

Addr

sys_A

Addr

sys_ADSn

sys_R_Wn

Data (out)

sys_D[0:15]

Data (in)

sys_D_VALID

sys_CYC_END

c_idle

iState

c_ACTIVE

c_tRCD

c_READA

NOP

ACTIVE

NOP

c_cl

c_rdata

c_idle

c_ACTIVE

c_tRCD

NOP

ACTIVE

sdr_CKE

sdr_COMMAND*

NOP

READ

NOP

NOP

NOP

NOP

NOP

NOP

NOP

sdr_DQM

sdr_A[0:9]

sdr_A[11]

Row

sdr_A[10]

Row

sdr_BA[0:1]

Bank

Row

Column

sdr_A[10] = 1

Enable Auto Precharge

Bank

Bank

sdr_DQ[0:3]

Don't care

Figure 7. Write Cycle Timing Diagram

T1

T2

T3

T4

T5

T6

T7

T8

T9

pllCLK

Addr

sys_A

Addr

sys_ADSn

sys_R_Wn

Data (in)

sys_D[0:15]

sys_D_VALID

sys_CYC_END

c_idle

iState

c_ACTIVE

c_tRCD

c_WRITEA

NOP

ACTIVE

NOP

c_wdata

c_tDAL

c_idle

c_ACTIVE

c_tRCD

c_READA

c_cl

NOP

NOP

NOP

ACTIVE

NOP

READ

sdr_CKE

sdr_COMMAND

NOP

WRITE

NOP

NOP

NOP

sdr_DQM

sdr_A[0:9]

sdr_A[11]

Row

sdr_A[10]

Row

sdr_BA[0:1]

Bank

Row

Column

Column

sdr_A[10] = 1

Enable Auto Precharge

sdr_A[10] = 1

Auto Precharge

Bank

Bank

sdr_DQ[0:3]

Don't care

Bank

SDR SDRAM Controller

Implementation

This design is implemented in Verilog and VHDL. When using this design in a different device, density, speed, or

grade, performance and utilization may vary. Default settings are used during the fitting of the design.

Table 1. Performance and Resource Utilization

Device Family

ECP5 9

LatticeECP3 3

LatticeECP 4

MachXO2 1

MachXO 2

Lattice XP2 5

Lattice XP 6

ispMACH 4000ZE7

ispLSI 5000VE8

1.

2.

3.

4.

5.

6.

7.

8.

9.

Language

Speed Grade

Utilization

fMAX (MHz)

I/Os

Architecture

Resources

Verilog-LSE

-6

92 LUTs

>60

73

N/A

Verilog-Syn

-6

142 LUTs

>60

73

N/A

VHDL-LSE

-6

89 LUTs

>60

73

N/A

VHDL-Syn

-6

125 LUTs

>60

73

N/A

Verilog-Syn

-7

154 LUTs

>60

73

N/A

VHDL-Syn

-7

146 LUTs

>60

73

N/A

Verilog-Syn

-5

150 LUTs

>60

73

N/A

VHDL-Syn

-5

184 LUTs

>60

73

N/A

Verilog-LSE

-5

92LUTs

>60

73

N/A

Verilog-Syn

-5

113 LUTs

>60

73

N/A

VHDL-LSE

-5

89 LUTs

>60

73

N/A

VHDL-Syn

-5

104 LUTs

>60

73

N/A

Verilog-LSE

-3

91 LUTs

>60

73

N/A

Verilog-Syn

-3

113 LUTs

>60

73

N/A

VHDL-LSE

-3

87 LUTs

>60

73

N/A

VHDL-Syn

-3

104 LUTs

>60

73

N/A

Verilog-Syn

-5

136 LUTs

>60

73

N/A

VHDL-Syn

-5

189 LUTs

>60

73

N/A

Verilog-Syn

-5

150 LUTs

>60

73

N/A

VHDL-Syn

-5

184 LUTs

>60

73

N/A

Verilog

-5 ns

84 Macrocells

>100

73

N/A

VHDL

-5 ns

84 Macrocells

>100

73

N/A

Verilog

155 MHz

84 Macrocells

>100

73

N/A

VHDL

155 MHz

84 Macrocells

>100

73

N/A

Performance and utilization characteristics are generated using LCMXO2-1200HC-5TG144C, with Lattice Diamond 3.3 design software.

Performance and utilization characteristics are generated using LCMXO256C-3T100C, with Lattice Diamond 3.3 design software.

Performance and utilization characteristics are generated using LFE3-95EA-7FN1156C, with Lattice Diamond 3.3 design software.

Performance and utilization characteristics are generated using LFECP33E-5F484C with Lattice Diamond 3.3 design software.

Performance and utilization characteristics are generated using LFXP2-5E-5FT256C, with Lattice Diamond 3.3 design software.

Performance and utilization characteristics are generated using LFXP20C-5F484C with Lattice Diamond 3.3 design software.

Performance and utilization characteristics are generated using LC4256ZE-5TN100C with Lattice ispLEVER Classic 1.4 software.

Performance and utilization characteristics are generated using ispLSI5512VE-155LB272 with Lattice ispLEVER Classic 1.4 software.

Performance and utilization characteristics are generated using LFE5U-45F-6MG285C, with Lattice Diamond 3.3 design software.

10

SDR SDRAM Controller

Figure 8. Module Relationships

sdr_tb

sdr

sdr_data

text

text

sdr_sig

sdr_top

sdr_ctrl

system

Technical Support Assistance

e-mail:

techsupport@latticesemi.com

Internet: www.latticesemi.com

Revision History

Date

Version

Change Summary

Previous Lattice releases.

July 2009

04.2

Added support for the ispMACH 4000ZE CPLD family.

October 2009

04.3

Added support fo VHDL language.

February 2010

04.4

Added support for LatticeXP2 device family.

November 2010

04.5

Added support for the MachXO2 device family.

Updated to support Lattice Diamond 1.1 design software.

Updated to support ispLEVER 8.1 SP1 design software.

April 2011

04.6

Added support for LatticeECP3 device family.

March 2014

04.7

Updated Table 1, Performance and Resource Utilization.

- Added support for ECP5 device family.

- Added support for Lattice Diamond 3.1 design software.

Updated corporate logo.

Updated Technical Support Assistance information.

September 2014

04.8

Updated Table 1, Performance and Resource Utilization.

- Added support for Lattice Diamond 3.3 design software.

- Added LSE support for LatticeXO and LatticeXO2.

- Added Synplify support for ECP5.

11

You might also like

- ADDx Compact Single Channel DF Antennas Bro en 3608 5458 12 v0300Document6 pagesADDx Compact Single Channel DF Antennas Bro en 3608 5458 12 v0300Hưng Nguyễn ĐìnhNo ratings yet

- Mti Radar PDFDocument102 pagesMti Radar PDFHưng Nguyễn ĐìnhNo ratings yet

- Multi-Standard ReceiverDocument8 pagesMulti-Standard ReceiverHưng Nguyễn ĐìnhNo ratings yet

- Fundamentals of MmWave SensorsDocument9 pagesFundamentals of MmWave SensorssanikereNo ratings yet

- Syntheric Aperture RadarDocument37 pagesSyntheric Aperture RadarHưng Nguyễn ĐìnhNo ratings yet

- Book 3Document16 pagesBook 3HariPonnanaNo ratings yet

- Radar, Electronic Warfare (EW) and ELINT Testing ChallengesDocument25 pagesRadar, Electronic Warfare (EW) and ELINT Testing ChallengesHưng Nguyễn ĐìnhNo ratings yet

- Hoole Implementation 2008Document104 pagesHoole Implementation 2008Hưng Nguyễn ĐìnhNo ratings yet

- An FPGA Based Controller For A MEMS Tri-Mode FMCW RadarDocument206 pagesAn FPGA Based Controller For A MEMS Tri-Mode FMCW RadarHưng Nguyễn ĐìnhNo ratings yet

- Phased ArrayDocument20 pagesPhased ArraysatyahalNo ratings yet

- 12 An FMCW Mimo Radar Sensor Dave PatrickDocument22 pages12 An FMCW Mimo Radar Sensor Dave PatrickHưng Nguyễn ĐìnhNo ratings yet

- Signal Processing of FMCW Synthetic Aperture Radar DataDocument133 pagesSignal Processing of FMCW Synthetic Aperture Radar DataHưng Nguyễn ĐìnhNo ratings yet

- Signal Processing of FMCW Synthetic Aperture Radar DataDocument133 pagesSignal Processing of FMCW Synthetic Aperture Radar DataHưng Nguyễn ĐìnhNo ratings yet

- 12 An FMCW Mimo Radar Sensor Dave PatrickDocument22 pages12 An FMCW Mimo Radar Sensor Dave PatrickHưng Nguyễn ĐìnhNo ratings yet

- Radar Handbook PDFDocument1,352 pagesRadar Handbook PDFAwak100% (7)

- Design of A Microstrip Bandpass Filter For 3.1-10.6 GHZ Uwb SysteDocument57 pagesDesign of A Microstrip Bandpass Filter For 3.1-10.6 GHZ Uwb SysteHarishNo ratings yet

- ADS Tutorial 2Document4 pagesADS Tutorial 2Minh VuNo ratings yet

- FmRadioDocument99 pagesFmRadioHưng Nguyễn ĐìnhNo ratings yet

- Microstrip Design Using HP Advanced Design System (ADS) : 304-573A Microwave Electronics TutorialDocument23 pagesMicrostrip Design Using HP Advanced Design System (ADS) : 304-573A Microwave Electronics TutorialbaburaokodavatiNo ratings yet

- VHDL SS09 Teil06Document38 pagesVHDL SS09 Teil06Krishnakumar SomanpillaiNo ratings yet

- FFTandMatLab Wanjun HuangDocument26 pagesFFTandMatLab Wanjun HuangDiego PurizagaNo ratings yet

- Design of A Microstrip Bandpass Filter For 3.1-10.6 GHZ Uwb SysteDocument57 pagesDesign of A Microstrip Bandpass Filter For 3.1-10.6 GHZ Uwb SysteHarishNo ratings yet

- CORE Generator GuideDocument146 pagesCORE Generator GuideHưng Nguyễn ĐìnhNo ratings yet

- Spartan-3E Libraries Guide For HDL DesignsDocument517 pagesSpartan-3E Libraries Guide For HDL DesignsHưng Nguyễn ĐìnhNo ratings yet

- Design and Implementation of An FPGA-basedDocument59 pagesDesign and Implementation of An FPGA-basedHưng Nguyễn ĐìnhNo ratings yet

- Simulink TutorialDocument56 pagesSimulink TutorialUday KumarNo ratings yet

- Filters FPGADocument36 pagesFilters FPGAAly BendlalaNo ratings yet

- Automatic Gain Control Circuits Theory and DesignDocument25 pagesAutomatic Gain Control Circuits Theory and DesignKhristianus BeauNo ratings yet

- FFTandMatLab Wanjun HuangDocument26 pagesFFTandMatLab Wanjun HuangDiego PurizagaNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Seminar Report 2017 Vlsi Implementation of A Cost Efficient Near-Lossless Cfa Image Compressor For Wireless Capsule EndosDocument31 pagesSeminar Report 2017 Vlsi Implementation of A Cost Efficient Near-Lossless Cfa Image Compressor For Wireless Capsule EndosAnanthu J VNo ratings yet

- CONTROLDocument12 pagesCONTROLTaseen JannatNo ratings yet

- Bird Meter 4391A-ManualDocument46 pagesBird Meter 4391A-Manualpy5rcbNo ratings yet

- Simulation For Iot Based Smart Traffic Control System For Emergency VehiclesDocument44 pagesSimulation For Iot Based Smart Traffic Control System For Emergency VehiclesJeba JinilNo ratings yet

- Chengzhou WangDocument159 pagesChengzhou WangAnonymous n30qTRQPoINo ratings yet

- Communications Systems - LBD8921/02 Wall Mounting Handset StationDocument3 pagesCommunications Systems - LBD8921/02 Wall Mounting Handset StationShreyaNo ratings yet

- Mpms Combi Controller Fault CodesDocument4 pagesMpms Combi Controller Fault CodesFatih YÜKSELNo ratings yet

- HP-AN243 - The Fundamentals of Signal AnalysisDocument68 pagesHP-AN243 - The Fundamentals of Signal Analysissirjole758483% (6)

- Reference Guide To Fiber Optic Testing: Second EditionDocument172 pagesReference Guide To Fiber Optic Testing: Second EditionJoao Silva100% (1)

- Lighting Lighting: A TLED Solution For Your ApplicationDocument35 pagesLighting Lighting: A TLED Solution For Your ApplicationCent LopezNo ratings yet

- 2 N 6394Document8 pages2 N 6394lgrome73No ratings yet

- Caleng3 - Problem Set - Q2Document5 pagesCaleng3 - Problem Set - Q2Rheina VelasquezNo ratings yet

- EN Calibration Source M340 - DatasheetDocument2 pagesEN Calibration Source M340 - DatasheetMansour AchaourNo ratings yet

- Daytime Running Lights,: Wiring DiagramDocument7 pagesDaytime Running Lights,: Wiring DiagramPetronela MasiliaNo ratings yet

- Tesys D Lc1d25bdDocument7 pagesTesys D Lc1d25bdw.priatmadiNo ratings yet

- SG125CX DatasheetDocument2 pagesSG125CX DatasheetJun OrtizNo ratings yet

- EN010101-000245-Document Ref 7.14 LC TA4.7 Outline Battery Safety Management PlanDocument33 pagesEN010101-000245-Document Ref 7.14 LC TA4.7 Outline Battery Safety Management PlanSerg MarushkoNo ratings yet

- Envicool AC AIRCON MC30HDNC1ADocument7 pagesEnvicool AC AIRCON MC30HDNC1ABores ModearNo ratings yet

- Joystick: RomeoDocument14 pagesJoystick: RomeoAdfbbNo ratings yet

- Acer Aspire 3750GDocument92 pagesAcer Aspire 3750GQomari Ali MustofaNo ratings yet

- Technology and Development of 800 KV HVDC Applications: M. Haeusler H. Huang V. Ramaswami D. KumarDocument12 pagesTechnology and Development of 800 KV HVDC Applications: M. Haeusler H. Huang V. Ramaswami D. KumarRatheesh KumarNo ratings yet

- PV Module Safety Qualification According To IEC 61730:2004 EN 61730:2007Document6 pagesPV Module Safety Qualification According To IEC 61730:2004 EN 61730:2007Vinko RazlNo ratings yet

- Activity 2.3.5 XOR, XNOR, and Binary AddersDocument3 pagesActivity 2.3.5 XOR, XNOR, and Binary AddersAvalon BrownNo ratings yet

- Site Test Report Date: Al-Osais Co. KHUDARIYAH S/S 115/13.8 KV S/S CT Supervision Relay - MVTPDocument4 pagesSite Test Report Date: Al-Osais Co. KHUDARIYAH S/S 115/13.8 KV S/S CT Supervision Relay - MVTPsikander843562No ratings yet

- Lab. Experiment 1: Verification of Mesh Analysis Date:27/09/2021 Lab. Slot: L31+L32 Name: Ayush Giri Reg. No.: 21BDS0031Document11 pagesLab. Experiment 1: Verification of Mesh Analysis Date:27/09/2021 Lab. Slot: L31+L32 Name: Ayush Giri Reg. No.: 21BDS0031psNo ratings yet

- Ec 6011Document8 pagesEc 6011Karthikeyan_Go_9525No ratings yet

- CR310 ManualDocument236 pagesCR310 Manualelisio_fonsecaNo ratings yet

- 4 ECE3013 Linear Integrated Circuits 9.10.17Document2 pages4 ECE3013 Linear Integrated Circuits 9.10.17Siva ShankarNo ratings yet

- Lab Viva QuestionDocument13 pagesLab Viva QuestionNarasimman Don100% (1)

- PRT Simulation, Two, Three and Four Wire Connecction ReportDocument6 pagesPRT Simulation, Two, Three and Four Wire Connecction Reportميسرة80% (5)