Professional Documents

Culture Documents

00156728

Uploaded by

Vivek RoyCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

00156728

Uploaded by

Vivek RoyCopyright:

Available Formats

~

IEEE Transactions on Consumer Electronics, Vol. 38, No. 3, AUGUST 1992

496

A VERSATILE DIGITAL ENCODER FOR VIDEO SIGNALS

Stefan Drude, Rolf-Dieter Gutsmann

Phi Ii ps Semiconductors, Hamburg, Germany

Abstract

A versatile integrated encoder circuit for television signals

is described. The encoder can convert digital baseband

video data input into NTSC or PAL coded analog output

signals. Composite video and S-Video output are available

simultaneously. The CMOS device accepts 24-bit RGB

data as well as indexed colour and a number of different

YUV data formats. The output signal can be synchronized

to an extemal video input signal. The circuit provides an

easy way to store computer and workstation graphics on a

video cassette recorder.

Introduction

Traditionally, the personal computer used to deal with inputs such as data, text and communication. Desktop Video

adds a new medium "Realtime Video" to the personal computing world. With other media like "Audio" and "Sound"

already available, the personal computer (PC) moves more

and more towards a universal multimedia processing engine. The ultimate goal is to replace the number of different

machines used to handle these media today by a single

computing device.

The basic idea behind desktop video is to combine both,

computer generated graphic data and realtime video on one

screen. The digital encoder to be presented here can be

used to record the resulting images on a video cassette recorder (VCR). The applications of desktop video include

training and education programmes, marketing, electronic

shopping, office video conferencing and others.

The general outline of a desktop video system is shown in

fig. 1. The input processing block digitizes the incoming

video information and decodes the signal to obtain

luminance and colour difference information in a format

suitable for delivery to the feature processing part. The

input signals can be delivered from a variety of signal sources: television (TV) tuner, camera, but also tape recorder,

laser or video compact disc (CD Video). The feature processing unit performs the operations necessary to fit the video image to the computer graphic data. The converted

Manuscript received June 5 , 1992

data is stored in the video frame buffer. The video frame

buffer has two independent outputs: one is to the monitor

of the personal computer system operating at the data rate

given by the computer video graphics card, the other is to

the digital encoder operating at data rates compatible with

Input

Processing

Input

Source

CVU8 /"

1

1

Feature

Processing

Output

Processing

output

Peripherals

CVBS oul

Tape Recorder

Corn. Networks

TV Monitor

CD Video

Laser Disc

TV Camera

TV tuner

VCR

butler

Fig. 1: Desktop Video System Architecture

the standard television deflection frequencies. The digital

encoder chip is intended for application in such a desktop

video system environment.

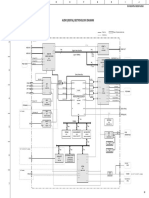

Digital Multistandard Encoder

The digital encoder chip is capable of converting digital

colour video input data into analog video output signals

coded according to the colour television standards NTSC

and PAL [2]. A composite video signal (CVBS) as well as

luminance (Y) and chrominance (C) information on separate outputs for S-Video applications are available simultaneously. The main signal processing functions are

performed in the input processing, modulator and output

processing blocks, see fig. 2. Other functional blocks of the

encoder care for device control access, crystal clock

generation, and synchronisation of the video output to an

extemal video source.

Principle of Operation

A simplified functional block diagram of the encoder is

shown in fig. 2. The 24-bit data supplied to the three data

inputs RED, GREEN and BLUE (R, G, B) is first passed

0098 3063/92 $03.00

1992 IEEE

Drude and Gutsmann: A Versatile Digital Encoder for Video Signals

through the colour look-up tables (CLUT). The digital encoder employs three independent tables, one per channel.

This allows to program different characteristics for each of

the channels. The colour look-up tables can be used e.g. to

implcment the gamma-precorrection sometimes required

for encoding. The following matrix block computes the

rcsulting luminance (Y) and colour difference (U, V) information from the corresponding RGB input based on the

well known matrix equations. The digital colour difference

signals U and V taken from the matrix output are filtered in

three filter sections. A decimation in time and interpolation

scheme is used in these filters to allow for maximum

flexibility in the input data formats. The filter characteristics can be set for a standard chrominance

bandwidth of 1.3 MHz or an enhanced bandwidth of 1.9

MHz. At the output of the filter sections sufficiently

bandlimited colour difference data is delivered at a sampling rate such that processed U and V data are available

with every sample in the luminance channel. The U and V

signal components are used to modulate the colour subcarrier. The U and V data is replaced by some fixed values

to define the colour reference burst phase during the burst

period. Finally, the encoder adds the luminance signal and

the modulated colour subcarrier, inserts the line and field

synchronisation pulses to obtain the digital composite video output. This is converted back to the analog domain by

one of the three on-chip digital to analog converters

(DAC).

491

Input Processor

A number of different input data formats are supported by

the digital encoder device. While the standard input format,

as previously described, is parallel 24-bit RGB data at pixel

clock rate, input of digital W V data in 4:4:4 parallel format, time-multiplexed4:2:2 and 4:l: 1 formats as well as 8bit indexed pseudo-colour format are also possible. The

time-multiplexed YW formats take advantage of the

reduced chrominance bandwidth used in television transmission systems and require less video frame buffer

capacity than the parallel formats. The indexed colour input

mode uses an 8-bit data word to select one out of 256

predefined colours stored in the colour look-up tables to

obtain the resulting 24-bit colour information.

Input data applied to the encoder input is first demultiplexed if required. The encoder can be set to expect input

data in a representation that complies with the input data

range defined by CCIR601 111. The resulting parallel data

is fed through the colour look-up tables. These can be used

to perform the gamma-precorrection required in RGB input

mode or to set parameters such as saturation, brightness

and contrast in W V input modes. The colour look-up

tables are implemented as three independent random access

memory blocks of 256 x 8 bit. In the normal functional

mode, the incoming data in each individual channel is

taken as an index to select the associated output value from

Input Processor

~>>-

256x8

GREEN

BLUE

G'

256x8

.

B'

Modulator and Outwt Interface

>

.

,

,,,

,.

I

'

4

I

RGBlYUV _z

Matrix

__.*

Lowpass

Normalizer

256 x 8

__-?I

Lowpass

>-

,

,I

,.*

,

,

,":

Modulator

9-bilDAC

C

FilterXZ

>- I

9-bilDAC

Genlock Processor

Synchronisation Processing

I

i

1

i CVBS +

9-bilDAC

,, ,,

, .,

,

Control Interface

Clodc Interface

serial

Fig. 2: General Block Diagram of the Encoder

parallel

IEEE Transactions on Consumer Electronics, Vol. 38, No. 3, AUGUST 1992

498

Y

b

ROM-B

Fig. 3: Digital RGB to YUV Matrix

the memory. In indexed colour input mode, the memories

are all supplied with the same 8-bit data to obtain the 24-bit

colour information from the three memory outputs. The

three memories can be loaded using the control interface

functions.

Lowpass filter #1 is a digital decimation filter section, refer

to fig. 2. It is used to reduce the bandwidth of the colour

difference signals if they are based on 4:4:4 input data signals. In this case also the data rate of the U and V channels

is reduced by a factor of two. The filter is automatically activated under software control. The transfer characteristic

in 4:4:4 mode is given by

H(z) = 1/16 ( PI(z) P ~ ( z-) z - )~P3(z) z ' ~ ,

where

PI(z) = -0.5 i-4z-2 - O S Z - ~ ,

P2(z) = 1 + z-l Y2, P3(z) = 0.5 + 2 - I + O . ~ Z - ~

The equivalent frequency transfer function of the decimation filter is shown in fig. 4. The filter is switched to a

simple pipeline delay in other input modes. Data in the

luminance channel is not filtered but delayed in time to

compensate for processing delays in the U and V channels.

A normalizer block is placed between lowpass filter #1and

lowpass filter #2. It introduces additional offset and gain to

adjust the output data range for optimum use of the digital

to analog converters' conversion range. The 8-bit input

data values are expanded to 9 bit.

A digital matrix block performs the conversion of RGB

input data to the Y W representation. The structure of the

matrix block is shown in fig. 3. Three read-only memories

(KOMs) are used to compute the weighted input values.

The luminance component Y is directly obtained by adding

these values. The colour difference outputs U and V are

determined by the difference of the Y component and the

respective colour input. The implementation of the matrix

coefficients as a ROM table access allows to avoid

hardware multipliers and to limit input values outside the

standard input range to some given maximum value.

The second filter section (Lowpass Filter #2) serves two

purposes: Original 4: 1: 1 colour difference data input can be

interpolated to obtain a 4:2:2 data rate, and the bandwidth

of U and V channel data is limited to achieve a standard

overall bandwidth of 1.3 MHz. The interpolation filter can

also be bypassed under software control to provide an ex-

Fig. 4: Transfer Characteristic Decimation Filter

Fig. 5: Frequency Response Lowpass Filter #2

Drude and Gutsmann: A Versatile Digital Encoder for Video Signals

tended chrominance bandwidth of 1.9 MHz in special encoding applications. The transfer function of the filter is

given by

H(z) = 1/16 (0.5 + z - +~0.5z-3(-1 + ~ O Z --2-8,

~ z-~,

the frequency characteristic is shown in fig. 5. A special

blanking control signal sets the outputs of filter #2 to zero

during the horizontal and vertical blanking time of the encoded output signal. The filtered and bandlimited YUV

data in 4:2:2 data format is applied to the modulator.

499

to cover NTSC and PAL television standards. In addition,

the V component is inverted in every other line and the

field indication burst sequence is generated as required by

the PAL standard. The colour difference data is applied to a

final filter section (filter #3), which interpolates U and V

data to obtain a sample of each colour difference signal

with every sample in the luminance channel (4:4:4 format).

The frequency characteristic is determined by

H(z) = (0.25 + O . ~ Z - ' + 0 . 2 5 ~ - z~-)~ .

The digital encoder features full compatibility with NTSC

and PAL television standards [2]. Field rates of 50 and 60

Hz are supported resulting in 625 and 525 lines per frame.

Encoding can be either interlaced or non-interlaced. The

pixel clock rate can be chosen such that either a CCIR601

compatible data rate of 13.5 M H z is maintained [l] or a

data rate compatible with the square pixel arrangement is

obtained, that is 12.27 M H z and 14.75 M H z , respectively.

The corresponding number of active pixels per line is

adaptcd accordingly.

The colour subcarrier is generated in a discrete time oscillator, which provides sine and cosine output frequencies to

drive the modulator. The nominal colour subcarrier frequency can be either 4.43 MHz or 3.58 MHz, it has a fixed

relation to the line frequency in use. Optionally, the colour

subcarrier frequency can be finetuned using one of the control registers and also be synchronized to an extemal video

source, see the following sections. Two 8 by 9 bit multipliers are used to obtain the quadrature signals from the

two baseband inputs. The two products are summed up and

rounded correctly by some additional logic and an auxiliary

adder to obtain the final QAM modulated subcarrier output.

The U and V signal components are used to modulate the

colour subcarrier according to the quadrature amplitude

modulation (QAM) scheme required by the NTSC and

PAL television standards, The encoder generates the colour

subcarrier burst whenever the burst gate signal is active,

see fig. 6. Three different burst phase positions are defined

Finally, the encoder adds the luminance signal and the modulated colour subcarrier, and inserts the line and field

synchronisation pulses (HSYNC, VSYNC) to obtain the

digital composite video output. This is converted back to

the analog domain by one of the three on-chip digital to

analog converters. The resolution of the converters is 9 bit.

Modulator and Output Processing

'

HN-Sync

Insertion

HSYNC

Luminance & Synchronisation

VSYNC

Digital to

Analog

Converter

ext. CVBS

CVBS

Frequency

I

PAL B

NTSC

"

Converter

sinR

I

PAL A

key

IEEE Transactions on Consumer Electronics, Vol. 38, No. 3 , AUGUST 1992

500

The other two outputs provide luminance and chrominance

output for S-Video systems. The encoder features also a

fast switch, which allows to key the extemal composite

video input into the usual output channel. Special device

control registers allow for chrominance phase adjust with

respect to the synchronizing reference input.

The three identical converter sections are implemented

using a dedicated resistor ladder network. A coarse ladder

delivers the reference voltages for a matrix of fine ladders.

By using this scheme of resistors the requirements on

device matching could be reduced from 1024 matched elements to 16 and 64 matched resistors, respectively. Analog

switches connect the selected output voltage to the output

driver stage. The outputs feature a 75 Ohm output impedance. The analog output drivers signal bandwidth is

better than 10 MHz. The nominal output voltage swing is

1 V,, into a 75 Ohm load, it can be adapted for nominal

CVBS or Y/C output voltages. Simple analog output filtering is applied to remove the unwanted aliasing components

and to compensate for the zero order hold frequency

characteristic of the converter output stage.

Genlock Processor

The operating modes of the digital encoder reflect the different applications it can be used for. In Slave-Mode, the

encoder receives pixel clock, horizontal and vertical

synchronisation from an external source together with the

video data to be encoded. In Stand-alone-Mode, the encoder generates these signals itself based on its internal

quartz clock reference. The synchronisation and clock sig-

nals generated by the encoder must be used to contTol the

video frame buffer read operation. Synchronisation of these

signals to an extemal composite video source is possible in

the Genlock-Mode of the encoder, this requires just two additional circuits: an analog to digital converter and a dedicated clock generator device. The encoder contains a

special hardware part, the genlock processor, to support

this mode of operation. Finally, a Test-Mode is provided

where the contents of three test registers are taken to determine the colour information of the encoded video signal.

The genlock processor takes the digitized external composite video signal as a reference for encoding. Based on

this composite video input, the genlock processor has to

maintain the sampling clock and to lock its own colour subcarrier oscillator frequency and phase to the input signal.

The respective circuit parts are shown in figs. 7 and 8. The

sampling clock is locked to the line frequency of the incoming signal in a digital phase locked loop. The genlock

processor receives the synchronisation pulses fH from the

synchronization processor. The phase detector compares

this signal with a locally generated signal f ~ .A crystal

controlled discrete time oscillator, a waveform shaper, and

a 4-bit digital to analog converter (DAC) are used to

provide the analog output signal LFCO. The dedicated

clock generator circuit multiplies LFCO in a second phase

locked loop to obtain the sampling clock, which in turn is

used to clock a counter. This counter operates as a second

discrete time oscillator at fH. The resulting phase difference is filtered, the control value added to the offset

input. This closes the loop, the sampling clock is locked to

Sampling Clock

l

I

Counter/

Oscillator

Digital

Phase

Detector

Loop

Filter

2I

from

Synchronisation

Processor

i

I

1I

I

Voltage

Controlled

Default

Divider

Oscillator

Genlock Processor

I

I

Crystal

I

v

II

I

I

Loop

Phase

Filter

Detector

LFCO

4-bit DAC

Waveform

Adjust

Clock Generator Circuit

L____________--_-___-________-__------_.

Fig. 7: Genlock Processor Sampling Clock Control Loop

Discrete

Time

Oscillator

Register

501

Drude and Gutsmann: A Versatile Digital Encoder for Video Signals

the line frequency of the incoming composite video signal.

The characteristics of the loop filter are crucial for lock-in

and tracking performance of the sampling clock control

loop. In order to avoid residual errors caused by non-standFull Wave

Rectifier

gnal for burst detection, and to deliver lowpass filtered

input signals to the synchronization processor for

synchronization pulse detection and extraction. Filter #2

accumulates the phase deviations of the reference burst in

genlock mode and thus generates the control signal for the

local colour subcarrier oscillator. The transfer function of

the filter is given by

to S nchronisation

Fyrocessor

to Burst

Detection

I

Colour.

Subcarrier

Oscillator

Lowpass

Filter #2

Fig. 8: Colour Subcarrier Control Loop

ard signals, the loop filter consists of an integral and a

proportional path. Three different sets of coefficients are

provided to cover television signal and VCR inputs as well

as the unlocked case.

A second digital phase locked loop inside the genlock

processor is used to control the internal colour subcarrier

frequency, see fig. 8. Lowpass filter #1 removes the high

frequency component while lowpass filter #2 is the colour

subcarrier control loop filter. Besides its use in the colour

subcarrier control loop, filter #1 is also used in a time multiplexed fashion to filter a rectified version of the input si-

H(Z) = 2-10z-1/(1-

+ 2-4,

i.e. it is of the proportional-integral type. Fig. 9 shows the

simulated loop settling performance with a real sampled

composite video reference signal as input data. The phase

control input to the digital colour subcarrier oscillator is

shown in units versus the time. The non-zero steady state

phase control input is due to a difference in the encoders

crystal clock frequency and thus the nominal colour subcarrier frequency of the encoder and the colour subcarrier frequency of the input signal. This difference was

intentionally introduced in the simulation.

Control Interface

The encoder offers a maximum of flexibility through a

number of programmable device registers. The internal

device registers are split into two separate tables: the control table contains 16 registers, and the colour look-up table

consists of three banks for red, green and blue of 256 bytes

each. The programmers model of the encoder is shown in

fig. 10. Two different types of control interfaces are

provided. The parallel 8-bit microprocessor interface fea-

40

30

20

10

0

-10

-20

-30

-40

10

15

Fig. 9: Simulated Colour Subcarrier Lock-in Performance

20

25 m s

IEEE Transactions on Consumer Electronics, Vol. 38, No. 3 , AUGUST 1992

502

tures fast access to the intemal registers while the two-wire

serial interface [3] allows for low control signal wiring

overhead. Using either interface, features like the operating

mode, the input data format and the colour encoding standard can be programmed and the colour look-up tables can

be loaded.

lution of the NTSC encoding standard. Complex overlays

can be created on the personal computer and mixed with

any video source using the genlock feature of the encoder.

.lnplt Format

Desktop Video Application System

The digital encoder is part of a family of devices for

desktop video systems [5] as shown in fig. 11. The frontend

part comprises an analog to digital converter and a digital

multistandad colour decoder with its associated sampling

clock generator device. A second ADC is optional for S Video systems. With two additional circuits processing of

analog RGB input signals is also possible. The decoder

delivers digital YUV data to the feature processing block,

which comprises all the manipulation units such as filtering, windowing and scaling blocks and the video memory.

The main purpose of the memory is to decouple the different sampling clock domains: television (TV) line frequency locked sampling clock in the input processing, computer

grauhic and independent TV output sampling clock

frequencies in the output processing block. From the output

of the video memory analog RGB signals are obtained to

drive the computer monitor, the digital encoder provides

the encoded composite and S-Video information.

Based on this architecture, the encoder can be used in a

number of applications. The most interesting one seems to

be to record personal computer graphics including realtime

video information on a video cassette recorder. A 640 x

480 pixels video graphics image fits perfectly to the reso-

Cdcur Lwk-upTables

Cmbol Table

-Test RegistersR. G. I3

-Encoder Operabng Mode

Sync Rocesshg

- Sync OuI$ut Slgnal

-Genlock Mode Conbol

.Enable Deum. Keyng

General Device

Cmbol Registers

.Clock Setup

.Colour Killer

.General Purpose, R e s t

12

Enmder Conbd

Registers

-Chrominance Phase Adjust

.Colour Subcarrier Frequency

.Encoding Standard

253

254

255

15

Fig. 10: Programmers Model of the Encoder

A similar arrangement can be used to perform editing of

home and commercial videos. Desktop video conferencing

uses the digital encoder to transmit desktop video information via the TV transmission facilities offered by some of

the new fast optical fibre communication networks.

Applications of the digital encoder outside the desktop

video area are also possible. A simple timebase correction

system for video cassette recorders is constructed using

first-in-first-out serial memory devices. The frontend part

locks to the line frequency of the video cassette recorder

and puts the decoded video data into the frame buffer. The

PC Graphic (RGB)

PC Graphic Data

Red

Green

Blue

PC Interface Bus

Line Locked Clock Domain

PC Graphidext. Video Clock Domain

Fig. 11: Desktop Video Application System Architecture

503

Drude and Gutsmann: A Versatile Digital Encoder for Video Signals

encoder in tum has a stable crystal clock and reads data out

of the frame buffer at a constant rate. A similar arrangement can be used to carry out video frame grabbing functions.

Biographies

Summary

The encoder circuit has been designed in our C200 Complementary Metal Oxide Semiconductor (CMOS) process

technology, which offers a minimum feature size of 1 um

and two layers of metal interconnect. The overall chip size

is about 68 mm2. The device is housed in a 84-pin plastic

leaded chip carrier (PLCC-84) package. The design of the

circuit is based on our library of digital video signal

processing blocks. Compared to analog encoder concepts

the digital video encoder has a number of advantages, particularly when looking at operation in personal computing

environments. A direct five volt supply, the realisation of

colour space matrix as well as encoding features independent of temperature and ageing effects, and the ability

to process computer generated data directly in digital form

fit perfectly to the desktop video and multimedia requirements.

Acknowledgement

The authors wish to thank Hartmut Hackmann, Achim Mittelberg and Gerhard Pletz-Kirsch for their contributions to

the realization of the chip.

Special thanks to Thomas Rudolph for his support in preparing the plots used in this paper.

References

[ 11 CCIR Recommendation 601-2 "Encoding Parameters of

Digital Television for Studios"

[2] CCIR Recommendations and Reports of the XIVth

Plenary Assembly, Rec. 470-1, Rec. 624-1, Vol. XI

(Television)

[3] Philips Semiconductors, Specification of the 12C-Bus,

Philips Publication 9398 393 4001 1

Stefan Drude was bom in Dusseldorf, Germany in 1957.

He received the Dip1.-Ing. degree in Electrical Engineering

from the Technical University of Aachen (RWTH) in 1983.

The same year he joined the Philips Semiconductors Application Laboratory Hamburg. From 1987 to 1991 he was

responsible for product innovation and sales support in the

field of radio pagers. He is now a section manager responsible for the sales support of digital video circuits for multimedia applications.

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- MT6768 LPDDR4x Internal ProjectDocument31 pagesMT6768 LPDDR4x Internal Projectpc partnerNo ratings yet

- Service Manual: GE SIGNA 1.5T T/R Knee and Foot Array CoilDocument28 pagesService Manual: GE SIGNA 1.5T T/R Knee and Foot Array CoilRogerio Castro100% (1)

- Least Bit Error Rate Adaptive Neural EqualisersDocument8 pagesLeast Bit Error Rate Adaptive Neural EqualisersVivek RoyNo ratings yet

- PDFDocument7 pagesPDFVivek RoyNo ratings yet

- Effects Impulsive Loop: of Noise Phase-Locked FM DemodulatorDocument7 pagesEffects Impulsive Loop: of Noise Phase-Locked FM DemodulatorVivek RoyNo ratings yet

- Demodulator Time-Constant Requirements Interference RejectionDocument9 pagesDemodulator Time-Constant Requirements Interference RejectionVivek RoyNo ratings yet

- PDFDocument11 pagesPDFVivek RoyNo ratings yet

- PDFDocument6 pagesPDFVivek RoyNo ratings yet

- An Analog-Encoder Employing Resistance: D (E (E e N (E 2)Document7 pagesAn Analog-Encoder Employing Resistance: D (E (E e N (E 2)Vivek RoyNo ratings yet

- Narrow-Band CMOS FM Receiver Using Single-Sideband Modulation IF FilteringDocument8 pagesNarrow-Band CMOS FM Receiver Using Single-Sideband Modulation IF FilteringVivek RoyNo ratings yet

- Phone Book Appendix from Programming in ANSI CDocument21 pagesPhone Book Appendix from Programming in ANSI Crathnam.pmNo ratings yet

- DOR-230 PCB input signal errorDocument1 pageDOR-230 PCB input signal errorDaniel GatdulaNo ratings yet

- Minor Project SynopsisDocument3 pagesMinor Project SynopsisHappy RajputNo ratings yet

- Phu Giang Electric Co - LTDDocument54 pagesPhu Giang Electric Co - LTDBùi Thanh SơnNo ratings yet

- Siemens Electric Motor 15hp 1500rpmDocument17 pagesSiemens Electric Motor 15hp 1500rpmShamsul HaqueNo ratings yet

- Andrew w2x6516dsvtmDocument2 pagesAndrew w2x6516dsvtmmirsNo ratings yet

- Lab3 LVDT CalibrationDocument14 pagesLab3 LVDT CalibrationSaurabhNo ratings yet

- Datasheet Cyrix I 400A ENDocument2 pagesDatasheet Cyrix I 400A ENTom TomNo ratings yet

- Patient Monitor Maintenance CheckDocument2 pagesPatient Monitor Maintenance CheckDickyNo ratings yet

- Datasheet General Heavy Duty ESS EnglishDocument2 pagesDatasheet General Heavy Duty ESS EnglishDavid Alexander CeronNo ratings yet

- Data Sheet: Integrated FM Tuner For Radio ReceiversDocument11 pagesData Sheet: Integrated FM Tuner For Radio ReceiversahmedNo ratings yet

- SDH Synchronization: ITSF, London October 2005 Jean-Loup FerrantDocument31 pagesSDH Synchronization: ITSF, London October 2005 Jean-Loup Ferranthas100% (5)

- Schematic Diagram DVD-P370Document8 pagesSchematic Diagram DVD-P370Alexandre S. Corrêa0% (1)

- State of The Art DC-DC Converter Topologies For The Multi-Terminal DC Grid Applications: A ReviewDocument7 pagesState of The Art DC-DC Converter Topologies For The Multi-Terminal DC Grid Applications: A ReviewariphineNo ratings yet

- Sony Kv-xf21 ManualDocument26 pagesSony Kv-xf21 ManualMuns BadillaNo ratings yet

- 11kv 200a Ab Switch PDFDocument2 pages11kv 200a Ab Switch PDFhimanshuNo ratings yet

- SDI ASI Encoder MultiplexerDocument41 pagesSDI ASI Encoder MultiplexerChristie MillerNo ratings yet

- Star Delta BomDocument7 pagesStar Delta BomEr.AROCKIA STEPHAN VSGNo ratings yet

- Digital to Analog Conversion ExplainedDocument37 pagesDigital to Analog Conversion ExplainedECEHOD SECNo ratings yet

- Low Voltage Alternator - 4 Pole: 2650 To 3300 kVA - 50 HZ / 3150 To 3900 kVA - 60 HZ Electrical and Mechanical DataDocument12 pagesLow Voltage Alternator - 4 Pole: 2650 To 3300 kVA - 50 HZ / 3150 To 3900 kVA - 60 HZ Electrical and Mechanical DataGustavo Gomes RochaNo ratings yet

- Sr90 StandardDocument26 pagesSr90 Standardflorin74No ratings yet

- Three ammeter method explainedDocument2 pagesThree ammeter method explainedkalokosNo ratings yet

- MiCOM P44XDocument8 pagesMiCOM P44XMahesh YadaNo ratings yet

- The GBD-PLUS' compact glass break detectionDocument2 pagesThe GBD-PLUS' compact glass break detectionDidier Samir GuillenNo ratings yet

- A Hybrid Cooperative Spectrum Sensing Technique For Cognitive Radio Networks Using Linear ClassifiersDocument6 pagesA Hybrid Cooperative Spectrum Sensing Technique For Cognitive Radio Networks Using Linear Classifierssuchi87No ratings yet

- Project-Antenna ArrayDocument17 pagesProject-Antenna ArraysushantNo ratings yet

- Block Diagrams: Audio (Digital) Section Block DiagramDocument19 pagesBlock Diagrams: Audio (Digital) Section Block DiagramAran Jed HostelleroNo ratings yet

- TPS-Instruction ManualDocument42 pagesTPS-Instruction ManualGheorghe Gabriel CerneanNo ratings yet

- FOR Approval Specification: 42.0" Wuxga TFT LCD TitleDocument35 pagesFOR Approval Specification: 42.0" Wuxga TFT LCD TitleWalter Petracca100% (1)